Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ), мультидифференциальных ОУ и RC-фильтрах на их основе).

Известны схемы комплементарных входных каскадов ОУ, выполненных в виде дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах с так называемой «архитектурой входного каскада операционного усилителя µА741» [1-30]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с типовым параллельно-балансным каскадом [29-31], стали основным усилительным элементом многих аналоговых интерфейсов. Это связано с тем, что в таких ДУ минимизируется входная емкость из-за отсутствия эффекта Миллера. Предлагаемое изобретение относится к данному подклассу устройств.

Ближайшим прототипом (фиг.1) заявляемого устройства является комплементарный дифференциальный усилитель по патенту US 4.429.284, fig.2, содержащий первый 1 и второй 2 входные транзисторы, базы которых являются соответствующими входами 3, 4 устройства, первый 5 и второй 6 выходные транзисторы, базы которых соединены с источником опорного тока 7, первый 8 и второй 9 токоограничивающие резисторы, включенные между эмиттерами соответствующих первого 1 входного и первого 5 выходного транзисторов, а также второго 2 входного и второго 6 выходного транзисторов, первый 10 и второй 11 последовательно соединенные вспомогательные резисторы, включенные между эмиттерами первого 1 и второго 2 входных транзисторов, вспомогательный прямосмещенный p-p переход 12, включенный между базами первого 5 и второго 6 выходных транзисторов и общим узлом 13 последовательно соединенных первого 10 и второго 11 вспомогательных резисторов, первую группу противофазных токовых выходов (14, 15), связанную с коллекторами первого 5 и второго 6 входных транзисторов, вторую группу противофазных токовых выходов (16, 17), связанную с коллекторами первого 1 и второго 6 выходных транзисторов.

Существенный недостаток известного ДУ состоит в том, что он имеет сравнительно узкий динамический диапазон (Uгр) линейного усиления дифференциальных сигналов (Uвх.max<Uгр≈100÷150 мВ). Как показано в монографии авторов настоящей заявки [31], это обстоятельство является главной причиной невысокого быстродействия современных операционных усилителей, обусловленной нелинейным режимом работы входного каскада ОУ. При этом для большинства ОУ с высокоимпедансным узлом и одним корректирующим конденсатором (Cк) максимальная скорость нарастания выходного напряжения определяется формулой [31]

где fcp - частота единичного усиления (частота среза) скорректированного ОУ;

Uгр - напряжение ограничения проходной характеристики iвых=f(uвх) входного каскада (для классических ДУ Uгр=50÷100 мВ).

Из (1) следует, что повышение υвых можно осуществить двумя качественно разными путями [31]:

1. Увеличением диапазона активной работы входного ДУ (Uгр) без изменения крутизны преобразования входного напряжения в выходные токи ДУ;

2. Повышением fcp за счет улучшения частотных свойств транзисторов, что связано, прежде всего, с использованием более высокочастотных и дорогостоящих техпроцессов (SG25VD, SG25Н1, SG25RН и др.).

Заявляемый входной каскад ОУ решает задачу повышения быстродействия за счет увеличения (без изменения крутизны) в несколько раз диапазона линейной работы входного каскада, измеряемого напряжением ограничения Uгр=0.4÷0,8 В.

Кроме этого предлагаемый ДУ достаточно эффективен в мультидифференциальных ОУ, где от входных каскадов требуется достаточно широкий диапазон линейной работы, а также в RC-фильтрах с малым уровнем нелинейных искажений.

Таким образом, основная задача предлагаемого изобретения состоит в расширении диапазона активной работы входного каскада ОУ для дифференциального сигнала - получении граничных напряжений его проходной характеристики iвых=f(uвх) на уровне Uгр=0.4÷0,8 В.

Поставленная задача достигается тем, что в комплементарном дифференциальном усилителе с расширенным диапазоном активной работы, содержащем первый 1 и второй 2 входные транзисторы, базы которых являются соответствующими входами 3, 4 устройства, первый 5 и второй 6 выходные транзисторы, базы которых соединены с источником опорного тока 7, первый 8 и второй 9 токоограничивающие резисторы, включенные между эмиттерами соответствующих первого 1 входного и первого 5 выходного транзисторов, а также второго 2 входного и второго 6 выходного транзисторов, первый 10 и второй 11 последовательно соединенные вспомогательные резисторы, включенные между эмиттерами первого 1 и второго 2 входных транзисторов, вспомогательный прямосмещенный p-n переход 12, включенный между базами первого 5 и второго 6 выходных транзисторов и общим узлом 13 последовательно соединенных первого 10 и второго 11 вспомогательных резисторов, первую группу противофазных токовых выходов (14, 15), связанную с коллекторами первого 1 и второго 2 входных транзисторов, вторую группу противофазных токовых выходов (16, 17), связанную с коллекторами первого 5 и второго 6 выходных транзисторов, предусмотрены новые элементы и связи - в качестве вспомогательного прямосмещенного p-n перехода 12 используется эмиттерный p-n переход дополнительного транзистора 18, коллектор которого связан с шиной 19 источника питания.

Схема усилителя-прототипа представлена на чертеже фиг.1. На чертеже фиг.2 показано заявляемое устройство в соответствии с формулой изобретения.

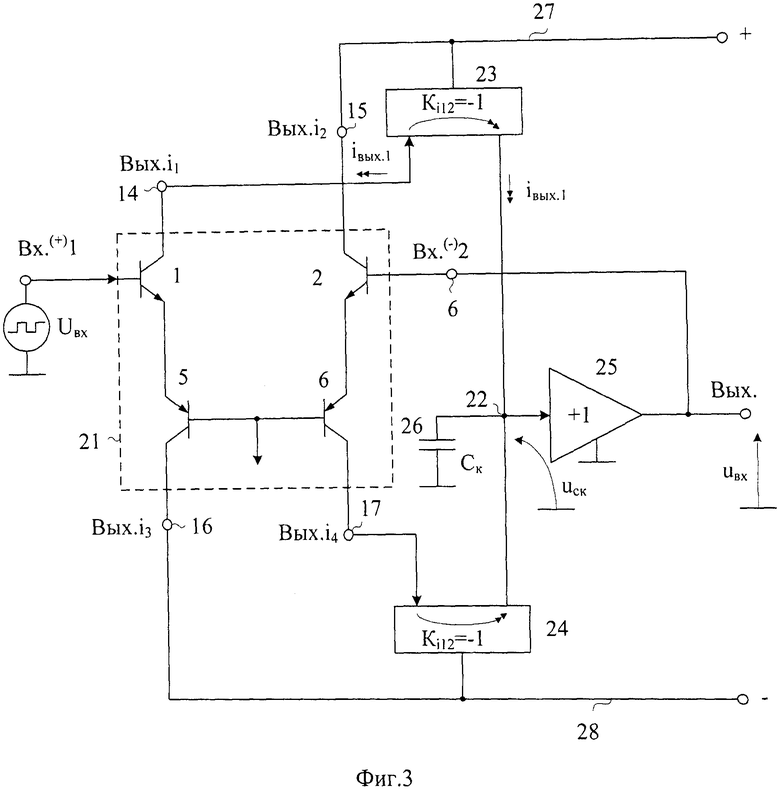

На чертеже фиг.3 показана типовая архитектура быстродействующего операционного усилителя.

На чертеже фиг.4 показана схема ДУ-прототипа в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар».

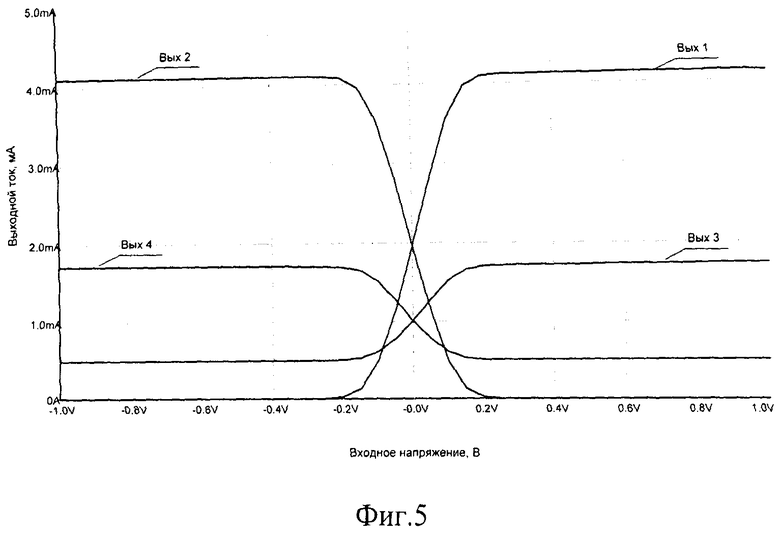

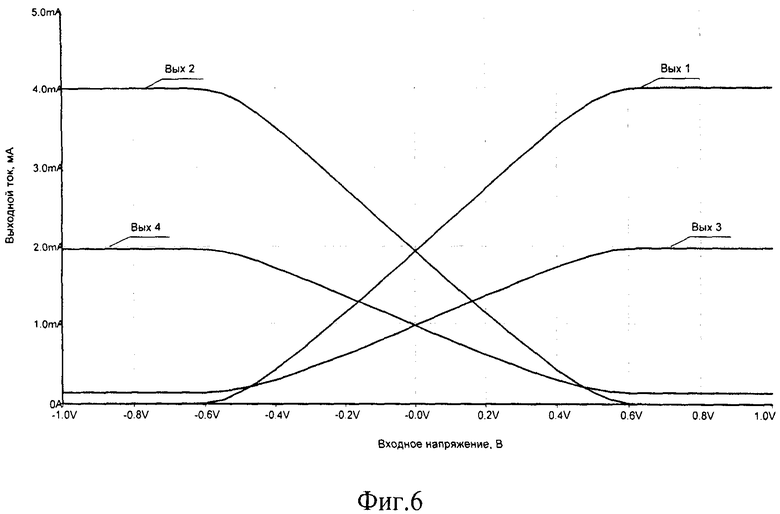

На чертеже фиг.5 - фиг.6 приведены зависимости выходных токов ДУ фиг.4 от входного напряжения при различных значениях сопротивлений резистора Ri Ri=R8=R9=R10=20 Ом - фиг.5 и Ri=200 Ом - фиг.6.

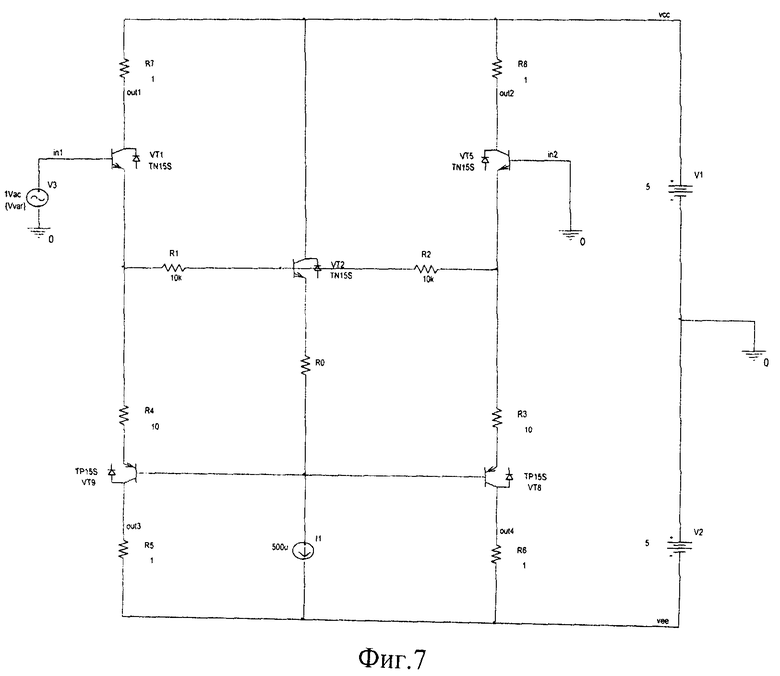

На чертеже фиг.7 показана схема заявляемого ДУ фиг.2 в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар».

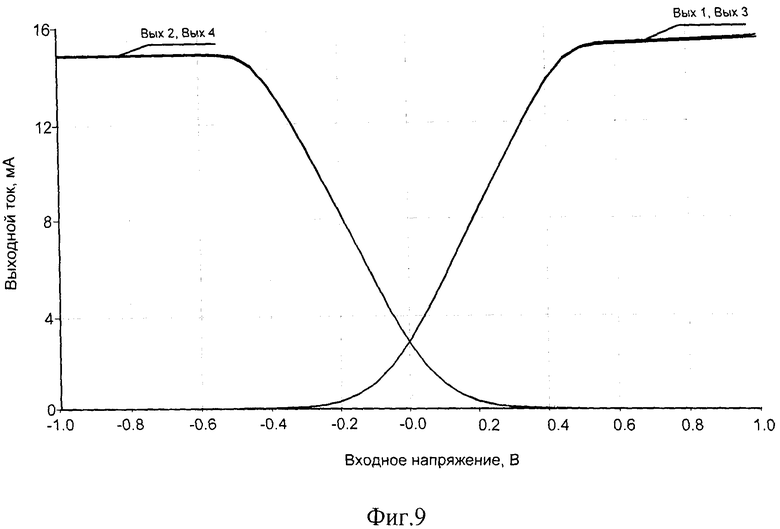

На чертежах фиг.8 - фиг.9 приведены зависимости выходных токов от входного напряжения ДУ фиг.7 при различных значениях сопротивлений R0 согласующего резистора 20, включенного в эмиттер транзистора 18.

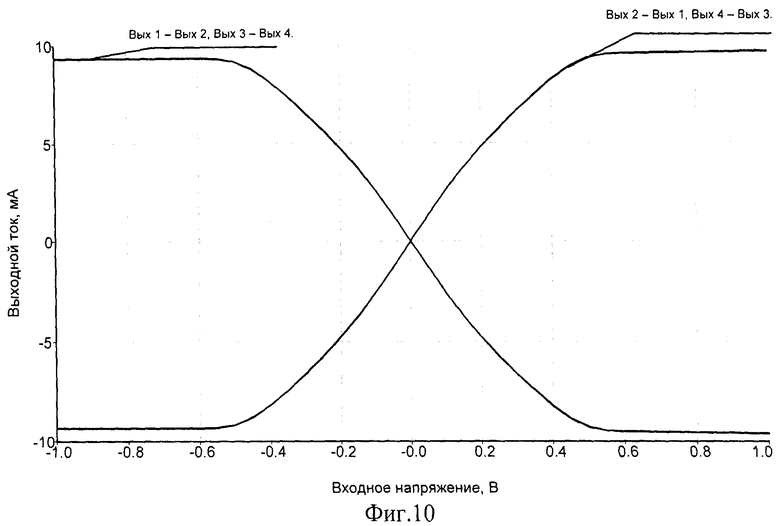

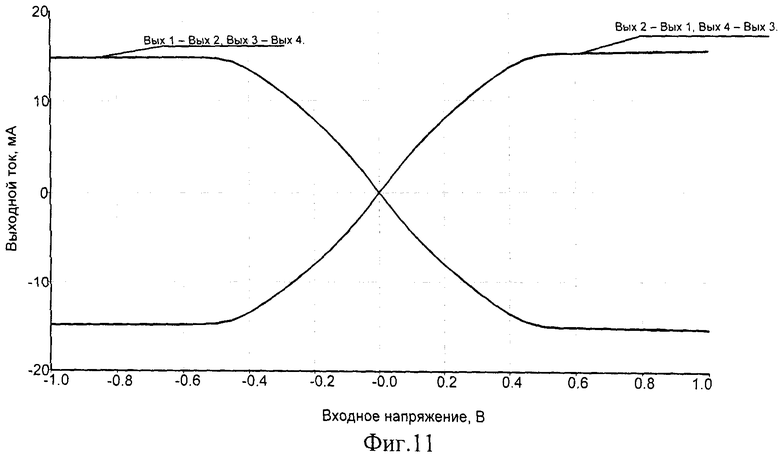

На чертежах фиг.10 - фиг.11 приведены зависимости разностей выходных токов ДУ от входного напряжения uвх ДУ фиг.7 при различных значениях сопротивлений R0 согласующего резистора 20.

Комлементарный дифференциальный усилитель с расширенным диапазоном активной работы фиг.2 содержит первый 1 и второй 2 входные транзисторы, базы которых являются соответствующими входами 3, 4 устройства, первый 5 и второй 6 выходные транзисторы, базы которых соединены с источником опорного тока 7, первый 8 и второй 9 токоограничивающие резисторы, включенные между эмиттерами соответствующих первого 1 входного и первого 5 выходного транзисторов, а также второго 2 входного и второго 6 выходного транзисторов, первый 10 и второй 11 последовательно соединенные вспомогательные резисторы, включенные между эмиттерами первого 1 и второго 2 входных транзисторов, вспомогательный прямосмещенный p-n переход 12, включенный между базами первого 5 и второго 6 выходных транзисторов и общим узлом 13 последовательно соединенных первого 10 и второго 11 вспомогательных резисторов, первую группу противофазных токовых выходов (14, 15), связанную с коллекторами первого 1 и второго 2 входных транзисторов, вторую группу противофазных токовых выходов (16, 17), связанную с коллекторами первого 5 и второго 6 выходных транзисторов. В качестве вспомогательного прямосмещенного p-n перехода 12 используется эмиттерный p-n переход дополнительного транзистора 18, коллектор которого связан с шиной 19 источника питания.

На чертеже фиг.3 заявляемый дифференциальный усилитель фиг.2 (21) включен в классическую структуру быстродействующего ОУ с высокоимпедансным узлом 22, которая содержит дополнительные токовые зеркала 23, 24, выходной буфер 25 и корректирующий конденсатор (Cк) 26. При этом ОУ охвачен 100% отрицательной обратной связью. Его электропитание обеспечивается источниками 27 и 28.

На чертеже фиг.2, в соответствии с п.2 формулы изобретения, последовательно с эмиттерным p-n переходом дополнительного транзистора 18 включен согласующий резистор 20.

Рассмотрим вначале работу известного устройства фиг.1.

Статические токи всех транзисторов схемы определяются током I7 токостабилизирущего двухполюсников 7. При этом, для достаточно низкоомных резисторов 8, 10, 11, 9 (R8=R10=R11=R9=R=10-15 Ом) за счет увеличения площадей эмиттерных переходов транзисторов 5, 6 можно при нулевом входном напряжении ДУ (Uвх=0) обеспечить равенство всех эмиттерных токов схемы:

где 2I0=I7 - некоторый опорный ток, например 1 мА.

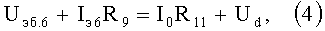

На основании уравнений Кирхгофа при Uвх=0 можно записать следующие уравнения

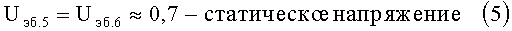

Ud=UAB=0,7 B - напряжение на двухполюснике 12 (вспомогательном прямосмещенном p-n переходе),

эмиттер-база транзисторов 5 и 6.

Таким образом, эмиттерные токи выходных транзисторов 5, 6 при Uвх=0

а эмиттерные токи входных транзисторов 1 и 2:

Для приращений тока через R10 и R11, вызванных изменениями входного напряжения, можно записать

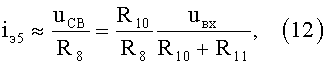

Поэтому приращение напряжения uCB между узлами «С» и «В», «открывающего» транзистор VT5

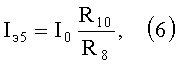

Как следствие, приращение эмиттерного тока iэ5 выходного транзистора 5 и его суммарный эмиттерный ток iэ5(t)

Аналогично для эмиттерного тока выходного транзистора 6

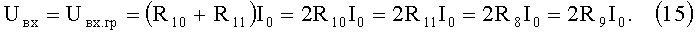

Транзистор 6 полностью «закроется», если iэ6(t)≈0, то есть при

Учитывая, что R8 и R9, существенно влияющие на крутизну Sвх проходной характеристики ДУ iвых=f(uвх), не могут выбираться большими, из (15) следует, что при фиксированной крутизне Sвх рассматриваемая схема фиг.1 не может обеспечить пропорциональность выходных токов от uвх в широком диапазоне изменений uвх, причем крутизна

где

Iк5.max=Iк6.max=2I0, Iк1.max=Iк2.max=4I0. Следовательно, ДУ фиг.1 работает в режиме класса «А», для которого выходные токи жестко связаны с суммарным статическим током, потребляемым ДУ от источника питания. В этом состоит один из существенных недостатков ДУ-прототипа.

Рассмотрим далее схему заявляемого ДУ фиг.2.

Статический режим транзисторов схемы фиг.2 при R10=R11≤1 кОм и Uвх=0, описываются следующей системой уравнений Кирхгофа:

где R0 - сопротивление резистора 20.

Если учесть, что Uэб.i≈0,7 В, то можно найти статические (Uвх=0) эмиттерные токи всех основных (1, 2, 5, 6) транзисторов схемы

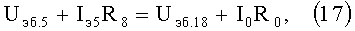

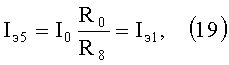

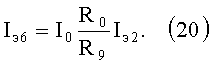

Будем в дальнейшем считать, например, что R0=R8=R9=10÷20 Ом. Если на вход Вх.1 подается положительное напряжение uвх, то ток через резисторы 10÷11 получает приращение iR, которое создает на резисторе 10 «отпирающее» транзистор 5, а на резисторе 11 «запирающее» транзистор 6 напряжения, которые вызывают соответствующие изменения коллекторных токов этих транзисторов. Так для левой части схемы ДУ фиг.2

При этом транзисторы 6 и 2 «подзапираются», так как их коллекторные токи уменьшаются на величину

Полное запирание транзисторов 2, 6 (Iк3=0, Iк6=0) произойдет при входном граничном напряжении

Таким образом при uвх=Uгр максимальные выходные токи ДУ достигнут значений

если R8=R9=10 ОМ, то iк1.max=iк5.max≈70 мА.

Практические значения iк1.max=iк5.max (фиг.9) отличаются от расчетных по формуле (24) из-за влияния сопротивлений резисторов 10, 11 и коэффициента усиления по току базы β18 транзистора 18 на работу схемы. Кроме этого при более точных расчетах следует учесть, что фактическое запирание транзисторов 5 (6) происходит не при Uэб=0, а при Uэб≈0,5 В. Как следствие, при R10=R11=1 кОм максимальные токи iк1.max, iк5.max несколько меньше расчетных по формуле (24).

Таким образом, ДУ фиг.2 работает как каскад класса «В» - его максимальные выходные токи существенно превышают статические токи транзисторов, что, наряду с более высоким значением Uгр, является его существенным достоинством.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.786.362

2. Патент США №4.030.044

3. Патент США №4.059.808, фиг.5

4. Патент США №4.286.227

5. Авт.свид. СССР №375754, H03f 3/38

6. Авт.свид. СССР №843164, H03f 3/30

7. Патент США №3.660.773

8. Патент США №4.560.948

9. Патент РФ №2930041, H03f 1/32

10. Патент Японии №57-5364, H03f 3/343

11. Патент ЧССР №134845, кл. 21а2 18/08

12. Патент ЧССР №134849, кл. 21а2 18/08

13. Патент ЧССР №135326, кл. 21а2 18/08

14. Патент США №4.389.579

15. Патент Англии №1543361, Н3Т

16. Патент США №5.521.552 (фиг.3а)

17. Патент США №4.059.808

18. Патент США №5.789.949

19. Патент США №4.453.134

20. Патент США №4.760.286

21. Авт.свид. СССР №1283946

22. Патент РФ №2019019

23. Патент США №4.389.579

24. Патент США №4.453.092

25. Патент США №3.566.289

26. Патент США №4.059.808 (фиг.2)

27. Патент США №3.649.926

28. Патент США №4.714.894 (фиг.1)

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

31. Операционные усилители с непосредственной связью каскадов [Текст] / В.И. Анисимов, М.В. Капитонов, Н.Н. Прокопенко, Ю.М. Соколов. - Л., 1979. - 148 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

| КОМПЛЕМЕНТАРНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2510570C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2504896C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НУЛЕВЫМ УРОВНЕМ ВЫХОДНЫХ СТАТИЧЕСКИХ НАПРЯЖЕНИЙ | 2012 |

|

RU2488954C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2421887C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМИ ВХОДНЫМИ ТРАНЗИСТОРАМИ | 2010 |

|

RU2423779C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2005 |

|

RU2292635C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2005 |

|

RU2282303C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2007 |

|

RU2346382C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319296C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном. Техническим результатом является расширение диапазона активной работы входного каскада операционного усилителя для дифференциального сигнала, а также получение граничных напряжений его проходной характеристики iвых=f(uвх) на уровне Uгр=0.4÷0,8 В. Комлементарный дифференциальный усилитель с расширенным диапазоном активной работы содержит первый (1) и второй (2) входные транзисторы, входы (3), (4) устройства, первый (5) и второй (6) выходные транзисторы, источник опорного тока (7), первый (8) и второй (9) токоограничивающие резисторы, первый (10) и второй (11) последовательно соединенные вспомогательные резисторы, вспомогательный прямосмещенный p-n переход (12), общий узел (13), первую группу противофазных токовых выходов (14, 15), вторую группу противофазных токовых выходов (16, 17), эмиттерный p-n переход дополнительного транзистора (18), шину (19) источника питания. 1 з.п. ф-лы, 11 ил.

1. Комлементарный дифференциальный усилитель с расширенным диапазоном активной работы, содержащий первый (1) и второй (2) входные транзисторы, базы которых являются соответствующими входами (3), (4) устройства, первый (5) и второй (6) выходные транзисторы, базы которых соединены с источником опорного тока (7), первый (8) и второй (9) токоограничивающие резисторы, включенные между эмиттерами соответствующих первого (1) входного и первого (5) выходного транзисторов, а также второго (2) входного и второго (6) выходного транзисторов, первый (10) и второй (11) последовательно соединенные вспомогательные резисторы, включенные между эмиттерами первого (1) и второго (2) входных транзисторов, вспомогательный прямосмещенный p-n переход (12), включенный между базами первого (5) и второго (6) выходных транзисторов и общим узлом (13) последовательно соединенных первого (10) и второго (11) вспомогательных резисторов, первую группу противофазных токовых выходов (14, 15), связанную с коллекторами первого (1) и второго (2) входных транзисторов, вторую группу противофазных токовых выходов (16, 17), связанную с коллекторами первого (5) и второго (6) выходных транзисторов, отличающийся тем, что в качестве вспомогательного прямосмещенного p-n перехода (12) используется эмиттерный p-n переход дополнительного транзистора (18), коллектор которого связан с шиной (19) источника питания.

2. Комлементарный дифференциальный усилитель с расширенным диапазоном активной работы по п.1, отличающийся тем, что последовательно с эмиттерным p-n переходом дополнительного транзистора (18) включен согласующий резистор (20).

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384938C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| US 6531920 B1, 11.03.2003 | |||

| US 20040145414 A1, 29.07.2004 | |||

Авторы

Даты

2014-06-10—Публикация

2012-11-01—Подача