УРОВЕНЬ ТЕХНИКИ

Область техники, к которой относится изобретение

Настоящее изобретение относится к системе обработки, имеющей совместно используемую память, в частности к способу и устройству для очистки семафорных резервирований.

Уровень техники

Компьютеры революционизировали электронную промышленность предоставлением возможности выполнения сложных задач обработки всего несколькими нажатиями клавиш. Упомянутые сложные задачи используют невероятно большое число комплексных компонентов, которые обмениваются между собой информацией быстрым и эффективным способом с использованием шины. Шина является каналом или трактом между компонентами в компьютере.

Многие шины, присутствующие в компьютере, традиционно выполнялись как общие шины. Общая шина обеспечивает средство для информационного обмена множества компонентов по общему тракту или каналу. В последние годы технологию общих шин заменили в большой степени двухточечными коммутационными соединениями. Двухточечные коммутационные соединения обеспечивают прямое соединение между двумя компонентами на шине, когда они обмениваются информацией между собой. Чтобы несколько компонентов могли одновременно обмениваться информацией, можно применить несколько непосредственных линий связи. Для управления обменом по шине можно использовать арбитр шины.

Компьютер, реализующий шинную архитектуру, может содержать несколько обрабатывающих компонентов, подсоединенных к памяти. Память может быть разделена на области либо системным разработчиком, либо динамически во время работы. Каждый обрабатывающий компонент может иметь собственную специализированную область памяти. «Совместно используемые области памяти», с другой стороны, являются областями, к которым можно получать доступ при множественной обработке. Для управления доступом к совместно используемым областям памяти можно применить семафор. «Семафор» представляет собой аппаратный или программный флаг, постоянно находящийся в ячейке совместно используемой памяти, который указывает на доступность совместно используемого ресурса. Обрабатывающий компонент, который нуждается в доступе к совместно используемой области памяти, может считывать семафор для определения доступности совместно используемой области памяти. Если семафор указывает, что совместно используемая область памяти доступна, то обрабатывающий компонент может установить семафор на указание, что совместно используемая область памяти заблокирована, и продолжить поиск доступа к памяти.

Когда обрабатывающий компонент считывает семафор, память создает «резервирование» совместно используемой области памяти для обрабатывающего компонента. Резервирование очищается после того, как обрабатывающий компонент устанавливает семафор на блокирование совместно используемой области памяти. Однако, если процессор прерывают прежде, чем получает возможность установить семафор, резервирование должно быть очищено. Существует потребность в эффективном средстве для очистки резервирования семафоров.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Предлагается способ очистки резервирования семафоров для монопольного доступа к совместно используемой памяти. Способ содержит этапы, заключающиеся в том, что передается запрос записи в область памяти семафора, связанную с совместно используемой памятью, и запрещается обновление содержимого области памяти семафора в ответ на запрос записи.

Предлагается система обработки. Система обработки содержит множество обрабатывающих компонентов, память, содержащую совместно используемую область памяти, которая может быть совместно используемой обрабатывающими компонентами, и семафорную область памяти, которая указывает доступность участка совместно используемой памяти для монопольного доступа для записи, и контроллер, который поддерживает состояние семафорного резервирования, при этом резервированное состояние упомянутого контроллера очищается в ответ на запрос записи в семафорную область памяти из одного из обрабатывающих компонентов, без записи данных в семафорную область памяти.

Предлагается другая система обработки. Система обработки содержит множество обрабатывающих компонентов, память, содержащую совместно используемую область памяти, которая может быть совместно используемой упомянутым множеством обрабатывающих компонентов, и семафорную область памяти, которая указывает доступность участка совместно используемой памяти для монопольного доступа для записи, и контроллер, который поддерживает состояние семафорного резервирования, при этом каждый из обрабатывающих компонентов выполнен с возможностью передачи запроса записи в семафорную область памяти, который очищает резервированное состояние семафора без записи в семафорную область памяти.

Вышеописанный способ обеспечивает такие преимущества, что семафорное резервирование можно очищать без занятия дополнительной памяти и исключает этапы получения доступа к памяти. Дополнительные преимущества настоящего изобретения станут очевидными специалистам в данной области техники из нижеследующего подробного описания, в котором представлен и поясняется только предпочтительный вариант осуществления, просто для демонстрации предполагаемого наилучшего варианта осуществления изобретения. Как можно представить, изобретение допускает другие и отличающиеся варианты осуществления, и ряд его частей допускает модификации в разных очевидных отношениях, во всех случаях, без отступления от изобретения. Соответственно чертежи и описание следует считать иллюстративными по характеру, а не ограничительными.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Настоящее изобретение поясняется для примера, а не в порядке ограничения, на фигурах прилагаемых чертежей, на которых одинаковые числовые позиции обозначают одинаковые элементы и на которых:

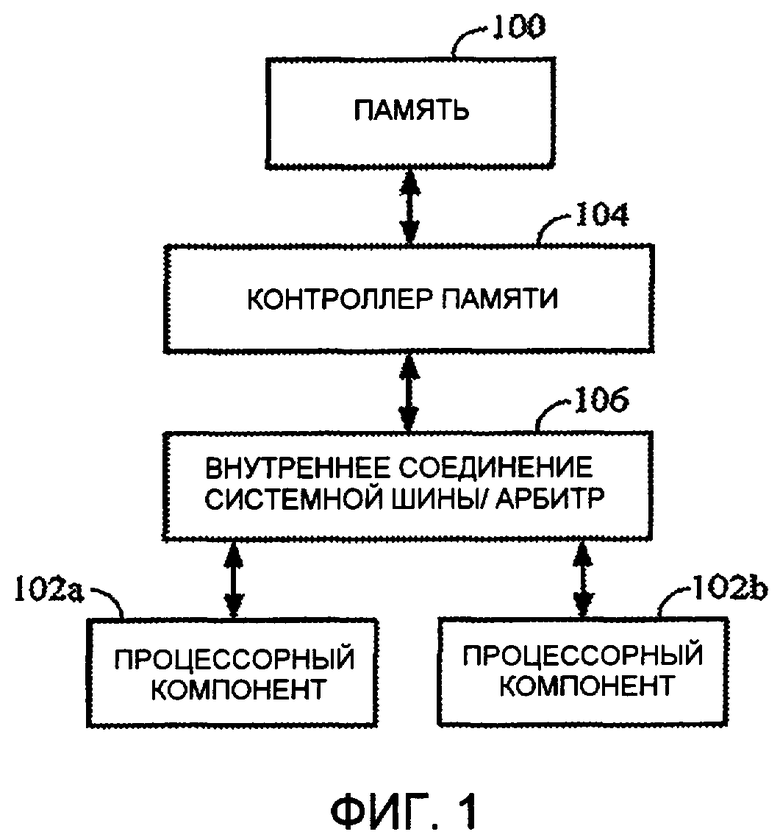

фиг.1 - функциональная блок-схема, поясняющая пример системы обработки;

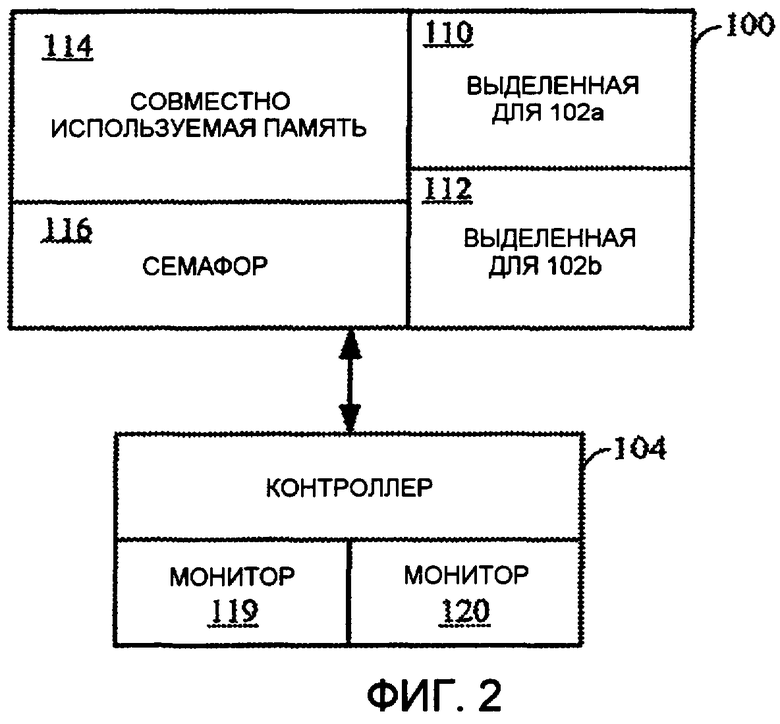

фиг.2 - более подробная частичная блок-схема элементов системы обработки;

фиг.3 - блок-схема последовательности операций, поясняющая работу систему обработки.

ПОДРОБНОЕ ОПИСАНИЕ

Фиг.1 является функциональной блок-схемой, поясняющей пример системы обработки. Система обработки может быть компьютером или резидентной частью компьютера и обладать способностью обработки, поиска и хранения информации. Система обработки может быть автономной системой или встроенной в устройство, например, проводной или беспроводной телефон, электронный секретарь (PDA), портативный компьютер, настольный компьютер (PC), пейджер, модем, игровую консоль, цифровую камеру, аппаратуру для видеоконференций, вещательную аппаратуру или любое другое подходящее устройство, которое нуждается в возможности обработки данных. Память 100 связана с, по меньшей мере, одним обрабатывающим (процессорным) компонентом 102a и 102b через контроллер 104 памяти и внутреннее соединение системной шины и арбитр 106 шины. Каждый процессорный компонент может быть ведущим компонентом шины любого типа, включая, например, микропроцессор, цифровой процессор сигналов (DSP), мост, программируемую логику, дискретную вентильную или транзисторную логику или любой другой компонент для обработки информации. Для простоты пояснения показано только два процессорных компонента, однако, можно применять большее число компонентов.

Память может быть разделена на области либо системным разработчиком, либо динамически во время работы. Область памяти может быть специально выделена каждому процессорному компоненту тогда, как другие области памяти могут быть совместно используемыми несколькими процессорными компонентами. Термин «область памяти» относится к любому запоминающему устройству, любому участку запоминающего устройства, области схемы распределения памяти или чему-то подобному. Совместно используемый запоминающий ресурс может быть подчиненным компонентом шины любого типа, включая, например, регистр, память, мост или любой компонент, способный к поиску и хранения информация.

Обычно, арбитр шины связан с шиной для управления доступом к памяти эффективным способом. Например, процессорный компонент 102a, осуществляющий поиск доступа к совместно используемой области памяти, может передавать запрос считывания или записи в арбитр шины по шине. Затем арбитр шины может предоставить запрашивающему процессорному компоненту 102a доступ совместно используемой области памяти для выполнения операции считывания или записи. В случае, если несколько запросов считывания и/или записи от, по меньшей мере, одного процессорного компонента конкурируют в арбитре шины, то тогда арбитр шины может определить последовательность, в которой будут выполнены операции считывания и/или записи, и динамически настроить конфигурацию внутреннего соединения шины соответственно схеме управления доступом к шине. Схема управления доступом к шине может изменяться в зависимости от конкретного приложения и общих проектных ограничений. Доступ к памяти может учитывать баланс между критериями приоритетности и соображениями равноправного распределения.

Процессор может передавать запрос считывания выставлением адреса на адресную шину. Запрос записи можно производить аналогичным образом, с дополнением данными, передаваемыми на шину данных. Адресная шина и шина данных могут быть отдельными шинами или одной шиной с временным разделением доступа. Для подачи соответствующих управляющих сигналов в контроллер 104 памяти можно применить передачу сигналов на боковой полосе частот. В альтернативном варианте управляющие сигналы можно мультиплексировать с адресами и данными либо на раздельных шинах, либо на одной шине с временным разделением доступа. Управляющие сигналы могут содержать, например, строб считывания/записи, монопольной или немонопольной операции, сигнал длины полезной информации и, в случае, операции записи, разрешения байтов записи. «Разрешения байтов записи» можно применять для указания байтовых трактов на шине, которые будут служить для передачи данных для операции записи. Например, передача 2-байтовой полезной информации по 32-разрядной шине данных может использовать 2 из 4 байтовых трактов. Разрешения байтов записи могут служить для указания контроллеру памяти, какой из 2 байтовых трактов на шине памяти будет применяться для передачи полезной информации.

Приложения обработки часто требуют монопольного доступа для записи в совместно используемую область памяти во время непрерываемой последовательности операций. Система обработки должна обеспечивать соответствующее управление доступом к памяти процессорам, которые нуждаются в таком монопольном доступе. На фиг.2 представлена более подробная блок-схема памяти 100 и контроллера 104 памяти. Возможностью монопольного доступа к совместно используемой памяти управляет «семафорная» операция. Память 100 поделена на области. Области 110 и 112 памяти соответственно выделены процессорам 102a и 102b. Область 114 памяти является областью памяти, которую совместно используют множество процессоров. Если соответствует конкретному применению системы, упомянутая область может быть дополнительно разделена на участки, каждый из которых является совместно используемым конкретными процессорами мультипроцессорной системы. Область 116 выделена для хранения семафора.

Контроллер 104 памяти содержит мониторы 119 и 120 конечных автоматов монопольного доступа. Монитор 119 является монитором монопольного доступа, связанным с процессором 102a, для контроля и управления операциями монопольного доступа данного процессора к совместно используемой памяти 114. Монитор 120 является монитором монопольного доступа, связанным с процессором 102b.

Как пояснялось ранее в описании в разделе уровня техники, семафор представляет собой флаг, постоянно находящийся в семафорной области 116 памяти, и характеризует доступность или недоступность ресурса 114 совместно используемой памяти. Процессорный компонент, который ведет поиск монопольного доступа к совместно используемой области памяти, может считывать семафорную область памяти посредством ассоциированного монитора контроллера памяти для определения доступности совместно используемой области памяти или участка области памяти. Если семафор указывает, что совместно используемая область памяти доступна для доступа, то контроллер памяти может установить флаг в семафорной области для указания, что совместно используемая область памяти «заблокирована», и продолжить поиск доступа к памяти для записи в совместно используемой 114 области памяти соответствующим процессором. Во время блокированного состояния семафора никакой другой процессорный компонент не способен получить доступ к совместно используемой памяти. По окончании операции обработки флаг удаляется контроллером памяти, и семафор возвращается в незаблокированное состояние, указывающее на доступность.

Схему семафорного резервирования обычно задействуют для управления монопольным доступом к совместно используемой памяти. В качестве предварительного условия получения монопольного доступа к записи в совместно используемую память должно быть создано резервирование для запрашивающего процессора в соответствующем ему мониторе контроллера памяти. Контроллер устанавливает резервированное состояние, когда происходит операция считывания семафора. Например, последовательность командных кодов может потребовать монопольного доступа для процессора 102a для записи в ячейки в совместно используемой 114 области памяти. Для выполнения монопольного запроса записи процессором сначала должен быть считан семафор для определения, может ли доступ к области 114 быть получен процессором 102a. Операция считывания семафора инициирует установку контроллером резервированного состояния для процессора 102a в мониторе 119.

Если совместно используемая область памяти не заблокирована, процессор 102a может получить доступ немедленно или подождать последующего кода в кодовой последовательности. Процессор 102b может также установить резервированное состояние в мониторе 120, если семафор не заблокирован. Если оба процессора одновременно имеют состояние резервирования, то первый процессор, запрос которого выигрывает арбитраж к контроллеру памяти, получит монопольный доступ к совместно используемой области памяти.

После получения доступа к области 114 семафорный флаг устанавливается, и процессор 102a получает монопольный доступ. В ответ на команду монопольной записи монитор 119 активизирует контроллер для очистки резервированного состояния, сохраненного в мониторе 119, а также любого резервирования для того же самого адреса, который может быть сохранен в мониторе 120. Заблокированное состояние семафора деблокируется, когда процессор, который владеет блокировкой, записывает в семафорную ячейку, указывающую, что семафор больше не заблокирован.

После установки резервирования процессор 102a может быть прерван в ходе выполнения кодовой последовательности, или кодовая последовательность может быть заменена до того, как выполнена операция записи в совместно используемую область памяти. Если доступ к совместно используемой памяти не получен ни одним из процессоров, то резервирование не будет очищаться. Поскольку монитор контроллера памяти не способен различать, связано ли резервирование с более ранней или поздней кодовой последовательностью, протокол требует, чтобы устаревшее резервирование очищалось прежде, чем может быть получено новое резервирование для последующего монопольного доступа к записи. Следовательно, если ни одна монопольная операция записи при резервировании не должна исполняться, то следует принять меры к очистке резервирования.

В, по меньшей мере, одном варианте осуществления системы обработки семафорное резервирование можно очищать передачей (вещанием) запроса записи в семафорной области 116 памяти, но одновременно запрещением процессору выполнять запись в семафорную область 116 памяти. Это можно обеспечить множеством различных способов. Например, разрешения байтов записи можно использовать для блокировки всех байтовых трактов на шине данных во время запроса процессора на запись в семафорную область 116 памяти. В результате, резервирование для процессора очищается, но семафорная область 116 памяти не обновляется и таким образом остается деблокированной для использования другим процессором.

Операция очистки семафора показана на блок-схеме последовательности операций на фиг.3. На этапе S20 процессор 102a инициирует обработку кодовой последовательности. На этапе S22 выполняется определение, запрошена ли процессором операция монопольной записи по адресу совместно используемой памяти. Если не запрошена, обработка продолжается, пока обработка кодовой последовательности не заканчивается. Если на этапе S22 определяется, что монопольная запись запрошена, то процессор выдает команду считывания на этапе S24 в адрес семафора. Упомянутая команда устанавливает резервирование в мониторе 119 контроллера памяти, который связан с процессором 102a.

На этапе S26 считывается адрес семафора и выполняется определение, доступен ли монопольный доступ к совместно используемой области памяти. Если не доступен, то резервирование очищается на этапе S28, и процесс обработки возвращается на этап S20 для продолжения обработки кодовой цепочки. Если семафор не указывает на заблокированное состояние, то на этапе S28(a) выполняется определение, прекращена ли кодовая последовательность, связанная с резервированием. Если кодовая последовательность еще должна обрабатываться, то процессором 102a выдается команда монопольной записи. Контроллер 104 памяти, осведомленный о состоянии резервирования процессора 102a, установленном в мониторе 119, обеспечивает процессору доступ к совместно используемой памяти 114 на этапе S30. Контроллер памяти записывает флаг блокировки в семафорную память и очищает любые существующие семафорные резервирования. Процессор 102a продолжает исполнять кодовую последовательность при монопольном доступе к совместно используемой области памяти. На этапе S32 процессор закончил свою рабочую последовательность, и уступает монопольный доступ.Контроллер 104 памяти очищает семафорный флаг для указания, что совместно используемая память доступна до доступа. Новая кодовая последовательность может быть обработана на этапе S20.

Если на этапе S28 определяется, что кодовая последовательность прекращена, то резервирование следует очистить из контроллера памяти. На этапе S34 процессор выдает команду монопольной записи. Процессор устанавливает разрешения байтов записи для блокировки всех байтовых трактов на шине данных. В ответ на команду записи контроллер памяти очищает резервированное состояние в мониторе 119 и, поскольку разрешенных байтовых трактов не существует, не записывает в семафорную область памяти. На этапе S20 возможна обработка новой кодовой последовательности.

Различные пояснительные логические блоки, модули, схемы, элементы и/или компоненты, описанные в связи с вариантами осуществления, описанными в настоящей заявке, могут быть реализованы или выполнены с помощью универсального процессора, процессора цифровых сигналов (DSP), специализированной интегральной схемы (ASIC), программируемой вентильной матрицы (FPGA) или другого программируемого логического компонента, дискретной вентильной или транзисторной логики, дискретных аппаратных компонентов или любой их комбинации, предназначенной для выполнения функций, описанных в настоящей заявке. Универсальный процессор может быть микропроцессором, но, в альтернативном варианте, процессор может быть любым обычным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор может быть также реализован в виде комбинации вычислительных компонентов, например комбинации DSP и микропроцессора, множества микропроцессоров, по меньшей мере, одного микропроцессора в связи с ядром DSP или в виде любой другой подобной конфигурации.

Способы или алгоритмы, описанные в связи с вариантами осуществления, предложенными в настоящей заявке, могут быть осуществлены непосредственно в аппаратном обеспечении, в программном модуле, исполняемом процессором, или в комбинации того и другого. Программный модуль может постоянно находиться в памяти RAM (оперативной памяти), флэш-памяти, памяти ROM (постоянной памяти), памяти EPROM (стираемой программируемой постоянной памяти), памяти EEPROM (электронно-перепрограммируемой постоянной памяти), регистрах, на жестком диске, сменном диске, CD-ROM (компакт-диске) или носителе информации любого другого типа, известном в данной области техники. Носитель информации может быть связан с процессором так, что процессор может считывать информацию на носителе информации и записывать информацию на него. В альтернативном варианте носитель информации может быть неотъемлемой частью процессора.

Вышеприведенное описание предложенных вариантов осуществления дано для того, чтобы любой специалист в данной области техники смог реализовать или применить настоящее изобретение. Специалистам в данной области техники будут очевидны различные модификации данных вариантов осуществления, и общие принципы, изложенные в настоящей заявке, можно применить к другим вариантам осуществления, не выходящим за пределы существа или объема изобретения. Следовательно, настоящее изобретение не подлежит ограничению вариантами осуществления, представленными в настоящей заявке, но должно соответствовать полному объему притязаний формулы изобретения, при этом ссылка на элемент в единственном числе не подразумевает смысла «один и только один», если нет специального такого указания, а означает «один или более». Все конструктивные и функциональные эквиваленты элементов разных вариантов осуществления, описанных в настоящей заявке, которые известны или в будущем станут известны специалистам со средним уровнем компетентности в данной области техники, в прямой форме включены в настоящую заявку путем отсылки и предполагают их охват формулой изобретения. Кроме того, ничего из раскрытого в настоящей заявке не предназначено для передачи в общее достояние, независимо от явного изложения упомянутого раскрытия в формуле изобретения. Ни один признак формулы изобретения не подлежит толкованию согласно положений шестого пункта, § 112 раздела 35 Кодекса законов США, если признак прямо не изложен с использованием формулировки «средство для», или, в случае пункта формулы изобретения на способ, признак не изложен с использованием формулировки «этап для».

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

| ПРЕОБРАЗОВАНИЕ ИНИЦИИРУЕМОГО СООБЩЕНИЯМИ ПРЕРЫВАНИЯ В УВЕДОМЛЕНИЕ О ГЕНЕРИРОВАННОМ АДАПТЕРОМ ВВОДА-ВЫВОДА СОБЫТИИ | 2010 |

|

RU2546561C2 |

| КОМАНДЫ СОХРАНЕНИЯ/СОХРАНЕНИЯ БЛОКА ДАННЫХ ДЛЯ СВЯЗИ С АДАПТЕРАМИ | 2010 |

|

RU2522314C1 |

| АКТИВАЦИЯ/ДЕАКТИВАЦИЯ АДАПТЕРОВ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2010 |

|

RU2562372C2 |

| ОПРЕДЕЛЕНИЕ ФОРМАТОВ ТРАНСЛЯЦИИ ДЛЯ ФУНКЦИЙ АДАПТЕРА ВО ВРЕМЯ ВЫПОЛНЕНИЯ | 2010 |

|

RU2556418C2 |

| ПРИНУДИТЕЛЬНОЕ ПРИМЕНЕНИЕ СТРОГО УПОРЯДОЧЕННЫХ ЗАПРОСОВ В СИСТЕМЕ СЛАБО УПОРЯДОЧЕННОЙ ОБРАБОТКИ | 2006 |

|

RU2405194C2 |

| ИЗМЕРИТЕЛЬНОЕ СРЕДСТВО ДЛЯ ФУНКЦИЙ АДАПТЕРА | 2010 |

|

RU2523194C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПРИОСТАНОВКИ ИСПОЛНЕНИЯ ПОТОКА ДО МОМЕНТА ОСУЩЕСТВЛЕНИЯ ОПРЕДЕЛЕННОГО ДОСТУПА К ПАМЯТИ | 2002 |

|

RU2308754C2 |

| УПРАВЛЕНИЕ СКОРОСТЬЮ, С КОТОРОЙ ОБРАБАТЫВАЮТСЯ ЗАПРОСЫ НА ПРЕРЫВАНИЕ, ФОРМИРУЕМЫЕ АДАПТЕРАМИ | 2010 |

|

RU2526287C2 |

| АРХИТЕКТУРА ПРОЦЕССОРА ВВОДА-ВЫВОДА, КОТОРЫЙ ОБЪЕДИНЯЕТ МОСТ МЕЖСОЕДИНЕНИЯ ПЕРВИЧНЫХ КОМПОНЕНТ | 1996 |

|

RU2157000C2 |

Изобретение относится к системе обработки, имеющей совместно используемую память, в частности к способу и устройству для очистки семафорных резервирований. Технический результат заключается в повышении быстродействия системы. Работа семафора (116) управляет монопольным доступом к памяти (114), которая совместно используется множеством процессорных элементов. Состояние семафорного резервирования для монопольного доступа процессорного элемента (102а), (102b) контролируется контроллером памяти. Для очистки устаревшего состояния резервирования передается командный сигнал для операции записи в память при одновременном блокировании обновления содержимого памяти. Состояние резервирования в контроллере (104) изменяется из состояния резервирования в состояние нерезервирования в ответ на прием командного сигнала. 3 н. и 14 з.п. ф-лы, 3 ил.

1. Способ очистки резервирования семафоров для монопольного доступа к совместно используемой памяти, при этом способ содержит следующие этапы: устанавливается семафорное резервирование в ответ на считывание первым процессорным компонентом области памяти семафора в совместно используемой памяти; передается запрос записи в область памяти семафора, связанную с совместно используемой памятью из второго процессорного компонента; и очищается резервирование семафора и запрещается обновление содержимого области памяти семафора первым процессорным компонентом в ответ на запрос записи.

2. Способ по п.1, в котором запрос записи передается с управляющим сигналом, который запрещает обновление области памяти семафора.

3. Способ по п.2, в котором управляющий сигнал содержит разрешения байтов записи.

4. Способ по п.3, в котором обеспечена шина данных для передачи данных по множеству байтовых трактов в совместно используемую память и при этом содержимое области памяти семафора заблокировано от обновления, по меньшей мере, одним процессорным компонентом посредством установки разрешений байтов записи на блокирование всех байтовых трактов на шине данных.

5. Способ по п.1, дополнительно содержащий этап, заключающийся в том, что состояние резервирования в контроллере изменяется из состояния резервирования в состояние нерезервирования в ответ на запрос записи.

6. Способ по п.5, в котором упомянутое состояние резервирования связано с конкретным процессорным компонентом из множества процессорных компонентов и упомянутый запрос записи передается из упомянутого конкретного процессорного компонента.

7. Способ по п.6, в котором упомянутый контроллер содержит состояние резервирования для каждого из множества процессорных компонентов и упомянутый запрос записи вызывает изменение в состоянии резервирования контроллера только для процессорного компонента, который передал запрос записи.

8. Система обработки, содержащая: множество процессорных компонентов; память, содержащую совместно используемую область памяти, которая может быть совместно используемой множеством процессорных компонентов, и область памяти семафора, которая указывает доступность участка совместно используемой памяти для монопольного доступа для записи; и контроллер, который поддерживает состояние семафорного резервирования для, по меньшей мере, одного из множества процессорных компонентов, при этом резервированное состояние упомянутого контроллера очищается в ответ на запрос записи в область памяти семафора из другого одного из множества процессорных компонентов, без выполнения записи данных в область памяти семафора.

9. Система обработки по п.8, в которой упомянутый один из множества процессорных компонентов предотвращает запись данных в область памяти семафора во время запроса записи в область памяти семафора посредством передачи управляющего сигнала с запросом записи в контроллер.

10. Система обработки по п.9, в которой управляющий сигнал содержит разрешения байтов записи.

11. Система обработки по п.10, дополнительно содержащая шину данных между процессорами и контроллером, при этом шина данных содержит множество байтовых трактов и причем упомянутый один из процессорных компонентов предотвращает запись данных в область памяти семафора во время запроса записи в область памяти семафора посредством установки разрешений байтов записи на блокирование байтовых трактов на шине данных.

12. Система обработки по п.8, в которой упомянутый контроллер содержит состояние резервирования для каждого из множества процессорных компонентов и упомянутый запрос записи вызывает изменение в состоянии резервирования контроллера только для процессорного компонента, который передал запрос записи.

13. Система обработки, содержащая: множество процессорных компонентов; память, содержащую совместно используемую область памяти, которая может быть совместно используемой упомянутым множеством процессорных компонентов, и область памяти семафора, которая указывает доступность участка совместно используемой памяти для монопольного доступа для записи; и контроллер, который поддерживает состояние семафорного резервирования; причем каждый из процессорных компонентов выполнен с возможностью передачи запроса записи в область памяти семафора, который очищает резервированное состояние семафора другого процессорного компонента, без записи в область памяти семафора.

14. Система обработки по п.13, в которой каждый из процессорных компонентов выполнен с возможностью предотвращения записи данных в область памяти семафора во время запроса записи в область памяти семафора посредством передачи управляющего сигнала с запросом записи в контроллер.

15. Система обработки по п.14, в которой управляющий сигнал содержит разрешения байтов записи.

16. Система обработки по п.15, дополнительно содержащая шину данных между процессорами и контроллером, при этом шина данных содержит множество байтовых трактов и причем каждый из процессорных компонентов дополнительно выполнен с возможностью предотвращения записи данных в область памяти семафора во время запроса записи в область памяти семафора посредством установки разрешений байтов записи на блокирование всех байтовых трактов на шине данных.

17. Система обработки по п.14, в которой упомянутый контроллер содержит состояние резервирования для каждого из процессорных компонентов и упомянутый запрос записи вызывает изменение в состоянии резервирования контроллера только для процессорного компонента, который передал запрос записи.

| US 20040024987 A1, 05.02.2004 | |||

| US 5408629 A, 18.04.1995 | |||

| Многопроцессорная система | 1990 |

|

SU1709330A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

Авторы

Даты

2010-01-27—Публикация

2006-10-20—Подача