Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих многопроцессорных систем.

Известна многопроцессорная система, которая содержит системную память, однотипные процессорные блоки, подключенные к общей шине, блок предоставления доступа к общей шине, внешнее устройство.

Недостатком такой системы является низкая производительность.

Известна многопроцессорная система с общей шиной, содержащая процессорные блоки, арбитр шины, системную память и внешнее устройство. К арбитру шины подключены выходы Запрос шины каждого процессорного блока и выходы сигнала Занятость шины. Входы сигнала Р азрешение представления доступа к шине подключены с выхода арбитра шины к входам каждого процессорного блока.

Недостатком системы является низкая производительность из-за больших затрат времени на установку связи с внешним устройством, являющимся общим для процессоров (общим аппаратным ресурсом). Это обусловлено необходимостью при обращении к внешнему устройству предварительного захвата общей шины для чтения и установки семафора (признака занятости внешнего устройства) в системной памяти. Процессор, использующий внешнее устройство, предварительно устанавливает, семафор, захватывая для этого общую шину, а после окончания работы с внешним устройством сбрасывает семафор, захватывая для этого еще раз общую шину. Такая организация доступа к внешнему устройству необходима для исключения возможности одновременного его использования несколькими процессорами. Таким образом, каждый процессор для использования

внешнего устройства должен прежде проверить семафор в режиме захвата шины. Если внешнее устройство занято, то ожидающие доступа к нему процессоры должны многократно повторять попытки занять внешнее устройство, каждый раз захватывая для этого общую шину. Это снижает пропускную способность общей шины, а следовательно, и производительность системы.

За счет непроизводительных затрат времени на анализ и установку семафора в памяти указанным недостатком обладают и системы, у которых арбитр шины выполнен в виде отдельных схем, входящих в состав процессорных блоков, соединенных между собой приоритетной (дейзи, гирляндной) цепочкой. Такая организация системы упрощает процесс наращивания количества процессорных блоков. Функции же, выполняемые как сосредоточенным, так и распределенным арбитрами шины, аналогичны.

Целью изобретения является повышение производительности многопроцессорной вычислительной системы.

Указанная цель достигается тем, что в многопроцессорную систему с общей шиной, содержащую К процессорных блоков, арбитр шины, системную память и внешнее устройство, введены триггеры, формирователи сигналов, элементы И, элементы ИЛИ, причем входы-выходы адреса (данных) управления каждого процессорного блока через общую шину соединены с одноименными входами-выходами системной памяти и внешнего устройства. Выходы Шина занята процессорных блоков с первого по К-й соединены с одноименными с первого по К-й входами арбитра шины соответственно. Выходы разрешения предоставления доступа к шине с первого по К-й арбитра шины соединены с одноименными входами процессорных блоков с первого по К-й соответственно. Выход Запрос внешнего устройства 1-го (,...,К) процессорного блока соединен с первым входом i-ro элемента И и входом сброса i-ro триггера, инверсный выход которого соединен с входом Предоставление внешнего устройства i-ro процессорного блока. Прямой выход i-ro триггера соединен с входом i-ro входного формирователя сигнала и через шину Внешнее устройство занято с входами всех остальных входных формирователей сигналов и выходами остальных выходных формирователей сигналов. Выход i-ro входного формирователя сигналов соединен с вторым входом i-ro элемента И, выход которого соединен с первым входом i-ro элемента ИЛИ, выход которого соединен 1-м

входом Запрос шины арбитра шины. Выход Запрос шины i-ro процессорного блока соединен с вторым входом i-ro элемента ИЛИ, i-й выход Разрешение предоставления доступа к шине арбитра соединен с входом установки i-ro триггера.

Отличительные признаки в указанной взаимосвязи ранее нигде не встречались, являются существенными, и в своей совокупности позволяют повысить производительность системы путем сокращения потерь времени на установку связи с внешним устройством, являющимся общим для процессоров.

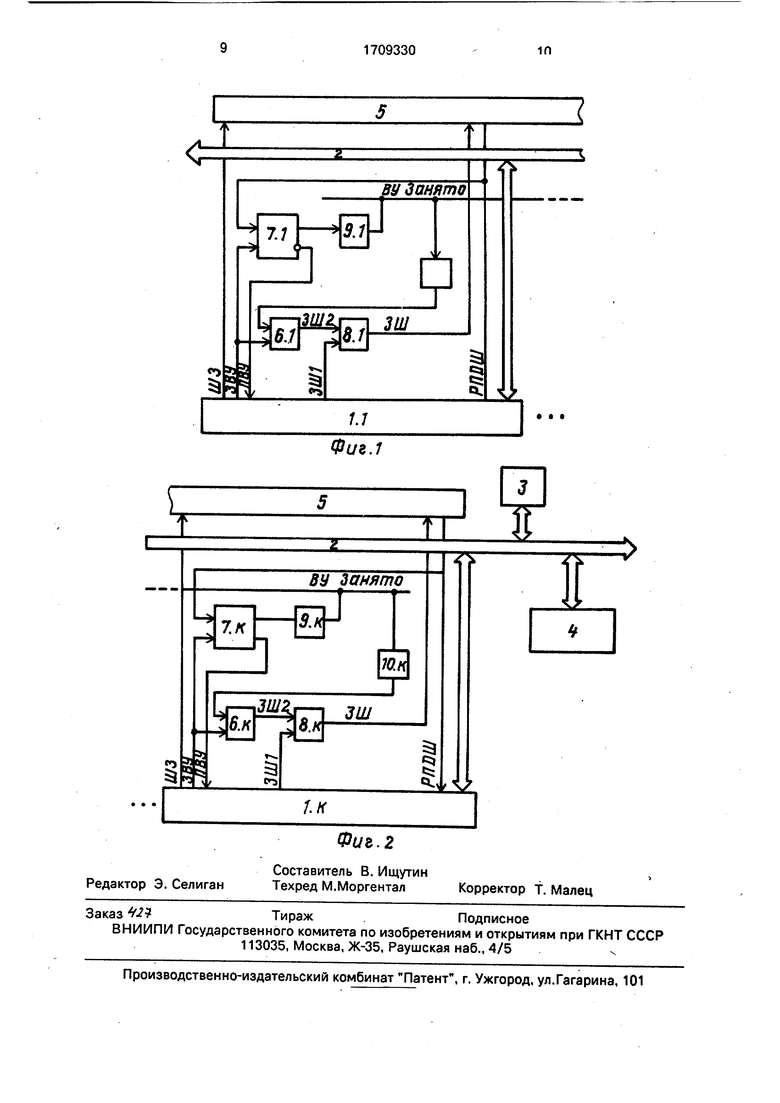

5 На фиг. 1 и 2 представлена структурная схема предлагаемой многопроцессорной системы.

Многопроцессорная система содержит процессорные блоки 1.1,...1, К, связанные

0 через общую шину 2 с системной памятью 3 и внешним устройством 4, арбитр 5 шины. Выходы 1иина занята процессорных блоков с первого по К-й соединены с одноименными с первого по К-й входами арбитра

5 шины соответственно. Выходы Запрос внешнего устройства процессорных блоков с первого по К-й соединены с первыми входами соответствующих элементов 6.16.К и входами сброса соответствую0 щихтриггеров 7.17.К. Инверсные выходы

триггеров 7.1...,7.К соединены с входами предоставления внешнего устройства соответствующих процессорных блоков 1.1,...,1.К. Выходы Запрос шины процессорных блоков 1.11.Ксоединены с вторыми входами соответствующих элементов

ИЛИ 8.18.К. Выходы элементов ИЛИ

8.18. К соединены с соответствующими

входами Запрос шины арбитра 5 шины.

0 Выходы Разрешение предоставления доступа к шине арбитра 5 шины соединены с соответствующими одноименными входами процессорных блоков 1.11.К и с соответствующими входами установки триггеров

5 7.1,...,7.К. Прямые выходы триггеров 7.17.К соединены с входами соответствующих выходных формирователей 9.1,...9.К сигналов, выходы которых соединены через шину Внешнее устройство занято с входа0 ми входных формирователей 10.110.К

сигналов. Выходы входных формирователей

10.110,К сигналов соединены с вторыми

входами соответствующих элементов И 6.16К, выходы которых соединены с пер5 выми входами соответствующих элементов

ИЛИ 8.18.К.

Процессорные блоки 1.1,...,1.К могут быть построены на базе серийно выпускаемых микропроцессорных комплектов. При использовании секционированных микропроцессоров К589, К1802, К1804 и др. выходные управляющие сигналы формируются в памяти микропрограмм, а входные являются логическими условиями.

Если процессорный блок строится на основе однокристального процессора CK 1801ВМ1, К1801ВМ2, К580ВМ80, К1810ВМ86 и др.), то в качестве управляющих входных и выходных сигналов используются соответствующие сигналы этого микропроцессора (Запрос шины, Предоставление шины и т. д.). Если число сигналов должно быть увеличено, то это достигается с помощью портов ввода-вывода, например, стандартных микросхем К580ВВ55, В1802ВВ1 и др.

В состав общей шины 2 входят проводники, обеспечивающие передачу между устройствами адреса, данных и управляющих сигналов. Количество и назначение указанных проводников определяется выбранным процессором. Например, для процессора микроэвм Электроника 60 число и назначение указанных проводников определяется в соответствии с ОСТ. Для построения системной памяти 3 могут быть использованы микросхемы типа К565РУЗ, К565РУ6, а также К573РФЗ, К537РУ10, К537РФ5 и др. В качестве арбитра шины 5 можно использовать микросхемы типа 1802ВВ2, К1810ВБ89идр.

В качестве элементов 6.1,...,6.К и 8.1 ,...,8.К могут быть использованы стандартные микросхемы серий К155, К531 и др. В

качестве формирователей 9.19.К и

10.1,...10.К сигналов могут использоваться микросхемы 531АПЗ, 531АП4, 559ИП1, 559ИП2, 559ИПЗ, 589АП16,

589АП26 и др. Триггеры 7.17.К могут быть

реализованы на любых триггерах, в которых предусмотрена их установка по перепаду сигнала.

Система в процессе установки связи процессорных блоков с внешним устройством работает следующим образом.

Триггеры 7.1,...,7.К установлены в единичное состояние, если на соответствующих процессорных блоках 1.11.К не

установлены сигналы Запрос внешнего устройства. Если процессорный блок, например 1.М, установит сигнал Запрос внешнего устройства, то этот сигнал, во первых, поступает на вход сброса триггера 7.М и снимает запрет на переключение его, а, во-вторых, поступает на первый вход элемента И 6.М. При этом, если внешнее устройство 4 занято, на шине Внешнее устройство занято в этом случае низкий уровень, который через формирователь 10.М сигналов поступает на второй вход

элемента И 6.М, элемент 6.М не вырабатывает сигнал Запрос шины 2, и сигнал Запрос шины не поступает на;арбитр шины 5. Когда внешнее устройство 4 освобождается

на шине Внешнее устройство занято устанавливается высокий уровень, элемент И б.М вырабатывает сигнал Запрос шины 2, а элемент ИЛИ 8.М - сигнал Запрос шины и последний поступает на соответствующий

0 вход арбитра шины 5. Арбитр 5 шины выбирает очередной запрашивающий процессорны.й блок для обслуживания и направляет ему сигнал Разрешения предоставления доступа к шине 2. С приходом

5 последнего на вход установки триггера 7.М триггер переключается. При этом, во-первых, через формирователь 9.М сигналов устанавливается сигнал Занятость внешнего устройства 4, - низкий уровень на шине

0 Внешнее устройство занято, а во-вторых, появляется сигнал Предоставление внешнего устройства на входе процессорного блока 1.М. После окончания обмена с внешним устройством 4 процессорный блок 1.М

5 снимает сигнал Запрос внешнего устройства и триггер 7.М снова переключается в единичное состояние. При этом снимается сигнал Занятость внешнего устройства 4, на шине Внешнее устройство занято через формирователь 9.М сигналов снова устанавливается высокий уровень.

Таким образом, в связи с наличием сигнальной линии Внешнее устройство занято процессорным блокам, нуждающимся в

5 обмене информацией с внешним устройством 4, hjeT необходимости обращаться к системной памяти 3 для анализа семафора в режиме захвата общей шины 2. За счет этого снижается время занятости общей шины

0 и непроизводительные затраты времени процессорами, т. е. повышается производительность предлагаемой многопроцессорной системы по сравнению с известными. В известной многопроцессорной системе каждый процессорный блок для использования внешнего устройства должен, в соответствии с алгоритмом, предварительно установить семафор, а после использования сбросить семафор в исходное

0 состояние. Например, в процессорных блоках, построенных на базе микропроцессора К1810ВМ86, это можно осуществить, используя команды ОСК ХСНС и МОУ. Суммарное среднее время выполнения их при

5 тактовой частоте 2 мГц будет равно 20 мкс. Каждый процессорный блок только на однократную проверку семафора, если внешнее устройство занято, будет затрачивать свыше 10 МКС. При многократном обращении к системной памяти, в случае занятости внешнего устройства, это время существенно возрастает для каждого процессора. Следует добавить, что при занятости внешнего устройства процессорные блоки, нуждающиеся в работе с ним, вынуждены будут практически блокировать общую шину, используя команду LOCK XCHG.

Все указанные временные затраты почти полностью отсутствуют в предлагаемой многопроцессорной системе, что позволяет снизить суммарное время выполнения программы. Действительно, для проверки занятости внешнего устройства нет необходимости захватывать общую шину. Кроме того, выставив сигнал Запрос внешнего устройства, каждый процессор может, не затрачивая время на ожидание, продолжать вычисления, если в этом есть необходимость. При получении ответного сигнала Представление внешнего устройства, процессор по прерыванию переходит на подпрограмму работы с внешним устройством. За счет этого повышается производительность системы, что является источником экономической эффективности.

Например, в системе числового программного управления спецвычислитель осуществляет расчет координат для разных видов интерполяции и является общим внешним устройством для процессоров. При управлении по 10 координатам спецвычислитель занят расчетами 3,5 мс в каждом такте управления. Теоретически, на протяжении указанного времени в известном устройстве шина может блокироваться процессорами, требующими доступ к спецвычислителю.

Применение предлагаемой системы приводит к уменьшению времени занятости общей шины примерно на 600 мкс в каждом такте управления. Это позволяет осуществлять управление по большему числу координат при неизменном такте управления или уменьшить длительность такта, повысив качество управления.

Формула изобретения Многопроцессорная система, содержащая К процессорных блоков, системную память, внешнее устройство, арбитр шины,

причем входы-выходы адреса (данных) управления каждого процессорного блока через общую шину соединена с одноименными входами-выходами системной памяти и внешнего устройства, выход Шина занята процессорных блоков с первого по К-й соединены с одноименными с первого по К-й входами арбитра шины соответственно, выходы разрешения представления доступа к шине с первого по К-й арбитра шины

соединены с одноименными входами процессорных блоков с первого по К-й соответственно, отличающаяся тем, что, с целью повышения производительности за счет сокращения времени на установку связи с внешними устройствами, в нее введены К элементов И, К триггеров, К элементов ИЛИ, К входных формирователей сигналов, К выходных формирователей сигналов, причем выход Запрос внешнего устройства

1-го процессорного блока соединен

с первым входом i-ro элемента И и входом сброса i-ro триггера, инверсный выход которого соединен с входом представления внешнего устройства i-ro процессорного

блока, прямой выход i-ro триггера соединен с входом -го выходного формирователя сигнала, выход которого соединен с входом i-ro входного формирователя сигнала и через шину Внешнее устройство занято с входами и выходами остальных выходных формирователей сигналов, выход i-ro входного формирователя сигналов соединен с вторым входом -го элемента И, выход которого соединен с первым входом i-ro элемента

ИЛИ, выход которого соединен с i-м входом Запрос шины арбитра шины, выход Запрос шины i-ro процессорного блока соединен с вторым входом i-ro элемента ИЛИ, 1-й выход разрешения предоставления доступа

к шине арбитра соединен с входом установки i-ro триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная система | 1988 |

|

SU1522228A1 |

| МНОГОМАШИННАЯ СИСТЕМА УПРАВЛЕНИЯ | 2006 |

|

RU2320003C2 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Многопроцессорная вычислительная система | 1988 |

|

SU1589287A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Устройство сопряжения многопроцессорной системы | 1987 |

|

SU1575195A1 |

| Мультипроцессорная система | 1990 |

|

SU1732351A1 |

| Устройство связи многопроцессорной вычислительной системы | 1988 |

|

SU1501081A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих многопроцессорных систем. Целью изобретения является повышение производительности за счет сокращения времени на установку связи с внешними устройствами. Поставленная цель достигается тем, что в систему, содержащую k процессорных блоков, системную память, внешнее устройство, арбитр шины, введены k элементов И, k триггеров, k элементов ИЛИ, k входных формирователей, k выходных формирователей, k входных формирователей. 2 ил.

| Система для обработки данных в реальном масштабе времени | 1978 |

|

SU734698A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| М.: Мир, 1985, с | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Насос | 1917 |

|

SU13A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1992-01-30—Публикация

1990-01-18—Подача