Изобретение относится к вычислительной технике и автоматики и может быть использовано в запоминающих устройствах, выполненных на блоках памяти большой разрядности.

Известны запоминающие устройства, в которых осуществляется запись, хранение и считывание информационных слов разрядности K [1-4]. Причем поле памяти этих устройств выполнено на блоках памяти разрядности L=1 с использованием для обнаружения и исправления одиночных ошибок преобразования информационных слов разрядности К в кодовые слова разрядности N (N>К). Однако в запоминающих устройствах, поле памяти которых выполнено на блоках памяти разрядности L>1, применение кода Хемминга не используется.

Наиболее близкими по технической сущности к предлагаемому устройству являются запоминающие устройства на блоках памяти с разрядностью L=1 [2], обеспечивающие обнаружение и исправление одиночных ошибок с помощью кода Хемминга. В этих запоминающих устройствах осуществляется проверка на четность определенных групп разрядов кодового слова, причем число контрольных разрядов, обеспечивающих локализацию места ошибки с помощью синдрома ошибки, удовлетворяет соотношению

N-K≥log2(N+1),

где N - число разрядов кодового слова;

K - число разрядов информационного слова;

(N-K) - число контрольных разрядов.

В общем случае такое запоминающее устройство с коррекцией одиночных ошибок содержит блоки памяти с разрядностью L=1, регистр информационного слова, блоки свертки определенных групп разрядов, входящих в корректор и реализующих суммирование разрядов информационного слова по модулю 2 для определения контрольных разрядов. Кодовое слово формируется из известного информационного слова и полученных контрольных разрядов. Сформированное кодовое слово из N разрядов записывается в регистр кодового слова и может быть использовано для передачи или хранения при отсутствии ошибок.

Проверка кодовых слов на наличие ошибок осуществляется с помощью блоков свертки, входящих в корректор, тех же групп разрядов кодовых слов по модулю 2 вместе с соответствующим контрольным разрядом и формированием синдрома ошибки, указывающим место ошибки. Код Хемминга применяется в том случае, когда наиболее вероятны одиночные ошибки.

Функциональные схемы постоянных и полупостоянных запоминающих устройств большой информационной емкости, поле памяти которых выполнено на блоках памяти большой разрядности (L>1, обычно L=8), описаны без использования кода Хемминга [3, 4]. Однако применять код Хемминга в запоминающих устройствах, поле памяти которых выполнено на блоках памяти большой разрядности L>1, при традиционном их построении нельзя, так как может выйти из строя, потеряв свою работоспособность, весь блок памяти, что приведет к появлению ошибки кратности L, исправить которую с помощью кода Хемминга невозможно.

В современной технике управления и информационно-вычислительных системах информационная избыточность и информационное резервирование используются для улучшения многих технических характеристик и прежде всего надежности их функционирования, точности вычислений и производительности [5].

Способы введения информационной избыточности разнообразны. К числу этих способов относятся:

- избыточность внутреннего информационного языка устройств обработки, передачи и хранения данных с использованием помехоустойчивых кодов;

- избыточность массивов данных в составе файлов данных;

- избыточность файловой структуры в памяти вычислительных машин, автоматизированных и автоматических систем управления и обработки информации и т.д.

Без информационной избыточности в той или иной форме невозможно организовать информационный процесс. Положение осложняется еще и тем, что без информационной избыточности нельзя использовать другие виды резервирования. Например, структурное резервирование в автоматизированных системах управления и обработки информации требует дублирования информации, хранимой в операционных регистрах и других операционных блоках основного процессора; особенно важно обеспечить надежное хранение постоянной и оперативной информации в запоминающих устройствах, подсистемах и системах большой информационной емкости. Важность надежной обработки, передачи и хранения информации существенно возрастает с усложнением задач и переходом в наносекундную область изготовления и использования.

Информационная избыточность со специальной упаковкой информации в запоминающих устройствах, подсистемах и системах уменьшает:

- потоки отказов и сбоев, так как не все отказы и сбои их элементов становятся отказами и сбоями сложных изделий. При этом если последствия отказа или сбоя элемента удается устранить за счет информационной избыточности, то они не считаются отказами и сбоями сложных изделий;

- время восстановления за счет уменьшения объема работ, обесцененных отказом или сбоем. При этом уменьшается время, затрачиваемое на повторение обесцененной части работ, и существенно увеличивается наработка до отказа или сбоя изделия;

- время восстановления за счет сокращения времени обнаружения и поиска неисправности.

Технический результат изобретения заключается в обеспечении многопортового режима работы устройства, повышении его надежности, обнаружении и исправлении ошибок в поле памяти, использовании блоков памяти большой разрядности L>1 с предварительным преобразованием массива информационных слов разрядности K в массив кодовых слов разрядности N, их упаковкой и записью в поле памяти. В каждом блоке памяти оказываются записанными одноименные разряды массива кодовых слов, что обеспечивает обнаружение и исправление ошибок с использованием кода Хемминга.

Технический результат предложенного решения достигается тем, что в запоминающее устройство, имеющее в своем составе корректор, N блоков памяти с числом информационных выходов в каждом, равным L, общую магистраль адреса, N индивидуальных магистралей записи L-разрядных слов, общую магистраль режима работы и общую магистраль инициализации, подключенных к блокам памяти, введены коммутатор, регистры портов, дополнительный дешифратор управления портами и внутренняя магистраль данных, L выходов каждого блока памяти подключены к коммутатору, имеющему L групп N-разрядных выходов, каждая из которых соединена с соответствующим регистром порта, вход инициализации которого подключен к одному из L выходов дополнительного дешифратора управления портами, снабженного индивидуальным адресным входом, а его вход инициализации соединен с общей магистралью инициализации, N-разрядные выходы каждого из L регистров портов подключены к внутренней магистрали данных, соединенной с входом корректора, вход инициализации которого подключен к общей магистрали инициализации.

Применение информационной избыточности со специальной упаковкой постоянной и оперативной информации, используемой в предлагаемом устройстве, намечает новые направления для построения изделий с возможностью исправления ошибок большей кратности, а не только одиночных ошибок.

Существо предлагаемого решения поясняется фиг.1 и фиг.2, а также табл.1.

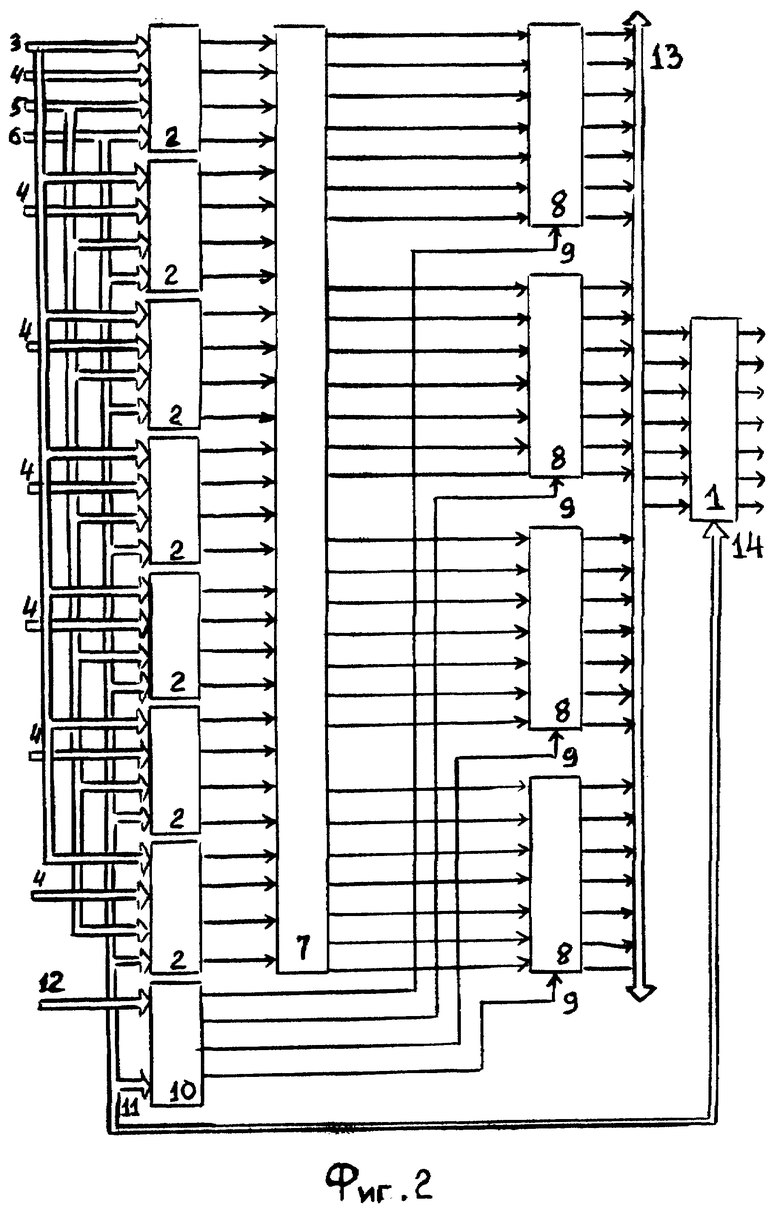

На фиг.1 представлена функциональная схема запоминающего устройства, в котором использованы блоки памяти с L информационными выходами, при L>1. Число блоков памяти равно N.

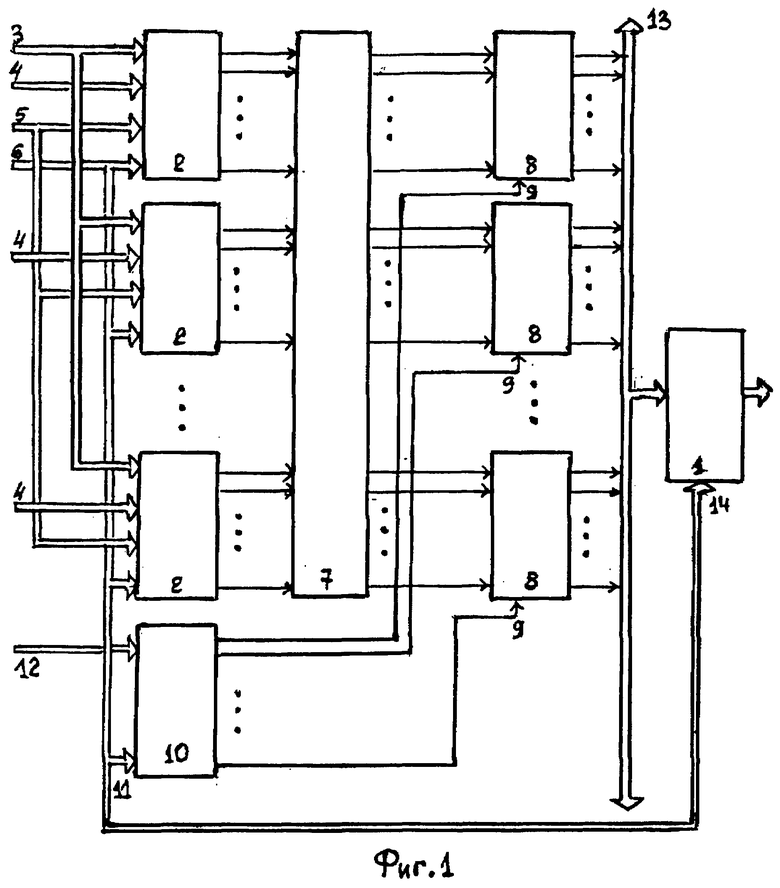

На фиг.2 изображена функциональная схема запоминающего устройства при N=7 и L=4, т.е. применен (7, 4) - код.

Предложенное запоминающее устройство (фиг.1) имеет в своем составе корректор 1, N блоков памяти 2 разрядности L. Блоки памяти 2 подключены к общей магистрали адреса 3. Каждый блок памяти 2 связан с одной из N индивидуальных магистралей записи L-разрядных слов 4. В состав запоминающего устройства входят магистраль режима работы 5 и общая магистраль инициализации 6, подключенные к каждому блоку памяти 2.

L выходов каждого блока памяти 2 подключены к коммутатору 7. Коммутатор 7 снабжен L группами выходов по N разрядов каждая. Выходы каждой группы выходов коммутатора 7 соединены с соответствующим регистром порта 8, вход инициализации 9 которого подключен к одному из выходов дополнительного дешифратора управления портами 10. Вход инициализации 11 дополнительного дешифратора управления портами 10 соединен с общей магистралью инициализации 6 запоминающего устройства. Дополнительный дешифратор управления портами 10 подключен к индивидуальной магистрали адреса выбора 12 регистров портов 8.

N выходов каждого регистра порта 8 соединены с внутренней магистралью данных 13, подключенной к корректору 1, вход инициализации которого 14 соединен с общей магистралью инициализации 6.

Устройство работает следующим образом.

Запись информации в блоки памяти 2 технических средств хранения оперативной информации осуществляется в штатном режиме - в составе этих средств. Запись информации в блоки памяти 2, предназначенные для хранения разного вида постоянной информации, производится или заводом-изготовителем, или пользователем, или в штатном режиме - в составе технических средств. При этом на общую магистраль инициализации 6 поступает сигнал инициализации, подготавливающий к работе блоки памяти 2, дополнительный дешифратор управления портами 10 и корректор 1.

На общую магистраль режима работы 5 приходит сигнал режима записи. При поступлении кода адреса на общую магистраль адреса 3 в каждом блоке памяти 2 выбираются элементы памяти, в которые записываются с индивидуальных магистралей записи L-разрядные слова.

В режиме считывания на общую магистраль инициализации 6 поступает сигнал инициализации, подготавливающий к работе блоки памяти 2, дополнительный дешифратор управления портами 10 и корректор 1.

На общую магистраль режима работы 5 приходит сигнал режима считывания. При поступлении кода адреса на общую магистраль адреса 3 на L выходах каждого блока памяти формируется L-разрядное слово, поступающее на коммутатор 7, на выходах которого формируются L N-разрядных слов.

Сформированные N-разрядные слова поступают только в тот регистр порта 8, на входе инициализации 9 которого присутствует сигнал инициализации, поступивший с соответствующего выхода дополнительного дешифратора управления портами 10.

Соответствующий регистр порта 8 выбирается дополнительным дешифратором управления портами 10 при поступлении на него по индивидуальной магистрали адреса 12 кода адреса регистра порта 8.

На N выходах выбранного регистра порта 8 формируется N-разрядное слово, поступающее на внутреннюю магистраль данных 13, а с последней - на корректор 1. Корректор 1 проверяет кодовое N-разрядное слово, поступившее на него, на наличие ошибок. При отсутствии ошибок кодовое слово с выхода корректора 1 используется по назначению. При наличии ошибок корректор 1 локализует места ошибок, исправляет их, подготавливая кодовое слово к использованию. Корректор 1 формирует слово при наличии на его входе инициализации 14 сигнала инициализации.

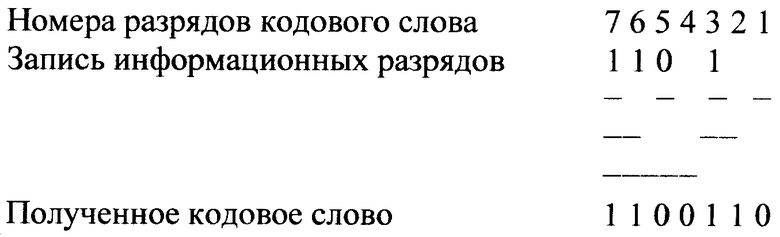

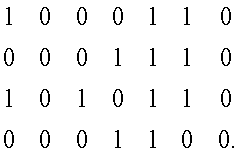

Уместно рассмотреть реализацию предложенного решения на конкретном примере, например, при N=7 и L=4 (фиг.2). Пусть требуется записать следующие информационные слова: 1101, 0011, 1010, 1001. После преобразования информационных слов соответственно получим следующие кодовые слова:

Символами «-» отмечены разряды трех групп кодового слова, для каждой из которых определяется контрольный разряд посредством суммирования отмеченных разрядов определенной группы кодового слова по модулю 2. Причем номера контрольных разрядов кодового слова соответствуют 2j, где j=0, 1, 2.

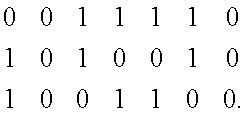

Остальные кодовые слова, полученные подобным образом, имеют вид:

Этому примеру соответствует запоминающее устройство с четырьмя портами, показанное на фиг.2, на котором изображены семь блоков памяти 2 (N=7), каждый из которых имеет четыре выхода (L=4). Выходы блоков памяти 2 обозначены словом DO с двухзначным числом, в котором старший разряд представляет номер блока памяти 2, а младший - номер его выхода.

Коммутатор 7 имеет семь групп входов по четыре разряда каждая и четыре группы выходов по семь разрядов. Выходы коммутатора 7 обозначены аналогичным образом, но с тем отличием, что значение их будет другим в соответствии с работой коммутатора 7. В таблице 1 обозначены номера выходов блоков памяти 2, их значения после записи кодовых слов в блоки памяти 2 и значения выходов коммутатора 7.

Каждая группа из семи выходов коммутатора 7 подключена к соответствующему регистру порта 8, инициализация которого осуществляется сигналом инициализации, поступающим на вход инициализации 9 с соответствующего выхода дополнительного дешифратора управления портами 10.

Перед режимом считывания пусть по определенному коду адреса в каждом блоке памяти 2 записаны одноименные разряды кодовых слов (см. табл.1 и фиг.2 сверху вниз), т.е. в блоках памяти 2 окажутся слова:

в первом - 0000, во втором - 1110, в третьем - 1101, в четвертом - 0101, в пятом - 0110, в шестом - 1000, в седьмом - 1011.

При поступлении на общую магистраль адреса 3 соответствующего кода адреса на выходах коммутатора 7 в отсутствии одиночных ошибок формируются четыре кодовых слова по семь разрядов:

Эти кодовые слова поступают на входы регистров портов 8, но записываются только в один из них по сигналу инициализации, поступающему на соответствующий вход инициализации 9 выбранного регистра порта 8. Сигнал инициализации формируется на одном из выходов дополнительного дешифратора управления портами 10.

Кодовое слово с выбранного регистра порта 8 через внутреннюю магистраль данных 13 поступает на корректор 1. Корректор 1 анализирует поступившее кодовое слово на наличие ошибки, вырабатывая синдром ошибки. Если синдром ошибки равен нулю, то кодовое слово поступает на выход корректора 1 для использования по назначению.

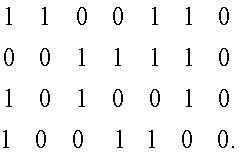

Определение синдрома ошибки для каждого кодового слова выполняется корректором 1 посредством суммирования разрядов определенных групп по модулю 2 вместе с их контрольным разрядом. Процесс вычисления синдрома ошибки каждого кодового слова можно проиллюстрировать следующим образом, имея в виду, что младший разряд определенной группы разрядов кодового слова - он же и контрольный разряд этой группы, находится справа в контролируемой группе, а старший разряд группы - слева. Причем номер контрольного разряда равен 2j, где j=0, 1, 2:

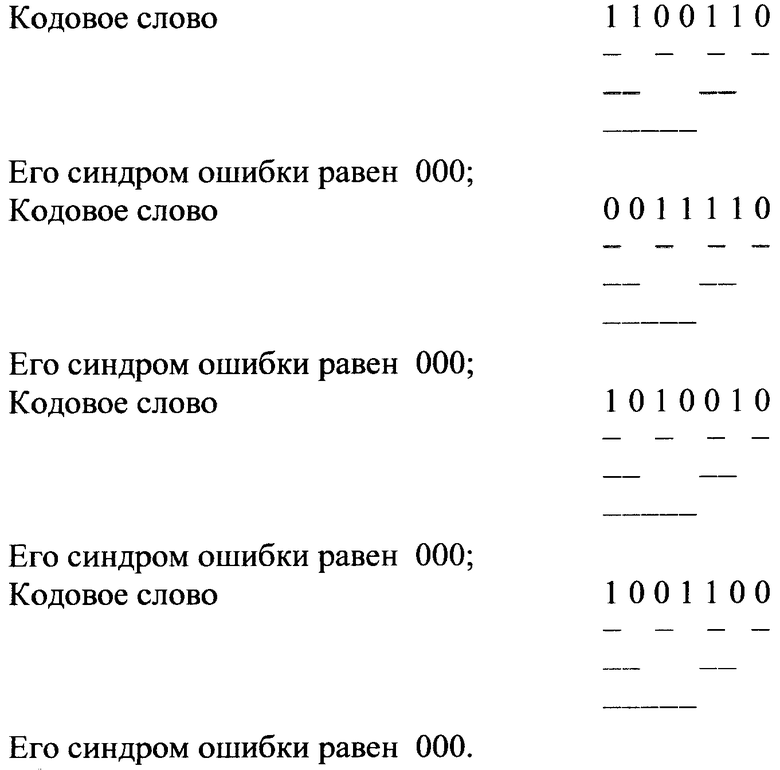

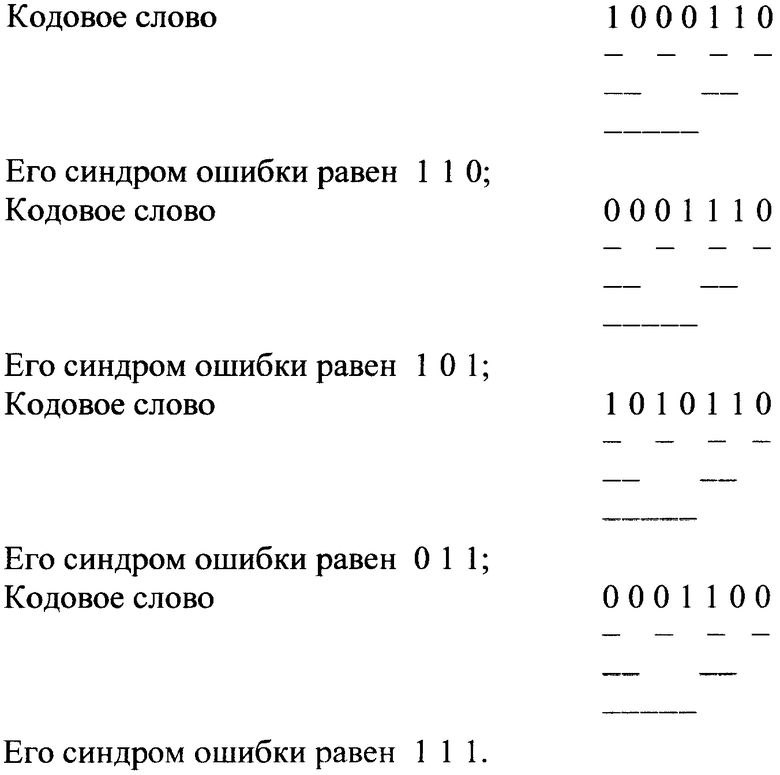

Пусть теперь каждое кодовое слово имеет ошибку в одном разряде и кодовые слова имеют вид:

После поступления этих кодовых слов на корректор 1 для каждого слова формируется синдром ошибки, указывающий номер разряда, в котором возник ошибочный символ (1 или 0). Кодовое слово корректируется посредством инвертирования ошибочного разряда. После этого кодовое слово поступает на выход корректор 1 и может быть использовано по назначению.

Процесс определения синдрома ошибки можно проиллюстрировать следующим образом:

Синдром ошибки указывает номер разряда, в котором произошла ошибка, считая справа налево, имея в виду, что номер младшего разряда кодового слова равен 1.

После исправления ошибки в каждом кодовом слове последнее используется по назначению.

При неизменном адресе на входе 12 дополнительного дешифратора управления портами 10 и поступлении нового кода адреса на общую магистраль адреса 3 на выходе ранее выбранного регистра порта 8 появится следующее кодовое слово.

Поступление нового адреса на вход 12 дополнительного дешифратора управления портами 10 при старом коде адреса на общей магистрали адреса 3 будет выбран соответствующий регистр порта 8 и на его выходе сформируется другое кодовое слово.

Рассмотренный пример иллюстрирует возможность использования кода Хемминга для обнаружения и исправления одиночных ошибок в поле памяти многопортового запоминающего устройства, выполненного на блоках памяти 2 с большим числом информационных выходов (L>1), открывая новые возможности при построении надежных устройств, подсистем и систем хранения информации и других технических средств с большим числом информационных каналов.

Источники информации

1. Потемкин И.С.Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат, 1988, с.115, 141-146.

2. Перспективы развития вычислительной техники. В 11 кн.: Справ. пособие /Под ред. Ю.М.Смирнова. Кн.7: Полупроводниковые запоминающие устройства/ А.Б.Акинфиев, В.И.Миронцев, Г.Д.Софийский, В.В.Цыркин. - М.: Высш. шк., 1989, с.7, 57, 98, 136-140.

3. Полупроводниковые БИС запоминающих устройств; Справочник /В.В.Баранов, Н.В.Бекин, А.Ю.Гордонов и др.; под ред. А.Ю.Гордонова и Ю.Н.Дьякова. - М.: Радио и связь, 1986, с.57-58.

4. Петросян О.А., Козырь И.Я., Коледов Л.А., Щетинин Ю.И. Схемотехника постоянных запоминающих устройств. - М.: Радио и связь, 1987.

5. Черкесов Г.Н. Надежность аппаратно-программных комплексов. Учебное пособие. - СПб.: Питер, 2005, 108-109.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2008 |

|

RU2390059C2 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для исправления ошибок в блоках памяти | 1983 |

|

SU1100639A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| Оперативное запоминающее устройство с коррекцией информации | 1983 |

|

SU1111206A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Запоминающее устройство с исправлением ошибок | 1987 |

|

SU1585835A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в запоминающих устройствах, выполненных на блоках памяти большой разрядности. Технический результат заключается в организации многопортового устройства, повышении его надежности, обнаружении и исправлении ошибок в поле его памяти. Запоминающее устройство обеспечивает использование в поле памяти блоков памяти большой информационной емкости и большой разрядности L>1 с предварительной упаковкой массива информационных слов разрядности К после их преобразования в массив кодовых слов разрядности N и записью их в поле памяти. Запоминающее устройство содержит корректор ошибок в разрядных словах, N блоков памяти с числом информационных выходов в каждом, равным L, общую магистраль адреса, N индивидуальных магистралей записи L-разрядных слов, общую магистраль режима работы и общую магистраль инициализации, коммутатор, регистры портов, дешифратор управления портами и внутреннюю магистраль данных. 2 ил., 1 табл.

Запоминающее устройство, имеющее в своем составе корректор ошибок в разрядных словах, N блоков памяти с числом информационных выходов в каждом, равным L, общую магистраль адреса, N индивидуальных магистралей записи L-разрядных слов, общую магистраль режима работы и общую магистраль инициализации, подключенных к блокам памяти, отличающееся тем, что в устройство введены коммутатор, регистры портов, дешифратор управления портами и внутренняя магистраль данных, L выходов каждого блока памяти подключены к коммутатору, имеющему N групп L-разрядных входов и L групп N-разрядных выходов, каждая из которых соединена с соответствующим регистром порта, вход инициализации которого подключен к одному из L выходов дешифратора управления портами, снабженного собственной магистралью адреса, а его вход инициализации соединен с общей магистралью инициализации, N-разрядные выходы каждого из L регистров портов подключены к внутренней магистрали данных, соединенной с входом корректора ошибок в разрядных словах, вход инициализации которого подключен к общей магистрали инициализации, причем L-разрядные слова, считанные по коду адреса, пришедшего на общую магистраль адреса, одновременно поступают на N групп L-разрядных входов коммутатора, одновременно формирующего L N-разрядные кодовые слова, появляющиеся одновременно на N-разрядных выходах коммутатора, кодовое слово записывается только в тот регистр порта, на вход инициализации которого подан сигнал инициализации с одного из выходов дешифратора управления портами в соответствии с кодом адреса, пришедшего с собственной магистрали адреса дешифратора управления портами.

| RU 2058603 C1, 20.04.1996 | |||

| САМОКОРРЕКТИРУЮЩЕЕСЯ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297032C2 |

| US 4958318, 18.09.1990 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| КОНОПЕЛЬКО В.К | |||

| и др | |||

| Надежное хранение информации в полупроводниковых запоминающих устройствах | |||

| - М.: Радио и связь, 1986, с.5, 105, 152, 212, 213. | |||

Авторы

Даты

2010-03-20—Публикация

2008-06-02—Подача