(21)4196251/24-24 (22) 17.02.87 (46)15.08.90. Бюл. №30

(71)Минский радиотехнический институт

(72)П.П.Урбанович (53)681.327(088.8)

(56)Авторское свидетельство СССР ISfe 964734. кл. G 11 С 29/00. 1981.

Авторское свидетельство СССР Мг 1133624. кл. G 11 С 29/00, 1983. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОШИБОК

(57)Изобретение относится к вычислительной технике и может быть использовано при

создании устройств памяти повышенной функциональной надежности. Цель изобретения - повышение быстродействия. Устройство содержит блок 1 памяти, коммутаторы 3 и 6, регистр 5 числа, блок 9 инверторов, блок 12 кодирования, блок 14 обнаружения ошибок, дешифратор 21. блок 23 коррекции, регистр 24 сдвига, элементы И 29-31, элементы ИЛИ 32.33. В устройстве обеспечивается исправление многократных ошибок в любом кодовом слове, количество которых более, чем в два раза превышает корректирующую способность применяе- мого кода. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство коррекции двойных ошибок с использованием кода Рида-Соломона | 1988 |

|

SU1662010A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство для исправления ошибокВ КОдОВОй КОМбиНАции | 1978 |

|

SU805315A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании устройств памяти повышенной функциональной надежности. Цель изобретения - повышение быстродействия. Устройство содержит блок 1 памяти, коммутаторы 3 и 6, регистр 5 числа, блок 9 инверторов, блок 12 кодирования, блок 14 обнаружения ошибок, дешифратор 21, блок 23 коррекции, регистр 24 сдвига, элементы И 29 - 31, элементы ИЛИ 32, 33. В устройстве обеспечивается исправление многократных ошибок в любом кодовом слове, количество которых более, чем в два раза превышает корректирующую способность применяемого кода. 2 ил.

СЛ

00 СЛ 00 СА СЛ

Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежных запоминающих устройств (ЗУ) и систем.

Цель изобретения - повышение быстродействия.

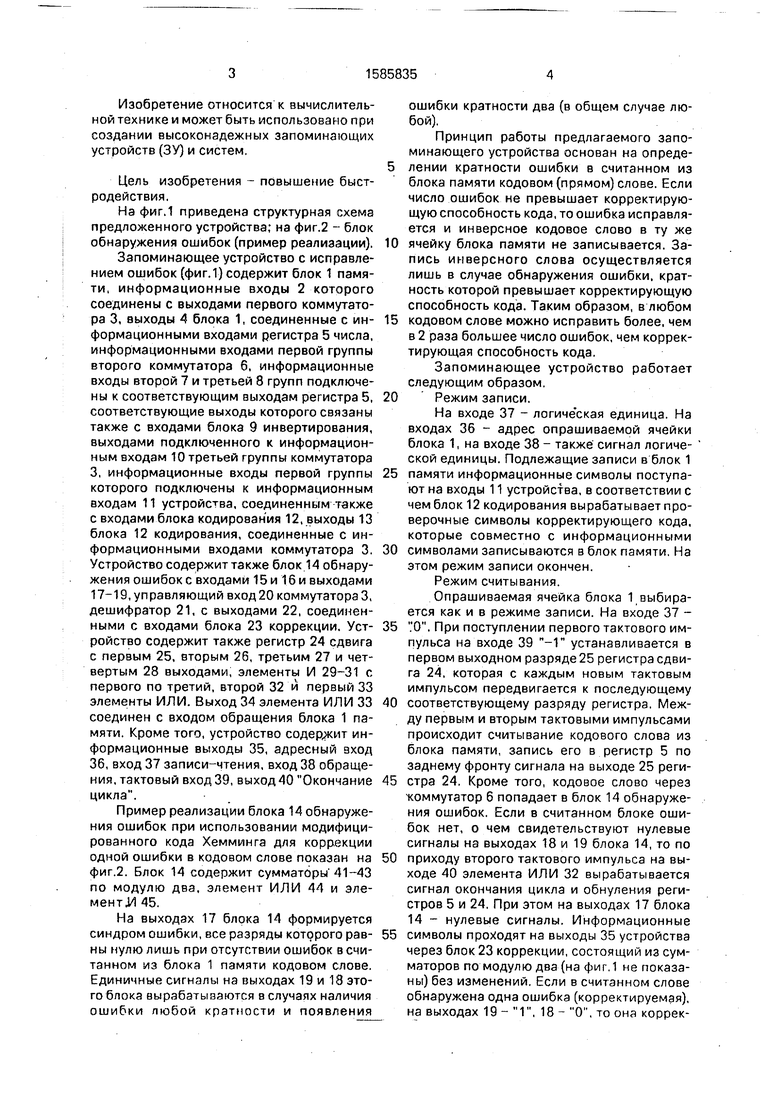

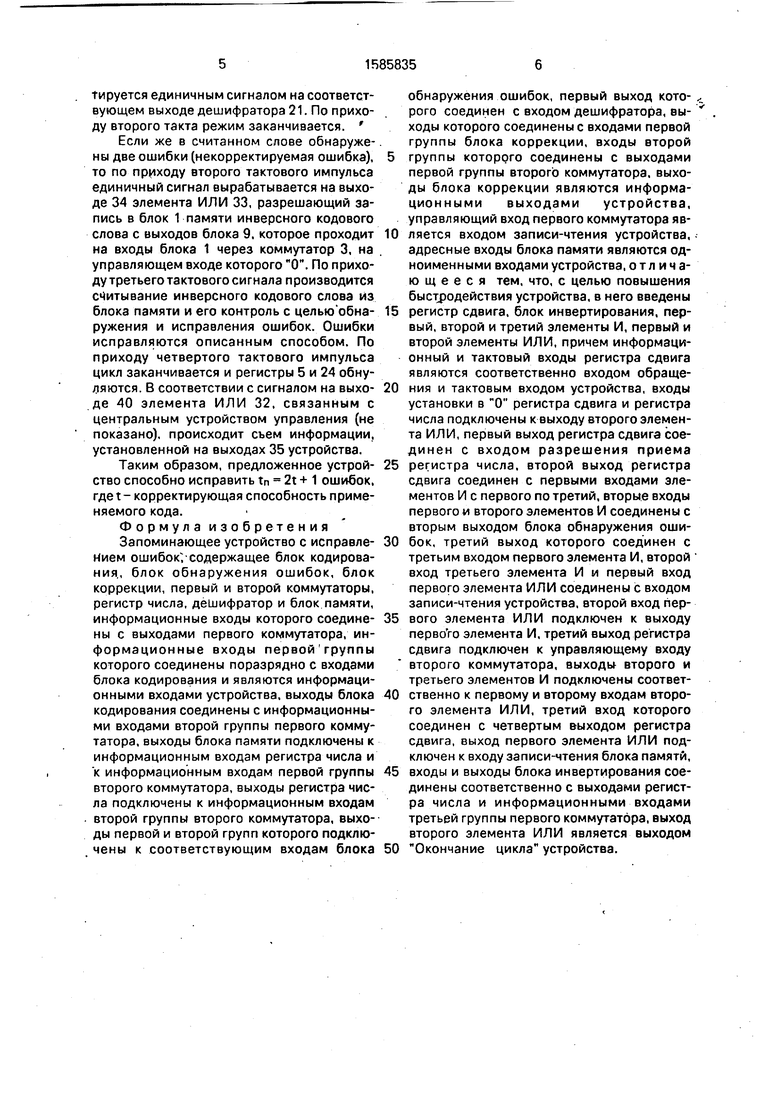

На фиг.1 приведена структурная схема предложенного устройства; на фиг.2 - блок обнаружения ошибок (пример реализации).

Запоминающее устройство с исправлением ошибок (фиг.1) содержит блок 1 памяти, информационные входы 2 которого соединены с выходами первого коммутатора 3, выходы 4 блока 1, соединенные с информационными входами регистра 5 числа, информационными входами первой группы второго коммутатора б, информационные входы второй 7 и третьей В групп подключены к соответствующим выходам регистра 5, соответствующие выходы которого связаны также с входами блока 9 инвертирования, выходами подключенного к информационным входам 10 третьей группы коммутатора 3, информационные входы первой группы которого подключены к информационным входам 11 устройства, соединенным также с входами блока кодирован ия 12, выходы 13 блока 12 кодирования, соединенные с информационными входами коммутатора 3. Устройство содержит также блок 14 обнаружения ошибок с входами 15 и 16 и выходами 17-19, уп равляющий вход 20 коммутатора 3, дешифратор 21, с выходами 22, соединенными с входами блока 23 коррекции. Устройство содержит также регистр 24 сдвига с первым 25, вторым 26, третьим 27 и четвертым 28 выходами, элементы И 29-31 с первого по третий, второй 32 и первый 33 элементы ИЛИ. Выход 34 элемента ИЛИ 33 соединен с входом обращения блока 1 памяти. Кроме того, устройство содержит информационные выходы 35, адресный вход 36, вход 37 записи-чтения, вход 38 обращения, тактовый вход 39, выход 40 Окончание цикла.

Пример реализации блока 14 обнаружения ошибок при использовании модифицированного кода Хемминга для коррекции одной ошибки в кодовом слове показан на фиг.2. Блок 14 содержит сумматоры 41-43 по модулю два, элемент ИЛИ 44 и эле- MeHTj/1 45.

На выходах 17 блока 14 формируется синдром ошибки, все разряды которого равны нулю лишь при отсутствии ошибок в считанном из блока 1 памяти кодовом слове. Единичные сигналы на выходах 19 и 18 этого блока вырабатываются в случаях наличия ошибки любой кратности и появления

ошибки кратности два (в общем случае любой).

Принцип работы предлагаемого запоминающего устройства основан на опреде- лении кратности ошибки в считанном из блока памяти кодовом (прямом) слове. Если число ошибок не превышает корректирующую способность кода, то ошибка исправляется и инверсное кодовое слово в ту же

0 ячейку блока памяти не записывается. Запись инверсного слова осуществляется лишь в случае обнаружения ошибки, кратность которой превышает корректирующую способность кода. Таким образом, в любом

5 кодовом слове можно исправить более, чем в 2 раза большее число ошибок, чем корректирующая способность кода.

Запоминающее устройство работает следующим образом.

0 Режим записи.

На входе 37 - логическая единица. На входах 36 - адрес опрашиваемой ячейки блока 1, на входе 38 - также сигнал логической единицы. Подлежащие записи в блок 1

5 памяти информационные символы поступают на входы 11 устройства, в соответствии с чем блок 12 кодирования вырабатывает проверочные символы корректирующего кода, которые совместно с информационными

0 символами записываются в блок памяти. На этом режим записи окончен. Режим считывания.

Опрашиваемая ячейка блока 1 выбирается как и в режиме записи. На входе 37 6 О. При поступлении первого тактового импульса на входе 39 -1 устанавливается в первом выходном разряде 25 регистра сдвига 24, которая с каждым новым тактовым импульсом передвигается к последующему

0 соответствующему разряду регистра. Между первым и вторым тактовыми импульсами происходит считывание кодового слова из блока памяти, запись его в регистр 5 по заднему фронту сигнала на выходе 25 реги5 стра 24. Кроме того, кодовое слово через -коммутатор 6 попадает в блок 14 обнаружения ошибок. Если в считанном блоке ошибок нет, о чем свидетельствуют нулевые сигналы на выходах 18 и 19 блока 14, то по

0 приходу второго тактового импульса на выходе 40 элемента ИЛИ 32 вырабатывается сигнал окончания цикла и обнуления регистров 5 и 24. При этом на выходах 17 блока 14 - нулевые сигналы. Информационные

5 символы проходят на выходы 35 устройства через блок 23 коррекции, состоящий из сумматоров по модулю два (на фиг.1 не показаны) без изменений. Если в считанном слове обнаружена одна ошибка (корректируемая), на выходах 19 - 1, 18 - О, то она коррекТируется единичным сигналом на соответствующем выходе дешифратора 21. По приходу второго такта режим заканчивается.

Если же в считанном слове обнаружены две ошибки (некорректируемая ошибка), то по пр 1ходу второго тактового импульса единичный сигнал вырабатывается на выходе 34 элемента ИЛИ 33, разрешающий запись в блок 1 памяти инверсного кодового слова с выходов блока 9, которое проходит на входы блока 1 через коммутатор 3, на управляющем входе которого О. По приходу третьего тактового сигнала производится считывание инверсного кодового слова из блока памяти и его контроль с целью обнаружения и исправления ошибок. Ошибки исправляются описанным способом. По приходу четвертого тактового импульса цикл заканчивается и регистры 5 и 24 обнуляются. В соответствии с сигналом на выходе 40 элемента ИЛИ 32, связанным с центральным устройством управления (не показано), происходит съем информации, установленной на выходах 35 устройства.

Таким образом, предложенное устройство способно исправить tn 2t + 1 ошибок, где t- корректирующая способность применяемого кода.

Формула изобретения

Запоминающее устройство с исправлением ошибок/содержащее блок кодирования,, блок обнаружения ошибок, блок коррекции, первый и второй коммутаторы, регистр числа, дешифратор и блок памяти, информационные входы которого соединены с выходами первого коммутатора, информационные входы первой группы которого соединены поразрядно с входами блока кодирования и являются информационными входами устройства, выходы блока кодирования соединены с информационными входами второй группы первого коммутатора, выходы блока памяти подключены к информационным входам регистра числа и к информационным входам первой группы второго коммутатора, выходы регистра числа подключены к информационным входам второй группы второго коммутатора, выходы первой и второй групп которого подключены к соответствующим входам блока

обнаружения ошибок, первый выход кото- рого соединен с входом дешифратора, вы- ходы которого соединены с входами первой группы блока коррекции, входы второй

группы которого соединены с выходами первой группы второго коммутатора, выходы блока коррекции являются информационными выходами устройства, управляющий вход первого коммутатора является входом записи-чтения устройства, адресные входы блока памяти являются одноименными входами устройства, отл ича- ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены

регистр сдвига, блок инвертирования, первый, второй и третий элементы И, первый и второй элементы ИЛИ, причем информационный и тактовый входы регистра сдвига являются соответственно входом обращения и тактовым входом устройства, входы установки в О регистра сдвига и регистра числа подключены к выходу второго элемента ИЛИ, первый выход регистра сдвига соединен с входом разрешения приема

регистра числа, второй выход регистра сдвига соединен с первыми входами элементов И с первого по третий, вторые входы первого и второго элементов И соединены с вторым выходом блока обнаружения ошибок, третий выход которого соединен с третьим входом первого элемента И, второй вход третьего элемента И и первый вход первого элемента ИЛИ соединены с входом записи-чтения устройства, второй вход первого элемента ИЛИ подключен к выходу перво го элемента И, третий выход регистра сдвига подключен к управляющему входу второго коммутатора, выходы второго и третьего элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ, третий вход которого соединен с четвертым выходом регистра сдвига, выход первого элемента ИЛИ подключен к входу записи-чтения блока памяти,

входы и выходы блока инвертирования соединены соответственно с выходами регистра числа и информационными входами третьей группы первого коммутатора, выход второго элемента ИЛИ является выходом

Окончание цикла устройства.

Фиа2

Авторы

Даты

1990-08-15—Публикация

1987-02-17—Подача