Изобретение относится к вычислительной технике и автоматике и может быть использовано в запоминающих устройствах, выполненных на блоках памяти с многоразрядной организацией.

Известны запоминающие устройства на блоках памяти с одноразрядной организацией с использованием информационной избыточности [1-5]. В этих устройствах возникновение одиночных ошибок в словах является наиболее вероятным как по отношению к сбоям запоминающих элементов, так и их отказам. По этой причине применение блоков коррекции для исправления одиночных ошибок и для обнаружения двойных в блоках памяти с одноразрядной организацией является эффективным средством надежного хранения и передачи информации.

Однако применение коррекции ошибок на основе кодов Хемминга в запоминающих устройствах, содержащих блоки памяти с многоразрядной организацией при их классическом построении, как для оперативных, так и для постоянных запоминающих устройств неэффективно из-за серьезных недостатков организации устройств. Это связано с тем, что коды Хемминга не исправляют ошибок из-за постоянных отказов как отдельных блоков памяти, так и их значительной части. Эти же ошибки, как показывают результаты анализов постоянных и наиболее вероятных ошибок, и являются наиболее часто встречающимися ошибками. Таким образом, при выходе из строя хотя бы одного блока памяти с многоразрядной организацией могут оказаться ошибочными сразу несколько разрядов слова (например, 4 или 8 разрядов, определяемых разрядной организацией блока памяти).

В известных функциональных и структурных схемах постоянных запоминающих устройств большой информационной емкости и большой разрядности применены способы наращивания информационной емкости устройств по разрядам, по словам и как по разрядам, так и по словам [2-4]. Наиболее близкими по технической сущности к предлагаемому устройству являются оперативные и постоянные запоминающие устройства, описанные в работах [1-4].

Наиболее близкими по технической сущности к предлагаемому постоянному запоминающему устройству являются постоянные запоминающие устройства на блоках памяти с многоразрядной организацией. В этих устройствах применены магистрали адреса и инициализации. Однако в них не использована информационная избыточность на основе кодов Хемминга при построении устройств постоянной памяти с большим числом информационных выходов.

Технический результат предлагаемого изобретения заключается в обеспечении однопортового режима работы устройства, повышении его надежности устройства за счет использования информационной избыточности (кода Хемминга) для обнаружения и исправления одиночных ошибок и обнаружения двойных ошибок в однопортовом режиме работы простыми средствами, расширении функциональных возможностей устройства за счет использования информационной избыточности, формирования на выходе устройства слов как в прямом, так и обратном кодах с выработкой признака кода. Для построения устройства обеспечивается возможность использования блоков постоянной памяти с многоразрядной организацией с предварительным преобразованием информационных слов разрядности К в кодовые слова разрядности N, их соответствующей упаковкой и записью в поле памяти, содержащем N блоков постоянной памяти с многоразрядной организацией (в каждом блоке постоянной памяти оказываются записанными одноименные разряды кодовых слов). Расширение функциональных возможностей устройства обеспечивается за счет использования информационной избыточности, формирования на выходе устройства слов как в прямом, так и в обратном кодах с выработкой признака кода.

Технический результат достигается тем, что в постоянное запоминающее устройство, имеющее в своем составе блоки памяти, магистраль инициализации, магистраль режима работы, магистраль адреса, магистраль записи, корректор и магистраль данных, введены блок управления упаковкой разрядов слова, блоки элементов И, блок элементов ИЛИ и блок выдачи слова.

Индивидуальные магистрали адреса блоков памяти и блока управления упаковкой разрядов слова подключены к друг другу, образуя общую магистраль адреса устройства. Индивидуальные магистрали режима работы блоков памяти подключены к друг другу, образуя общую магистраль режима работы. Индивидуальные магистрали инициализации блоков памяти, блока управления упаковкой разрядов слова, корректора и блока выдачи слова подключены к друг другу, образуя общую магистраль инициализации. Выходы каждого блока памяти подключены к информационным входам элементов И соответствующего блока элементов И, а управляющие упаковкой разрядов слова входы элементов И этого блока элементов И подключены к выходам блока управления упаковкой разрядов слова. Выходы элементов И блока элементов И соединены с входами соответствующего элемента ИЛИ блока элементов ИЛИ, выходы которого подключены к корректору. Выходы корректора соединены с входами блока выдачи слова, подключенного к управляющим входам приема слова, выдачи слова в прямом коде и выдачи слова в обратном коде с формированием признака кода слова на выходе признака кода слова. Выходы блока выдачи слова соединены с магистралью данных устройства.

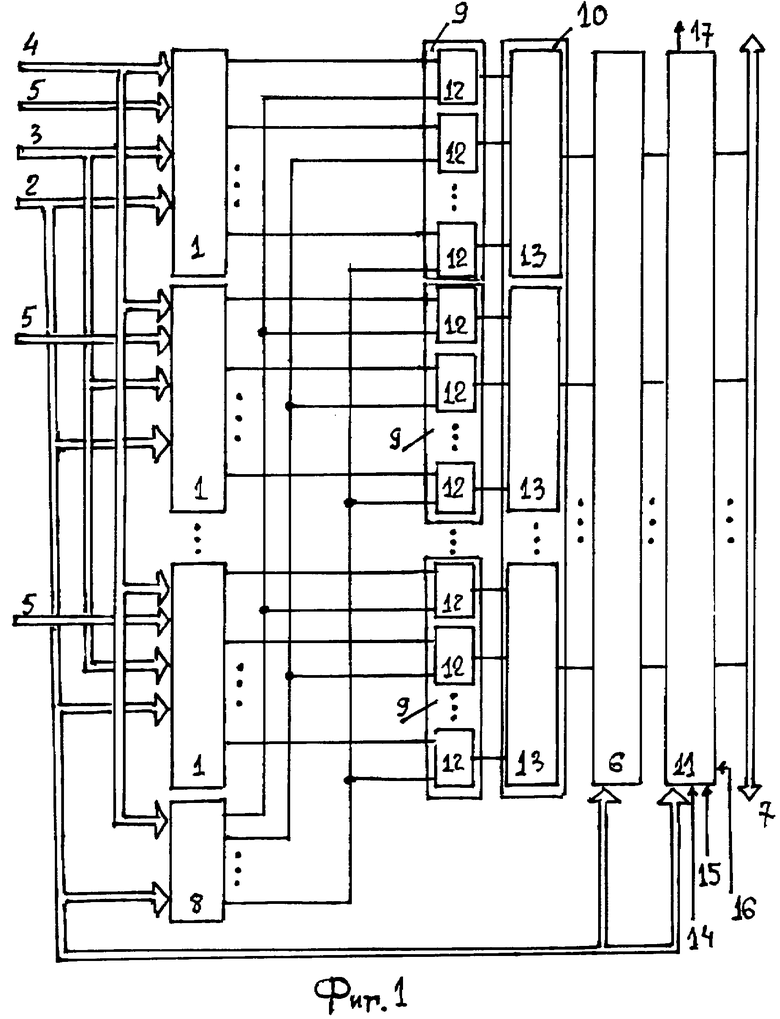

Существо предлагаемого технического решения иллюстрируется фиг.1, фиг.2 и табл.1.

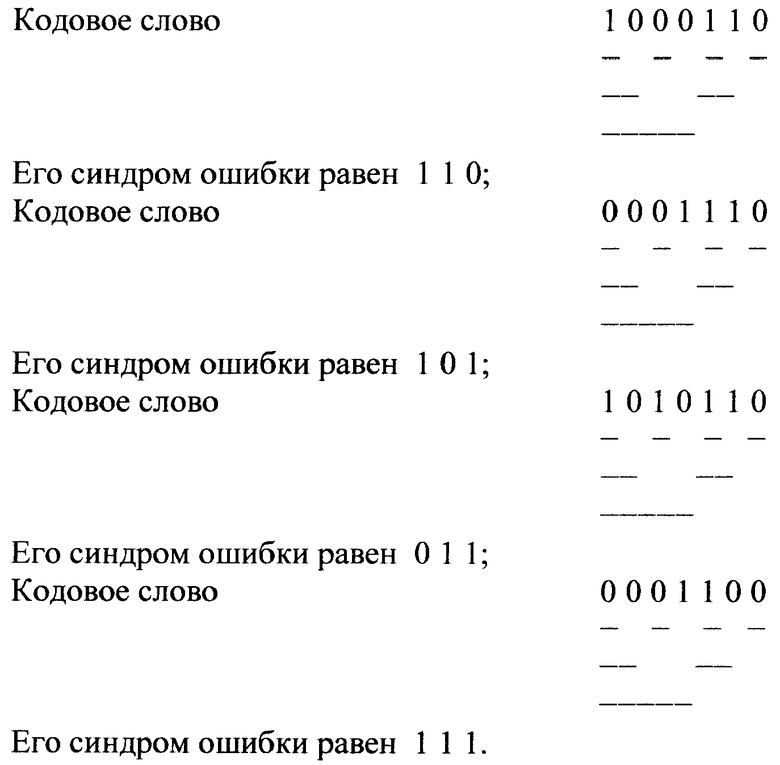

На фиг.1 изображена функциональная схема постоянного запоминающего устройства для записи, хранения и считывания N-разрядных кодовых слов, формируемых из информационных K-разрядных слов.

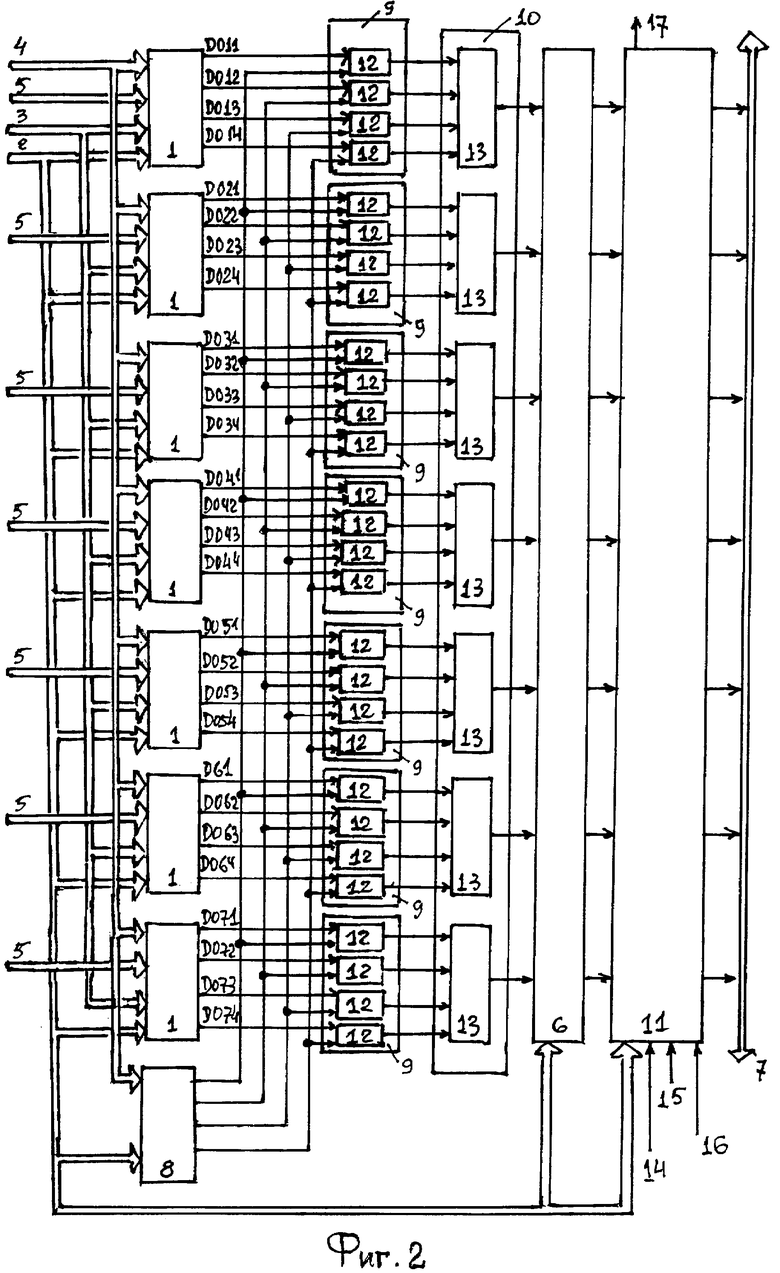

На фиг.2 представлена схема постоянного запоминающего устройства для записи, хранения и считывания кодовых слов при N=7, K=4.

Постоянное запоминающее устройство на фиг.1 имеет в своем составе блоки памяти 1, магистраль инициализации 2, магистраль режима работы 3, магистраль адреса 4, магистраль записи 5, корректор 6 и магистраль данных 7. В устройство введены блок управления упаковкой разрядов слова 8, блоки элементов И 9, блок элементов ИЛИ 10 и блок выдачи слова 11. Причем индивидуальные магистрали адреса блоков памяти 1 и блока управления упаковкой разрядов слова 8 подключены к друг другу, образуя общую магистраль адреса 4. Индивидуальные магистрали режима работы блоков памяти 1 подключены к друг другу, образуя общую магистраль режима работы 3. Индивидуальные магистрали инициализации блоков памяти 1, блока управления упаковкой разрядов слова 8, корректора 6 и блока выдачи слова 11 подключены к друг другу, образуя общую магистраль инициализации 2. Выходы каждого блока памяти 1 подключены к информационным входам элементов И 12 соответствующего блока элементов И 9, а управляющие упаковкой разрядов слова входы элементов И 12 этого блока элементов И 9 подключены к соответствующему выходу блока управления упаковкой разрядов слова 8. Выходы элементов И 12 блока элементов И 9 соединены с входами соответствующего элемента ИЛИ 13 блока элементов ИЛИ 10, выходы которого подключены к корректору 6. Выходы корректора 6 соединены с входами блока выдачи слова 11, подключенного к управляющим входам приема слова 14, выдачи слова в прямом коде 15 и выдачи слова в обратном коде 16. Блок выдачи слова обеспечивает формирование признака кода слова на выходе признака кода слова 17. Выходы блока выдачи слова 11 соединены с магистралью данных устройства 7.

Постоянное запоминающее устройство работает следующим образом. Запись информации в блоки памяти 1, предназначенные для хранения разного вида постоянной информации, производится или заводом-изготовителем, или пользователем, или в штатном режиме - в составе технических средств. При этом на общую магистраль инициализации 2 поступает сигнал инициализации, подготавливающий к работе блоки памяти 1, блок управления упаковкой разрядов слова 7, корректор 6 и блок выдачи слова 11.

На общую магистраль режима работы 3 приходит сигнал режима записи. При поступлении кода адреса на общую магистраль адреса 4 в каждом блоке памяти 1 выбираются элементы памяти, в которые записываются с индивидуальных магистралей записи 5 кодовые слова, разрядность которых определяется разрядной организацией блоков памяти 1.

Перед записью информации известные информационные слова преобразуются в кодовые слова аппаратным или (чаще всего) программным способами. При записи кодовых слов в блоки памяти 1 пользователем применяется программатор, управляемый компьютером.

В режиме считывания на общую магистраль инициализации 2 поступает сигнал инициализации, подготавливающий к работе блоки памяти 1, блок управления упаковкой разрядов слова 8, корректор 6 и блок выдачи слова 11.

На общую магистраль режима работы 3 приходит сигнал режима считывания. При поступлении кода адреса на общую магистраль адреса 4 на выходах каждого из блоков памяти 1 формируются одноименные разряды нескольких кодовых слов, поступающие на соответствующие элементы И 12 блока элементов И 9.

Разряды кодовых слов поступают на информационные входы элементов И 12 блоков элементов И 9, но появляются на выходе тех элементов И 12, на управляющих входах которых присутствует сигнал управления упаковкой разрядов кодового слова, поступивший с соответствующего выхода блока управления упаковкой разрядов кодового слова 8.

Элементы ИЛИ 13 блока элементов ИЛИ 10 принимают кодовое слово, поступающее на корректор 6, который проверяет кодовое слово на наличие одиночных ошибок. При отсутствии одиночной ошибки в кодовом слове корректор 6 вырабатывает синдром ошибки, равный 0, в противном случае корректором вырабатывается синдром ошибки, не равный 0 и указывающий место ошибочного разряда кодового слова. Далее корректор 6 исправляет одиночную ошибку, подготавливая кодовое слово к использованию по назначению: кодовое слово с корректора 6 поступает при наличии сигнала приема кодового слова на входе 14 в блок выдачи слова 11. При поступлении на вход 15 сигнала выдачи слова в прямом коде кодовое слово поступает в магистраль данных 7 в прямом коде, а при наличии сигнала на входе 16 блока выдачи слова 11 кодовое слово в обратном коде поступает на магистраль данных 7. При выдаче кодового слова вырабатывается сигнал признака кода на выходе 17 блока выдачи слова 11.

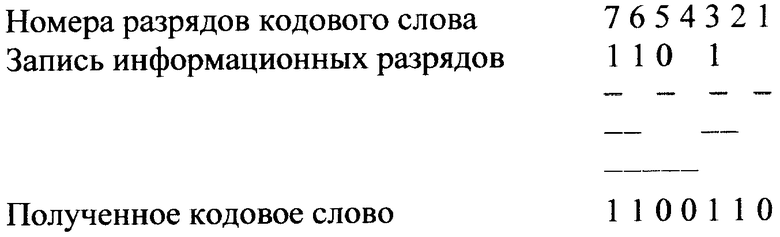

Реализация предложенного решения может быть проиллюстрирована на конкретном примере, например, при N=7 и L=4, где N - число разрядов кодового слова, а L - число информационных выходов блоков памяти 1. Пусть требуется записать в постоянное запоминающее устройство следующие информационные слова: 1101, 0011, 1010, 1001. Перед записью информационные слова преобразуются в кодовые слова. Преобразование информационных слов в кодовые слова по Хеммингу может быть показано следующим образом:

Символами «-» отмечены разряды трех групп кодового слова, для каждой из которых определяется контрольный разряд посредством суммирования отмеченных разрядов определенной группы кодового слова по модулю 2. Причем номера контрольных разрядов кодового слова соответствуют 2j, где j=0, 1, 2. Остальные кодовые слова, полученные подобным образом, имеют вид:

0011110

1010010

1001100

Этому примеру соответствует постоянное запоминающее устройство с одним портом, показанное на фиг.2, на котором изображены семь блоков памяти 1 (N=7), каждый из которых имеет четыре выхода (L=4). Выходы блоков памяти 1 обозначены словом DO с двухзначным числом, в котором старший разряд представляет номер блока памяти 1, а младший - номер его выхода. В табл.1 обозначены номера выходов блоков памяти 1, их значения после записи кодовых слов в блоки памяти 1 и значения выходов элементов ИЛИ 13 блока элементов ИЛИ 10. Выход каждого элемента ИЛИ 13 блока элементов ИЛИ 10 подключен к корректору 6, выходы которого подключены к блоку выдачи слова 11.

Перед режимом считывания пусть по определенным кодам адреса в каждом блоке памяти 1 записаны одноименные разряды кодовых слов (см. табл.1 и фиг.2 сверху вниз), т.е. в блоках памяти 1 окажутся слова:

в первом - 0000, во втором - 1110, в третьем - 1101, в четвертом - 0101, в пятом - 0110, в шестом - 1000, в седьмом - 1011.

При поступлении на общую магистраль адреса 4 соответствующих кодов адреса на выходах элементов ИЛИ 13 блока элементов ИЛИ 10 в отсутствие одиночных ошибок формируются четыре кодовых слова по семь разрядов:

1100110

0011110

1010010

1001100

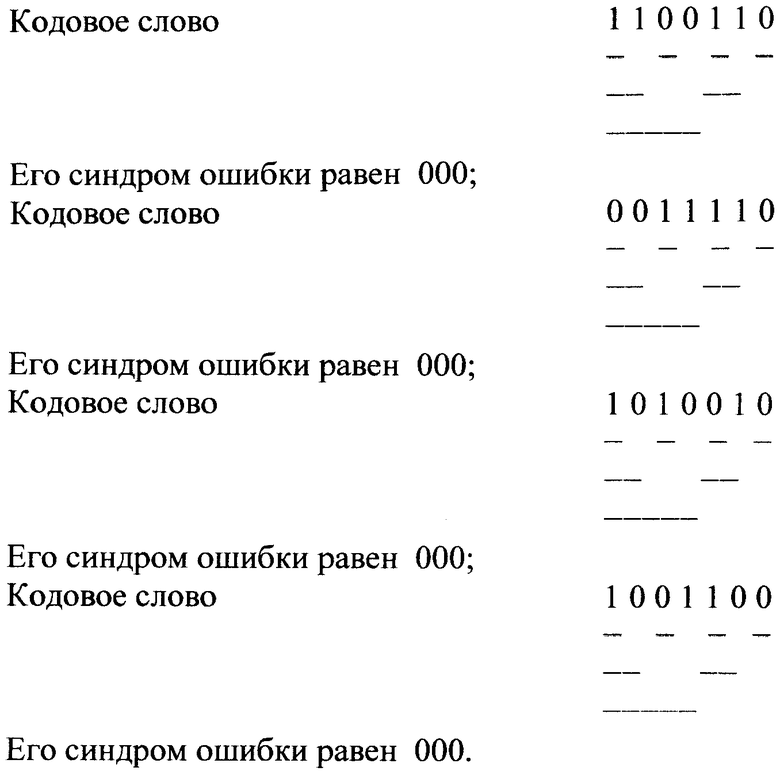

Эти кодовые слова поступают по очереди в соответствии с кодами адреса на входы корректора 6, но принимаются корректором только при наличии сигнала с определенного выхода блока управления упаковкой разрядов слова 8. Корректор 6 анализирует поступившее кодовое слово на наличие ошибки, вырабатывая синдром ошибки. Если синдром ошибки равен нулю, то кодовое слово поступает на выход корректора 6.

Определение синдрома ошибки для каждого кодового слова выполняется корректором 6 посредством суммирования разрядов определенных групп по модулю 2 вместе с их контрольным разрядом. Процесс вычисления синдрома ошибки каждого кодового слова можно проиллюстрировать следующим образом, имея в виду, что младший разряд определенной группы разрядов кодового слова - он же и контрольный разряд этой группы, находится справа в контролируемой группе, а старший разряд группы - слева. Причем номер контрольного разряда равен 2j, где j=0, 1, 2:

Пусть теперь каждое кодовое слово имеет ошибку в одном разряде и кодовые слова имеют вид:

1000110

0001110

1010110

0001100

После поступления этих кодовых слов на корректор 6 для каждого слова формируется синдром ошибки, указывающий номер разряда, в котором возник ошибочный символ (1 или 0). Кодовое слово корректируется посредством инвертирования ошибочного разряда. После этого кодовое слово поступает на выход корректора 6.

Процесс определения синдрома ошибки можно проиллюстрировать следующим образом:

Синдром ошибки указывает номер разряда, в котором произошла ошибка, считая справа налево, имея в виду, что номер младшего разряда кодового слова равен 1.

После исправления ошибки в каждом кодовом слове последнее поступает в блок выдачи слова 11.

При изменении кода адреса на магистрали адреса 4 на определенном выходе блока управления упаковкой разрядов слова 8 вырабатывается сигнал формирования последующего кодового слова.

Рассмотренный пример иллюстрирует возможность использования кода Хемминга для обнаружения и исправления одиночных ошибок в поле памяти однопортового постоянного запоминающего устройства, выполненного на блоках памяти с многоразрядной организацией (L>1, обычно L=8). При этом возникают новые возможности при построении надежных устройств, подсистем и систем хранения информации и других технических средств с большим числом информационных каналов.

Источники информации

[1]. Потемкин И.С. Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат, 1988.

[2]. Перспективы развития вычислительной техники. В 11 кн.: Справ. пособие / Под ред. Ю.М.Смирнова. Кн. 7: Полупроводниковые запоминающие устройства / А.Б.Акинфиев, В.И.Миронцев, Г.Д.Софийский, В.В.Цыркин. - М.: Высш. шк., 1989.

[3]. Полупроводниковые БИС запоминающих устройств. Справочник / В.В.Баранов, Н.В.Бекин, А.Ю.Гордонов и др.; под ред. А.Ю.Гордонова и Ю.Н.Дьякова. - М.: Радио и связь, 1986.

[4]. Петросян О.А., Козырь И.Я., Коледов Л.А., Щетинин Ю.И. Схемотехника постоянных запоминающих устройств. - М.: Радио и связь, 1987.

[5]. Черкесов Г.Н. Надежность аппаратно-программных комплексов. Учебное пособие. - СПб.: Питер, 2005, 108-109.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2008 |

|

RU2384899C2 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1336122A1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК И ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2024 |

|

RU2826822C1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С ПОВЫШЕННОЙ КОРРЕКТИРУЮЩЕЙ СПОСОБНОСТЬЮ | 2024 |

|

RU2829012C1 |

| Устройство для обнаружения и коррекции ошибок памяти | 1986 |

|

SU1377918A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в запоминающих устройствах, выполненных на блоках памяти с многоразрядной организацией. Техническим результатом является повышение надежности устройства и расширение функциональных возможностей. Постоянное запоминающее устройство содержит блоки памяти, магистраль инициализации, магистраль режима работы, магистраль адреса, магистраль записи, корректор одиночных ошибок и магистраль данных, блок управления упаковкой разрядов слова, блоки элементов И, блок элементов ИЛИ и блок выдачи слова, индивидуальные магистрали адреса блоков памяти и блока управления упаковкой разрядов слова подключены к друг другу, образуя общую магистраль адреса устройства, индивидуальные магистрали режима работы блоков памяти подключены к друг другу, образуя общую магистраль режима работы, индивидуальные магистрали инициализации блоков памяти, блока управления упаковкой разрядов слова, корректора одиночных ошибок и блока выдачи слова подключены к друг другу, образуя общую магистраль инициализации. 2 ил., 1 табл.

Постоянное запоминающее устройство, имеющее в своем составе блоки памяти, магистраль инициализации, магистраль режима работы, магистраль адреса, магистраль записи, корректор одиночных ошибок и магистраль данных, отличающееся тем, что в устройство введены блок управления упаковкой разрядов слова, блоки элементов И, блок элементов ИЛИ и блок выдачи слова, индивидуальные магистрали адреса блоков памяти и блока управления упаковкой разрядов слова подключены к друг другу, образуя общую магистраль адреса устройства, индивидуальные магистрали режима работы блоков памяти подключены к друг другу, образуя общую магистраль режима работы, индивидуальные магистрали инициализации блоков памяти, блока управления упаковкой разрядов слова, корректора одиночных ошибок и блока выдачи слова подключены к друг другу, образуя общую магистраль инициализации, выходы каждого блока памяти подключены к информационным входам элементов И соответствующего блока элементов И, а управляющие упаковкой разрядов слова входы элементов И этого блока элементов И подключены к выходам блока управления упаковкой разрядов слова, выходы элементов И блока элементов И соединены с входами соответствующего элемента ИЛИ блока элементов ИЛИ, выходы которого подключены к корректору одиночных ошибок, выходы корректора одиночных ошибок соединены с входами блока выдачи слова, имеющего управляющие входы приема слова, выдачи слова в прямом коде и выдачи слова в обратном коде, а также выход признака кода слова, выходы блока выдачи слова соединены с магистралью данных устройства.

| САМОКОРРЕКТИРУЮЩЕЕСЯ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297032C2 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| ГУК М | |||

| «Аппаратные средства IBM PC | |||

| Энциклопедия» | |||

| - СПб.: Питер Ком, 1999, 317-319. | |||

Авторы

Даты

2010-05-20—Публикация

2008-06-02—Подача