Изобретение относится к электросвязи и может использоваться в телеметрических системах для ассоциативного сжатия передаваемой информации. Цель изобретения - повышение ин формативности устройства.

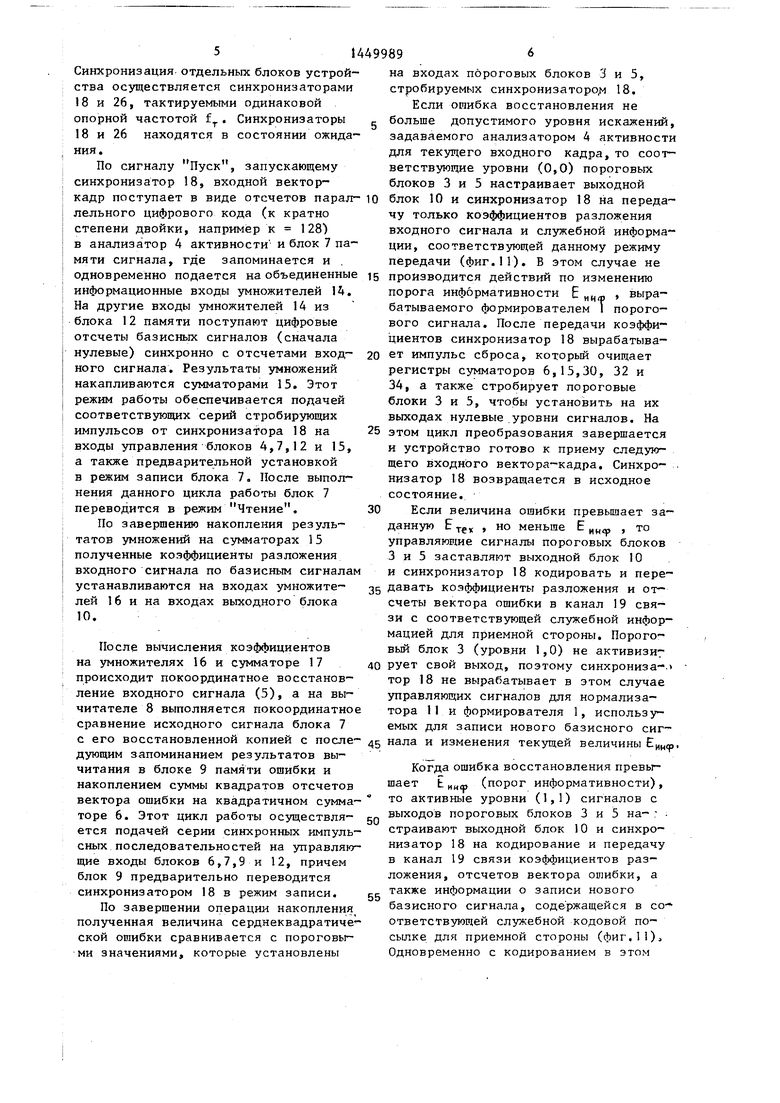

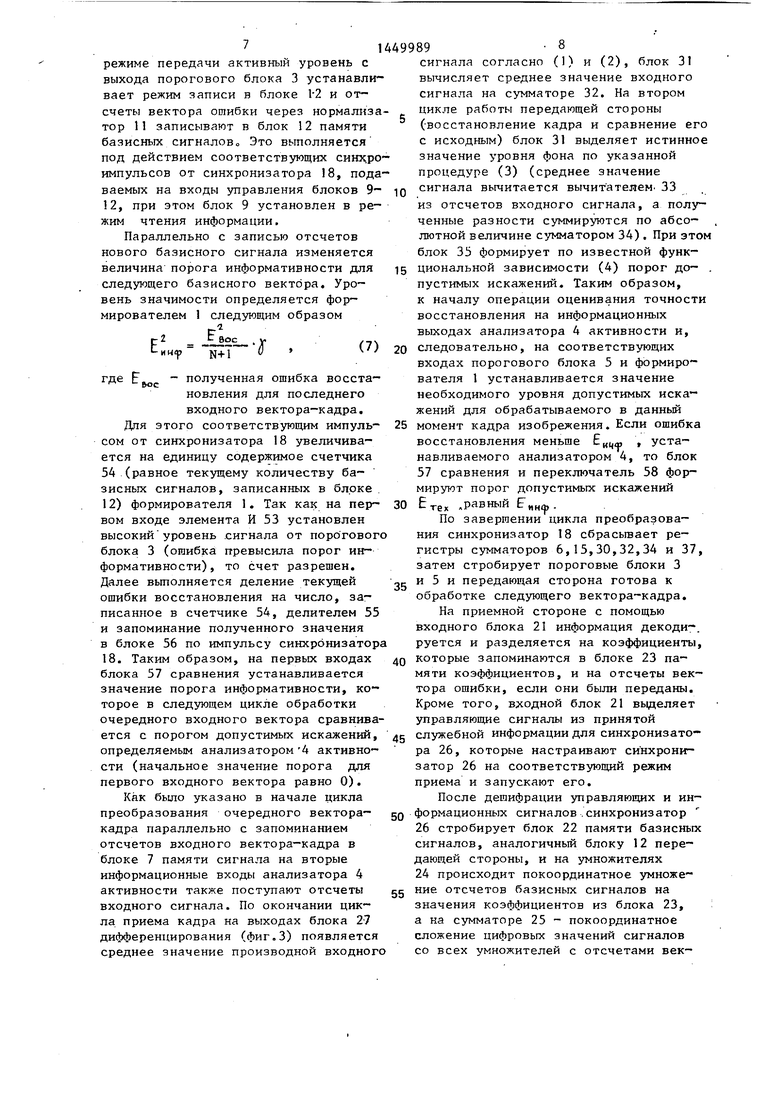

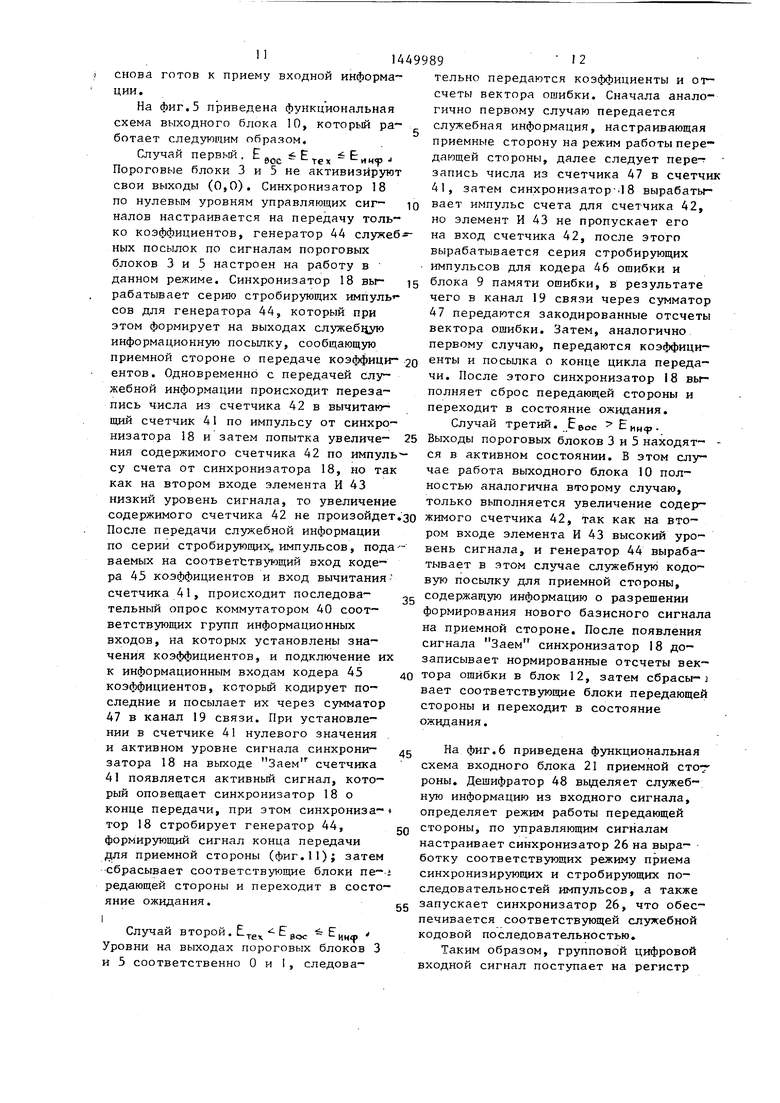

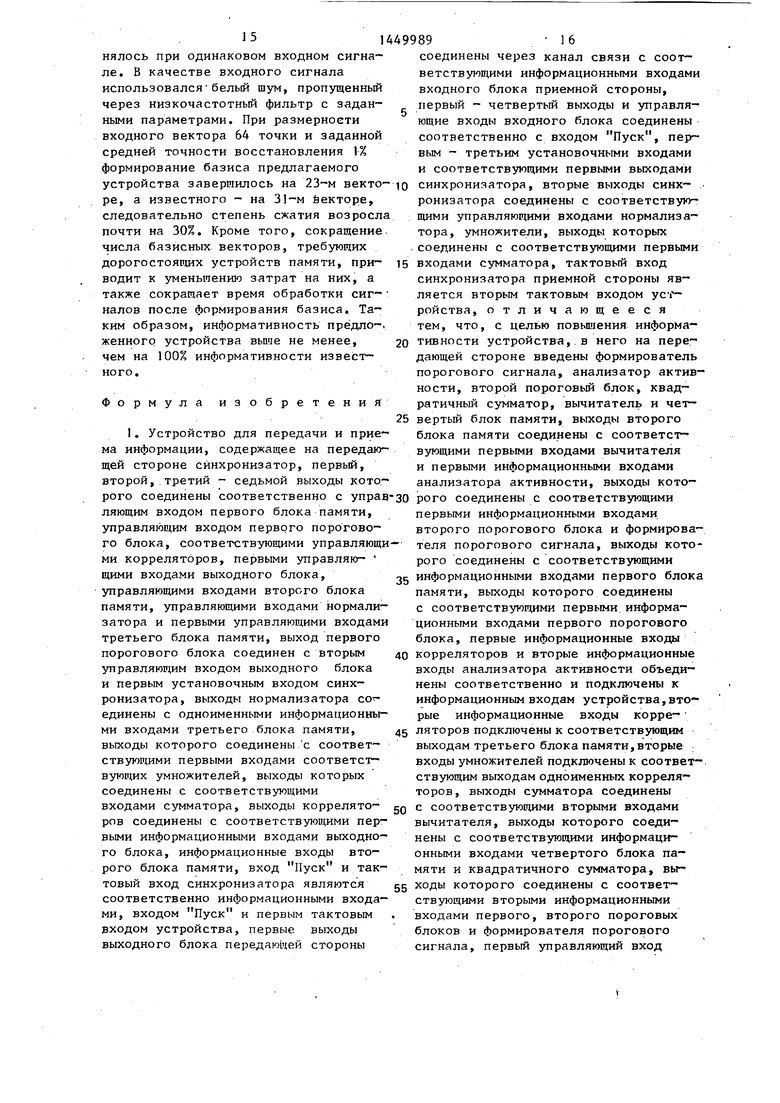

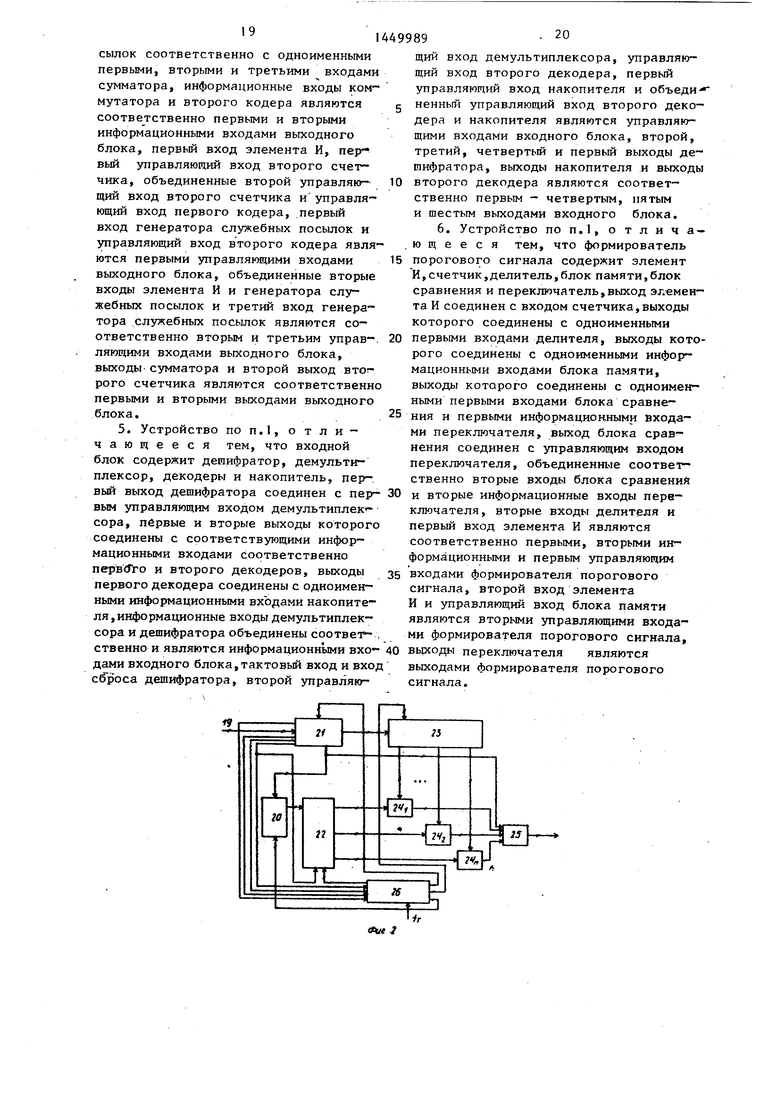

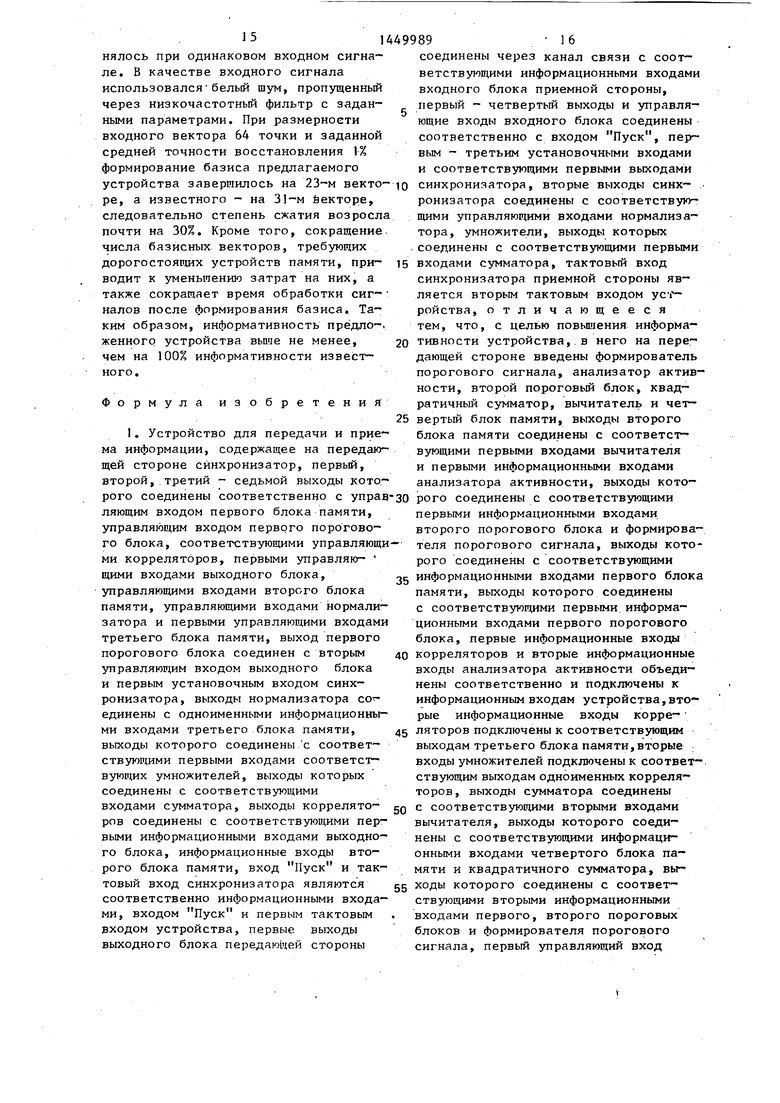

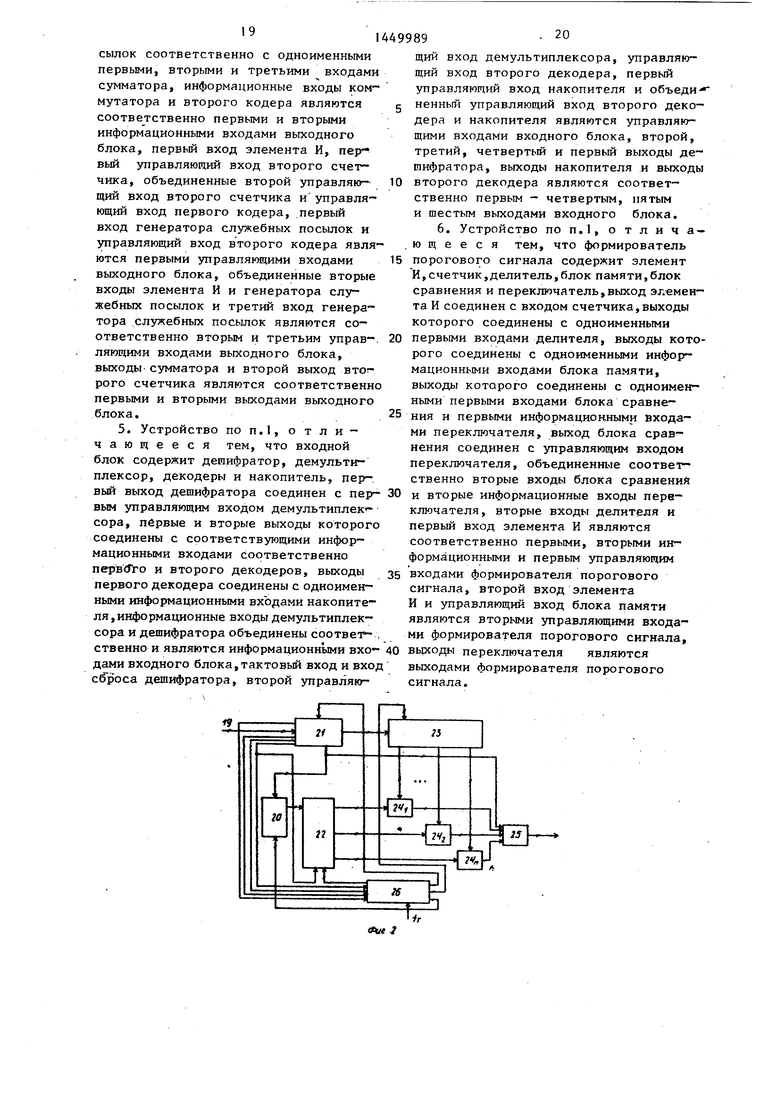

На фиг.1 представлена структурная схема передающей сторонь: устройства; на фиг.2 структурная схема приемной стороны устройства; на фиг.З - функциональная схема анализатора активности; на фиг.4 - функци ональная схема нормализатора; на фиг.З - функциональная схема выходно го блока; на фиг.6 - функциональная. схема входного блока;:на фиг.7 - функциональная схема формирователя порогового сигнала; на фиг.8 - функциональная схема блока питания базисных сигналов; на фиг.9 - функциональная схема дешифратора служебных посылок; на фиг.10 - функциональная схема синхронизатора, на фиг. 11 - форматы передаваемых информационных кадров.

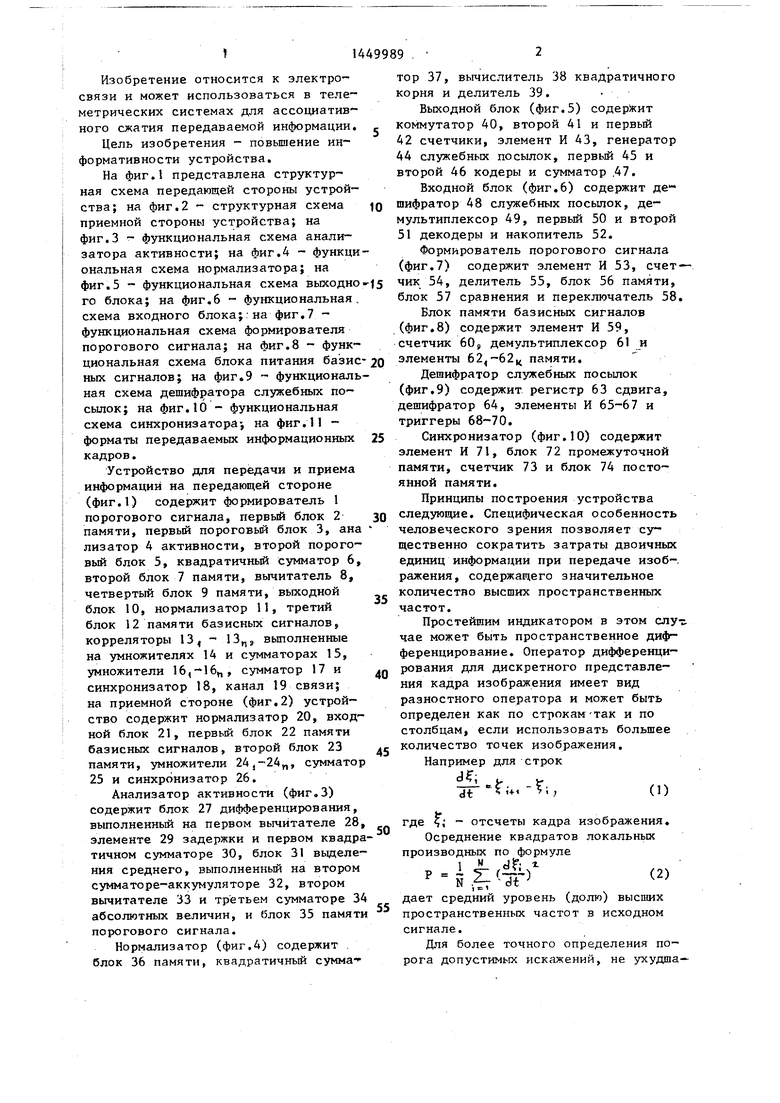

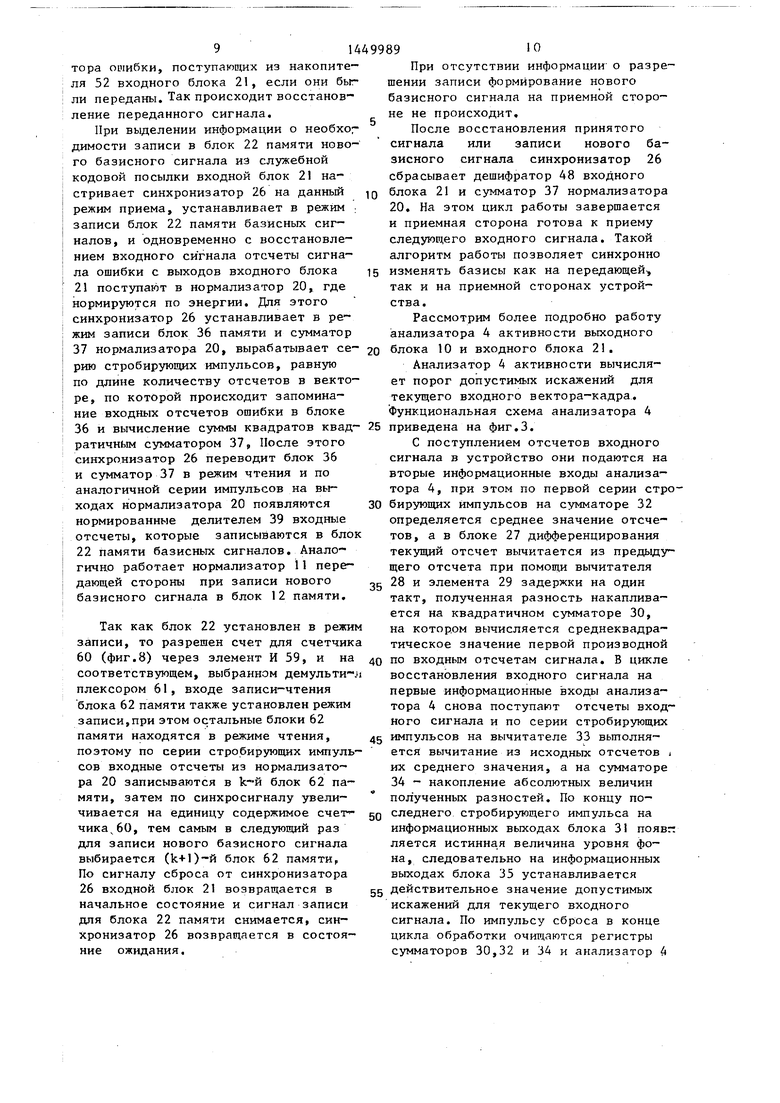

Устройство для передачи и приема информации на передающей стороне (фиг.1) содержит формирователь I порогового сигнала, первый блок 2 памяти, первый пороговый блок 3, ана лизатор 4 активности, второй пороговый блок 5, квадратичньш сумматор 6, второй блок 7 памяти, вычитатель 8, четвертый блок 9 памяти, выходной блок 10, нормализатор 11, третий блок 12 памяти базисных сигналов, корреляторы 13, - вьшолненные на умножителях 14 и сумматорах 15, умножители 16,-16„, сумматор 17 и синхронизатор 18, канал 19 связи; на приемной стороне (фиг.2) устройство содержит нормализатор 20, входной блок 21, первый блок 22 памяти базисных сигналов, второй блок 23 памяти, умножители 24,--24„, сумматор 25 и синхронизатор 26.

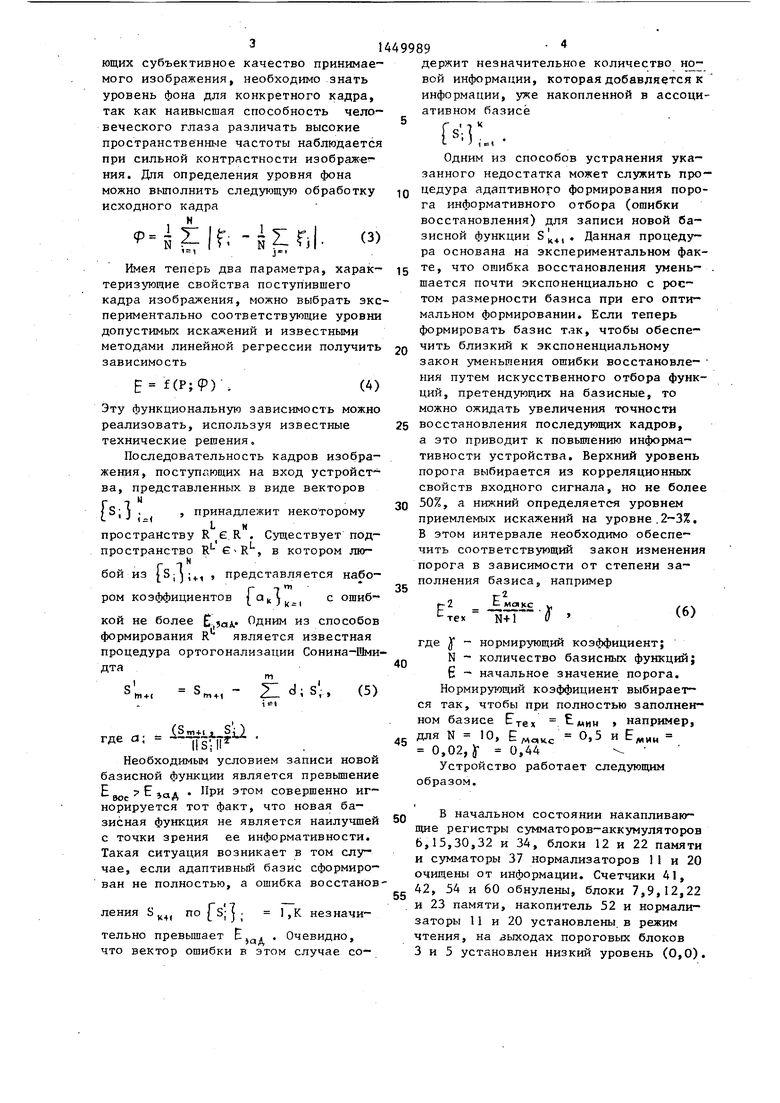

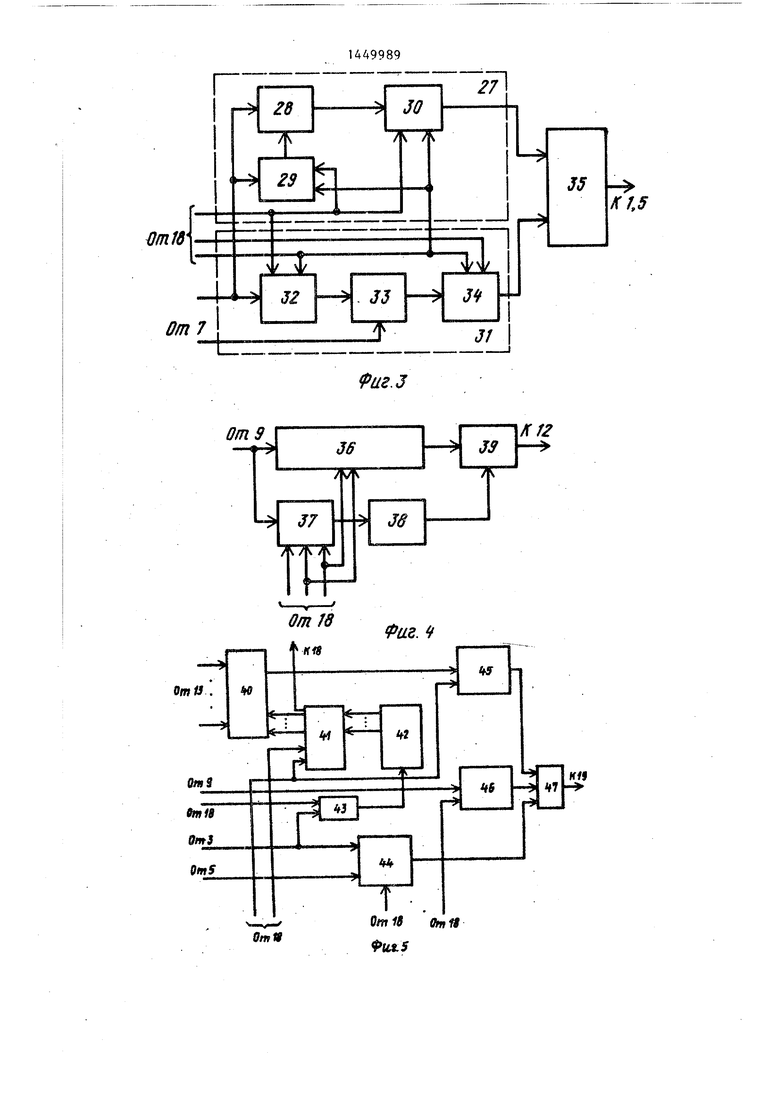

Анализатор активности (фиг.З) содержит блок 27 дифференцирования, выполненный на первом вьгчйтателе 28 элементе 29 задержки и первом квадра тичном сумматоре 30, блок 31 выделения среднего, выполненный на втором сумматоре-аккумуляторе 32, втором вычитателе 33 и третьем сумматоре 34 абсолютных величин, и блок 35 памяти порюгового сигнала.

Нормализатор (фиг.4) содержит блок 36 памяти, квадратичньй сумма

10

15

20

25

30

35

40

45

50

тор 37, вычислитель 38 квадратичного корня и делитель 39.

Выходной блок (фиг.З) содержит коммутатор 40, второй 41 и первьй 42 счетчики, элемент И 43, генератор 44 служебньк посылок, первый 43 и второй 46 кодеры и сумматор .47.

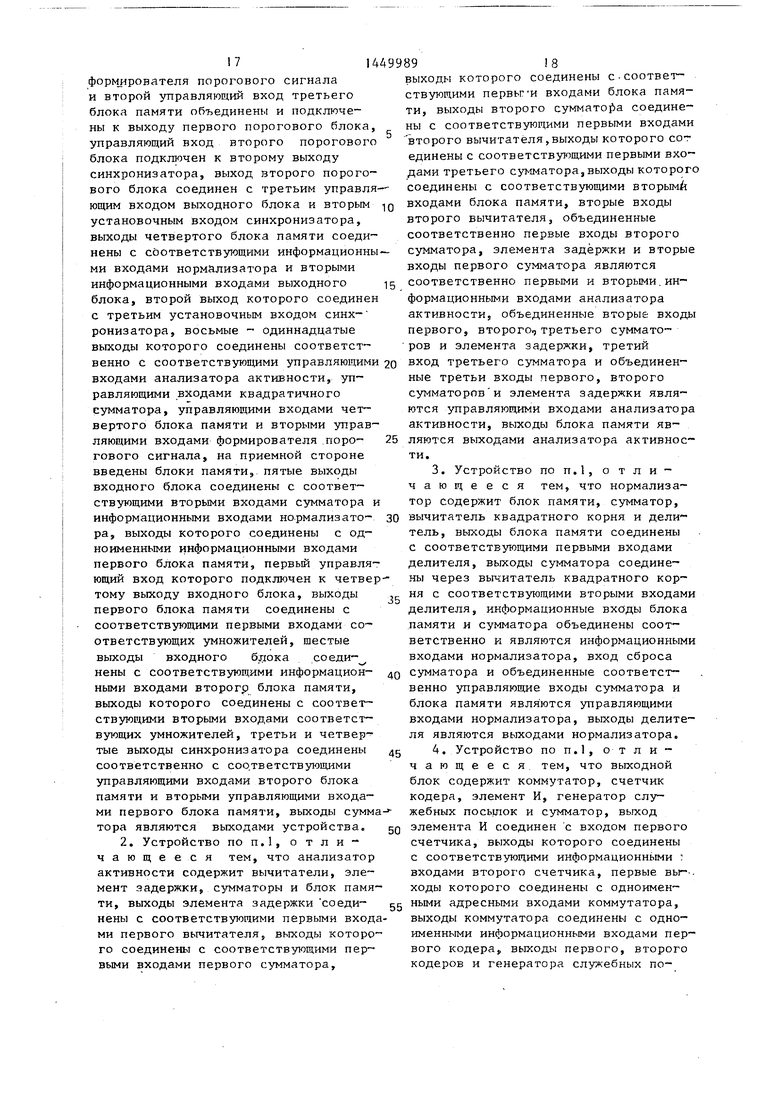

Входной блок (фиг.6) содержит дешифратор 48 служебных посылок, де- мультиплексор 49, первый 30 и второй 51 декодеры и накопитель 32.

Формирователь порогового сигнала (фиг.7) содержит элемент И 33, счетчик 34, делитель 33, блок 36 памяти, блок 37 сравнения и переключатель 38.

Блок памяти базисных сигналов (фиг.8) содержит элемент И 39, счетчик 60, демультиплексор 61 и элементы памяти.

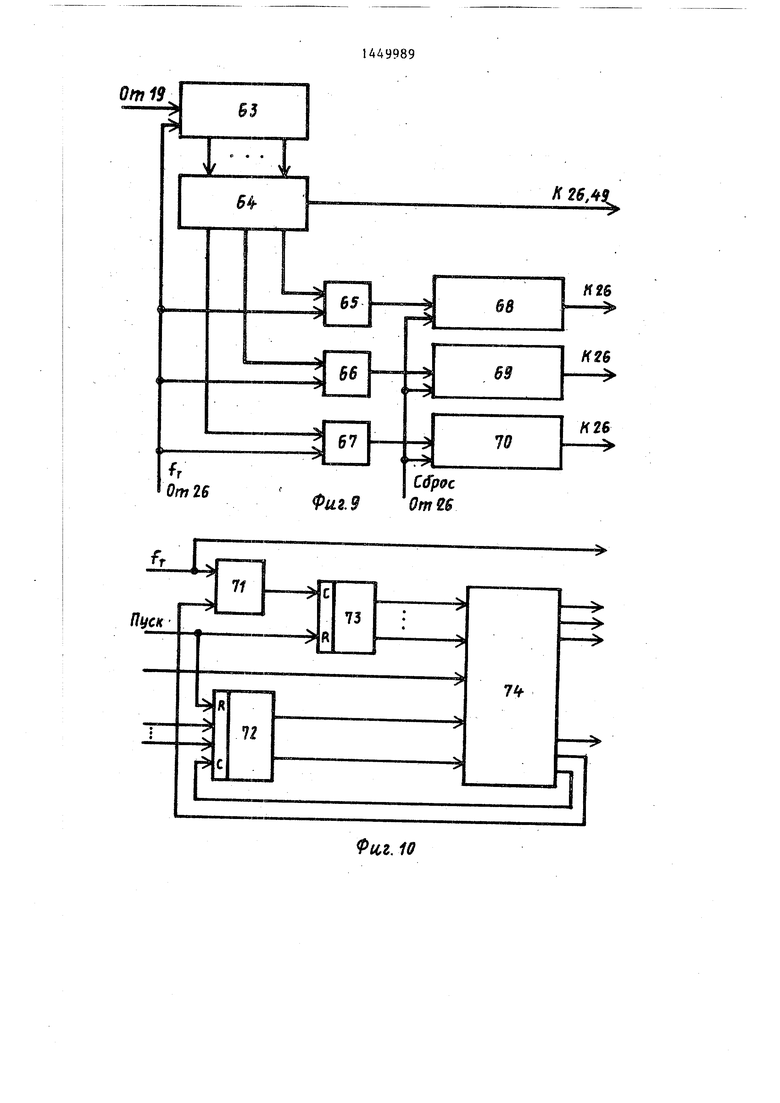

Дешифратор служебных посылок (фиг.9) содержит регистр 63 сдвига, дешифратор 64, элементы И 65-67 и триггеры 68-70.

Синхронизатор (фиг.10) содержит элемент И 71, блок 72 промежуточной памяти, счетчик 73 и блок 74 постоянной памяти.

Принципы построения устройства следующие. Специфическая особенность человеческого зрения позволяет существенно сократить затраты двоичных единиц информации при передаче изоб-. ражения, содержащего значительное количество высших пространственных частот.

Простейшим индикатором в этом слут чае может быть пространственное дифференцирование. Оператор дифференцирования для дискретного представления кадра изображения имеет вид разностного оператора и может быть определен как по строкам-так и по столбцам, если использовать большее количество точек изображения.

Например для строк

.,

(1)

где ; - отсчеты кадра изображения.

Осреднение квадратов локальных производных по формуле 1 Д- ,Г;

N

-ж

(2)

дает средний уровень (долю) высших пространственных частот в исходном сигнале.

Для более точного определения порога допустимых искажений, не ухудшающих субъективное качество принимаемого изображения, необходимо знать уровень фона для конкретного кадра, так как наивысшая способность человеческого глаза различать высокие пространственные частоты наблюдается при сильной контрастности изображен ния. Для определения уровня фона можно выполнить следующую обработку исходного кадра

ij

(р i Т I if. - I 5 Г-1 (3) N П N Jl-

Имея теперь два параметра, характеризующие свойства поступившего кадра изображения, можно выбрать экспериментально соответствующие уровни допустимых искажений и известными методами линейной регрессии получить зависимость

Е(Р;Ф).(4)

Эту функциональную зависимость можно реализовать, используя известные технические решения.

Последовательность кадров изображения, поступ 1ющих на вход устройства, представленных в виде векторов

U

J ( (

, принадлежит некоторому

L N

пространству . R . Существует подпространство R - , в котором лю. г

бой из , , представляется набором коэффициентов {оцТ с ошиб

кой не более jciA Одним из способов формирования R является известная процедура ортогонализации Сонина-Шмидта

Ж+(

S

ГП+1

- 2Id;s ,, (5)

(Sni-H , Si )

где а;

Необходимым условием записи новой базисной функции является превышение Е 7 Е зад этом совершенно игнорируется тот факт, что новая базисная функция не является наилучшей с точки зрения ее информативности. Такая ситуация возникает в том случае, если адаптивный базис сформирован не полностью, а ошибка восстанов

ления S , по fS; . 1,К незначительно превьшает

JaA

Очевидно,

что вектор ошибки в этом случае со-

0

держит незначительное количество новой информации, которая добавляется к информации, уже накопленной в ассоциативном базисе

г I -, к

Г,-..

Одним из способов устранения указанного недостатка может служить процедура адаптивного формирования порога информативного отбора (ошибки восстановления) для записи новой базисной функции S|,, Данная процедура основана на экспериментальном фак- 5 те, что ошибка восстановления умень- . шается почти экспоненциально с ростом размерности базиса при его оптимальном формировании. Если теперь формировать базис так, чтобы обеспечить близкий к экспоненциальному закон уменьшения ошибки восстановле- ния путем искусственного отбора функций, претендующих на базисные, то можно ожидать увеличения точности восстановления последующих кадров, а это приводит к повьшению информативности устройства. Верхний уровень порога выбирается из корреляционных свойств входного сигнала, но не более 50%, а нижний определяется уровнем приемлемых искажений на уровне . 2-3%, В этом интервале необходимо обеспечить соответствующий закон изменения порога в зависимости от степени за-

5

0

35

полнения базиса, например

Мр1К

N+1

(6)

0

где J - нормирующий коэффициент;

N - количество базисных функций; 6 - начальное значение порога, Нормирующий коэффициент выбирается так, чтобы при полностью заполненном базисе Е-гех Е ,„« например, для N 10, Ед,дкс 05 и /«ин 0,02, If 0,44

Устройство работает следующим образом.

В начальном состоянии накапливающие регистры сумматоров-аккумуляторов 6,15,30,32 и 34, блоки 12 и 22 памяти и сумматоры 37 нормализаторов 11 и 20 очищены от информации. Счетчики 41, 42, 54 и 60 обнулены, блоки 7,9,12,22 и 23 памяти, накопитель 52 и нормализаторы 11 и 20 установлены, в режим тения, на зыходах пороговых блоков 3 и 5 установлен низкий уровень (0,0),

5I4A99896

Синхронизация отдельных блоков устрой- на входах пороговых блоков 3 и 5,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Устройство для ассоциативного сжатия информации | 1984 |

|

SU1170482A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056244A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Устройство для обработки изображений | 1989 |

|

SU1772806A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Цифровой анализатор сигнала | 1988 |

|

SU1619297A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

Изобретение относится к электросвязи и может использоваться в телеметрических системах для ассоциативного сжатия передаваемой информации. Изобретение позволяет повысить информативность устройствао Устройство осуществляет сжатие на передающей стороне передаваемой информации и восстановление ее. на приемной стороне. Устройство содержит на передающей стороне формирователь 1 порогового сигнала, блоки 2,7,9,12 памяти, пороговые блоки 3,5, анализатор 4 активности, квадратичный сумматор 6, вычитатель 8, выходной блок 10, нормализатор 11, корреляторы 13, выполненные на умножителях 14 и сумматорах 13, умножители 16, сумматор 17 и синхронизатор 18. 5 з.п. ф-лы, 11 ил. (Л ( со 00 со

ства осуществляется синхронизаторами 18 и 26, тактируемыми одинаковой опорной частотой f. Синхронизаторы

находятся в состоянии ожидастробируемых синхронизаторо; 18. Если ошибка восстановления не больше допустимого уровня искажений, задаваемого анализатором 4 активности для текущего входного кадра, то соответствующие уровни (0,0) пороговых блоков 3 и 5 настраивает выходной

18 и 26 ния.

По сигналу Пуск, запускающему синхронизатор 18, входной вектор- кадр поступает в виде отсчетов парал-ю блок 10 и синхронизатор 18 на переда- лельного цифрового кода (к кратно чу только коэффициентов разложения степени двойки, например к 128) входного сигнала и служебной информа- в анализатор 4 активности и блок 7 па- ции, соответствующей данному режиму мяти сигнала, где запоминается и . передачи (фиг.11). В этом случае не одновременно подается на объединенные15 производится действий по изменению информационные входы умножителей 14. порога информативности , , выра- На другие входы умножителей 14 из батываемого формирователем Г порого- блока 12 памяти поступают цифровые вого сигнала. После передачи коэффи- отсчеты базисных сигналов (сначала циентов синхронизатор 18 вырабатыва- нулевые) синхронно с отсчетами вход-20 ет импульс сброса, который очищает

ного сигнала. Результаты умножений накапливаются сумматорами 15. Этот режим работы обеспечивается подачей соответствующих серий стробирующих импульсов от синхронизатора 18 на входы управления блоков 4,7,12 и 15, а также предварительной установкой в режим записи блока 7. После выполнения данного цикла работы блок 7 переводится в режим Чтение.

По завершению накопления результатов умножений на сумматорах 15 полученные коэффициенты разложения входного сигнала по базисным сигналам устанавливаются на входах умножителей 16 и на входах выходного блока 10.

После вычисления коэффициентов на умножителях 16 и сумматоре 17 происходит покоординатное восстановление входного сигнала (5), а на вы- читателе 8 выполняется покоординатное

регистры сумматоров 6,15,30, 32 и 34, а также стробирует пороговые блоки 3 и 5, чтобы установить на их выходах нулевые.уровни сигналов. На

25 этом цикл преобразования завершается и устройство готово к приему следующего входного вектора-кадра. Синхро- низатор 18 возвращается в исходное состояние.

30 Если величина ошибки превышает заданную ET-J , но меньше Е то управляющие сигналы пороговых блоков 3 и 5 заставляют выходной блок 10 и синхронизатор 18 кодировать и пере35 давать коэффициенты разложения и от- счеты вектора ошибки в канал 19 связи с соответствующей служебной информацией для приемной стороны. Пороговый блок 3 (уровни 1,0) не активизиг

40 рует свой выход, поэтому синхрониза-. тор 18 не вырабатывает в этом случае управляющих сигналов для нормализатора 11 и формирователя 1, использу40 рует свой выход, поэтому синхрониза-. тор 18 не вырабатывает в этом случае управляющих сигналов для нормализатора 11 и формирователя 1, использушает

сравнение исходного сигнала блока 7 емых для записи нового базисного сиг- с его восстановленной копией с после- 45 нала и изменения текущей величины E, дующим запоминанием результатов вычитания в блоке 9 памяти ошибки и накоплением суммы квадратов отсчетов вектора ошибки на квадратичном сумматоре 6. Этот цикл работы осуществля- gQ ется подачей серии синхронных импульсных последовательностей на управляю щие входы блоков 6,7,9 и 12, причем блок 9 предварительно переводится синхронизатором 18 в режим записи. gg

По завершении операции накопления базисного сигнала, содержащейся в со- полученная величина серднеквадратиче - ской ошибки сравнивается с пороговыми значениями, которые установлены

Когда ошибка восстановления превы- (порог информативности), то активнь е уровни (1,1) сигналов с выходов пороговых блоков 3 и 5 на- : - страивают выходной блок 10 и синхронизатор 18 на кодирование и передачу в канал 19 связи коэффициентов разложения, отсчетов вектора ошибки, а также информации о записи нового

ответствующей служебной кодовой посылке для приемной стороны (фиг.П) Одновременно с кодированием в этом

стробируемых синхронизаторо; 18. Если ошибка восстановления не больше допустимого уровня искажений, задаваемого анализатором 4 активности для текущего входного кадра, то соответствующие уровни (0,0) пороговых блоков 3 и 5 настраивает выходной

блок 10 и синхронизатор 18 на переда- чу только коэффициентов разложения входного сигнала и служебной информа- ции, соответствующей данному режиму передачи (фиг.11). В этом случае не производится действий по изменению порога информативности , , выра- батываемого формирователем Г порого- вого сигнала. После передачи коэффи- циентов синхронизатор 18 вырабатыва- ет импульс сброса, который очищает

регистры сумматоров 6,15,30, 32 и 34, а также стробирует пороговые блоки 3 и 5, чтобы установить на их выходах нулевые.уровни сигналов. На

25 этом цикл преобразования завершается и устройство готово к приему следующего входного вектора-кадра. Синхро- низатор 18 возвращается в исходное состояние.

30 Если величина ошибки превышает заданную ET-J , но меньше Е то управляющие сигналы пороговых блоков 3 и 5 заставляют выходной блок 10 и синхронизатор 18 кодировать и пере35 давать коэффициенты разложения и от- счеты вектора ошибки в канал 19 связи с соответствующей служебной информацией для приемной стороны. Пороговый блок 3 (уровни 1,0) не активизиг

40 рует свой выход, поэтому синхрониза-. тор 18 не вырабатывает в этом случае управляющих сигналов для нормализатора 11 и формирователя 1, использу емых для записи нового базисного сиг- 45 нала и изменения текущей величины E, gQ gg

шает

емых для записи нового базисного сиг- нала и изменения текущей величины E,

Когда ошибка восстановления превы- (порог информативности), то активнь е уровни (1,1) сигналов с выходов пороговых блоков 3 и 5 на- : - страивают выходной блок 10 и синхронизатор 18 на кодирование и передачу в канал 19 связи коэффициентов разложения, отсчетов вектора ошибки, а также информации о записи нового

базисного сигнала, содержащейся в со-

ответствующей служебной кодовой посылке для приемной стороны (фиг.П) Одновременно с кодированием в этом

/

режиме передачи активный уровень с выхода порогового блока 3 устанавли вает режим записи в блоке 1-2 и отсчеты вектора ошибки через нормализатор 11 записывают в блок 12 памяти базисных сигналово Это выполняется под действием соответствующих синкро импульсов от синхронизатора 18, пода ваемых на входы управления блоков 9 12, при этом блок 9 установлен в режим чтения информации.

Параллельно с записью отсчетов нового базисного сигнала изменяется величина порога информативности для следующего базисного вектора. Уровень значимости определяется формирователем 1 следующим образом

N+T

Е:

т

(7)

где Е

&ОС

- полученная ошибка восстановления для последнего входного вектора-кадра. Для этого соответствующим импульсом от синхронизатора 18 увеличивается на единицу содержимое счетчика 54 (равное текущему количеству базисных сигналов, записанных в блоке 12) формирователя 1. Так как на первом входе элемента И 53 установлен высокий уровень сигнала от пороговог блока 3 (огаибка превысила порог информативности) , то счет разрешен. Далее вьтолняется деление текущей ошибки восстановления на число, записанное в счетчике 54, делителем 55 и запоминание полученного значения в блоке 56 по импульсу синхронизатор 18. Таким образом, на первых входах блока 57 сравнения устанавливается значение порога информативности, которое в следующем цикле обработки очередного входного вектора сравнивается с порогом допустимых искажений, определяемым анализатором 4 активности (начальное значение порога для первого входного вектора равно 0). Как было указано в начале цикла преобразования очередного вектора- кадра параллельно с запоминанием отсчетов входного вектора-кадра в блоке 7 памяти сигнала на вторые информационные входы анализатора 4 активности также поступают отсчеты входного сигнала. По окончании цикла приема кадра на выходах блока 27 дифференцирования (фиг.З) появляется среднее значение производной входног

10

449989

. 8

сигнала согласно (1) и (2), блок 31 вычисляет среднее значение входного сигнала на сумматоре 32. На втором цикле работы передающей стороны (восстановление кадра и сравнение его с исходным) блок 31 выделяет истинное значение уровня фона по указанной процедуре (3) (среднее значение сигнала вычитается вычит ателеМ 33 из отсчетов входного сигнала, а полученные разности суммируются по абсолютной величине сумматором 34) . При этом блок 35 формирует по известной функ- 15 циональной зависимости (4) порог до- . пустимых искажений. Таким образом, к началу операции оценивания точности восстановления на информационных выходах анализатора 4 активности и.

20 следовательно, на соответствующих

5

входах порогового блока 5 и формиро- вателя 1 устанавливается значение необходимого уровня допустимых иска жений для обрабатываемого в данньм

5 момент кадра изобретения. Если ошибка восстановления меньше «(0, , устанавливаемого анализатором 4, то блок 57 сравнения и переключатель 58 формируют порог допустимых искажений

0 Етех .равный Е„н По завершении цикла преобразования синхронизатор 18 сбрасьшает регистры сумматоров 6,15,30,32,34 и 37, затем стробирует пороговые блоки 3 и 5 и передающая сторона готова к обработке следующего вектора-кадра.

На приемной стороне с помощью входного блока 21 информация декоди-. руется и разделяется на коэффициенты, которые запоминаются в блоке 23 памяти коэффициентов, и на отсчеты вектора ошибки, если они были переданы. Кроме того, входной блок 21 выделяет управляющие сигналы из принятой

5 служебной информации для синхронизатора 26, которые настраивают синхронизатор 26 на соответствующий режим приема и запускают его.

После дешифрации управляющих и ин-

Q формационных сигналов .синхронизатор 26 стробирует блок 22 памяти базисных сигналов, аналогичный блоку 12 передающей стороны, и на умножителях 24 происходит покоординатное умножение отсчетов базисных сигналов на значения коэффициентов из блока 23, а на сумматоре 25 - покоординатное сложение цифровых значений сигналов со всех умножителей с отсчетами век-

0

5

ля 52 входного блока 21, если они были переданы. Так происходит восстановление переданного сигнала.

При выделении информации о необхог димости записи в блок 22 памяти нового базисного сигнала из служебной кодовой посылки входной блок 21 на- стривает синхронизатор 26 на данный режим приема, устанавливает в режим ; записи блок 22 памяти базисных сигналов, и одновременно с восстановлением входного си гнала отсчеты сигнала ошибки с выходов входного блока 21 поступают в нормализатор 20, где нормируются по энергии. Дпя этого синхронизатор 26 устанавливает в режим записи блок 36 памяти и сумматор

37 нормализатора 20, вырабатывает се- 20 блока 10 и входного блока 21. рию стробирующих импульсов, равную Анализатор 4 активности вычисля- по длине количеству отсчетов в векто- ет порог допустимых искажений для ре, по которой происходит запомина- текущего входного вектора-кадра, ние входных отсчетов ошибки в блоке Функциональная схема анализатора 4 36 и вычисление суммы квадратов квад- 25 приведена на фиг.З.

ратичным сумматором 37, После этого синхронизатор 26 переводит блок 36 и сумматор 37 в режим чтения и по аналогичной серии импульсов на вы ходах нормализатора 20 появляются нормированные делителем 39 входные отсчеты, которые записываются в бло 22 памяти базисных сигналов. Аналогично работает нормализатор 11 передающей стороны при записи нового базисного сигнала в блок 12 памяти.

С поступлением отсчетов входного сигнала в устройство они подаются на вторые информационные входы анализатора 4, при этом по первой серии стро 30 бирующих Импульсов на сумматоре 32 определяется среднее значение отсчетов, а в блоке 27 дифференцирования текущий отсчет вычитается из предыдущего отсчета при помощи вычитателя 28 и элемента 29 задержки на один такт, полученная разность накапливается на квадратичном сумматоре 30, на котором вычисляется среднеквадра- тическое значение первой производной

Так как блок 22 установлен в режим записи, то разрешен счет для счетчика

60 (фиг.8) через элемент И 59, и на 40 по входным отсчетам сигнала. В цикле соответствующем, выбранном демульти л восстановления входного сигнала на плексором 61, входе записи-чтения блока 62 памяти также установлен режим записи,при этом остальные блоки 62 памяти находятся в режиме чтения, поэтому по серии стробирующих импульсов входные отсчеты из нормализатора 20 записываются в k-й блок 62 памяти, затем по синхросигналу увеличивается на единицу содержимое счет , тем самым в следующий раз для записи нового базисного сигнала выбирается (К-И)-й блок 62 памяти, По сигналу сброса от синхронизатора выходах блока 35 устанавливается 26 входной блок 21 возвращается в gg действительное значение допустимых

искажений для текущего входного сигнала. По импульсу сброса в конце цикла обработки очищаются регистры сумматоров 30,32 и 34 и анализатор 4

первые информационные входы анализатора 4 снова поступают отсчеты входного сигнала и по серии стробирующих 45 импульсов на вычитателе 33 вьтолня- ется вычитание из исходных отсчетов их среднего значения, а на сумматоре 34 - накопление абсолютных величин полученных разностей. По концу последнего стробирующего импульса на информационных выходах блока 31 появляется истинная величина уровня фона, следовательно на информационных

50

начальное состояние и сигнал записи для блока 22 памяти снимается, синхронизатор 26 возвращается в состояние ожидания.

шении записи формирование нового базисного сигнала на приемной стороне не происходит.

После восстановления принятого сигнала или записи нового базисного сигнала синхронизатор 26 сбрасывает дешифратор 48 входного

блока 21 и сумматор 37 нормализатора 20. На этом цикл работы завершается и приемная сторона готова к приему следующего входного сигнала. Такой алгоритм работы позволяет синхронно

изменять базисы как на передающей-, так и на приемной сторонах устройства.

Рассмотрим более подробно работу анализатора 4 активности выходного

С поступлением отсчетов входного сигнала в устройство они подаются на вторые информационные входы анализатора 4, при этом по первой серии стро 30 бирующих Импульсов на сумматоре 32 определяется среднее значение отсчетов, а в блоке 27 дифференцирования текущий отсчет вычитается из предыдущего отсчета при помощи вычитателя 28 и элемента 29 задержки на один такт, полученная разность накапливается на квадратичном сумматоре 30, на котором вычисляется среднеквадра- тическое значение первой производной

35

40 по входным отсчетам сигнала. В цикле восстановления входного сигнала на выходах блока 35 устанавливается gg действительное значение допустимых

по входным отсчетам сигнала. В цикле восстановления входного сигнала на выходах блока 35 устанавливается действительное значение допустимых

первые информационные входы анализатора 4 снова поступают отсчеты входного сигнала и по серии стробирующих импульсов на вычитателе 33 вьтолня- ется вычитание из исходных отсчетов i их среднего значения, а на сумматоре 34 - накопление абсолютных величин полученных разностей. По концу последнего стробирующего импульса на информационных выходах блока 31 появляется истинная величина уровня фона, следовательно на информационных

снова готов к приему входной информации.

На фиг.5 приведена функциональная схема выходного блока 10, который ра ботает следующим образом.

Случай первьй. Е еос , , Пороговые блоки 3 и 5 не активизируют свои выходы (0,0). Синхронизатор 18 по нулевым уровням управляющих сиг- ю налов настраивается на передачу толь ко коэффициентов, генератор 44 служебных посылок по сигналам пороговых блоков 3 и 5 настроен на работу в данном режиме. Синхронизатор 18 вы- 15 рабатывает серию стробирующих импуль - сов для генератора 44, который при этом формирует на выходах служебдую информационную посьшку, сообщающую

тельно передаются коэффициенты и отсчеты вектора ошибки. Сначала аналогично первому случаю передается служебная информация, настраивающая приемные сторону на режим работы пере дающей стороны, далее следует пере- запись числа из счетчика 47 в счетчик 41, затем синхронизатор. В вырабатывает импульс счета для счетчика 42, но элемент И 43 не пропускает его на вход счетчика 42, после этого вырабатывается серия стробирующих импульсов для кодера 46 ошибки и блока 9 памяти ошибки, в результате чего в канал 19 связи через сумматор 47 передаются закодированные отсчеты вектора ошибки. Затем, аналогично первому случаю, передаются коэффициприемной стороне о передаче коэффици- -20енты и посылка о конце цикла переда- ентов. Одновременно с передачей слу-чи. После этого синхронизатор 18 вы- жебной информации происходит переза-полняет сброс передающей стороны и пись числа из счетчика 42 в вычитающий счетчик 41 по импульсу от синхронизатора 18 и затем попытка увеличе- 25Выходы пороговых блоков 3 и 5 находят- - НИН содержимого счетчика 42 по импуль--ся в активном состоянии. В этом слу- су счета от синхронизатора 18, но так как на втором входе элемента И 43

низкий уровень сигнала, то увеличение „.„ „„

содержимого счетчика 42 не произойдет.зожимого счетчика 42, так как на втоПосле передачи служебной информацииром входе элемента И 43 высокий уро- по серии стробирующих, импульсов, пода-переходит в состояние ожидания. Случай третий. ЕВОС .

чае работа выходного блока 10 полностью аналогична второму случаю, только вьтолняется увеличение содерваемых на соответЬтвующий вход кодера 45 коэффициентов и вход вычитания счетчика 41, происходит последовательный опрос коммутатором 40 соответствующих групп информационных входов, на которых установлены значения коэффициентов, и подключение их к информационным входам кодера 45 коэффициентов, который кодирует последние и посылает их через сумматор 47 в канал 19 связи. При установлении в счетчике 41 нулевого значения и активном уровне сигнала синхронизатора 18 на выходе Заем счетчика 41 появляется активный сигнал, который оповещает синхронизатор 18 о конце передачи, при этом синхрониза- тор 18 стробирует генератор 44, CQ формирующий сигнал конца передачи для приемной стороны (фиг.11); затем сбрасывает соответствующие блоки пе-i редающей стороны и переходит в состояние ожидания.

вень сигнала, и генератор 44 вырабатывает в этом случае служебную кодовую посылку для приемной стороны, 35 содержащую информацию о разрешении формирования нового базисного сигнала на приемной стороне. После появления сигнала Заем синхронизатор 18 до- записывает нормированные отсчеты век- 40 тора ошибки в блок 12, затем сбрасы-j вает соответствующие блоки передающей стороны и переходит в состояние ожидания.

45

55

На фиг,6 приведена функциональная схема входного блока 21 приемной сто-г роны. Дешифратор 48 выделяет служеб-; ную информацию из входного сигнала, определяет режим работы передающей стороны, по управляющим сигналам настраивает синхронизатор 26 на выработку соответствующих режиму приема синхронизирующих и стробирующих последовательностей импульсов, а также запускает синхронизатор 26, что обеспечивается соответствующей служебной кодовой последовательностью.

-тех - вое

Случай второй. E,g - - вое - - Уровни на выходах пороговых блоков 3 и 5 соответственно О и 1, следовательно передаются коэффициенты и отсчеты вектора ошибки. Сначала аналогично первому случаю передается служебная информация, настраивающая приемные сторону на режим работы пере дающей стороны, далее следует пере- запись числа из счетчика 47 в счетчи 41, затем синхронизатор. В вырабатывает импульс счета для счетчика 42, но элемент И 43 не пропускает его на вход счетчика 42, после этого вырабатывается серия стробирующих импульсов для кодера 46 ошибки и блока 9 памяти ошибки, в результате чего в канал 19 связи через сумматор 47 передаются закодированные отсчеты вектора ошибки. Затем, аналогично первому случаю, передаются коэффициенты и посылка о конце цикла переда- чи. После этого синхронизатор 18 вы- полняет сброс передающей стороны и Выходы пороговых блоков 3 и 5 находят- ся в активном состоянии. В этом слу-

енты и посылка о конце цикла пер чи. После этого синхронизатор 18 полняет сброс передающей стороны Выходы пороговых блоков 3 и 5 нахо ся в активном состоянии. В этом

переходит в состояние ожидания. Случай третий. ЕВОС .

енты и посылка о конце цикла переда- чи. После этого синхронизатор 18 вы- полняет сброс передающей стороны и Выходы пороговых блоков 3 и 5 находят- ся в активном состоянии. В этом слу-

„.„ „„

жимого счетчика 42, так как на вточае работа выходного блока 10 полностью аналогична второму случаю, только вьтолняется увеличение содерром входе элемента И 43 высокий уро-

вень сигнала, и генератор 44 вырабатывает в этом случае служебную кодовую посылку для приемной стороны, содержащую информацию о разрешении формирования нового базисного сигнала на приемной стороне. После появления сигнала Заем синхронизатор 18 до- записывает нормированные отсчеты век- тора ошибки в блок 12, затем сбрасы-j вает соответствующие блоки передающей стороны и переходит в состояние ожидания.

На фиг,6 приведена функциональная схема входного блока 21 приемной сто-г роны. Дешифратор 48 выделяет служеб-; ную информацию из входного сигнала, определяет режим работы передающей стороны, по управляющим сигналам настраивает синхронизатор 26 на выработку соответствующих режиму приема синхронизирующих и стробирующих последовательностей импульсов, а также запускает синхронизатор 26, что обеспечивается соответствующей служебной кодовой последовательностью.

Таким образом, групповой цифровой входной сигнал поступает на регистр

63сдвига, тактируемый опорной частотой f. Дешифратор 64 выделяет два сигнала настройки, которые запоминаются сначала в триггере 68, а затем в триггере 69, После этого дешифратор

64формирует сигнал запуска синхронизатора 28. В конце информационного кадра дешифратор 64 выделяет маркер конца передачи, который запоминается в триггере 70 и информирует синхронизатор 26 о конце цикла приема.

В конце процесса обработки кадра синхронизатор 26 сбрасывает триггеры 68-70 в исходное состояние.

В случае передачи одних коэффициентов выходы дешифратора 48 не актив зированы (0,0), выход синхронизатора 26 не активен, поэтому демультиплек- сор 42 подключает информационные входы входного блока 21 через декоде 51 коэффициентов к блоку 23 памяти коэффициентов, предварительно установленный в режим записи, в который по серии синхроимпульсов записываются декодированные декодером 51 отсчеты коэффициентов.

Если количество коэффициентов . меньше максимального, то после сигна ла передачи на выходе декодера 51 устанавливается нулевое значение, а синхронизатор 26 заполняет оставшиеся ячейки памяти блока 23 нулевыми отсчетами и переводит блок 23 в ре-

жим чтения. Поэтому принятые коэффи- gствующих выходах блока 74 появляются циенты записываются всегда в строгоуправляющие импульсные последователь- определенные ячейки памяти согласноности. Три адресных входа блока 74 их порядковому номеру. После завер-служат входами управления (переклю- шения цикла восстановления синхрониза -чения последовательностей) синхрони40

тор 26 устанавливает дешифратор 48 в исходное состояние, а сам переходит в состояние ожидания.

Если были переданы отсчеты вектора ошибки и коэффициенты (уровни настройки 0,1), то дешифратор 48 и синхронизатор 26 через демультиплек- сор 49, при установленном на его адресном входе сигнале синхронизатора 26, и декодер 50 ошибки записывают отсчеты вектора ошибки в накопитель 52 ошибки, для которого установлен режим записи и вырабатываются стробиру- ющие импульсы. Затем принимаются коэффициенты аналогично рассмотренной процедуре. Если число коэффициентов меньше максимального j, то после сигнала конца передачи синхронизатор 26 заполняет нулями оставшиеся ячейки памяти блока 23. Синхронизатор 26 в

затором 18 (26), управляемым пороговыми блоками 3 и 5 и выходным блоком 10 (входным блоком 21 для приемной стороны). Синхронизатор 18 (26) формирует управляющие сигналы до тех

45 пор, пока на выходе блокировки блока

74 не установится низкий уровень, запрещающий прохождение тактовой частоты на вход счетчика 73.

Переключение (настройка) синхрони50 затора 18 (Й6) происходит путем

стробирования блока 72 памяти сигналом записи с соответствующего выхода блока 74. В блок 72 памяти при этом записываются сигналы, установленные

55 на его входах. Очистка содержимого блока 72 памяти выполняется при запуске синхронизатора 18 (26).

Сравнение эффективности работы устройства с базовым объектом выпол-

0

20

этом режиме приема не формирует упрочняющих сигналов для нормализатора 20, блока 21 для записи отсчетов вектора ошибки, так как формирование нового базисного сигнала запрещено. После завершения цикла восстановления синхронизатор 26 устанавливает дешифратор 48 в исходное состояние, а сам переходит в состояние ожидания.

В третьем случае при передаче отсчетов вектора ошибки, коэффициентов и служебной информации о записи нового базисного сигнала работа входного

15 блока 21 полностью аналогична рассмотренной, только разрешается запись нового базисного сигнала через нормализатор 20 в блок 22 памяти базисных сигналов. После завершения цикла формирования нового базисного сигнала синхронизатор 26 устанавливает дешифратор 48 в исходное состояние, а сам переходит в состояние ожидания. Синхронизатор 18 (26) работает

25 следующим образом. По импульсному сигналу запуска сбрасывается счетчик 73 и на соответствующем выходе блокировки блока 74 постоянной памяти, подключенном к второму входу элемента И 71, устанавливается высокий уровень сигнала, импульсы тактовой частоты поступают на счетный вход счетчика 73, который начинает перебирать адрес блока 74, и на соответ30

затором 18 (26), управляемым пороговыми блоками 3 и 5 и выходным блоком 10 (входным блоком 21 для приемной стороны). Синхронизатор 18 (26) формирует управляющие сигналы до тех

пор, пока на выходе блокировки блока

74 не установится низкий уровень, запрещающий прохождение тактовой частоты на вход счетчика 73.

Переключение (настройка) синхронизатора 18 (Й6) происходит путем

стробирования блока 72 памяти сигналом записи с соответствующего выхода блока 74. В блок 72 памяти при этом записываются сигналы, установленные

на его входах. Очистка содержимого блока 72 памяти выполняется при запуске синхронизатора 18 (26).

Сравнение эффективности работы устройства с базовым объектом выпол-

151449989 16

нялось при одинаковом входном сигма- соединены через канал связи с соот- ле. В качестве входного сигнала ветствующими информационными входами использовался бельй шум, пропущенный входного блока приемной стороны, через низкочастотный фильтр с задан- первый - четвертый выходы и управля- ными параметрами. При размерности ющие входы входного блока соединены входного вектора 64 точки и заданной соответственно с входом Пуск, пер- средней точности восстановления 1% вым - третьим установочньми входами формирование базиса предлагаемого и соответствующими первыми выходами устройства завершилось на 23-м векто- о синхронизатора, вторые выходы синх- ре, а известного - на 31-м йекторе, ронизатора соединены с соответствую- следовательно степень сжатия возросла щими управляющими входами нормализа- почти на 30%. Кроме того, сокращение. тора, умножители, выходы которых числа базисных векторов, требующих .соединены с соответствующими первыми дорогостоярдах устройств памяти, при- 15 входами сумматора, тактовый вход водит к уменьшению затрат на них, а синхронизатора приемной стороны яв- также сокращает время обработки сиг- ляется вторым тактовым входом уст- налов после формирования базиса. Та- ройства, отличающееся КИМ образом, информативность прёдло-, тем, что, с целью повышения информа- женногр устройства вьаче не менее, 20 тивности устройства,. в него на пере- чем на 100% информативности извест- дающей стороне введены формирователь ного.порогового сигнала, анализатор активности, второй пороговый блок, квад- Формула изобретения ратичный сумматор, вычитатель и чет25 вертый блок памяти, выходы второго

входами сумматора, выходы коррелято- gQ с соответствующими вторыми входами ров соединены с соответствующими пер- вычитателя, выходы которого соеди- выми информационными входами выходно- нены с соответствующими информаци- го блока, информационные входы вто- онными входами четвертого блока па- рого блока памяти, вход Пуск и так- мяти и квадратичного сумматора, вы- товый вход синхронизатора являются gg ходы которого соединены с соответ- соответственно информационными входа- ствующими вторыми информационными ми, входом Пуск и первым тактовым . входами первого, второго пороговых входом устройства, первые выходы блоков и формирователя порогового выходного блока передающей стороны сигнала, первый управляющий вход

1714А998918

формирователя порогового сигнала выходы которого соединены с-соответствующими первьг и входами блока памяти, выходы второго сумматора соединены с соответствующими первыми входами isTOporo вычитателя,выходы которого cor единены с соответствующими первыми вхо-

и второй управляющий вход третьего блока памяти объединены и подключены к выходу первого порогового блока, управляющий вход второго порогового блока подключен к второму выходу синхронизатора, выход второго порогового блока соединен с третьим управля--дами третьего сумматора,выходы которого соединены с соответствующими вторыми

ющим входом выходного блока и вторым 1Q входами блока памяти, вторые входы

установочным входом синхронизатора, выходы четвертого блока памяти соединены с соответствующими информационными входами нормализатора и вторыми информационными входами выходного 15 блока, второй выход которого соединен с третьим установочным входом синх- ронизатора, восьмые - одиннадцатые выходы которого соединены соответственно с соответствующими управляющими 20 вход третьего сумматора и объединенвходами анализатора активности, управляющими входами квадратичного сумматора, управляющими входами четвертого блока памяти и вторыми управляющими входами формирователя порогового сигнала, на приемной стороне введены блоки памяти, пятые выходы входного блока соединены с соответствующими вторыми входами сумматора и информационными входами нормализатора, выходы которого соединены с одноименными информационными входами первого блока памяти, первый управляющий вход которого подключен к четвер тому выходу входного блока, выходы первого блока памяти соединены с соответствующими первыми входами со™ ответствующих умножителей, шестые выходы входного блока соединены с соответствующими информацион- 40 сумматора и объединенные соответстными входами второгр блока памяти, выходы которого соединены с соответ ствующими вторыми входами соответствующих умножителей, третьи и четвер- тые выходы синхронизатора соединены соответственно с соответствующими управляющими входами второго блока памяти и вторыми управляющими входами первого блока памяти, выходы сумма тора являются выходами устройства,

нены с соответствующими первыми входами первого вычитателя, выходы которого соединены с соответствующими первыми входами первого сумматора.

дами третьего сумматора,выходы которого соединены с соответствующими вторыми

второго вычитателя, объединенные соответственно первые входы второго сумматора, элемента задержки и вторые входы первого сумматора являются соответственно первыми и вторыми.информационными входами анализатора активности, объединенные вторые входы первого, второго,третьего суммато- ров и элемента задержки, третий

ные третьи входы первого, второго сумматоров и элемента задержки являются управляющими входами анализатора активности, выходы блока памяти являются выходами анализатора активности.

вычитатель квадратного корня и дели5

тель, выходы блока памяти соединены с соответствующими первыми входами делителя, выходы сумматора соединены через вычитатель квадратного корня с соответствующими вторыми входами делителя, информационные входы блока памяти и сумматора объединены соответственно и являются информационными входами нормализатора, вход сброса

венно управляющие входы сумматора и блока памяти являются управляющими входами нормализатора, выходы делителя являются выходами нормализатора, 4, Устройство по П.1, отличающееся тем, что выходной блок содержит коммутатор, счетчик кодера, элемент И, генератор слу жебных посьщок и сумматор, выход элемента И соединен с входом первого счетчика, выходы которого соединены с соответствующими информационньгми : входами второго счетчика, первые вы- , ходы которого соединены с одноименвыходы коммутатора соединены с одноименными информационными входами первого кодера, выходы первого, второго кодеров и генератора служебных посылок соответственно с одноименными первыми, вторыми и третьими входами сумматора, информационные входы коммутатора и второго кодера являются соответственно первыми и вторыми информационными входами выходного блока, первый вход элемента И, пер- вый управляющий вход второго счетчика, объединенные второй управляющий вход второго счетчика и управляющий вход первого кодера, .первый вход генератора служебных посылок и управляющий вход второго кодера являются перв1ыми управлягадими входами выходного блока, объединенные вторые входы элемента И и генератора служебных посылок и третий вход генератора служебных посылок являются со-

щий вход демультиплексора, управляющий вход второго декодера, первый управляющий вход накопителя и объеди- g ненный управляющий вход второго декодера и накопителя являются управляющими входами входного блока, второй, третий, четвертьй и первый выходы дешифратора, выходы накопителя и выходы

10 второго декодера являются соответственно первьп - четвертым, пятым и шестым выходами входного блока.

15 порогового сигнала содержит элемент И, счетчик,делитель, блок памяти, блок сравнения и переключатель,выход эл-емен- та И соединен с входом счетчика,выходы которого соединены с одноименными

ответственно вторым и третьим управ-. 20 первыми входами делителя, выходы кото- ляющими входами выходного блока, рого соединены с одноименными информационными входами блока памяти, выходы которого соединены с одноименными первыми входами блока сравне- 25 ния и первыми информационными входами переключателя, выход блока сравнения соединен с управляющим входом переключателя, объединенные соответственно вторые входы блока сравнений вый выход дешифратора соединен с пер- 30 и вторые информационные входы перв- BbW управляющим входом демультиплек- ключателя, вторые входы делителя и сора, первые и вторые выходы которого соединены с соответствующими информационными входами соответственно nepBiJro и второго декодеров, выходы

выходы сумматора и второй выход рого счетчика являются соответственно первыми и вторыми выходами выходного блока.

первый вход элемента И являются соответственно первыми, вторыми информационными и первым управляющим 35 входами формирователя порогового

первый вход элемента И являются соответственно первыми, вторыми информационными и первым управляющим 35 входами формирователя порогового

первого декодера соединены с одноимен-сигнала, второй вход элемента ными информационными входами накопите-И и управляющий вход блока памяти ля,информационные входы демультиплек-являются вторыми управляющими входа- сора и дешифратора объединены соответ-,ми формирователя порогового сигнала, ственно и являются информационными вхо«- 40выходы переключателя являются дами входного блока,тактовый вход и входвыходами формирователя порогового сброса дешифратора, второй управляю сигнала.

щий вход демультиплексора, управляющий вход второго декодера, первый управляющий вход накопителя и объеди- ненный управляющий вход второго декодера и накопителя являются управляющими входами входного блока, второй, третий, четвертьй и первый выходы дешифратора, выходы накопителя и выходы

второго декодера являются соответственно первьп - четвертым, пятым и шестым выходами входного блока.

порогового сигнала содержит элемент И, счетчик,делитель, блок памяти, блок сравнения и переключатель,выход эл-емен- та И соединен с входом счетчика,выходы которого соединены с одноименными

20 первыми входами делителя, выходы ко рого соединены с одноименными информационными входами блока памяти, выходы которого соединены с одноимен ными первыми входами блока сравне- 25 ния и первыми информационными входами переключателя, выход блока сравнения соединен с управляющим входом переключателя, объединенные соответственно вторые входы блока сравнений 30 и вторые информационные входы перв- ключателя, вторые входы делителя и

первый вход элемента И являются соответственно первыми, вторыми информационными и первым управляющим 35 входами формирователя порогового

сигнала, второй вход элемента И и управляющий вход блока памяти являются вторыми управляющими входа- ми формирователя порогового сигнала, 40выходы переключателя являются выходами формирователя порогового сигнала.

mid

От 9

JS

W

0m Id

Omti ,

-r

€-г

М

втЗ

9пП От)

Г

4J

0m tf

as.J

jy

Kf2

Фа.г.

г

45

Kff

4J

т.

0m f« йп ff (0.5

К 26

и.г.6

fas. 7 От 18(26)

От 26 О т IS .

K13f2 }

иг.З

Ofn19.

65

J

54

65

56

67

fr 0m 26

Фиг,9

К 26AS

68

/Г26

69

K2B

10

H26

Cffpoc 0m ZS

PlCZ, 10

| Авторское свидетельство СССР № | |||

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1989-01-07—Публикация

1987-03-20—Подача