Изобретение относится к вычислительной технике и может быть использовано в процессорных устройствах ЭВМ. Известны способы и устройства умножения двоично-десятичных кодов, заключающиеся в сложении кодов тетрад множимого с кодами тетрад регистра частичных произведений столько раз, сколько единиц содержится в младшей тетраде регистра множителя, с последующим сдвигом кодов регистров частичных произведений и множителя на один десятичный разряд вправо. Указанные процедуры повторяется столько раз, сколько десятичных разрядов содержит регистр множителя. Основные способы и устройства рассмотрены в книге М.А.Карцев «Арифметика цифровых машин» М., Наука, 1969, стр.346-354. Основным недостатком известных способов выполнения умножения с формированием частичных произведений на основе суммирующих устройств является необходимость выполнения корректировки результатов сложения, если результат сложения i-й тетрады будет равен или больше десяти единиц. Указанная процедура снижает быстродействие выполнения операций умножения в два - три раза. Известны также устройства суммирования, в которых коррекция кода исключается за счет увеличения оборудования, что является их недостатком. Пример такого устройства, который является прототипом предложенного изобретения, приведен на стр.168 рис.2-16 названного выше источника. Кроме того, для выполнения операции умножения с использованием противопоставляемого устройства требуется включение в состав оборудования каждого десятичного разряда двадцати RS-триггеров, что также является недостатком прототипа.

Целью изобретения является повышение быстродействия выполнения операции умножения без существенного увеличения оборудования.

Для достижения поставленной цели предложен способ умножения двоично-десятичных кодов, отличающийся тем, что множитель и множимое принимают соответственно в регистры А и B в кодах 8, 4, 2, 1 и одновременно преобразуют коды второго, третьего и четвертого двоичных разрядов каждой тетрады триггеров регистра В и младшей тетрады регистра А в четные десятичные числа 8, 6, 4, 2, с помощью матрицы умножения получают произведение, равное одному из десятичных чисел 4, 8, 12, 16, 24, 32, 36, 48 и 64, полученное число преобразуют в двоично-десятичный код; по первому временному такту определяют наличие нулевых значений триггеров первого-четвертого разрядов младшей тетрады А, при нулевых значениях упомянутых триггеров операцию умножения кода регистра В на код младшей тетрады регистра А не производят, а выполняют сдвиг кодов регистров А и С на четыре двоичных разряда в сторону младших разрядов, если код тетрады А не равен нулю, то суммируют двоично-десятичный код разряда единиц произведения матрицы умножения всех десятичных разрядов регистра В с соответствующими разрядами регистра С; по второму временному такту суммируют коды разряда десятков матрицы умножения i-го разряда с кодом i+1-й тетрады регистра С; по третьему временному такту, если код первого разряда младшей тетрады А равен нулю, а первый разряд i-й тетрады В равен единице, суммируют код младшей тетрады А с кодом i-й тетрады С соответствующего десятичного разряда; по третьему такту суммируют коды тетрад В и С, если код первого разряда тетрады А равен единице; по четвертому такту при равенстве единице кодов первых разрядов тетрад А и В выполняют сложение кодов второго, третьего и четвертого разрядов тетрады А с соответствующими тетрадами регистра С; после выполнения умножения тетрад регистра В на код младшей тетрады регистра А производят сдвиг кода регистров А и С на четыре двоичных разряда вправо, операцию умножения заканчивают после умножения всех тетрад регистра А на тетрады регистра В, и устройство умножения, отличающееся тем, что содержит n-разрядные триггерные регистры множителя А, множимого В и частичных произведений С, трехвходовые сумматоры комбинационного типа, каждый десятичный разряд представляют тетрадами А, В, С в коде 8, 4, 2, 1, т.е. четырехразрядными триггерными регистрами А, В и С, содержит первую группу логических элементов И-ИЛИ передачи на выходы сумматоров кодов всех тетрад В, второго, третьего и четвертого разрядов тетрады А, кодов единиц произведения i-го десятичного разряда и кодов десятков произведения i-1-го десятичного разряда, логические элементы И преобразования двоично-десятичных кодов второго и третьего двоичных разрядов тетрад В и младшей тетрады А в десятичные числа 6, 4, 2, матрицу умножения десятичных чисел 8, 6, 4, 2 на 8, 6, 4, 2 со схемами преобразования двухразрядного десятичного числа в двоично-десятичные коды единиц и десятков произведения, логические элементы И, ИЛИ, НЕ управления умножением тетрад В на тетраду А, а также первый вход управления выдачей кода разряда единиц произведения на входы сумматоров второго, третьего и четвертого разрядов i-го десятичного разряда, второй вход управления выдачей кода разряда десятков произведения на входы сумматоров первого, второго и третьего двоичных разрядов i+1-го десятичного разряда, третий вход управления выдачей кода второго, третьего и четвертого разрядов младшей тетрады регистра А на входы соответствующих сумматоров, если коды первых разрядов тетрад А и В равны нулю и единице соответственно, четвертый вход управления выдачей кода тетрады В на входы сумматоров, если код младшей тетрады А равен единице, пятый вход управления выдачей кода тетрады А, если коды первых разрядов младшей тетрады А и i-й тетрады В равны единице; шестой вход управления сдвигом кодов регистров А и С вправо на один десятичный разряд; седьмой вход управления выдачей кодов регистра В при операциях сложения двоичных и двоично-десятичных кодов; восьмой вход управления сдвигом кодов регистров А и С; поступающий от центрального устройства управления; девятый вход управления занесением суммы в регистр С; десятый вход управления выполнением операции умножения, а также первый, второй, третий и четвертый временные такты выполнения операцией умножения, при этом единичные выходы первых триггеров тетрады В соединены с первыми входами первых элементов И, вторые входы которых подключены к выходу первого элемента ИЛИ, первый вход которого соединен с четвертым входом управления, а выходы первых элементов И соединены с первыми входами вторых элементов ИЛИ, выходы которых связаны с первыми входами одноразрядных сумматоров, единичный выход первого триггера первого разряда тетрады В соединен с первым входом одиннадцатого элемента И, второй его вход через одиннадцатый элемент ИЛИ связан с третьим и пятым входоми управления, первые входы вторых элементов И второго, третьего и четвертого двоичных разрядов соединены с девятым, десятым и одиннадцатым выходами матрицы умножения соответственно, вторые входы этих элементов И связаны с первым входом управления, выходы упомянутых элементов И соединены с вторыми входами вторых элементов ИЛИ, первые входы третьих элементов И связаны с единичными выходами триггеров второго, третьего и четвертого разрядов тетрады А, вторые входы этих элементов И связаны с выходом одиннадцатого элемента И, выходы третьих элементов И соединены с третьими входами вторых элементов ИЛИ второго, третьего и четвертого разрядов, первые входы четвертых элементов И первого, второго и третьего двоичных разрядов связаны с двенадцатым, тринадцатым и четырнадцатым выходами матрицы умножения i-1-го десятичного разряда, вторые входы четвертых элементов И подключены к второму входу управления, выходы упомянутых элементов И соединены с четвертыми входами вторых элементов ИЛИ первого, второго и третьего двоичных разрядов i-того десятичного разряда, вторые и третьи входы комбинационных сумматоров связаны с единичными выходами триггеров одноименных разрядов тетрады С и с выходами переносов сумматоров младших разрядов соответственно; выход переноса сумматора четвертого двоичного разряда является входом переноса в первый разряд сумматора старшего десятичного разряда, выходы суммы каждого сумматора соединены с входами триггеров тетрады С, к входам триггеров тетрады С также подключены шестой и девятый входы управления, первый и второй входы пятого элемента И подключены к единичным выходам триггеров третьего и второго разрядов младшей тетрады А, входы шестого элемента И связаны с единичным и нулевым выходами триггеров третьего и второго разряда соответственно, входы седьмого элемента И соединены с нулевым и единичным выходами триггеров третьего и второго разрядов соответственно, упомянутые седьмой, шестой и пятый элементы И являются схемой преобразования двоично-десятичного кода второго и третьего разрядов младшей тетрады А в четное десятичное число, их выходы связаны с первым, вторым и третьим входами матрицы умножения, единичный выход триггера четвертого разряда тетрады А подключен к четвертому входу упомянутой матрицы; восьмой, девятый и десятый элементы И с соответствующими связями являются схемой преобразования двоично-десятичного кода в десятичное число тетрады В, выходы восьмого, девятого и десятого элементов И и единичный выход триггера четвертого разряда тетрады В соединены с пятым, шестым, седьмым и восьмым входами матрицы умножения; матрица умножения четных десятичных чисел содержит 16 элементов И-ИЛИ, расположенных в точках пересечения линий выходов седьмого, шестого и пятого элементов И и единичного выхода триггера четвертого разряда тетрады А и выходов восьмого, девятого и десятого элементов И и единичного выхода триггера четвертого разряда тетрады В, каждая точка пересечения упомянутых линий соответствует значениям одного из четных десятичных чисел 4, 8, 12, 16, 24, 32, 36, 48, и 64, выходы элементов ИЛИ каждой точки пересечения входов матрицы умножения соединены с точками, соответствующими равным числам произведения, выходы элементов ИЛИ каждого узла матрицы соединены с входами третьего, четвертого, пятого и шестого элементов ИЛИ, выходы которых, кроме шестого, соответствуют двоично-десятичным кодам разряда единиц произведения i-го десятичного разряда, соответствующие выходы элементов ИЛИ узлов матрицы связаны с входами седьмого, восьмого и девятого элементов ИЛИ, выходы которых соответствуют двоично-десятичным кодам разряда десятков произведения i-го десятичного разряда и соединены с первыми входами четвертых элементов И первого, второго и третьего разрядов i+1-го десятичного разряда; схема управления умножением тетрад В на тетраду А содержит тринадцатый элемент И, первый-четвертый входы которого соединены соответственно с нулевыми выходами триггеров первого-четвертого двоичных разрядов младшей тетрады А, выход этого элемента И соединен с входами четырнадцатого элемента И и первого элемента НЕ, выход которого связан с первым входом пятнадцатого элемента И, вторые входы упомянутых элементов И подключены к входу первого временного такта, выход четырнадцатого элемента И соединен с входом десятого элемента ИЛИ, второй выход которого подключен к восьмому входу управления, выход упомянутого ИЛИ является шестым входом управления и соединен с входами вторых и третьих триггеров, выход пятнадцатого элемента И является первым входом управления, выход двенадцатого элемента И является вторым входом управления, первый вход упомянутого элемента И соединен с вторым временным тактом, второй его вход связан с десятым входом управления, выход шестнадцатого элемента И является третьим входом управления, выход семнадцатого элемента И является четвертым входом управления, выход восемнадцатого элемента И является пятым входом управления, первый и второй входы шестнадцатого элемента И соединены с первым входом тринадцатого элемента И и входом третьего временного такта, входы семнадцатого элемента И соединены с входом третьего временного такта и единичным выходом триггера первого разряда тетрады А, входы восемнадцатого элемента И связаны с четвертым временным тактом и с единичным выходом триггера первого разряда тетрады А, седьмой вход управления подключен к второму входу первого элемента ИЛИ, восьмой вход управления подключен к входу десятого элемента ИЛИ, девятый вход управления подключен к входам вторых триггеров тетрады С, кроме того каждый двоичный разряд регистров А, В и С содержит RS-триггер, разряды регистров А и С, кроме RS-триггеров, содержат первый-седьмой элементы И, первый-третий элементы ИЛИ, первый-четвертый элементы НЕ, при этом шестой вход управления соединен с первыми входами первого и четвертого элементов И, вторые входы этих элементов соединены с выходами третьего элемента НЕ и седьмого элемента И соответствующего разряда старшей тетрады, входы второго и третьего элементов И вторых триггеров тетрад С соединены с девятым входом управления, вторые входы этих элементов связаны с выходом и входом четвертого элемента НЕ, вход которого связан с выходом суммы одноразрядного сумматора, выходы первого и второго элементов И по цепи элементов первый ИЛИ, пятый И, первый НЕ связаны с нулевым входом RS-триггера, выходы третьего и четвертого элементов И по цепи элементов второй ИЛИ, шестой И, второй НЕ связаны с единичным входом RS-триггера, единичный выход RS-триггера через третий элемент ИЛИ соединен с входом седьмого элемента И, второй вход которого связан с выходом второго элемента НЕ, выход пятого элемента И через третий элемент ИЛИ подключен к второму входу седьмого элемента И, выход которого является единичным выходом триггера два тетрады С, выход седьмого элемента И соединен с вторым входом пятого элемента И и с входом третьего элемента НЕ, выход которого подключен к входу шестого элемента И и является нулевым выходом триггера два тетрады С, триггер три регистра А построен аналогично триггеру два тетрады С, отличие состоит только в том, что в этом триггере отсутствуют второй и третий элементы И, первый и второй элементы ИЛИ, четвертый элемент НЕ и девятый вход управления.

Повышение быстродействия в предложенных способе и устройстве достигается за счет того, что в состав каждого десятичного разряда устройства введены дешифраторы двоичных кодов, хранящихся в во вторых и третьих разрядах каждой тетрады множимого и младшей тетрады множителя, матрица умножения четных десятичных чисел тетрады на четыре входа каждого сомножителя, на три выхода единиц i-го разряда, на три выхода десятков i+1-го десятичного разряда и схема управления умножением. Кроме того, каждый десятичный разряд содержит первую группу логических элементов И-ИЛИ, подключенных к входам четырех одноразрядных трехвходовых сумматоров, вторую группу элементов И-ИЛИ и три четырехразрядных регистра А, В, и С, выполненных на основе RS-триггеров.

Рассмотрим основные отличительные особенности предлагаемого способа умножения двоично-десятичных кодов. Основное отличие заключается в преобразовании кодов тетрад сомножителей, представленных в кодах 8 4 2 1, в четное десятичное число 8, 6, 4, 2, (1), применение матрицы умножения (МУ) четных чисел 8, 6, 4, 2 на 8, 6, 4, 2 четных чисел тетрад регистра В и младшей тетрады регистра А, применения обратного преобразования двухразрядного десятичного числа произведения в код 8, 4, 2, разряда единиц и в код 8, 4, 2, разряда десятков. При этом первый двоичный разряд работает традиционным способом и выполнен по известным схемным построениям. Отличительные особенности позволяют выполнить умножение всех тетрад множимого на младшею тетраду множителя практически одновременно с временем приема кода в тетрады регистров А и В. Это позволяет повысить быстродействие выполнения операции умножения четных чисел приблизительно в два-три раза. Второй отличительной особенностью способа является поочередное суммирование кодов разряда единиц и разряда десятков произведения, что позволяет выполнять умножение на одном и том же оборудовании, что требуется для выполнения умножения двоичных кодов. Увеличение оборудование имеет место только за счет построения МУ. Таким образом предлагаемые способ и устройство позволяют выполнять операции сложения как в двоичных, так и в двоично-десятичных кодах, а также умножения двоично-десятичных кодов. Особенностью предлагаемого устройства умножения также является построение всех регистров на основе простейших RS-триггеров, при этом в регистрах множителя и частичных произведений с помощью дополнительных элементов И, ИЛИ, НЕ обеспечивается задержка сигнала с выхода RS-триггеров при их переключении на время длительности исполнительного импульса сдвига или запоминания результата суммирования. Это позволяет построить каждый десятичный разряд на основе двенадцати RS-триггеров. Для построения известных устройств потребуется двадцать RS -триггеров, что в полтора раза больше. В такой же пропорции снизится потребление электропитания по сравнению с известными устройствами.

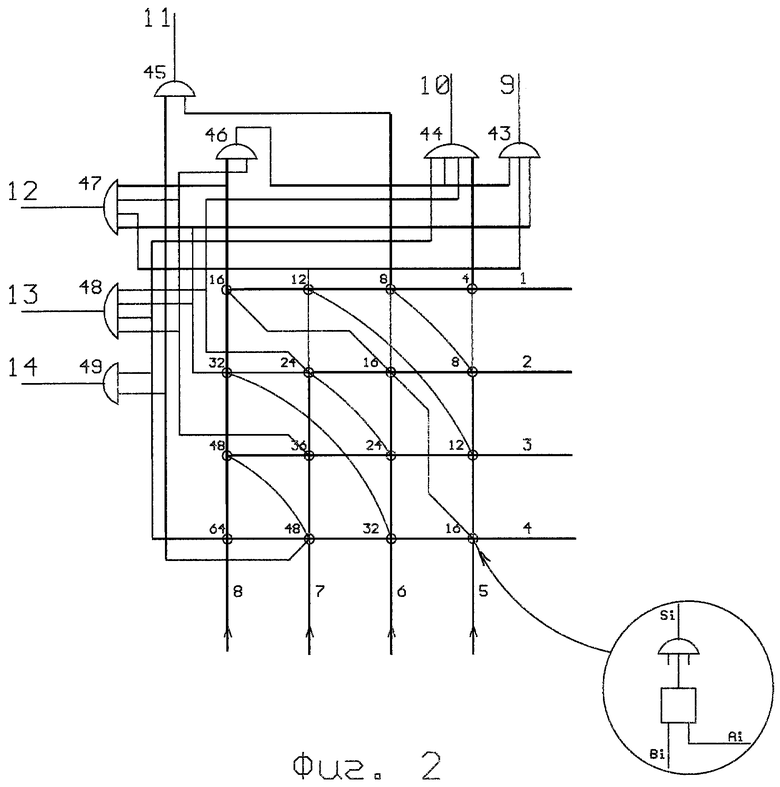

Для пояснения работы предлагаемого устройства на фиг.1 приведена функциональная схема одного десятичного разряда. На чертеже приняты следующие обозначения: RS-триггеры (Тr) регистра В 1, триггеры регистров С и А с элементами задержки сигнала 2, 3, элементы И 4-22, 50-55, 86, 87, элементы ИЛИ 23-26, 40-42, элемент НЕ 56, одноразрядные комбинационные сумматоры 27, вход сигнала переноса из сумматора младшего разряда 28, первый вход управления (ВУ) выдачей кода разряда единиц произведения i-го десятичного разряда на входы сумматоров 29, второй ВУ выдачей кода разряда десятков произведения на входы сумматоров i+1-го десятичного разряда 30, третий ВУ выдачей кода тетрады А, если коды первых разрядов тетрад А и В равены нулю и единице соответственно, 31, четвертый ВУ выдачей кода всех тетрад В 32, пятый ВУ выдачей кода второго, третьего и четвертого разрядов тетрады А 33, шестой ВУ сдвигом кода регистров А и С 34, матрица умножения 35, входы кода десятков из младшего десятичного разряда 36, 37, 38, седьмой ВУ выдачей кода регистра В при операциях сложения двоичных и двоично-десятичных кодов 39, нулевые выходы первого-четвертого разрядов тетрады А 57-60, первый-четвертый временные такты (ВТ) 61, 62, 63, 64, восьмой ВУ 65, десятый ВУ операцией умножения 66, единичные выходы Тr второго - четвертого разрядов тетрады А 67-69, девятый ВУ 85.

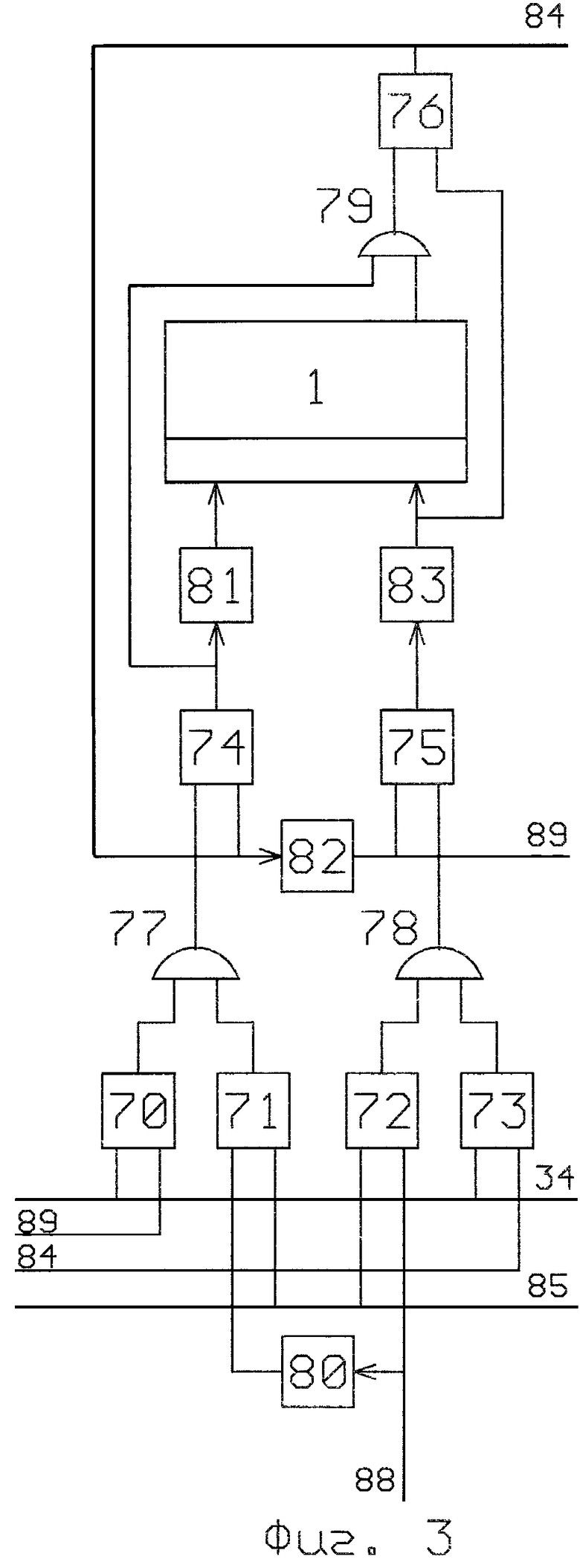

На фиг.2 приведена функциональная схема матрицы умножения четных десятичных чисел 8, 6, 4, 2 тетрады А на четные десятичные числа 8, 6, 4, 2 тетрады В. На фигуре приняты следующие обозначения: элементы ИЛИ преобразования разряда единиц произведения в двоично-десятичный код 43-46, элементы ИЛИ преобразования разряда десятков произведения в двоично-десятичный код 47-49, входы четных чисел тетрады А 1, 2, 3, 4, входы четных чисел тетрады В 5, 6, 7, 8, выходы разряда единиц произведения двоично-десятичного кода МУ 9-11, выходы разряда десятков произведения двоично-десятичного кода МУ 12-14, в каждом узле пересечения линий входов чисел А и В установлены элементы И-ИЛИ, всего шестнадцать элементов.

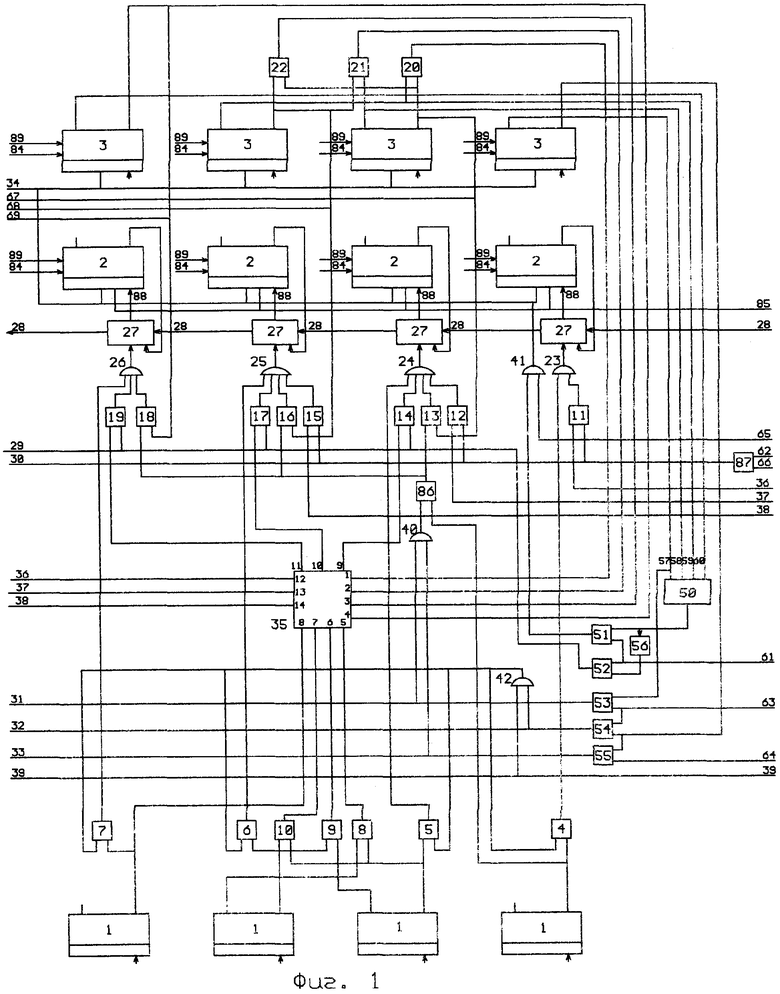

На Фиг.3 приведена функциональная схема RS-триггера с элементами И, ИЛИ, НЕ, обеспечивающими задержку сигнала с выходов триггеров 2 и 3. На фигуре приняты следующие обозначения: элементы И 70-76, элементы ИЛИ 77-79, элементы НЕ 80-83, RS-триггер 1, единичный выход триггера с задержкой сигнала 84, нулевой выход триггера с задержкой сигнала 89, ВУ сдвигом кода вправо 34, ВУ занесением суммы 85, вход суммы 1-го двоичного разряда 88.

Предложенный объект осуществляется следующим образом. В исходном состоянии в триггерных тетрадах В и А хранятся двоично-десятичные коды множимого и множителя, в триггерных тетрадах С может храниться код результата предыдущей операции или эти триггеры установлены в нуль. На единичных выходах триггеров 1, 2, 3 присутствуют высокие потенциалы, соответствующие двоично-десятичным кодам занесенным в упомянутые триггеры. На входах управления 29-33, 34, 39, 65, 66, 85 отсутствуют высокие потенциалы. На входах ВТ 61-64 также отсутствуют высокие потенциалы. Единичные выходы Тr1 тетрады В соединены с входами И 4, 5, 6, 7, вторые входы этих элементов через ИЛИ 42 подключены к ВУ 32, 39, а выходы упомянутых элементов И соединены соответственно с входами ИЛИ 23, 24, 25, 26, входы И 8 связаны с единичным и нулевым выходами Тr1 второго и третьего разрядов тетрады В, входы И 9 соединены с нулевым и единичным выходами Тr1 второго и третьего разрядов, входы И 10 соединены с единичными выходами упомянутых триггеров тетрады В, выходы И 8, 9, 10 связаны с входами 5, 6, 7 МУ 35 соответственно, выход Тr1 четвертого разряда соединен с 8 входом МУ 35, первый-четвертый входы МУ 35 связаны с выходами И 20, 21, 22 и с единичным выходом Тr 3 четвертого двоичного разряда, двенадцатый-четырнадцатый выходы матрицы i-го десятичного разряда соединены с И 11, 12, 15 i+1-гo десятичного разряда, выходы И 11-19 через ИЛИ 23, 24, 25, 26 соединены с CM 27 соответствующих разрядов, вторые и третьи входы СМ 27 каждого двоичного разряда соединены с единичным выходом Тr 2 и входом переноса из СМ 27 младшего разряда - 28, ВУ 34 подключен к входам Тr 2, 3 тетрад С и А и к выходу ИЛИ 41, нулевые выходы всех Тr 3 младшей тетрады А соединены с входами И 50, выход который является признаком кода нулей в младшей тетраде А, нулевой выход Тr 3 младшего разряда тетрады А соединен с И 53, второй вход которого соединен с ВТ 63, вход ВТ 61 подключен к входам И 51, 52, вторые входы которых соединены с входом и выходом НЕ 56 соответственно, вход НЕ 56 связан с выходом И 50, выход И 51 соединен с входом ИЛИ 41, выход И 52 соединен с ВУ 29 и подключен к И 14, 17, 19, выход И 87 соединен с ВУ 30 и подключен к И 11, 12, 15, выход И 53 соединен с ВУ 31, ИЛИ 40, второй вход которого подключен к выходу И 55, а выход соединен с И 86, выход И 86 подключен к И 13, 16, 18, выход И 54 соединен с ВУ 32 и с входом ИЛИ 42, ВУ 39 соединены с ИЛИ 42, вход ВТ 63 соединен с И 53, 54, единичный выход Тr 3 первого разряда тетрады А соединен с И 54, 55, вход ВТ 64 подключен к И 55, ВУ 65 подключен к ИЛИ 41, выходы 67-69 соединены с И 13, 16 и 18 всех десятичных разрядов соответственно. В каждом Тr 2 (фиг.3) вход 88 соединен с И 72 и НЕ 80, выход НЕ 80 соединен с И 71, вторые входы И 71, 72 связаны с ВУ 85, прямой и инверсный выходы Тr 2 соответствующего старшего разряда соединены с И 73, 70, их вторые входы соединены с ВУ 34, выходы И 70, 71 через ИЛИ 77 соединены с И 74, выходы И 72, 73 через ИЛИ 78 соединены с И 75, выходы И 74, 75 через НЕ 81, 83 подключены к нулевому и единичному входам триггера 1, единичный выход которого через ИЛИ 79 соединен с И 76, второй вход ИЛИ 79 подключен к выходу И 74, второй вход И 76 связан с выходом НЕ 83, выход И 76 соединен с входом НЕ 82, вход и выход которого подключены к И 74, 75 соответственно, выход И 76 является единичным выходом Тr 2 i-го разряда и соединен с И 73 i-го разряда младшей тетрады, выход НЕ 82 является инверсным (нулевым) выходом Тr 2 i-го разряда и соединен с И 70 i-го разряда младшей тетрады. Триггеры 3 регистра множителя выполнены по аналогичной схеме. Отличие состоит в том, что в них исключены элементы приема кода из сумматоров, т.е. исключены И 71, 72, ИЛИ 77, 78, ВУ 85, НЕ 80 и вход 88.

Рассмотрим работу устройства при выполнении операций умножения и сложения.

1. Операция умножения всех тетрад множимого на младшею тетраду множитнля выполняется за четыре временных такта (без учета времени сдвига и приема сомножителей в регистры А и В). До начала выполнения операции в регистры А и В принимаются коды множителя и множимого. Одновременно с приемом сомножителей выполняют преобразование двоично-десятичных кодов второго и третьего разрядов каждой тетрады В и младшей тетрады А в четные десятичные числа 6, 4 и 2. Названная элементарная операция (ЭО) выполняется с помощью элементов И 8, 9, 10 в тетрадах В и элементов И 20, 21, 22 в тетраде А. Выходы упомянутых элементов И и единичных выходов Тr 1 и 3 четвертых разрядов тетрад, соответствующие одному из четных десятичных чисел 8, 6, 4 и 2, подаются на соответствующие входы МУ 35, на выходах которой получают произведение одного из ряда десятичных чисел 4, 8, 12, 16, 24, 32, 36, 48, 64, полученное десятичное число преобразуют с помощью элементов ИЛИ 43-46 (фиг.2) в двоично-десятичный код единиц i-го десятичного разряда и с помощью ИЛИ 47-49 - в двоично-десятичный код десятков i-1-го разряда.

По ВТ1 выполняют проверку наличия нулевых значений всех триггеров младшей тетрады А. Эта ЭО выполняется элементами И 50, 51 и входа 61. При наличии нулевых значений триггеров по этому временному такту производят сдвиг кодов регистров А и С на четыре двоичных разряда вправо. Если в триггерах тетрады А хранится код чисел от 1 до 9, то по ВТ1 выполняют операцию сложения двоично-десятичных кодов разряда единиц произведения каждой тетрады В с соответствующими тетрадами С. Для выполнения этой операции на вход 61 подается высокий потенциал, который через И 52 поступает на ВУ 29. Если в разряде единиц произведения МУ 35 на выходах 9, 10, 11 присутствуют высокие потенциалы, то с выходов И 14, 17, 19 через ИЛИ 24, 25, 26 на вход См 27 поступит высокий потенциал и выполнит суммирование кода разряда единиц МУ 35, кода хранящегося в Тr 2 и сигнала переноса младшего разрядов 28. Результат с выхода СМ 27 будет занесен в Тr 2. Для выполнения этой ЭО на ВУ 85 подается исполнительный импульс занесения суммы в триггеры 2.

По ВТ2 выполняют операцию сложения двоичных кодов разряда десятков произведения i-го десятичного разряда с i+1-м десятичным разрядом тетрады С. Эта операция выполняется путем подачи на вход И 87 высоких потенциалов ВТ 62 и ВУ 66. Высокий потенциал с И 87, по ВУ 30 поступит на входы И 11, 12, 15. Если на выходе 12, 13 и 14 МУ 35 имеет место высокий потенциал, то с выхода упомянутых элементов И через ИЛИ 23, 24, 25 на вход СМ 27 поступит высокий потенциал. С выхода СМ 27 будет получен результат суммирования, который будет занесен в Тr 2.

По ВТ3 анализируют состояние Тr 3 первого разряда тетрады А. Если код этого триггера равен нулю, а код Тr 1 первого разряда тетрады В равен единице, то выполняется операция сложения кодов младшей тетрады А с кодами тетрад С. При этом на ВТ 63 подают высокий потенциал, который по цепи элементов И 53, ВУ 31, ИЛИ 48, И 86 разрешает прохождение сигналов с единичных выходов Тr 3 второго-четвертого разрядов тетрады А через И 13, 16, 18, ИЛИ 24, 25, 26 на входы CM 27. Если код Тr 3 первого разряда тетрады А равен единице, то выполняют операцию сложения кодов всех тетрад В и С. При этом на вход 63 поступает высокий потенциал, который через И 54, ВУ 32, ИЛИ 42 разрешает прохождение сигналов с единичных выходов Тr 1 через И 4, 5, 6, 7, ИЛИ 23, 24, 25, 26 на входы СМ 27. Результат суммирования заносят в Тr2.

По ВТ4, при равенстве единице кодов Тr 1,3 первых разрядов тетрады А и В выполняют сложение кода триггеров второго, третьего и четвертого разрядов тетрады А с кодами тех тетрад С, в которых код Тr 1 первого разряда тетрады В равен единице. При выполнении этой операции на ВТ 64 подают высокий потенциал, который по цепи элементов И 55, ИЛИ 40, И 86 поступает на входы И 13, 16, 18 и далее на входы СМ 27 и Тr 2. Выход И 55 является ВУ 33. Примеры выполнения операции умножения кодов тетрады А на тетраду В приведены в таблице 1.

А, В, С - регистры множителя, множимого, произведения.

А1, B1 - значение кодов первых двоичных разрядов тетрад А и В. При А1=0, В1=0 числа тетрад четные, при А1=1, В1=1 - нечетные.

2. Операция сложения чисел, представленных как в двоичных, так и в двоично-десятичных кодах, выполняется за три временных такта. По ВТ1 принимает код второго слагаемого в регистр В, код первого слагаемого хранится в регистре С. На время выполнения операции на ВТ 39 подается высокий потенциал, поступающий через ИЛИ 42 на входы И 4, 5, 6, 7 и далее на вход ИЛИ 23, 24, 25, 26 и входы СМ 27 всех разрядов. По ВТ2 формируется потенциалы переносов 28 и суммы на выходах СМ 27. По ВТЗ результат суммирования заносится в Тr 2 регистра С. При этом на ВУ 85 поступает сигнал. Если триггер 2 хранит код нуля, а по входу 88 (фиг.3) поступает высокий потенциал с СМ 27, то сигнал по цепи И 72, ИЛИ 78, И 75, НЕ 83 поступает на единичный вход RS-триггера 1 и устанавливает его в единицу. На время длительности сигнала приема кода за счет связи с выхода НЕ 83 с входом И 76 будет обеспечена задержка сигнала с упомянутого выхода. Если триггер меняет свое состояние с единицы на нуль, то за счет связи с выхода И 74, через ИЛИ 79 будет искуственно поддерживаться высокий потенциал с И 76 на время длительности сигнала на ВУ 85. В том случае, если значения потенциалов с входа 88 и выхода 76 совпадают, триггер сохранит свое состояние. Работа триггера 2 при выполнении ЭО сдвига кода аналогична его работе при приеме кода из СМ 27. Отличие состоит в том, что сигнал выполнения сдвига поступает на ВУ 34 и элементы И 70, 73, вторые входы которых управляются выходами 84 и 89 соответствующего разряда.

Основные технические характеристики предлагаемого устройства приведены в таблице 2.

Таким образом, предлагаемые способ и устройство обеспечивают повышение быстродействия выполнения операции умножения двоично-десятичных кодов, выполнение операций сложения слагаемых, представленных как в двоично-десятичных, так и в двоичных кодах при минимальных затратах оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ДВОИЧНЫХ КОДОВ | 2010 |

|

RU2410746C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2014 |

|

RU2551414C1 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ЕДИНИЦ | 2014 |

|

RU2540787C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

Изобретение относиться к цифровой вычислительной технике и устройствам автоматики. Техническим результатом является повышение быстродействия выполнения операции умножения при минимальных затратах оборудования. Устройство содержит в каждом десятичном разряде три четырехразрядных триггерных регистра, четыре комбинационных сумматора, матрицу умножения четных десятичных чисел, логические элементы И, логические элементы ИЛИ, логические элементы НЕ, десять входов управления. 2 н.п. ф-лы, 3 ил., 2 табл.

1. Способ умножения двоично-десятичных кодов, заключающийся в сложении кодов регистров множимого В и частичных произведений С столько раз, сколько десятичных единиц содержит младшая тетрада регистра множителя А и сдвига кодов регистров А и С на четыре двоичных разряда в сторону младших разрядов с последовательным умножением всех тетрад регистра В на тетрады регистра А, отличающийся тем, что множитель и множимое принимают соответственно в регистры А и B в кодах 8, 4, 2, 1 и одновременно преобразуют коды второго, третьего и четвертого двоичных разрядов каждой тетрады триггеров регистра В и младшей тетрады регистра А в четные десятичные числа 8, 6, 4, 2, с помощью матрицы умножения получают произведение, равное одному из десятичных чисел 4, 8, 12, 16, 24, 32, 36, 48 и 64, полученное число преобразуют в двоично-десятичный код; по первому временному такту определяют наличие нулевых значений триггеров первого - четвертого разрядов младшей тетрады А, при нулевых значениях упомянутых триггеров операцию умножения кода регистра В на код младшей тетрады регистра А не производят, а выполняют сдвиг кодов регистров А и С на четыре двоичных разряда в сторону младших разрядов, если код тетрады А не равен нулю, то суммируют двоично-десятичный код разряда единиц произведения матрицы умножения всех десятичных разрядов регистра В с соответствующими разрядами регистра С; по второму временному такту суммируют коды разряда десятков матрицы умножения 1-го разряда с кодом i+1-й тетрады регистра С; по третьему временному такту, если код первого разряда младшей тетрады А равен нулю, а первый разряд i-й тетрады В равен единице, суммируют код младшей тетрады А с кодом i-й тетрады С соответствующего десятичного разряда; по третьему такту суммируют коды тетрад В и С, если код первого разряда тетрады А равен единице; по четвертому такту при равенстве единице кодов первых разрядов тетрад А и В выполняют сложение кодов второго, третьего и четвертого разрядов тетрады А с соответствующими тетрадами регистра С; после выполнения умножения тетрад регистра В на код младшей тетрады регистра А производят сдвиг кода регистров А и С на четыре двоичных разряда вправо, операцию умножения заканчивают после умножения всех тетрад регистра А на тетрады регистра В.

2. Устройство умножения двоично-десятичных кодов, отличающееся тем, что содержит n-разрядные триггерные регистры множителя А, множимого В и частичных произведений С, трехвходовые сумматоры комбинационного типа, каждый десятичный разряд представляют тетрадами А, В, С в коде 8, 4, 2, 1, т.е. четырехразрядными триггерными регистрами А, В и С, содержит первую группу логических элементов И-ИЛИ передачи на выходы сумматоров кодов всех тетрад В, второго, третьего и четвертого разрядов тетрады А, кодов единиц произведения i-го десятичного разряда и кодов десятков произведения i-1-го десятичного разряда, логические элементы И преобразования двоично-десятичных кодов второго и третьего двоичных разрядов тетрад В и младшей тетрады А в десятичные числа 6, 4, 2, матрицу умножения десятичных чисел 8, 6, 4, 2 на 8, 6, 4, 2 со схемами преобразования двухразрядного десятичного числа в двоично-десятичные коды единиц и десятков произведения, логические элементы И, ИЛИ, НЕ управления умножением тетрад В на тетраду А, а также первый вход управления выдачей кода разряда единиц произведения на входы сумматоров второго, третьего и четвертого разрядов i-го десятичного разряда, второй вход управления выдачей кода разряда десятков произведения на входы сумматоров первого, второго и третьего двоичных разрядов i+1-го десятичного разряда, третий вход управления выдачей кода второго, третьего и четвертого разрядов младшей тетрады регистра А на входы соответствующих сумматоров, если коды первых разрядов тетрад А и В равны нулю и единице соответственно, четвертый вход управления выдачей кода тетрады В на входы сумматоров, если код младшей тетрады А равен единице, пятый вход управления выдачей кода тетрады А, если коды первых разрядов младшей тетрады А и i-й тетрады В равны единице; шестой вход управления сдвигом кодов регистров А и С вправо на один десятичный разряд; седьмой вход управления выдачей кодов регистра В при операциях сложения двоичных и двоично-десятичных кодов; восьмой вход управления сдвигом кодов регистров А и С; поступающий от центрального устройства управления; девятый вход управления занесением суммы в регистр С; десятый вход управления выполнением операции умножения, а также первый второй, третий и четвертый временные такты выполнения операцией умножения, при этом единичные выходы первых триггеров тетрады В соединены с первыми входами первых элементов И, вторые входы которых подключены к выходу первого элемента ИЛИ, первый вход которого соединен с четвертым входом управления, а выходы первых элементов И соединены с первыми входами вторых элементов ИЛИ, выходы которых связаны с первыми входами одноразрядных сумматоров, единичный выход первого триггера первого разряда тетрады В соединен с первым входом одиннадцатого элемента И, второй его вход через одиннадцатый элемент ИЛИ связан с третьим и пятым входами управления, первые входы вторых элементов И второго, третьего и четвертого двоичных разрядов соединены с девятым, десятым и одиннадцатым выходами матрицы умножения соответственно, вторые входы этих элементов И связаны с первым входом управления, выходы упомянутых элементов И соединены с вторыми входами вторых элементов ИЛИ, первые входы третьих элементов И связаны с единичными выходами триггеров второго, третьего и четвертого разрядов тетрады А, вторые входы этих элементов И связаны с выходом одиннадцатого элемента И, выходы третьих элементов И соединены с третьими входами вторых элементов ИЛИ второго, третьего и четвертого разрядов, первые входы четвертых элементов И первого, второго и третьего двоичных разрядов связаны с двенадцатым, тринадцатым и четырнадцатым выходами матрицы умножения i-1-го десятичного разряда, вторые входы четвертых элементов И подключены к второму входу управления, выходы упомянутых элементов И соединены с четвертыми входами вторых элементов ИЛИ первого, второго и третьего двоичных разрядов i-го десятичного разряда, вторые и третьи входы комбинационных сумматоров связаны с единичными выходами триггеров одноименных разрядов тетрады С и с выходами переносов сумматоров младших разрядов соответственно; выход переноса сумматора четвертого двоичного разряда является входом переноса в первый разряд сумматора старшего десятичного разряда, выходы суммы каждого сумматора соединены с входами триггеров тетрады С, к входам триггеров тетрады С также подключены шестой и девятый входы управления, первый и второй входы пятого элемента И подключены к единичным выходам триггеров третьего и второго разрядов младшей тетрады А, входы шестого элемента И связаны с единичным и нулевым выходами триггеров третьего и второго разряда соответственно, входы седьмого элемента И соединены с нулевым и единичным выходами триггеров третьего и второго разрядов соответственно, упомянутые седьмой, шестой и пятый элементы И являются схемой преобразования двоично-десятичного кода второго и третьего разрядов младшей тетрады А в четное десятичное число, их выходы связаны с первым, вторым и третьим входами матрицы умножения, единичный выход триггера четвертого разряда тетрады А подключен к четвертому входу упомянутой матрицы; восьмой, девятый и десятый элементы И с соответствующими связями являются схемой преобразования двоично-десятичного кода в десятичное число тетрады В, выходы восьмого, девятого и десятого элементов И и единичный выход триггера четвертого разряда тетрады В соединены с пятым, шестым, седьмым и восьмым входами матрицы умножения; матрица умножения четных десятичных чисел содержит 16 элементов И-ИЛИ, расположенных в точках пересечения линий выходов седьмого, шестого и пятого элементов И и единичного выхода триггера четвертого разряда тетрады А и выходов восьмого, девятого и десятого элементов И и единичного выхода триггера четвертого разряда тетрады В, каждая точка пересечения упомянутых линий соответствует значениям одного из четных десятичных чисел 4, 8, 12, 16, 24, 32, 36, 48, и 64, выходы элементов ИЛИ каждой точки пересечения входов матрицы умножения соединены с точками, соответствующими равным числам произведения, выходы элементов ИЛИ каждого узла матрицы соединены с входами третьего, четвертого, пятого и шестого элементов ИЛИ, выходы которых, кроме шестого, соответствуют двоично-десятичным кодам разряда единиц произведения i-го десятичного разряда, соответствующие выходы элементов ИЛИ узлов матрицы связаны с входами седьмого, восьмого и девятого элементов ИЛИ, выходы которых соответствуют двоично-десятичным кодам разряда десятков произведения i-го десятичного разряда и соединены с первыми входами четвертых элементов И первого, второго и третьего разрядов i+1-го десятичного разряда; схема управления умножением тетрад В на тетраду А содержит тринадцатый элемент И, первый - четвертый входы которого соединены соответственно с нулевыми выходами триггеров первого - четвертого двоичных разрядов младшей тетрады А, выход этого элемента И соединен с входами четырнадцатого элемента И и первого элемента НЕ, выход которого связан с первым входом пятнадцатого элемента И, вторые входы упомянутых элементов И подключены к входу первого временного такта, выход четырнадцатого элемента И соединен с входом десятого элемента ИЛИ, второй вход которого подключен к восьмому входу управления, выход упомянутого ИЛИ является шестым входом управления и соединен с входами вторых и третьих триггеров, выход пятнадцатого элемента И является первым входом управления, выход двенадцатого элемента И является вторым входом управления, первый вход упомянутого элемента И соединен с вторым временным тактом, второй его вход связан с десятым входом управления, выход шестнадцатого элемента И является третьим входом управления, выход семнадцатого элемента И является четвертым входом управления, выход восемнадцатого элемента И является пятым входом управления, первый и второй входы шестнадцатого элемента И соединены с первым входом тринадцатого элемента И и входом третьего временного такта, входы семнадцатого элемента И соединены с входом третьего временного такта и единичным выходом триггера первого разряда тетрады А, входы восемнадцатого элемента И связаны с четвертым временным тактом и с единичным выходом триггера первого разряда тетрады А, седьмой вход управления подключен к второму входу первого элемента ИЛИ, восьмой вход управления подключен к входу десятого элемента ИЛИ, девятый вход управления подключен к входам вторых триггеров тетрады С, кроме того, каждый двоичный разряд регистров А, В и С содержит RS-триггер, разряды регистров А и С, кроме RS-триггеров, содержат первый - седьмой элементы И, первый - третий элементы ИЛИ, первый - четвертый элементы НЕ, при этом шестой вход управления соединен с первыми входами первого и четвертого элементов И, вторые входы этих элементов соединены с выходами третьего элемента НЕ и седьмого элемента И соответствующего разряда старшей тетрады, входы второго и третьего элементов И вторых триггеров тетрад С соединены с девятым входом управления, вторые входы этих элементов связаны с выходом и входом четвертого элемента НЕ, вход которого связан с выходом суммы одноразрядного сумматора, выходы первого и второго элементов И по цепи элементов первый ИЛИ, пятый И, первый НЕ связаны с нулевым входом RS-триггера, выходы третьего и четвертого элементов И по цепи элементов второй ИЛИ, шестой И, второй НЕ связаны с единичным входом RS-триггера, единичный выход RS-триггера через третий элемент ИЛИ соединен с входом седьмого элемента И, второй вход которого связан с выходом второго элемента НЕ, выход пятого элемента И через третий элемент ИЛИ подключен к второму входу седьмого элемента И, выход которого является единичным выходом триггера два тетрады С, выход седьмого элемента И соединен с вторым входом пятого элемента И и с входом третьего элемента НЕ, выход которого подключен к входу шестого элемента И и является нулевым выходом триггера два тетрады С, триггер три регистра А построен аналогично триггеру два тетрады С, отличие состоит только в том, что в этом триггере отсутствуют второй и третий элементы И, первый и второй элементы ИЛИ, четвертый элемент НЕ и девятый вход управления.

| КАРЦЕВ М.А | |||

| Арифметика цифровых машин | |||

| - М.: Наука, 1969, с.346-354 | |||

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| DE 3934898 A1, 02.05.1991 | |||

| JP 60186933 A, 24.09.1985. | |||

Авторы

Даты

2010-04-20—Публикация

2008-11-17—Подача