Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известны сумматоры комбинационно-накапливающего типа, выполненные на основе элементов И, ИЛИ, НЕ, содержащие в каждом разряде три RS-триггера, девять элементов И, четыре элемента ИЛИ, один элемент НЕ и три шины управления (см. а.с. № 1264165). Недостатком этого сумматора является наличие трех RS-триггеров в каждом разряде, что определяет время выполнения операций сложения, объем оборудования и стоимость устройства в целом. Кроме того, общим недостатком накапливающих и комбинационных сумматоров является сложность схемной реализации совмещения во времени выполнения операций сложения и сдвига кода вправо, что требуется для выполнения операции умножения.

Наиболее близким, принятым за прототип, является сумматор (далее - объект) по а.с. № 1262479. Он устраняет некоторые недостатки объекта по а.с. № 1264165, т.к. содержит в каждом разряде только два RS-триггера, но не позволяет совмещать операции сложения и сдвига и выполняет только одну операцию сложения.

Целью изобретения является повышение быстродействия работы объекта и расширение перечня выполняемых арифметических и логических операций при минимальных затратах оборудования. Для чего предложен объект, содержащий в каждом разряде первый и второй RS-триггеры, три элемента ИЛИ, семь элементов И, два элемента НЕ, причем первый и второй входы первого элемента И соединены с входом разрешения приема и информационным входом i-того разряда, выход этого элемента подключен к S-входу первого RS-триггера, нулевой и единичный выходы этого триггера связаны с первыми входами второго и третьего элементов И соответственно, единичный выход первого триггера соединен с вторыми входами второго элемента ИЛИ и шестого элемента И, выходы второго и третьего элементов И соединены с первым элементом ИЛИ, первый вход третьего элемента ИЛИ соединен с выходом переноса из младшего разряда, выход шестого элемента И подключен к третьему входу третьего элемента ИЛИ, выходы второго и третьего элементов ИЛИ соединены с первым и третьим входами седьмого элемента И, выход которого является входом переноса в старший разряд, отличающийся тем, что в каждый разряд сумматора введены восьмой, девятый, десятый и одиннадцатый элементы И, четвертый, пятый, шестой, седьмой и восьмой элементы ИЛИ, третий, четвертый, пятый и шестой элементы НЕ, пять входов управления, при этом вход управления запретом переноса соединен с третьим входом седьмого элемента И, первый вход восьмого элемента И связан с S-входом второго триггера, второй вход упомянутого элемента И соединен с выходом четвертого элемента ИЛИ, а выход восьмого элемента И подключен к первым входам второго элемента ИЛИ, шестого элемента И, одиннадцатого элемента И и с входом первого элемента НЕ, вход и выход которого связаны с третьими входами четвертого и пятого элементов И, выход четвертого элемента И связан с первым входом четвертого элемента ИЛИ, второй его вход соединены с единичным выходом второго RS-триггера, выходы четвертого и пятого элементов И через третий и второй элементы НЕ связаны с R- и S-входами второго триггера соответственно, выход первого элемента ИЛИ соединен с первыми входами девятого и десятого элементов И и с входом пятого элемента НЕ, выход которого подключен к второму входу одиннадцатого элемента И, выходы десятого и одиннадцатого элементов И через пятый элемент ИЛИ связаны с первым входом седьмого элемента ИЛИ i-1-го разряда, второй вход этого элемента подключен к третьему входу управления инвертированием триггера, второй вход девятого элемента И соединен с входом управления инвертированием триггера, выход этого элемента И через шестой элемент ИЛИ подключен к первым входам четвертого и пятого элементов И, к второму входу шестого элемента ИЛИ подключен вход управления занесением кода в триггер, выход седьмого элемента ИЛИ соединен с вторым входом пятого элемента И и через шестой элемент НЕ с первым входом восьмого элемента ИЛИ, второй вход его связан со вторым входом управления инвертированием триггера, выход восьмого элемента ИЛИ соединен с вторым входом четвертого элемента И, вход переноса из младшего разряда подключен к входу четвертого элемента НЕ и ко второму входу второго элемента И, выход четвертого элемента НЕ связан с вторым входом третьего элемента И, выход первого элемента НЕ соединен с вторым входом десятого элемента И; в каждый разряд введен вход управления сдвигом кода вправо без сложения, подключенный к третьему входу третьего элемента И; в каждый разряд введены двенадцатый элемент И и (вход управления сдвигом кода влево, при этом упомянутый вход управления подключен к первому входу двенадцатого элемента И, второй его вход связан с выходом восьмого элемента И младшего разряда, а выход двенадцатого элемента И подсоединен к второму входу седьмого элемента ИЛИ; в каждый разряд введен вход управления операцией логического умножения, подключенный к третьим входам третьего и четвертого элементов ИЛИ.

Предлагаемый объект позволяет повысить быстродействие выполнения операции умножения за счет совмещения во времени операций сложения и сдвига кода, обеспечивает широкий перечень выполняемых арифметических и логических операций (сложение, сложение со сдвигом вправо, инвертирование, сдвиг кода вправо, сложение по модулю 2, сдвиг кода влево, логическое сложение и логическое умножение).

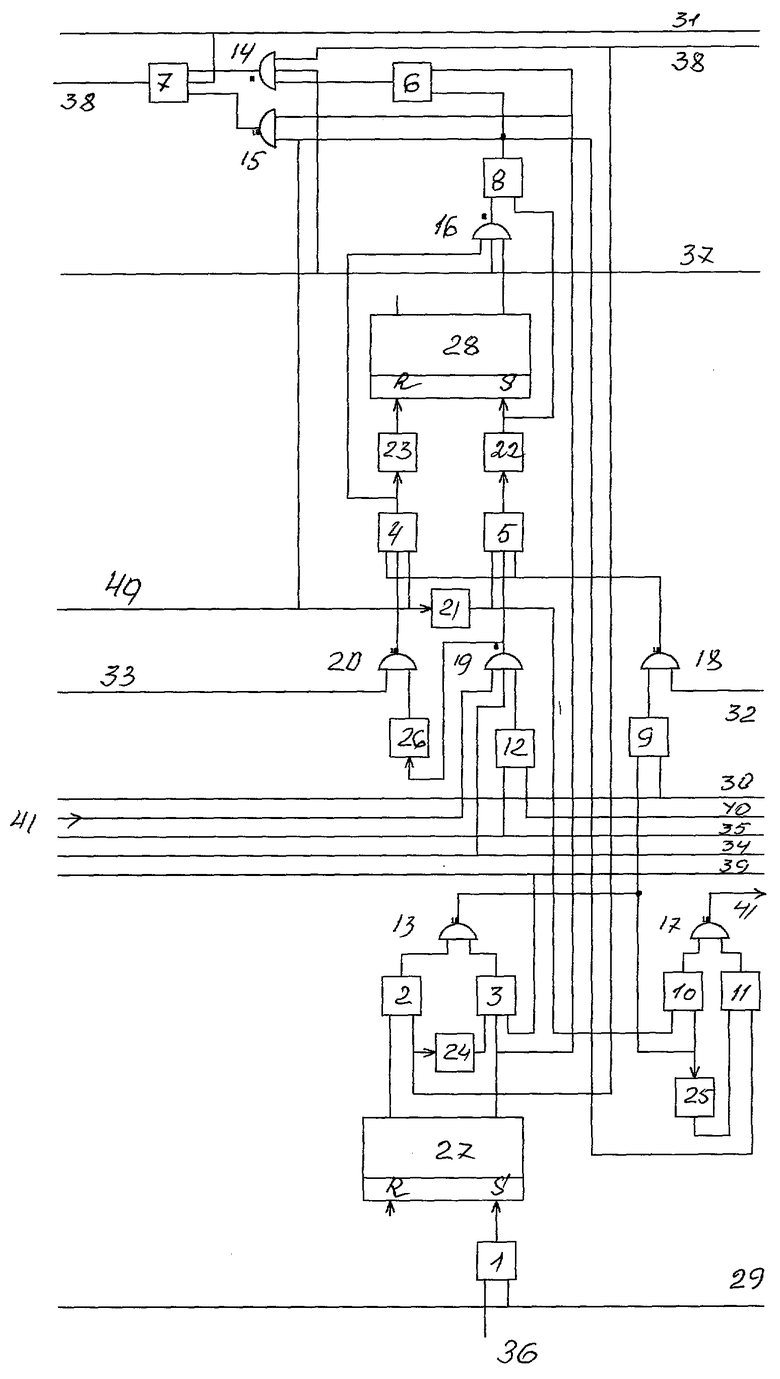

Для пояснения работы предлагаемого объект на чертеже приведена функциональная схема одного двоичного разряда, где приняты следующие обозначения: элементы И 1-12, элементы ИЛИ 13-20, элементы НЕ 21-26, RS-триггеры 27, 28, вход разрешения приема - 29, вход управления инвертированием триггера 28-30, вход управления (ВУ) запретом переноса 31, ВУ занесением кода в триггер 28-32, второй ВУ инвертированием триггера 28-33, третий ВУ инвертированием триггера 28-34, ВУ сдвигом кода влево 35, информационный вход i-того разряда 36, ВУ операций логического умножения 37, вход переноса из младшего разряда 38, ВУ сдвигом кода вправо без сложения 39, связь И 8 i-того разряда со старшим разрядом 40, связь передачи суммы в младший разряд 41.

Предложенный объект осуществляется следующим образом. Информационный вход 36 и вход разрешения приема 29 через И 1 подключены к S входу триггера 27, нулевой выход которого связаны с И 2, а единичный с элементами И 3, 6 и ИЛИ 15. Выходы элементов И 2, 3 через ИЛИ 13 соединены с выходами элементов И 9, 10 и НЕ 5, выход которого подключен к входу ИИ. Выходы И 10, 11 через ИЛИ 17 и межразрядную связь 41 соединена с входом ИЛИ 19 младшего разряда. Второй и третий входы ИЛИ 19 соединены с ВУ 34 и выходом И 12. Входы И 12 соединены с ВУ З5 и выходом И 8 младшего разряда. Выход ИЛИ 19 связан с входами И 5 и НЕ 26, выход которого через ИЛИ 20 подключен к И 4. Второй вход ИЛИ 20 связан с ВУ 33. Второй вход И 9 подключен к ВУ 30. Выход И 9 через ИЛИ 18 подключен к входам И 4, 5, выходы которых через НЕ 23, 22 связаны с R и S входами триггера 28 соответственно. Выход И 4 соединен с ИЛИ 16, второй вход которого соединен с выходом триггера 28. Выход ИЛИ 16 подключен к входу И 8, второй вход которого соединен с S входом триггера 28. Выход И 8 соединен с входами И 6, 4, 11, ИЛИ 15, НЕ 21 i-того разряда и с И 12 старшего разряда. Выход НЕ 21 подключен к входам И 5, 10. Вход переноса 38 соединен с входами ИЛИ 14, И 2, НЕ 4, выход которого соединен с И 3. Выход И 6 подключены к ИЛИ 14 Выходы ИЛИ 14, 15 связаны с входами И 7, третий вход которого соединен с ВУ 31. ВУ 37 подключены к входам ИЛИ 14, 16. ВУ 39 соединен с входом И 3.

Рассмотрим работу объекта при выполнении операций сложения, сложения со сдвигом вправо, сдвигом вправо без сложения, сдвигом влево, инвертирования, сложения по модулю два, логического сложения и умножения. В исходном положении (в статике) триггеры 27 и 28 установлены в нуль, на всех входах управления отсутствуют управляющие (высокие) потенциалы. Исключение составляет ВУ 39, на котором присутствует высокий потенциал. С выходов элементов НЕ 21-26 также поступают высокие потенциалы.

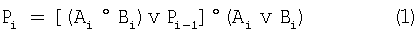

1. Операция сложения. Будем полагать, что первое и второе слагаемые хранятся в триггерах 28 и 27 как результат выполнения предыдущей операции. Операция выполняется за два временных такта t1 и t2 (под тактом понимается длительность исполнительных импульсов, поступающих на ВУ 29, 30, 32). На время выполнения операции на ВУ 31, 34 и 33 подаются высокие потенциалы. По t1 выполняется элементарная операция (ЭО) формирования сквозного переноса (Pi) в каждом разряде, согласно соотношению

Здесь Аi, Вi - значение первого и второго слагаемых i-того разряда;

Pi-1 - перенос, поступивший из младшего разряда.

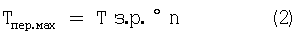

При этом длительность t1 должна быть больше или равна максимальному времени задержки выработки переносов во всех разрядах, т.е.

Здесь Тпер.мах - максимальная задержка сигнала в цепи переноса;

Тз.р - временная задержка сигнала на одном разряде объекта;

n - число двоичных разрядов.

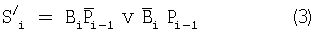

После завершения формирования сигнала сквозного переноса в каждом разряде на выходе ИЛИ 13 будет сформирована первая полусумма согласно соотношению

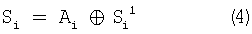

По второму такту (t2) формируется результат суммирования двух чисел Аi, Вi согласно следующему соотношению

Здесь Si - сумма i-того разряда;

Si1 - первая полусумма i-того разряда;

⊕ - знак сложения по модулю два (инвертирование).

Для завершения операции сложения, т.е. для выполнения соотношения (4), на ВУ 30 поступает исполнительный импульс. Если с выхода И 13 поступает высокий потенциал, что соответствует неравнозначности Вi и Pi-1, то исполнительный импульс по цепи ВУ 30, И 9, ИЛИ 18 поступит на первые входы И 4, 5 и проинвертирует триггер 28. На этом операция сложения завершена, в триггере 28 будет храниться сумма, а в триггере 27 - второе слагаемое. После выполнения операции с ВУ 31, 34, 33 снимаются высокие потенциалы.

2. Операция сложения со сдвигом вправо. Выполняется за два временных такта t1 и t2. По t1 формируется потенциал максимального переноса, формирование полусуммы и результат полной суммы i-того разряда. Для этого S'i, полученную на первом полусумматоре (элементы НЕ 24, И 2, 3, ИЛИ 13), суммируют на втором полусумматоре (элементы НЕ 25, И 10, 11, ИЛИ 17) с кодом, хранящимся в триггере 28. Операция выполняется согласно соотношению

При этом сигнал с выхода ИЛИ17 (Si) i-того разряда поступает на первый вход ИЛИ 19, НЕ 26, и второй вход И 5 i-1-го разряда. По t2, код суммы i-того разряда будет занесен в триггер 28 i-1-го разряда. Для этого на ВУ 32 подается исполнительный импульс, который через ИЛИ 18 поступает на первые входы И 4, 5 и занесет парафазным кодом значение Si в триггер 28 младшего разряда. Отметим, что данная операция в предложенном объекте выполняется на основе двух RS-триггеров и за два временных такта, т.е. по сравнению с комбинационным сумматором, достигается экономия оборудования и повышение быстродействия на 30% (вместо трех тактов используется только два такта).

3. Операция сдвига кода вправо без сложения. Операция сдвига кода на один разряд вправо выполняется за два временных такта t1 и t2. Для выполнения операции с ВУ 39, 31 снимутся высокие потенциалы, при этом с выхода НЕ 25 на вход И 11 будет поступать высокий потенциал. Если триггер 28 i-того разряда хранит код единицы, то с выхода И 11 через ИЛИ 17 на вход ИЛИ 19, И 5 i-1-го разряда поступит высокий потенциал. Поступивший по ВУ 32 исполнительный импульс через ИЛИ 18 поступит на первые входы И 4, 5 и установит триггер 28 этого разряда в единицу. Если в триггере 28 i-того разряда хранился код нуля, то исполнительный импульс установит триггер 28 i-1-го разряда в нуль. Второй временной такт (t2) используется для подготовки элементов объекта для прихода следующего импульса сдвига. Операция сдвига будет продолжаться до тех пор, пока на ВУ 32 будут поступать исполнительные импульсы. Для выполнения этой операции требуется только один вход элемента И 3.

4. Операция сдвига кода влево. Сдвиг кода влево, хранящегося в триггерах 28, производится за два такта на один двоичный разряд. Для выполнения этой операции на ВУ 35 подается высокий потенциал. Если триггер 28 i-того разряда хранит код единицы, то высокий потенциал по цепи ИЛИ 16, И 8 по связи 40 поступит на вход И 12 i+1-го разряда и далее через ИЛИ 19 на вход И 5. По (t1) исполнительный импульс по цепи ВУ 32, И 18, И 5, НЕ 22 поступит на S-вход триггера 28 i+1-го разряда и установит его в единицу. Если триггер 28 i-того разряда хранит код нуля, то исполнительный импульс по цепи ВУ 32, ИЛИ 18, И 4, НЕ 23 поступит на R-вход триггера старшего разряда и установит его в нуль. Для выполнения этой операции требуется всего три входа элементов И, ИЛИ.

5. Операция инвертирования. Для выполнения этой операции на ВУ 33, 34 подаются управляющие потенциалы, а с ВУ 31 снимается высокий потенциал. По (t1) на ВУ 32 поступает исполнительный импульс. Если первоначально триггер 28 хранил код единицы, то исполнительный импульс по цепи ВУ 32, ИЛИ 18, И 4, НЕ 23 поступит на R-вход триггера и установит его в нуль. Выполнение операции не требует дополнительного оборудования.

6. Операция сложения по модулю два. Операция выполняется за два временных такта. Для ее выполнения на ВУ 34, 33 подаются высокие потенциалы, а с ВУ 31 снимается высокий потенциал. Первое слагаемое хранится в триггерах 28, а второе принимается с информационного входа 36 и через И 1 в триггер 27. При выполнении операции высокий потенциал с единичного входа триггера 27 по цепи элементов И 3, ИЛИ 13 поступит на вход И 9. По (t1) исполнительный импульс по ВУ 30, И 9, ИЛИ 18 поступит на первые входы И 4, 5 и проинвертирует код триггера 28. Если код триггера 27 равен нулю, то значение триггера 28 не меняется. Второй временной такт используется для подготовки схемы к выполнению последующих операций. Для выполнения этой операции не требуется дополнительного оборудования.

7. Операция логического сложения. Операция выполняется за два временных такта. Слагаемые хранятся в триггерах 28 и 27. Для выполнения операции с ВУ 31 снимается высокий потенциал, а на ВУ 34 подается высокий потенциал, который через ИЛИ 19 поступает на второй вход И 5 и на вход НЕ 26. При этом будет запрещена работа И 4 и разрешена работа И 5. Если триггер 27 хранит код единицы, то исполнительный импульс с ВУ 30, И 9, ИЛИ 18, И 5, НЕ 22 поступит на S-вход триггера 28 и установит его в единицу. В противоположном случае состояние триггера 28 не меняется. Второй такт используется для подготовки схемы к выполнению последующих операций. Для выполнения операции не требуется дополнительного оборудования.

8. Операция логического умножения. Выполняется за два такта. Для ее выполнения на ВУ 31, 33 и 37 подаются высокие потенциалы, которые подготавливают И 4 для прохождения на R-вход триггера 28 исполнительного импульса. Если триггер 27 хранит код нуля, а потенциал переноса из младшего разряда поступит на второй вход И 2 старшего разряда, то с выхода упомянутого И 2 через ИЛИ 13 на первый вход И 9 поступит высокий потенциал. Исполнительный импульс с ВУ 30 через ИЛИ 18, И 4, НЕ 23 поступит на R-вход триггера 28 и установит его в нуль. На этом операция заканчивается. Для ее выполнения требуется два входа элементов ИЛИ в качестве дополнительного оборудования.

Таким образом, предлагаемый объект позволяет выполнять функции как комбинационно-накапливающего, так и комбинационного сумматоров, при этом повышается быстродействие выполнения операций сложения и умножения на 30%, число RS-триггеров в каждом разряде доведено до двух (вместо трех), расширен перечень выполняемых объектом операций до 8 (сложение, сложение с одновременным сдвигом вправо, сдвиг вправо, сдвиг влево, инвертирование, сложение по модулю два, логическое сложение и умножение). Отмеченные преимущества обеспечены при минимальных затратах аппаратных средств: операции инвертирования, сложение по модулю два и логического сложения не требует дополнительного оборудования, операция сдвига кода вправо требует только одного дополнительного входа элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ДВОИЧНЫХ КОДОВ | 2010 |

|

RU2410746C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия и расширение перечня выполняемых операций при минимальных аппаратурных затратах. Указанный результат достигается за счет того, что сумматор в каждом разряде содержит два RS-триггера, двенадцать элементов И, восемь элементов ИЛИ, шесть элементов НЕ и десять входов управления. 3 з.п. ф-лы, 1 ил.

| Накапливающий сумматор | 1985 |

|

SU1262479A1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| 1972 |

|

SU416869A1 |

Авторы

Даты

2007-01-20—Публикация

2005-07-04—Подача