Изобретение относится к области вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики. Известны способы и устройства вычитания двоичных кодов, содержащие триггерные регистры, логические элементы И, ИЛИ, НЕ и входы управления работой устройства. Варианты способов и устройств вычитания рассмотрены в книге Карцева М.А., «Арифметика цифровых машин», изд. Наука, 1969 г., стр.288-297, рис 3-1а, стр 294. Устройство, приведенное на рис.3-1а, стр.294, является ближайшим прототипом предлагаемого устройства. В указанном источнике операция вычитания выполняется на основе оборудования, предназначенного для выполнения операции сложения двоичных кодов, сделана оценка вариантов алгебраического вычитания в прямых, дополнительных и обратных кодах. При этом существенных преимуществ в сокращении времени вычитания не приводится. Основные элементарные операции (ЭО), выполняемые в известных устройствах при вычитании, следующие: прием вычитаемого, обращение (инвертирование) кода вычитаемого, формирование переноса и суммы, занесение результата суммирования в регистр уменьшаемого и прибавление единицы к коду младшего разряда устройства. Указанный перечень выполняемых ЭО определяет быстродействие операции вычитания. Это следует считать недостатком известных способов и устройств выполнения вычитания. Предлагаемый способ и устройство снижают этот недостаток.

Целью предлагаемого способа и устройства является повышение быстродействия выполнения операции вычитания за счет совмещения во времени выполнения ЭО приема вычитаемого и формирования потенциала заема, а также исключения затрат времени на выполнение первого обращения вычитаемого. Для этого предложен способ вычитания двоичных кодов, отличающийся тем, что операцию выполняют с кодом чисел, имеющих равные значения знаков уменьшаемого и вычитаемого, при этом уменьшаемое хранят в прямом коде в первом триггерном регистре А, по первому временному такту выполняют прием вычитаемого, поступающего по информационным входам в прямом коде, путем выполнения первой операции логического умножения потенциалов информационного входа и первого входа управления приемом кода вычитаемого во второй триггерный регистр В, если результат упомянутой операции i-того разряда равен единице, то первый триггер Ai устанавливают в нуль; выполняют вторую операцию логического умножения потенциалов первой операции логического умножения и инверсного значения выхода первого триггера Ai, если результат второй операции логического умножения равен единице, то этот потенциал подают на первый вход третьего элемента И и через первый элемент НЕ - на первый вход четвертого элемента И, на вторые входы упомянутых элементов И подают исполнительный импульс второго входа управления парафазным приемом вычитаемого во второй триггерный регистр В, при этом второй триггер Bi устанавливают в единицу, кроме того, потенциал первой операции логического умножения подключают к входу четвертого элемента ИЛИ, потенциал второй операции логического умножения подключают к первому входу первого элемента ИЛИ, к второму входу которого подключают потенциал заема из i-1-го разряда; потенциал инверсного значения первого триггера Ai подключают к первому входу второго элемента ИЛИ, второй вход которого подключают к выходу пятого элемента И, потенциал выхода которого является результатом третьей операции логического умножения потенциалов единичного выхода первого триггера Ai, подключенного к второму входу пятого элемента И через третий элемент ИЛИ и двенадцатый элемент И, и потенциала первой операции логического умножения, результат четвертой операции логического умножения потенциалов с выходов первого и второго элементов ИЛИ является входом потенциала заема в i+1-тый разряд; по истечении максимальной временной задержки сигнала заема единицы в старших разрядах, по второму временному такту поддерживают потенциал заема, выработанный в i-том разряде по первому временному такту, за счет передачи потенциала единичного выхода второго триггера Bi через тринадцатый элемент И, к второму входу которого подключают третий вход управления формированием потенциала заема по второму временному такту, выход тринадцатого элемента И соединяют с третьим входом первого элемента ИЛИ; одновременно с сохранением выработанных потенциалов заемов, подают на четвертый вход управления формированием результата вычитания в триггерах первого регистра А исполнительный импульс, который инвертирует код первого триггера Ai, если из i-1-го разряда поступил потенциал заема или потенциал единичного выхода второго триггера Bi равен единице; если упомянутые потенциалы в i-том разряде присутствуют одновременно, то инверсное значение результата пятой операции логического умножения потенциалов заема i-1-го разряда и единичного выхода второго триггера Bi запрещают инвертирование первого триггера Ai; также по второму временному такту при наличии потенциала заема из самого старшего разряда, устанавливают в единицу триггер хранения потенциала упомянутого заема и формируют знак кода первого регистра А путем сложения по модулю два кода триггера знака упомянутого регистра с потенциалом заема из самого старшего разряда, кроме того, при нулевых значениях всех триггеров регистра А устанавливают в нуль триггер знака кода первого регистра А; по третьему временному такту формируют потенциал циклического заема единицы, если триггер хранения потенциала заема из самого старшего разряда установлен предыдущим временным тактом в единицу, упомянутый потенциал с единичного выхода третьего триггера через четырнадцатый элемент И, на второй вход которого через пятнадцатый элемент ИЛИ подключают входы третьего и четвертого временных тактов, соединяют с входами первого элемента ИЛИ и третьего элемента НЕ самого младшего разряда, выход третьего элемента НЕ запрещает работу седьмого элемента И, проходит во второй разряд, если первый триггер первого разряда хранит код нуля, и запрещает работу седьмого элемента И второго разряда, по четвертому временному такту выполняют инвертирование триггеров регистра А и добавление единицы к первому разряду устройства, для этого на пятый вход управления инвертированием кода регистра А подают исполнительный импульс, который подключают к первому входу седьмых элементов И, второй вход которых соединяют с выходами третьих элементов НЕ каждого разряда, вход этого элемента НЕ подключают к входу потенциала заема кода из младшего разряда или к входу потенциала циклического заема в первом разряде, выход седьмого элемента И через пятый и четвертый элементы ИЛИ соединяют со счетным входом первого триггера Ai, при отсутствии потенциала заема из младшего разряда, исполнительный импульс инвертирования поступит на счетный вход первого триггера Ai и выполнит инвертирование кода, хранящегося в этом триггере, если в младший разряд поступил потенциал циклического заема и первый триггер первого разряда хранит код нуля, то упомянутый триггер не будет проинвертирован; если группа триггеров A1, A2, A3 и т.д. хранит коды нулей, то эти триггеры не будут инвертироваться, также не будет инвертироваться первый триггер, хранящий код единицы после окончания группы триггеров с нулевыми значениями кодов, на этом операцию вычитания заканчивают, результат вычитания хранят в первом регистре А в прямом коде.

Также предложено устройство вычитания двоичных кодов, содержащее первый n-разрядный триггерный регистр уменьшаемого А, второй n-разрядный триггерный регистр вычитаемого В, выполненное на элементах И, ИЛИ, НЕ и RS-триггерах, содержащее в каждом двоичном разряде тринадцать элементов И, шесть элементов ИЛИ, шесть элементов НЕ, два RS-триггера, информационный вход, пять входов управления, отличающееся тем, что информационный вход i-того разряда соединен с первым входом первого элемента И, второй вход первого элемента И связан с первым входом управления приемом кода вычитаемого во второй триггерный регистр В, выход первого элемента И соединен с первыми входами второго и пятого элементов И и четвертого элемента ИЛИ, второй вход второго элемента И соединен с выходом четвертого элемента НЕ и первым входом второго элемента ИЛИ, выход второго элемента И соединен с первым входом первого элемента ИЛИ, с первым входом третьего элемента И и входом первого элемента НЕ, выход которого соединен с первым входом четвертого элемента И, вторые входы третьего и четвертого элементов И всех разрядов и нулевой вход триггера хранения потенциала заема из самого старшего разряда связаны с вторым входом управления парафазным приемом вычитаемого во второй триггерный регистр В, выходы упомянутых элементов И соединены с единичным и нулевым входами второго триггера Bi, единичный выход которого соединен с первыми входами шестого элемента ИЛИ, десятого и тринадцатого элементов И, второй вход тринадцатого элемента И соединен с третьим входом управления формированием потенциала заема по второму временному такту, вход заема из младшего разряда соединен с вторым входом первого элемента ИЛИ, с входом третьего элемента НЕ и с вторыми входами десятого элемента И и шестого элемента ИЛИ, выход которого соединен с первым входом одиннадцатого элемента И, выход десятого элемента И через второй элемент НЕ связан с вторым входом одиннадцатого элемента И, третий вход которого подключен к четвертому входу управления формированием результата вычитания в триггерах первого регистра А, выход третьего элемента НЕ соединен с первым входом седьмого элемента И, второй вход которого подключен к пятому входу управления инвертированием кода триггеров регистра А, выходы одиннадцатого и седьмого элементов И соединены с входами пятого элемента ИЛИ, выход которого подключен к первым входам четвертого элемента ИЛИ и девятого элемента И, выход четвертого элемента ИЛИ соединен с первым входом восьмого элемента И, выходы восьмого и девятого элементов И через пятый и шестой элементы НЕ подключены к нулевому и единичному входам первого RS-триггера, выход восьмого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к единичному выходу первого RS-триггера, выход третьего элемента ИЛИ соединен с первым входом двенадцатого элемента И, второй вход которого подключен к выходу шестого элемента НЕ, выход двенадцатого элемента И соединен с вторыми входами восьмого и пятого элементов И и входом четвертого элемента НЕ, выход четвертого элемента НЕ подключен к первому входу девятого элемента И, выходы первого и второго элементов ИЛИ соединены с входами шестого элемента И, выход которого является потенциалом заема единицы из старших разрядов и подключен к второму входу первого элемента ИЛИ, третьего элемента НЕ, к вторым входам шестого элемента ИЛИ и десятого элемента И i+1-го разряда, устройство также содержит третий и четвертый RS-триггеры хранения потенциалов заема из самого старшего разряда и знака кода первого регистра А соответственно, при этом входы пятнадцатого элемента И соединены с четвертым входом управления и выходом потенциала заема из самого старшего разряда, выход пятнадцатого элемента И через двадцатый элемент ИЛИ, семнадцатый И, двадцать шестой элемент НЕ соединен с нулевым входом четвертого RS-триггера; через элементы восемнадцатый И, двадцать седьмой НЕ выход пятнадцатого элемента И связан с единичным входом четвертого RS-триггера, выход семнадцатого И соединен с двадцать первым ИЛИ, второй его вход подключен к единичному выходу четвертого RS-триггера, выход которого соединен с первым входом девятнадцатого элемента И, второй его вход подключен к выходу двадцать седьмого НЕ, выход девятнадцатого элемента И соединен с входами двадцать восьмого элемента НЕ и семнадцатого элемента И, выход упомянутого элемента НЕ соединен с входом восемнадцатого элемента И, перечисленные элементы и связи обеспечивают работу четвертого триггера в режиме счета импульсов, кроме того, выход пятнадцатого элемента И связан с единичным входом третьего RS-триггера; входы двадцатого элемента И соединены с выходами четвертых элементов НЕ всех разрядов устройства, сигнал с выхода этого элемента является признаком наличия нулевых значений первых триггеров всех разрядов и соединен с первым входом шестнадцатого элемента И, второй вход которого соединен с четвертым входом управления формированием результата вычитания в триггерах регистра А, выход шестнадцатого элемента И через элементы двадцатый ИЛИ, семнадцатый И, двадцать шестой НЕ соединен с нулевым входом четвертого RS-триггера, при этом входы третьего и четвертого временных тактов через двадцать второй элемент ИЛИ соединены с входом четырнадцатого элемента И, второй его вход соединен с единичным выходом третьего RS-триггера, выход четырнадцатого элемента И является потенциалом циклического заема и соединен с входами первого элемента ИЛИ и третьего элемента НЕ самого младшего разряда.

Рассмотрим основные отличительные признаки предлагаемых способа и устройства и покажем, что они обеспечивают.

1. Предложенный способ за счет совмещения во времени приема вычитаемого и формирования потенциала заема позволяет выполнить операцию вычитания минимум за два временных такта. В известных устройствах это время равно четырем тактам.

2. Исключается первое обращение кода вычитаемого.

3. В ходе выполнения первого временного такта осуществляется вычитание кода единиц, хранящихся в триггерах регистра А и поступающих по информационным входам одноименных разрядов, что позволяет выполнить операцию вычитания равных кодов за один временной такт. Также за один временной такт выполняется операция вычитания при значении кодов регистра А, равных 11111, 01111, при любых кодах вычитаемого В, меньшего кода А по модулю.

4. Вторая ЭО логического умножения выполняется за счет соединения выхода первого элемента И с входом четвертого элемента НЕ. Соединение выхода второго элемента И i-того разряда с первым входом первого элемента ИЛИ позволяет начать формирование потенциала заема (ПЗ) во время первого временного такта.

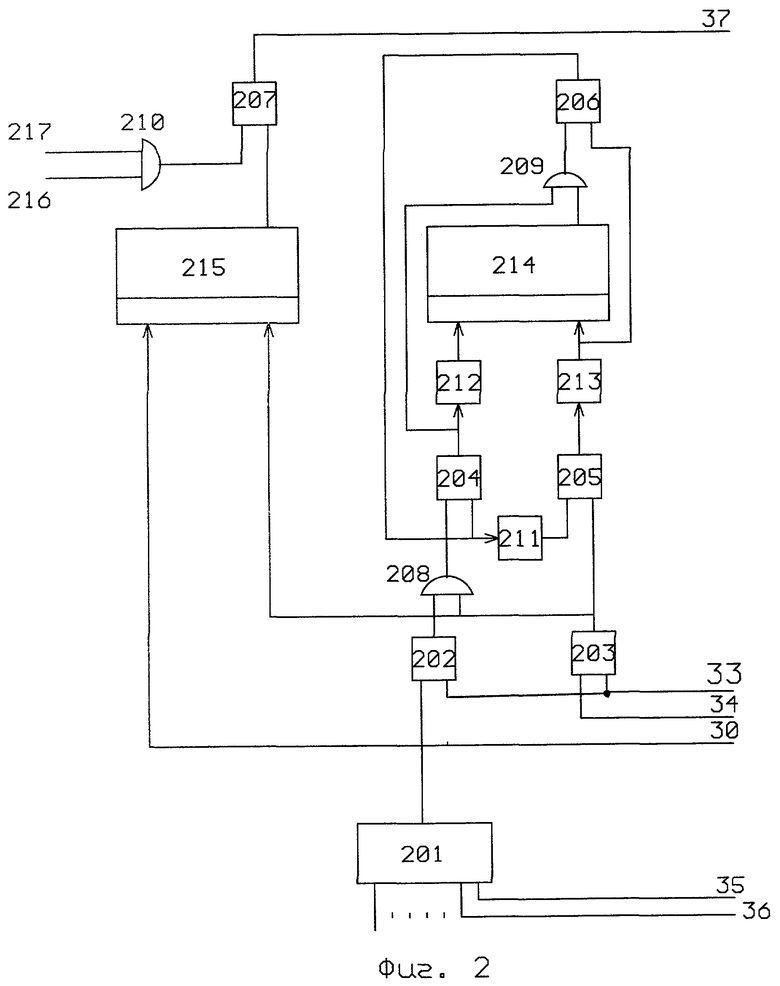

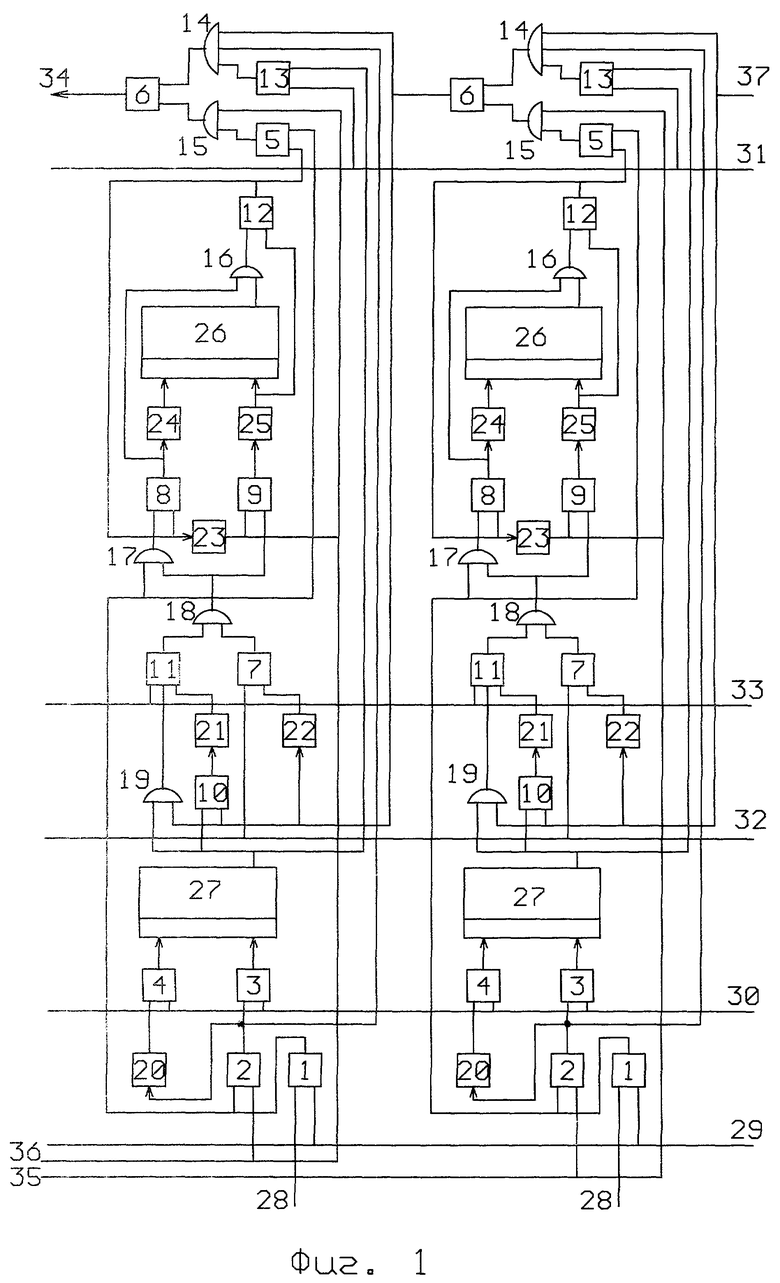

На фиг.1 приведена функциональная схема двух разрядов предлагаемого устройства. Каждый разряд содержит элементы И 1-13, элементы ИЛИ 14-19, элементы НЕ 20-25, RS-триггеры (Tr) 26, 27, информационный вход (ИВ) 28, первый - пятый входы управления (ВУ) 29-33, выход потенциала заема из младшего в старший разряд 34, информационные связи определения нулевого значения триггеров первого и второго разрядов регистра А 35, 36…, выход потенциала циклического заема (ПЦЗ), хранящийся в Тr 215, передаваемый в первый разряд 37. На фиг.2. приведена функциональная схема формирования и хранения знака кода первого регистра А Тr 214, триггер хранения потенциала заема из самого старшего разряда устройства Тr 215, элементы И 201-207, элементы ИЛИ 208-210, элементы НЕ 211-213, вход третьего временного такта (ВТ3) 216, вход четвертого временного такта (ВТ4) 217.

Рассмотрим работу устройства при выполнении операции вычитания. В исходном состоянии (в статике) в триггерах 26 регистра А хранится прямой код разности, полученной от выполнения предыдущей операции вычитания. В триггере 214 может храниться код знака разности. В Тr 27 регистра В хранится результат второй операции логического умножения предыдущей операции вычитания. Знак кода вычитаемого, принятого в регистр В, всегда совпадает с значением знака уменьшаемого. Полагаем, что засылку уменьшаемого в устройство вычитания выполняет устройство управления (УУ) работой вычислительного комплекса по значению знака уменьшаемого. На входах управления ВУ 29-33 и на информационном входе 28 отсутствуют высокие потенциалы. Операция вычитания выполняется за четыре временных такта ВТ1-ВТ4. Это максимальное время выполнения операции. Минимальное время выполнения вычитания равняется одному временному такту.

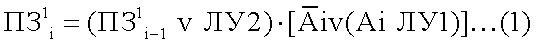

По ВТ1 во всех разрядах выполняется первая ЭО логического умножения (ЛУ1) потенциалов ВУ 29 и ИВ 28. Для этого на входы ВУ 29 и ИВ 28 поступают высокие потенциалы. На выходе И1 вырабатывается высокий потенциал. Упомянутый потенциал поступает на ИЛИ 17 и устанавливает Тr 26 в нуль, одновременно упомянутый сигнал поступает на вход И5. При наличии высокого потенциала с выхода И 12, на выходе И5 будет выработан потенциал, который через ИЛИ 5 поступит на вход И6. Выполняется вторая операция ЛУ 2 сигналов с выхода И1 и с выхода НЕ 23. Потенциал результата ЛУ 2 через ИЛИ 14 поступает на второй вход И6, потенциал с выхода этого элемента является потенциалом заема единицы в старших разрядах. Упомянутый потенциал вырабатывается согласно следующему соотношению.

Здесь приняты обозначения:

ПЗ1 i - потенциал заема, выработанный по ВТ1 в i-том разряде;

ПЗ1 i-1 - потенциал заема, выработанный по ВТ1 в i-1-том разряде;

ЛУ1,2 - потенциалы первой и второй ЭО логического умножения;

Ai,  - прямое и инверсное значения триггера Аi-того разряда.

- прямое и инверсное значения триггера Аi-того разряда.

Выработанный в i-том разряде ПЗ распространяется в сторону старших разрядов по цепи элементов ИЛИ 14, 15, И 6. Потенциал ЛУ 2 также поступает на первый вход И3 и через элемент НЕ 20 - на первый вход И4. На вторые входы И 3, 4 поступит исполнительный импульс по ВУ 30 и осуществит прием сигнала с ИВ 28 парафазным кодом в Тr 27. В случае отсутствия высокого потенциала с выхода И2, Тr 27 будет установлен в нуль, а при наличии упомянутого потенциала - в единицу. По этому же временному такту сигнал, поступивший на ВУ 30, поступает на нулевой вход Тr 215 и устанавливает его в нуль.

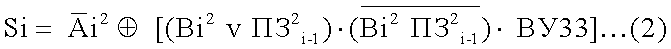

По ВТ2, после завершения распространения потенциала заема во всех разрядах устройства, выполняются ЭО формирования разности путем выполнения логического соотношения (2).

Здесь обозначены:

Si - разность i-того разряда;

Ai2, Bi2 - значения триггеров i - того разряда по времени ВТ2;

ПЗ2 i-1 - потенциал заема единицы, выработанный в младшем разряде;

ВУ33 - четвертый вход управления формированием результата вычитания;

⊕ - знак сложения по модулю два.

Для этого на ВУ 33 поступает исполнительный импульс, который при наличии высоких потенциалов на первом и втором входах И 11, по цепи элементов И11, ИЛИ 18, 17 поступит на вторые входы И8, 9 и выполнит инвертирование кода Тr 26. При этом при переключении триггера из единицы в нуль высокий потенциал с выхода И 12 будет поступать на первый вход И8 и на вход НЕ 23 неизменным на время длительности исполнительного импульса, поступившего на ВУ33, за счет связи с выхода И8 через ИЛИ 16 с входом И 12. При переключении Тr 26 из нуля в единицу нулевой потенциал с выхода И 12 и высокий потенциал с выхода НЕ 23 не изменят своего значения за счет связи с выхода НЕ 25 с вторым входом И 12 на время длительности исполнительного импульса, поступившего на ВУ 33. Таким образом код Тr 26 будет проинвертирован с одновременной задержкой сигнала с выхода И 12, независимо от момента переключения RS-триггера в пределах длительности исполнительного импульса, выполняющего ЭО сложения по модулю два (или инвертирование) Тr 26. В том случае если в i-том разряде присутствуют одновременно В2i=1 и ПЗ2 i-1=1, то инвертирование Тr 26 запрещается низким потенциалом с выхода НЕ 7. Также по ВТ2 выполняется ЭО запоминания потенциала заема, выработанного в самом старшем разряде устройства, и формирование знака разности. Знак разности формируется путем инвертирования Тr 214 при наличии потенциала ПЗ из самого старшего разряда и исполнительного импульса на ВУ33. При этом сигнал инвертирования вырабатывается на выходе И 203 и через ИЛИ 208 поступает на вход И 204 и прямо на вход И 205, т.е на счетный вход триггера 214. Одновременно сигнал с выхода И 203 поступает на единичный вход Тr 215 и устанавливает его в единицу. Если Тr 215 по ВТ2 в единицу не установлен, что имеет место при |А|>|В|, то операция вычитания на этом заканчивается. В случае |А|<|В| вырабатывается ПЗ из самого старшего разряда, Тr 215 устанавливается в единицу, и требуется продолжить выполнение операции вычитания по ВТ3 и ВТ4.

По ВТ3 и ВТ4 выполняются ЭО инвертирования триггеров 26 и прибавление единицы к коду первого разряда, если триггер 215 по ВТ2 установлен в единицу. Для выполнения ЭО добавления единицы к коду регистра А по ВТ3 формируют потенциал циклического заема с выхода И207, входы которого соединены с единичным выходом Тr 215 и с выходом ИЛИ 210.

Сигнал с выхода И 207 поступает на входы ИЛИ 14 и НЕ 22 первого разряда. Если Тr 26 первого разряда хранит код нуля, то потенциал по цепи элементов ИЛИ 14, И6 поступает в старшие разряды, триггеры которых хранят код нуля.

По ВТ4 на ВУ 32 поступает исполнительный импульс инвертирования кода триггеров регистра А. Если на вход НЕ 22 i-того разряда не поступил потенциал циклического заема, сформированный по ВТ3, то исполнительный импульс с ВУ32 пройдет по цепи элементов И7, ИЛИ 18, ИЛИ17, поступит на входы И 8, 9, т.е на счетный вход, и выполнит инвертирование Тr 26. Если на вход НЕ 22 поступил сигнал, ПЦЗ или сформированный на выходе И6 младшего разряда, то через И7, ИЛИ 18, 17 на счетный вход Тr 26 не пройдет исполнительный импульс инвертирования и упомянутый триггер сохранит прежнее состояние.

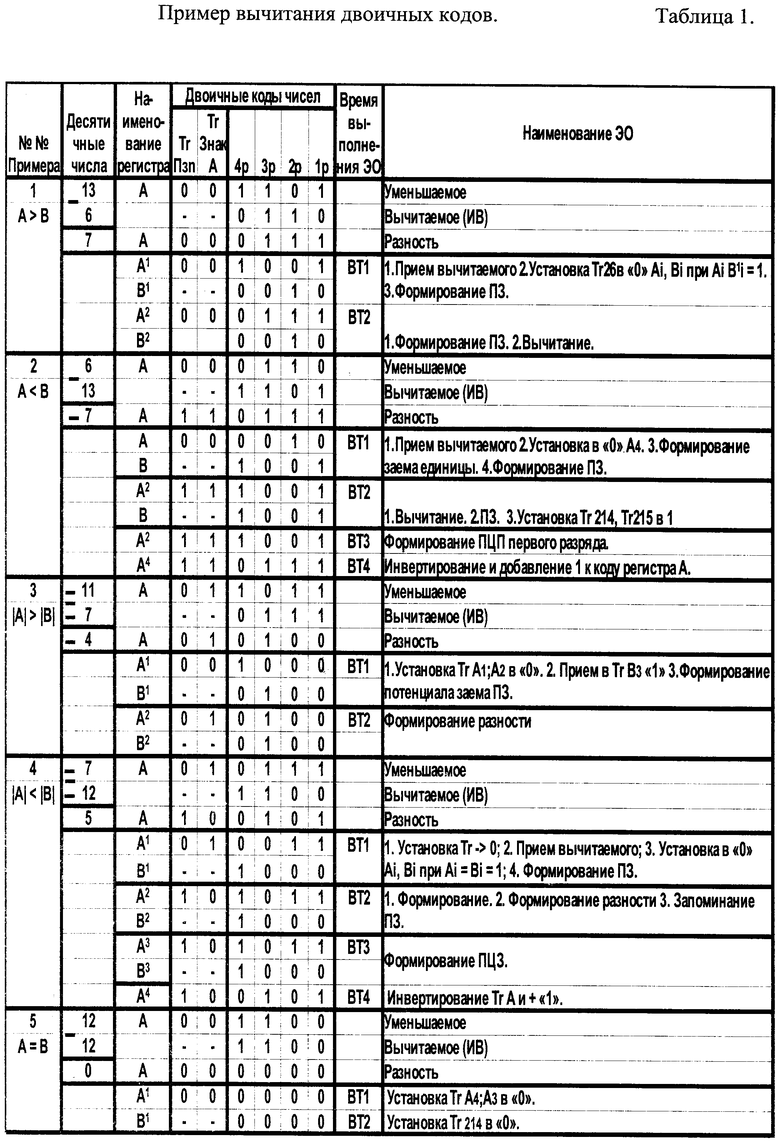

В случае вычитания отрицательного кода В из отрицательного кода А, равных по модулю, требуется установить Тr 214 в нуль при нулевых значениях триггеров регистра А по ВТ2. Для этого выходы НЕ 23 всех разрядов устройства с помощью информационных связей 35, 36… соединяют с входами И 201. По второму временному такту при наличии высокого потенциала на выходах И 201 и на ВУ33, с выхода И 202 через ИЛИ 208, И 204, НЕ 212 на нулевой вход Тr 214 поступит сигнал и установит его в нуль. В таблице 1 приведены примеры выполнения вычитания двоичных кодов.

Таким образом, предлагаемый способ и устройство выполняют операцию вычитания целых двоичных чисел и обеспечивают повышение быстродействия по сравнению с известными устройствами.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ЕДИНИЦ | 2014 |

|

RU2540787C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2004 |

|

RU2284653C2 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и устройствах цифровой автоматики. Техническим результатом является повышение быстродействия выполнения операции вычитания за счет совмещения во времени выполнения элементарной операции приема вычитаемого и формирования потенциала заема. В способе по первому временному такту ВТ1 выполняют первую и вторую элементарные операции (ЭО) логического умножения (ЛУ), по результатам которых формируют потенциал заема (ПЗ) единицы в старших разрядах, принимают код ЛУ2 во второй регистр В и устанавливают триггеры регистра А в нуль при единичных кодах разрядов уменьшаемого и вычитаемого. По второму ВТ2 выполняют ЭО сложения по модулю два кода Ai с ПЗ из младшего разряда или кодом Bi. При наличии упомянутых сигналов в i-том разряде одновременно сложение по модулю два запрещают. По Вт2 также формируют знак разности и запоминают ПЗ из самого старшего разряда. При ПЗ=0, т.е. при |А|>|В|, заканчивают выполнение операции. При ПЗ=1, т.е. |А|<|В|, по ВТ 3, 4 выполняют инвертирование кода регистра А с добавлением единицы в младший разряд устройства. Устройство содержит элементы И, элементы ИЛИ, элементы НЕ, RS-триггеры и входы управления. 2 н.п. ф-лы, 2 ил., 1 табл.

1. Способ вычитания двоичных кодов, отличающийся тем, что операцию выполняют с кодом чисел, имеющих равные значения знаков уменьшаемого и вычитаемого, при этом уменьшаемое хранят в прямом коде в первом триггерном регистре А, по первому временному такту выполняют прием вычитаемого, поступающего по информационным входам в прямом коде, путем выполнения первой операции логического умножения потенциалов информационного входа и первого входа управления приемом кода вычитаемого во второй триггерный регистр В, если результат упомянутой операции i-го разряда равен единице, то первый триггер Ai устанавливают в нуль; выполняют вторую операцию логического умножения потенциалов первой операции логического умножения и инверсного значения выхода первого триггера Ai, если результат второй операции логического умножения равен единице, то этот потенциал подают на первый вход третьего элемента И и через первый элемент НЕ на первый вход четвертого элемента И, на вторые входы упомянутых элементов И подают исполнительный импульс второго входа управления парафазным приемом вычитаемого во второй триггерный регистр В, при этом второй триггер Bi устанавливают в единицу, кроме того, потенциал первой операции логического умножения подключают к входу четвертого элемента ИЛИ, потенциал второй операции логического умножения подключают к первому входу первого элемента ИЛИ, к второму входу которого подключают потенциал заема из i-1-го разряда; потенциал инверсного значения первого триггера Ai подключают к первому входу второго элемента ИЛИ, второй вход которого подключают к выходу пятого элемента И, потенциал выхода которого является результатом третьей операции логического умножения потенциалов единичного выхода первого триггера Ai, подключенного к второму входу пятого элемента И через третий элемент ИЛИ и двенадцатый элемент И, и потенциала первой операции логического умножения, результат четвертой операции логического умножения потенциалов с выходов первого и второго элементов ИЛИ является входом потенциала заема в i+1-й разряд; по истечении максимальной временной задержки сигнала заема единицы в старших разрядах, по второму временному такту поддерживают потенциал заема, выработанный в i-м разряде по первому временному такту, за счет передачи потенциала единичного выхода второго триггера Bi через тринадцатый элемент И, к второму входу которого подключают третий вход управления формированием потенциала заема по второму временному такту, выход тринадцатого элемента И соединяют с третьим входом первого элемента ИЛИ; одновременно с сохранением выработанных потенциалов заемов, подают на четвертый вход управления формированием результата вычитания в триггерах первого регистра А исполнительный импульс, который инвертирует код первого триггера Ai, если из i-1-го разряда поступил потенциал заема или потенциал единичного выхода второго триггера Bi равен единице; если упомянутые потенциалы в i-м разряде присутствуют одновременно, то инверсное значение результата пятой операции логического умножения потенциалов заема i-1-го разряда и единичного выхода второго триггера Bi запрещают инвертирование первого триггера Ai; также по второму временному такту при наличии потенциал заема из самого старшего разряда, устанавливают в единицу триггер хранения потенциала упомянутого заема и формируют знак кода первого регистра А путем сложения по модулю два кода триггера знака упомянутого регистра с потенциалом заема из самого старшего разряда, кроме того, при нулевых значениях всех триггеров регистра А устанавливают в нуль триггер знака кода первого регистра А; по третьему временному такту формируют потенциал циклического заема единицы, если триггер хранения потенциала заема из самого старшего разряда установлен предыдущим временным тактом в единицу, упомянутый потенциал с единичного выхода третьего триггера через четырнадцатый элемент И, на второй вход которого через пятнадцатый элемент ИЛИ подключают входы третьего и четвертого временных тактов, соединяют с входами первого элемента ИЛИ и третьего элемента НЕ самого младшего разряда, выход третьего элемента НЕ запрещает работу седьмого элемента И, проходит во второй разряд, если первый триггер первого разряда хранит код нуля, и запрещает работу седьмого элемента И второго разряда, по четвертому временному такту выполняют инвертирование триггеров регистра А и добавление единицы к первому разряду устройства, для этого на пятый вход управления инвертированием кода регистра А подают исполнительный импульс, который подключают к первому входу седьмых элементов И, второй вход которых соединяют с выходами третьих элементов НЕ каждого разряда, вход этого элемента НЕ подключают к входу потенциала заема кода из младшего разряда или к входу потенциала циклического заема в первом разряде, выход седьмого элемента И через пятый и четвертый элементы ИЛИ соединяют со счетным входом первого триггера Ai, при отсутствии потенциала заема из младшего разряда, исполнительный импульс инвертирования поступит на счетный вход первого триггера Ai и выполнит инвертирование кода, хранящегося в этом триггере, если в младший разряд поступил потенциал циклического заема и первой триггер первого разряда хранит код нуля, то упомянутый триггер не будет проинвертирован; если группа триггеров А1, А2, A3 и т.д. хранит коды нулей, то эти триггеры не будет инвертироваться, также не будет инвертироваться первый триггер, хранящий код единицы после окончания группы триггеров с нулевыми значениями кодов, на этом операцию вычитания заканчивают, результат вычитания хранят в первом регистре А в прямом коде.

2. Устройство вычитания двоичных кодов, содержащее первый n-разрядный триггерный регистр уменьшаемого А, второй n-разрядный триггерный регистр вычитаемого В, выполненное на элементах И, ИЛИ, НЕ и RS-триггерах, содержащее в каждом двоичном разряде тринадцать элементов И, шесть элементов ИЛИ, шесть элементов НЕ, два RS-триггера, информационный вход, пять входов управления, отличающееся тем, что информационный вход i-го разряда соединен с первым входом первого элемента И, второй вход первого элемента И связан с первым входом управления приемом кода вычитаемого во второй триггерный регистр В, выход первого элемента И соединен с первыми входами второго и пятого элементов И и четвертого элемента ИЛИ, второй вход второго элемента И соединен с выходом четвертого элемента НЕ и первым входом второго элемента ИЛИ, выход второго элемента И соединен с первым входом первого элемента ИЛИ, с первым входом третьего элемента И и входом первого элемента НЕ, выход которого соединен с первым входом четвертого элемента И, вторые входы третьего и четвертого элементов И всех разрядов и нулевой вход триггера хранения потенциала заема из самого старшего разряда связаны с вторым входом управления парафазным приемом вычитаемого во второй триггерный регистр В, выходы упомянутых элементов И соединены с единичным и нулевым входами второго триггера Bi, единичный выход которого соединен с первыми входами шестого элемента ИЛИ, десятого и тринадцатого элементов И, второй вход тринадцатого элемента И соединен с третьим входом управления формированием потенциала заема по второму временному такту, вход заема из младшего разряда соединен с вторым входом первого элемента ИЛИ, с входом третьего элемента НЕ и с вторыми входами десятого элемента И и шестого элемента ИЛИ, выход которого соединен с первым входом одиннадцатого элемента И, выход десятого элемента И через второй элемент НЕ связан с вторым входом одиннадцатого элемента И, третий вход которого подключен к четвертому входу управления формированием результата вычитания в триггерах первого регистра А, выход третьего элемента НЕ соединен с первым входом седьмого элемента И, второй вход которого подключен к пятому входу управления инвертированием кода триггеров регистра А, выходы одиннадцатого и седьмого элементов И соединены с входами пятого элемента ИЛИ, выход которого подключен к первым входам четвертого элемента ИЛИ и девятого элемента И, выход четвертого элемента ИЛИ соединен с первым входом восьмого элемента И, выходы восьмого и девятого элементов И через пятый и шестой элементы НЕ подключены к нулевому и единичному входам первого RS-триггера, выход восьмого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к единичному выходу первого RS-триггера, выход третьего элемента ИЛИ соединен с первым входом двенадцатого элемента И, второй вход которого подключен к выходу шестого элемента НЕ, выход двенадцатого элемента И соединен с вторыми входами восьмого и пятого элементов И и входом четвертого элемента НЕ, выход четвертого элемента НЕ подключен к первому входу девятого элемента И, выходы первого и второго элементов ИЛИ соединены с входами шестого элемента И, выход которого является потенциалом заема единицы из старших разрядов и подключен к второму входу первого элемента ИЛИ, третьего элемента НЕ, с вторым входом шестого элемента ИЛИ и десятого элемента И i+1-го разряда, устройство также содержит третий и четвертый RS-триггеры хранения потенциалов заема из самого старшего разряда и знака кода первого регистра А соответственно, при этом входы пятнадцатого элемента И соединены с четвертым входом управления и выходом потенциала заема из самого старшего разряда, выход пятнадцатого элемента И через двадцатый элементы ИЛИ, семнадцатый И, двадцать шестой элемент НЕ соединен с нулевым входом четвертого RS-триггера; через элементы восемнадцатый И, двадцать седьмой НЕ - выход пятнадцатого элемента И связан с единичным входом четвертого RS-триггера, выход семнадцатого И соединен с двадцать первым ИЛИ, второй его вход подключен к единичному выходу четвертого RS-триггера, выход которого соединен с первым входом девятнадцатого элемента И, второй его вход подключен к выходу двадцать седьмого НЕ, выход девятнадцатого элемента И соединен с входами двадцать восьмого элемента НЕ и семнадцатого элемента И, выход упомянутого элемента НЕ соединен с входом восемнадцатого элемента И, перечисленные элементы и связи обеспечивают работу четвертого триггера в режиме счета импульсов, кроме того, выход пятнадцатого элемента И связан с единичным входом третьего RS-триггера; входы двадцатого элемента И соединены с выходами четвертых элементов НЕ всех разрядов устройства, сигнал с выхода этого элемента является признаком наличия нулевых значений первых триггеров всех разрядов и соединен с первым входом шестнадцатого элемента И, второй вход которого соединен с четвертым входом управления формированием результата вычитания в триггерах регистр А, выход шестнадцатого элемента И через элементы двадцатый ИЛИ, семнадцатый И, двадцать шестой НЕ, соединен с нулевым входом четвертого RS-триггера, при этом входы третьего и четвертого временных тактов через двадцать второй элемент ИЛИ соединены с входом четырнадцатого элемента И, второй его вход соединен с единичным выходом третьего RS-триггера, выход четырнадцатого элемента И является потенциалом циклического заема и соединен с входами первого элемента ИЛИ и третьего элемента НЕ самого младшего разряда.

| Устройство для сложения и вычитания | 1988 |

|

SU1571575A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство по модулю | 1988 |

|

SU1571583A1 |

| МИКРОМЕТР | 1932 |

|

SU31621A1 |

Авторы

Даты

2011-01-27—Публикация

2010-02-08—Подача