Изобретение относится к вычислительной технике и может быть использовано в процессорных устройствах ЭВМ. Известны способы и устройства умножения двоично-десятичных кодов, заключающиеся в сложении кодов тетрад множимого с кодами тетрад регистра частичных произведений столько раз, сколько единиц содержится в младшей тетраде регистра множителя, с последующим сдвигом кодов регистров частичных произведений и множителя на один десятичный разряд вправо. Указанные процедуры повторяются столько раз, сколько десятичных разрядов содержит регистр множителя. Основные способы и устройства рассмотрены в книге М.А.Карцев «Арифметика цифровых машин», М.: Наука, 1969, стр.346-354. Основным недостатком известных способов выполнения умножения с формированием частичных произведений на основе суммирующих устройств является необходимость выполнения корректировки результатов сложения, если результат сложения i-той тетрады будет равен или больше десяти единиц. Указанная процедура снижает быстродействие выполнения операций умножения в два-три раза. Известны также устройства суммирования, в которых коррекция кода исключается за счет применения матриц сложения, что ведет к увеличению оборудования и является недостатком таких устройств. Пример такого устройства, который является прототипом предлагаемого изобретения, приведен на стр.168, рис.2-16 названного выше источника. Кроме того, для выполнения операции умножения с использованием противопоставляемого устройства требуется включение в состав оборудования каждого десятичного разряда двадцати RS-триггеров, что также является недостатком прототипа.

Целью изобретения является повышение быстродействия выполнения операции умножения без существенного увеличения оборудования.

Для достижения поставленной цели предложен способ умножения двоично-десятичных кодов, отличающийся тем, что множитель, множимое и частичные произведения принимают и хранят соответственно в регистрах A, B и C или тетрадах A, B и C в кодах 8, 4, 2, 1, после приема преобразуют коды второго и третьего двоичных разрядов тетрад B, C и младшей тетрады регистра A в четные десятичные числа 6, 4, 2; выполняют умножение четных десятичных чисел 8, 6, 4, 2 тетрад B на аналогичные числа младшей тетрады A с помощью матрицы умножения, на вертикальные и горизонтальные входы которой подают соответственно значения упомянутых чисел тетрад B и A, получают в каждом десятичном разряде произведения четных десятичных чисел младшей тетрады A на все тетрады B, равные одному из десятичных чисел, 4, 8, 12, 16, 24, 32, 36, 48 и 64, по первому временному такту суммируют четные десятичные числа разряда единиц произведения матрицы умножения всех тетрад B с соответствующими тетрадами C, при этом суммирование выполняют с помощью матрицы сложения, на горизонтальные входы которой подают четные десятичные числа 8, 6, 4, 2, 0 тетрады C, а на ее вертикальные входы поступают четные десятичные числа 8, 6, 4, 2, 0 разряда единиц матрицы умножения, с выходов матрицы сложения получают предварительную сумму, равную одному из десятичных чисел 0, 2, 4, 6, 8, 10, 12, 14 и 16, при этом суммирование кодов первых двоичных разрядов тетрад B, C производят с помощью одноразрядного трехвходового сумматора в каждом десятичном разряде, по результатам предварительной суммы и сигнала переноса из одноразрядного трехвходового сумматора первого разряда формируют значения переноса в старший десятичный разряд и окончательные значения суммы каждого десятичного разряда, при этом при наличии сигнала переноса из одноразрядного трехвходового сумматора прибавляют к значениям предварительной суммы две единицы, окончательное значение суммы i-того десятичного разряда преобразуют в код 8, 4, 2, 1 и заносят его в тетрады C; по второму временному такту суммируют десятичные числа 6, 4, 2, 1 разряда десятков матрицы умножения i-того десятичного разряда с числом i+1-той тетрады C; по третьему временному такту, если код первого разряда младшей тетрады A равен нулю, а первый разряд i-той тетрады B равен единице, суммируют четные числа младшей тетрады A с кодами i-тых тетрад C, по этому же третьему такту суммируют числа тетрад B и C, если код первого разряда тетрады A равен единице; по четвертому временному такту при равенстве единице кодов первых разрядов младшей тетрады A и i-той тетрады B выполняют сложение четного десятичного числа тетрады A с десятичным числом тетрады C; после выполнения умножения чисел тетрад B на младшую тетраду A производят сдвиг кодов регистров A и C на один десятичный разряд вправо, операцию умножения заканчивают после умножения всех кодов тетрад регистра A на коды тетрад регистра B, а также предложено устройство умножения двоично-десятичных кодов, выполненное на логических элементах И, ИЛИ, НЕ, содержащее в каждом десятичном разряде первый, второй и третий четырехразрядные триггерные регистры A, B и C для хранения кодов множителя A, множимого B и частичных произведений C, соответственно тетрады A, B, C, входы управления выполнением отдельных элементарных операций, одноразрядный трехвходовый сумматор, при этом все тетрады A и C выполняют элементарные операции приема, хранения и сдвига кода на один десятичный разряд вправо, все тетрады B выполняют элементарные операции приема и хранения кода множимого; отличающееся тем, что каждый двоичный разряд тетрад A, B, C содержит RS-триггер, кроме того, каждый двоичный разряд тетрад C и A содержит первый и второй элементы И, подключенные через первый и второй элементы НЕ к нулевому и единичному входам RS-триггера, выход первого элемента И соединен с входом первого элемента ИЛИ, второй вход которого подключен к единичному выходу RS-триггера, а выход упомянутого элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго элемента НЕ, выход третьего элемента И соединен с первым входом первого элемента И и входом третьего элемента НЕ, выход этого элемента НЕ соединен с первым входом второго элемента И, вторые входы первого и второго элементов И подключены к выходам второго и третьего элементов ИЛИ, первые входы четвертого и седьмого элементов И подключены к входу управления сдвигом кода вправо в тетрадах A и C, вторые входы упомянутых элементов И соединены с выходами третьих элементов НЕ, И соответственно первого разряда старшей тетрады, первые входы пятого и шестого элементов И соединены с выходом и входом четвертого элемента НЕ, вторые входы упомянутых элементов И подключены к входу управления занесением кода суммы в тетрады C, вход четвертого элемента НЕ первого двоичного разряда тетрады C соединен с первым выходом одноразрядного трехвходового сумматора упомянутого разряда; входы четвертых элементов НЕ второго-четвертого двоичных разрядов являются входами суммы соответствующих разрядов, каждая тетрада B, C и младшая тетрада A содержат восьмой, девятый и десятый элементы И для преобразования двоично-десятичных кодов второго и третьего двоичных разрядов в четные десятичные числа 6, 4, 2, при этом выходы третьих элементов И второго и третьего разрядов соединены с входами восьмого элемента И, входы пятого элемента И связаны с выходами третьего элемента И третьего разряда и третьего элемента НЕ второго разряда, входы десятого элемента И соединены с выходами третьего элемента И второго разряда и третьего элемента НЕ третьего разряда; каждый десятичный разряд устройства содержит: матрицу умножения четных десятичных чисел 8, 6, 4, 2 младшей тетрады A и тетрады B, выполненную на шестнадцати логических элементах И-ИЛИ, расположенных в точках пересечения горизонтальных входов A2-A5 тетрады A и вертикальных входов B2-B5 тетрады B, выходы элементов И-ИЛИ, расположенных в точке пересечения упомянутых линий, соответствуют значениям произведения одного из четных десятичных чисел 4, 8, 12, 16, 24, 32, 36, 48 и 64, выходы элементов ИЛИ, расположенных в точках пересечения линий горизонтальных и вертикальных входов, соединены с точками, соответствующими равным числам произведения, выходы объединенных элементов ИЛИ соединены с входами первого, второго, третьего и четвертого элементов ИЛИ, выходы которых соответствуют четным десятичным числам 8, 6, 4, 2 разряда единиц произведения i-того десятичного разряда, соответствующие выходы объединенных элементов ИЛИ связаны с входами пятого и шестого элементов ИЛИ, выходы которых соответствуют десятичным числам 1, 2 разряда десятков произведения i+1-того десятичного разряда, а выходы элементов ИЛИ, соответствующие произведению 48 и 64, являются выходами чисел 4 и 6 в i+1-тый десятичный разряд; матрицу сложения четных десятичных чисел 8, 6, 4, 2 и нулевого значения триггеров второго-четвертого разрядов тетрады С с четными десятичными числами слагаемых тетрад A, B, разряда единиц произведения i-того десятичного разряда и разряда десятков произведения i+1-го десятичного разряда матрицы умножения и нулевого значения упомянутых слагаемых, выполненную на двадцати пяти логических элементах И-ИЛИ, расположенных в точках пересечения горизонтальных и вертикальных входов матрицы сложения, выходы элементов ИЛИ, расположенные на диагональных линиях матрицы сложения, соединены между собой, каждая диагональная линия является одним из девяти выходов матрицы сложения и соответствует предварительной сумме одного из четных десятичных чисел от 0 до 16; логические элементы ИЛИ, НЕ определения нулевых значений первого и второго слагаемых матрицы сложения; схему суммирования предварительной суммы с выходов матрицы сложения и сигнала переноса с выхода одноразрядного сумматора; схему формирования переноса в старший десятичный разряд при значении предварительной или окончательной суммы i-того десятичного разряда, равной или более 10; первый вход управления выдачей числа разрядов единиц произведения матриц умножения на входы матриц сложения всех десятичных разрядов, второй вход управления выдачей числа разрядов десятков произведения матрицы умножения i-тых разрядов на входы матриц сложения i+1-тых десятичных разрядов, третий вход управления выдачей четных десятичных чисел 8, 6, 4, 2 младшей тетрады A на входы матрицы сложения i-того разряда, если коды первых разрядов тетрад A и B равны нулю и единице соответственно, четвертый вход управления выдачей числа тетрады B на входы матрицы сложения и одноразрядного трехвходового сумматора, если код младшей тетрады A равен единице, пятый вход управления занесением кода суммы, представленной в коде 8, 4, 2, 1, в тетрады C, шестой вход управления сдвигом кодов вправо регистров A и C, при этом первый-пятый выходы тетрады B соединены с первыми входами первого-пятого элементов И, вторые входы которых подключены к четвертому входу управления, а выходы упомянутых элементов И соединены с первыми входами двенадцатого-пятнадцатого элементов ИЛИ соответственно, выходы которых связаны с седьмым-десятым входами матрицы сложения и с входами первого элемента ИЛИ, выход которого через первый элемент НЕ связан с шестым входом матрицы сложения, второй-пятый выходы тетрады B подключены к пятому-восьмому вертикальным входам матрицы умножения, второй-пятый выходы младшей тетрады A подключены к первому-четвертому горизонтальным входам матриц умножения всех десятичных разрядов, второй-пятый выходы тетрады C каждого десятичного разряда соединен с вторым-пятым входами матрицы сложения соответственно и с входами второго элемента ИЛИ, выход которого через второй элемент НЕ соединен с первым входом матрицы сложения, первый-четвертый выходы матрицы умножения соединены с первыми входами пятнадцатого, восемнадцатого, двадцать первого и двадцать третьего элементов И, вторые входы которых подключены к первому входу управления, а выходы упомянутых элементов И подключены к вторым входам двенадцатого-пятнадцатого элементов ИЛИ, пятый-восьмой выходы матрицы умножения i-того десятичного разряда подключены к первым входам двенадцатого, тринадцатого, шестнадцатого и девятнадцатого элементов И i+1-го десятичного разряда, вторые входы которых связаны с вторым входом управления, а выходы упомянутых элементов И подключены к третьим входам одиннадцатого-четырнадцатого элементов ИЛИ, первые входы четырнадцатого, семнадцатого, двадцатого и двадцать второго элементов И соединены с вторым - пятым выходами тетрады A соответственно, вторые входы этих элементов подключены к третьему входу управления, выход упомянутых элементов И соединен с четвертыми входами двенадцатого-пятнадцатого элементов ИЛИ, выход одиннадцатого элемента ИЛИ соединен с первым входом одноразрядного трехвходового сумматора, второй и третий входы которого связаны с первым выходом тетрады C и с входом переноса из младшего десятичного разряда соответственно, первый выход матрицы сложения через третий элемент ИЛИ соединен с первым входом двадцать пятого элемента И, второй-четвертый выходы матрицы сложения подключены к входам четвертого-шестого элементов ИЛИ, пятый выход соединен с первыми входами тридцатого и тридцать второго элементов И, шестой-девятый выходы матрицы сложения соединены с входами третьего-шестого элементов ИЛИ соответственно и с входами шестнадцатого элемента ИЛИ, выход которого является сигналом переноса в старший десятичный разряд, выход четвертого элемента ИЛИ соединен с первыми входами двадцать четвертого и двадцать седьмого элементов И, выход пятого элемента ИЛИ соединен с первыми входами двадцать шестого и двадцать девятого элементов И, выход шестого элемента ИЛИ соединен с первыми входами двадцать восьмого и тридцать первого элемента И, вторые входы двадцать пятого, двадцать седьмого, двадцать девятого, тридцать первого и тридцать второго элементов И связаны с вторым выходом одноразрядного трехвходового сумматора, третий выход которого соединен с вторыми входами двадцать четвертого, двадцать шестого, двадцать восьмого и тридцатого элементов И, выходы двадцать четвертого и двадцать пятого элементов И подключены к входам седьмого элемента ИЛИ, выходы двадцать шестого и двадцать седьмого элементов И соединены с восьмым элементом ИЛИ, выходы двадцать восьмого и двадцать девятого элементов И через девятый элемент ИЛИ подключены к седьмому и восьмому элементам ИЛИ, выходы тридцатого и тридцать первого элементов И соединены с входами десятого элемента ИЛИ, выходы седьмого, восьмого и десятого элементов ИЛИ соединены соответственно с вторым-четвертым входами тетрады C, пятый, шестой входы упомянутой тетрады соединены с пятым и шестым входами управления, выход тридцать второго элемента И соединен с входом шестнадцатого элемента ИЛИ.

Повышение быстродействия в предложенных способе и устройстве достигается за счет того, что в состав каждого десятичного разряда устройства введены дешифраторы двоично-десятичных кодов, хранящихся во вторых и третьих двоичных разрядах тетрад множимого, частичных произведений и младшей тетрады множителя, в четные десятичные числа 6, 4, 2; матрица умножения (МУ) четных десятичных чисел тетрад A и В, матрица сложения (МС) четных десятичных чисел тетрады C с четными десятичными числами, поступающими с выходов двенадцатого-пятнадцатого элементов ИЛИ, и нулевыми значениями этих слагаемых, каждый десятичный разряд содержит: первую группу логических элементов И, подключенных к первому-пятому выходам тетрады В, вторую группу элементов И-ИЛИ и три четырехразрядных триггерных регистра A, B и C (TA1, TB3, TC2), выполненных на основе RS-триггеров, одноразрядный трехвходовый сумматор, элементы ИЛИ-НЕ определения нулевых значений первого и второго слагаемых матрицы сложения, схему корректировки предварительной суммы и схему преобразования десятичного числа 6 в двоично-десятичный код 0110.

Рассмотрим основные отличительные особенности предлагаемого способа умножения двоично-десятичных кодов. Основные отличия заключаются в преобразовании кодов TB3, TC2 и младшей TA1, представленных в кодах 8, 4, 2, 1, в четные десятичные числа 8, 6, 4, 2, применение МУ четных чисел 8, 6, 4, 2 TB3 на 8, 6, 4, 2 TA1, применение матрицы сложения четных чисел 8, 6, 4, 2 и нулевых значений триггеров второго-четвертого разрядов первого и второго слагаемых, применение преобразования десятичного числа окончательной суммы в код 8, 4, 2, 1. При этом первый двоичный разряд работает по правилам двоичной арифметики и выполнен по известным схемным построениям. Отличительные особенности позволяют выполнить умножение всех тетрад множимого на младшую тетраду множителя практически одновременно с временем приема кода в тетрады регистров TA1 и TB3. Это позволяет повысить быстродействие выполнения операции умножения приблизительно в два-три раза. Отличительной особенностью способа также является поочередное суммирование чисел разряда единиц и разряда десятков произведения МУ с частичными произведениями, хранящимися в тетрадах С2. Это позволяет выполнять умножение практически на одном и том же оборудовании, что и при выполнении операции умножения путем многократного сложения. Таким образом предлагаемые способ и устройство позволяют выполнять операции умножения двоично-десятичных кодов при повышении быстродействия в 2-3 раза. Особенностью предлагаемого устройства умножения также является построение всех регистров на основе простейших RS-триггеров, при этом в регистрах множителя и частичных произведений с помощью дополнительных элементов И, ИЛИ, НЕ обеспечивается задержка сигнала с выхода RS-триггеров при их переключении на время длительности импульса занесения кода суммы в регистры или сдвига кода. Это позволяет построить каждый десятичный разряд устройства на основе двенадцати RS-триггеров. Для построения известных устройств потребуется двадцать RS-триггеров, что в полтора раза больше. В такой же пропорции снизится потребление электропитания триггерными регистрами по сравнению с известными устройствами.

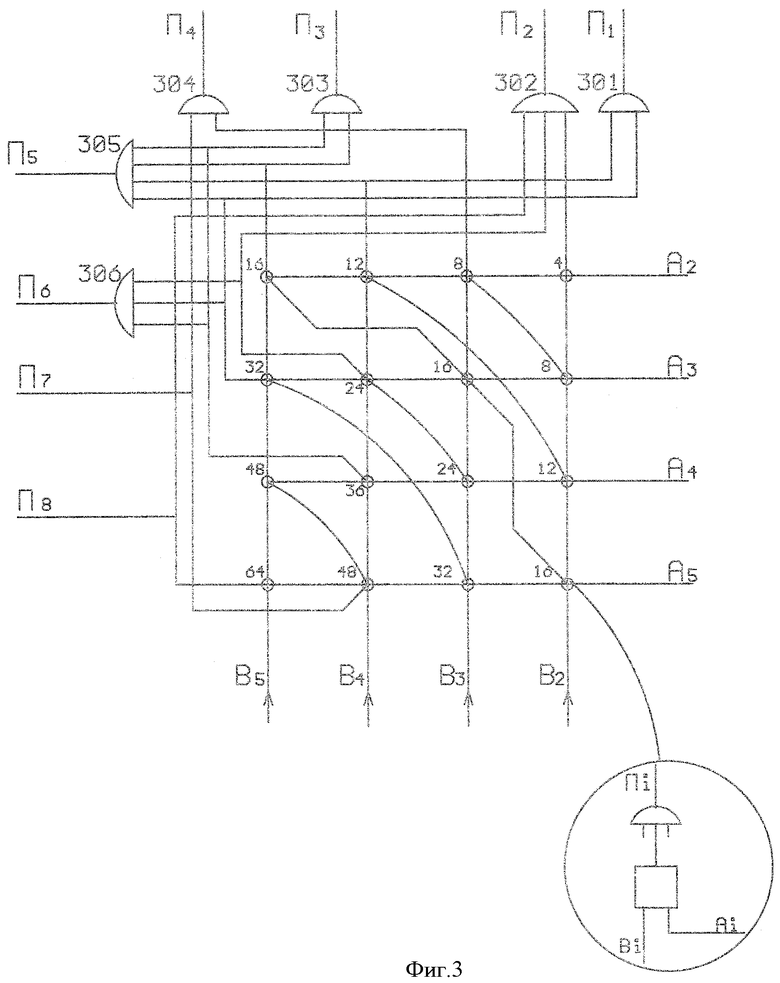

Для пояснения работы предлагаемого устройства умножения на Фиг.1 приведена функциональная схема одного десятичного разряда устройства. На фигуре приняты следующие обозначения: четырехразрядные триггерные регистры - тетрады TA1, TC2, TB3, 1, 2, 3, матрица умножения 4, матрица сложения 5, одноразрядный трехвходовый сумматор (ОТС) 6, элементы И 7-32, элементы ИЛИ 33-47, 68, элементы НЕ 48, 49, вход и выход переноса 50, 51, единичный выход триггера первого разряда (TA1) 52, информационные связи пятого-восьмого выходов МУ4 i-того разряда с входами И 15, 18, 22 и 23 i+1-го разряда 53-56, первый вход управления (ВУ) выдачей чисел разряда единиц МУ4 57, второй ВУ выдачей чисел разряда десятков МУ4 58, третий ВУ выдачей четных чисел ТА1 на входы МС5 59, четвертый ВУ выдачей чисел TB3 на входы МС5 и ОТС6 60, пятый ВУ сдвигом кода вправо 65, ВУ занесением кода суммы в ТС2 66, единичный выход триггера первого разряда ТВ3 67.

На фиг.2 приведена функциональная схема ТС2, каждый двоичный разряд которой выполнен на основе RS-триггера с элементами И, ИЛИ, НЕ, обеспечивающими задержку сигнала с выходов RS-триггеров. На фигуре приняты следующие обозначения: элементы И 201-207, 219-221, элементы ИЛИ 208-210, элементы НЕ 211-214, RS-триггер 215, единичный выход триггера с задержкой сигнала 216, нулевой выход триггера с задержкой сигнала 217, вход суммы i-того двоичного разряда 218, ВУ сдвигом кода вправо 5, ВУ занесением кода суммы в ТС2 6.

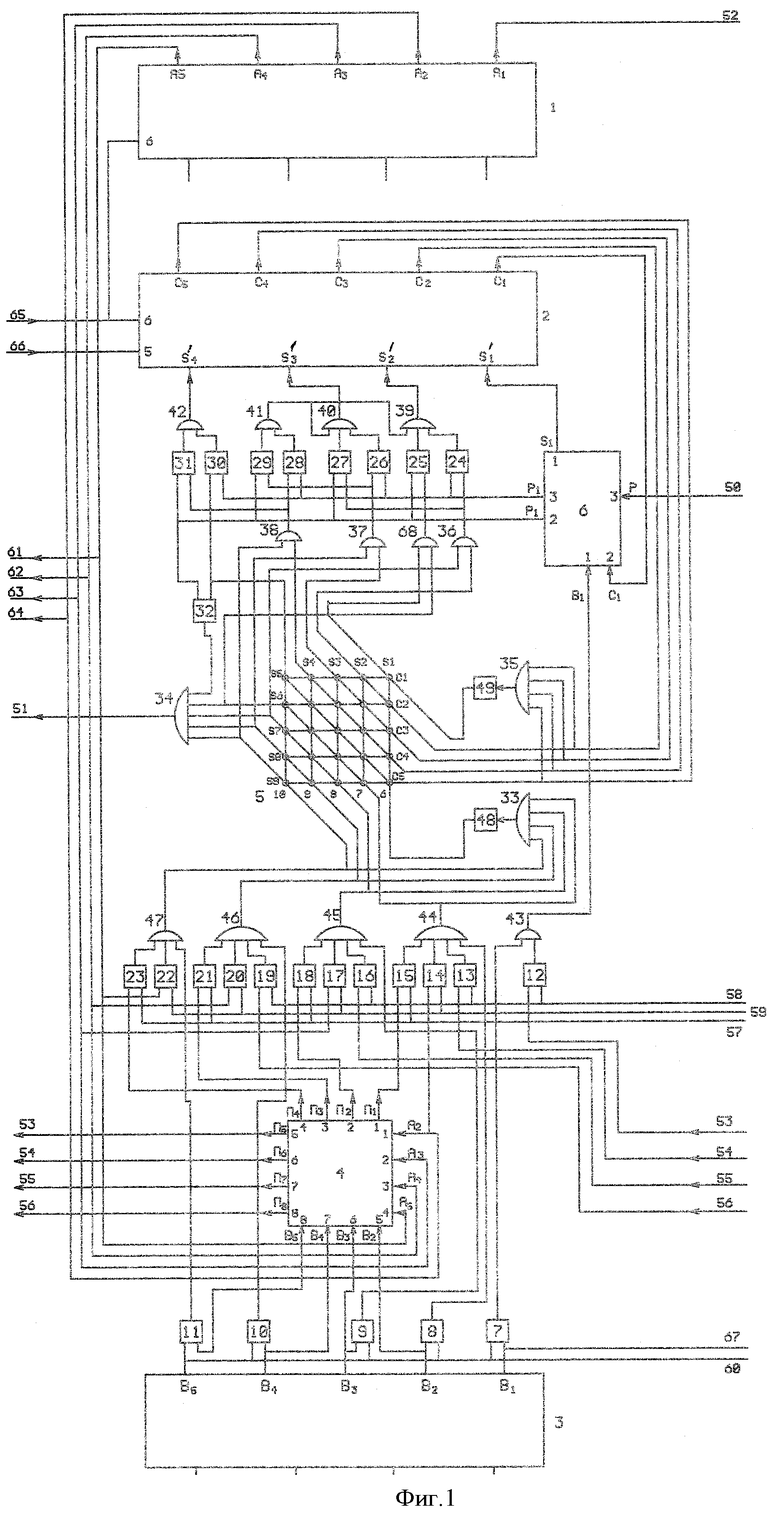

На фиг.3 приведена функциональная схема матрицы умножения четных десятичных чисел 8, 6, 4, 2 ТА1 на четные десятичные числа 8, 6, 4, 2 ТВ3. На фигуре приняты следующие обозначения: элементы ИЛИ 301-306, горизонтальные входы четных чисел ТА1 A2, А3, A4, A5, вертикальные входы четных чисел ТВ3 В2, В3, В4, B5, выходы разряда единиц произведения П1-П4, выходы разряда десятков произведения П5-П8. В каждом узле пересечения горизонтальных и вертикальных линий входов четных чисел ТА1 и ТВ3 установлены шестнадцать элементов И-ИЛИ.

Предложенное устройство осуществляется следующим образом. В исходном состоянии в ТВ3 и ТА1 хранятся двоично-десятичные коды множимого и множителя, в ТС2 может храниться код результата предыдущей операции, или эти триггеры установлены в нуль. На одном из вторых-пятых выходов TA1, ТС2, ТВ3 присутствуют высокие потенциалы, соответствующие четным десятичным числам, занесенным в упомянутые тетрады. На первых выходах упомянутых тетрад будет потенциал, соответствующий значению первого двоичного разряда. На ВУ 57-60, 65, 66 отсутствуют высокие потенциалы. На выходах П1-П8 всех МУ4 могут присутствовать высокие потенциалы, соответствующие произведению четных чисел ТА1 на ТВ3. Выходы А2-A5 и В2-В5 ТА1 и ТВ3 соединены с первым-четвертым и с пятым-восьмым входами МС 4 соответственно. Первый-пятый выходы ТВ3 соединены с первыми входами И 7-11, вторые входы которых подключены к ВУ 60. Выходы И 7-11 подключены к первым входам ИЛИ 43-47 соответственно. Первый-четвертый выходы МС 4 соединены с первыми входами И 15, 18, 21, 23, их вторые входы подключены к ВУ 57. Пятый-восьмой выходы МУ4 i-того десятичного разряда подключены к первым входам И 12, 13, 16, 19 i+1 разряда, вторые входы этих элементов связаны с ВУ 58. Выходы - A2-А5 ТА1 соединены с первыми входами И 14, 17, 20, 22, вторые входы которых соединены с ВУ 59. Выходы И 12-23 через ИЛИ 43-47 соединены с 7-10 входами МС5 и с входами ИЛИ 33. Выход ИЛИ 33 через НЕ 48 подключен к шестому входу МС5. Выход ИЛИ 43 соединен с первым входом ОТС 6, второй и третий входы которого подключены к C1 выходу ТС2 и входу переноса 50. Выходы ТС2 С2-С5 соединены с вторым-пятым входами МС5 соответственно и с входами ИЛИ 35, выход которого через НЕ 49 связан с первым входом упомянутой матрицы. Первый выход МС5 через ИЛИ 68 подключен к первому входу И 25, второй-четвертый выходы соединены с ИЛИ 36-38 соответственно, пятый выход связан с входами И 30, 32, шестой выход подключен к ИЛИ 68 и ИЛИ 34, седьмой-девятый выходы МС5 соединены с ИЛИ 36-38 и 34 соответственно. Выходы ИЛИ 36-37 соединены с И 24, 27, И 26, 29, И 28, 31. Вторые входы И 24, 26, 28, 30 соединены с третьим выходом ОТС 6. Выход И 32 подключен к ИЛИ 34, выход которого является входом переноса в старший разряд. Вторые входы И 25, 27, 29, 31 и 32 подключены к второму выходу ОТС 6. Выходы И 24, 25 соединены с входами ИЛИ 39, выходы И 26, 27 соединены с входами ИЛИ 40, выходы И 31, 30 подключены к входам ИЛИ 42. Выходы И 28, 29 связаны с входом ИЛИ 41, вход которого подключен к ИЛИ 39, 40. Выходы ИЛИ 39, 40 и 42 соединены с S'2-S'4 входами ТС2. ВУ 66 подключен к пятому входу ТС2. ВУ 65 подключен к шестым входам ТС2 и ТА1. Выходы 52 и 67 подключены к входу устройства управлением выполнения умножения (на схеме не приводится). Выходы А2-A5 TA1 через информационные связи 64-61 соединены с А2-А4 входами МУ4 и с И 14, 17, 20, 22 всех десятичных разрядов устройства умножения соответственно. На фиг.2 приведена функциональная схема ТС2, в каждом двоичном разряде которой выходы И 201, 202 через ИЛИ 208, И 205, НЕ 211 соединены с R-входом RS-триггера (Tr) 215. Выходы И 203-204 через ИЛИ 209, И 206, НЕ 212 соединены с S-входом TR 215. Первые входы И 201, 204 подключены к входу 5, вторые входы этих элементов И соединены с выходами НЕ 213 и И 207 первого разряда старшей ТС2 соответственно. Первые входы И 202, 203 подключены к выходу 6. Вторые входы упомянутых И соединены с выходом и входом НЕ 214, вход которого является S'1 выходом ОТС6. Выход И 205 через ИЛИ 210 соединен с первым входом И 207, второй его вход связан с выходом НЕ 212. Единичный выход Tr 215 соединен с ИЛИ 210. Выход И 207 является С1 выходом ТС2 и соединен с вторым входом И 205 и входом НЕ 213, выход которого соединен с вторым входом И 206.

Входы И 219 соединены с выходами И 207 второго и третьего двоичных разрядов, выход И 219 является выходом С4 ТС2. Входы И 220 соединены с выходами И 207 третьего разряда и НЕ 213 второго разряда ТС2. Выход И 220 является выходом C3 ТС2. Входы И 221 соединены с выходом И 207 второго разряда и НЕ 213 третьего разряда. Выход И 221 является С2 выходом ТС2. Информационные связи 216 и 217 каждого двоичного разряда i-той тетрады соединены с входами И 204, 201 этого же разряда i-1-той ТС2. (Тетрады ТА1, кроме самой младшей, не содержат И 219-221. Тетрады ТС3 содержат только Tr 215 и элементы И 219-221.)

На фиг.3 приведена функциональная схема МУ4. В точках пересечения горизонтальных входов А2-A5 и вертикальных входов B2-B5 установлены шестнадцать элементов И, выход которых подключен к входам шестнадцати элементов ИЛИ. Выходы упомянутых элементов ИЛИ соответствуют значению произведения Ai Bi (i=2, 4, 6, 8). Каждая точка пересечения (узел) МУ4 помечены цифрами, соответствующими однозначным или двухзначным числам произведения. Выходы элементов ИЛИ в точках пересечения одинаковых значений произведения соединены между собой. Упомянутые выходы элементов ИЛИ, соответствующие цифрам произведения разряда единиц 8, 6, 4, 2, соединены с входами ИЛИ 304-301 соответственно. Выходы элементов ИЛИ, соответствующие цифрам произведения разрядов десятков 2, 1, соединены с входами ИЛИ 305, 306. Выходы элементов ИЛИ 304-301 являются выходами МУ4 П4-П1 соответственно. Выходы элементов ИЛИ 306, 305 являются выходами МУ4 П5 и П6. Выходы МУ4 П7 и П8 соответствуют значениям цифр произведения десятков, т.е 4 и 6.

Рассмотрим работу устройства при выполнении операции сложения и умножения.

1. Операция сложения. Выполняется за один временной такт, содержащий три временных подтакта (t1, t2, t3).

По t1 второе слагаемое принимается в ТВ3 в коде 8, 4, 2, 1, при этом код первого слагаемого хранится в ТС2 в коде 8, 4, 2, 1. Одновременно с приемом кода выполняется преобразование кода 8, 4, 2, 1 в четное десятичное число 8, 6, 4, 2, 0. Значение первых двоичных разрядов ТВ3 и ТС2 сохраняется.

По t2 формируются сигналы переносов и значения предварительной суммы в каждом десятичном разряде. Для этого на ВУ 60 подается высокий потенциал, разрешающий поступление сигнала, соответствующего значению одного из чисел второго слагаемого, с выходов ТВ3 через И 8-11, ИЛИ 44-47, ИЛИ 33, НЕ 48 на входы МС 5 и через И7, ИЛИ 43 - на первый вход ОТС 6. Число первого слагаемого с выходов С2-С5 ТС2 поступает на входы С2-С5 МС5 и с выхода C1 ТС2 - на второй вход ОТС 6. Результат суммирования четных десятичных чисел с выходов МС 5, равный одному из значений суммы 16, 14, 12, 10, 8, 4, 2, 0, поступает через ИЛИ 36-38, 68 на входы элементов И 24-32. Одновременно коды первых разрядов ТС2 и ТВ3 суммируются с помощью ОТС 6. Если в результате суммирования первых разрядов ТВ3, ТС2 не выработан сигнал переноса с второго выхода ОТС 6, то результат предварительной суммы с выходов S 1 - 9 МС 5 через И 24, 26, 28, 30 и далее через ИЛИ 39, 40, 41 и 42 поступит на S'2-S'4 входы ТС2 в коде 8, 4, 2, 1. В том случае если с второго выхода ОТС 6 на входы И 25, 27, 29, 31 и 32 поступит высокий потенциал, т.е имеет место сигнал переноса из первого двоичного разряда, значение предварительной суммы с первого-девятого выходов МС 5 увеличивается на две единицы. При этом сигнал с выходов матрицы сложения через элементы ИЛИ 36-38, 68 и элементы И 27, 29, 31, ИЛИ 39, 40, 42 поступит на второй-четвертый входы ТС2. При этом сигнал с первого выхода ОТС 6 поступит на вход S'1 ТС2, если результат суммирования кодов первых разрядов C1 и В1 будет равен единице.

По третьему временному подтакту результат суммирования заносится в триггеры ТС2. Для этого на ВУ 66 подается исполнительный импульс. Заметим, что изменение значений потенциалов на C1-C5 выходах тетрады ТС2 произойдет после снятия сигнала с ВУ 66. На этом выполнение операции сложения завершается. Результат сложения будет храниться в ТС2, а второе слагаемое - в ТВ3.

2. Операция умножения. Максимальное время выполнения операции умножения ТА1 на все ТВ3 равняется суммарному времени выполнения четырех операций сложения десятичных чисел ТС2 с числами ТВ3, ТА1, с числами разрядов единиц, с числами разрядов десятков МУ4 и выполнения операции сдвига кодов TA1, ТС2 на один десятичный разряд вправо. Каждая операция сложения выполняется за два подтакта, т.е. Тсл=t1+t2. Первый подтакт - время формирования максимального сигнала переноса, равное 4nt (здесь n - число десятичных разрядов, t - временная задержка сигнала переноса на одном элементе И (ИЛИ)), время формирования предварительной суммы, ее корректировка и преобразование в код 8, 4, 2, 1. Второй подтакт - время занесения суммы в ТС2. На подготовительном этапе выполнения операции умножения множитель принимается в ТА1, множимое в ТВ3. Как только в тетрады заносятся сомножители в кодах 8, 4, 2, 1, производится преобразование кодов второго-третьего двоичных разрядов младшей тетрады, А1 и всех TB3 в четные десятичные числа 6, 4, 2 и определение нулевого значения триггеров второго-четвертого разрядов ТС2. Значение кодов первых и четвертых разрядов ТА1, ТВ3, TC2 сохраняются. Одновременно с преобразованием четные десятичные числа умножаются с помощью МУ4. На П1-П4 выходах МС4 будет «представлено» значение разряда единиц произведения, т.е. одно из десятичных чисел 8, 6, 4, 2, а на П5-П8 выходах будет значение разряда десятков произведения, т.е десятичные числа 6, 4, 3, 2 и 1, при этом число 3 представляется как 2 и 1 одновременно.

По времени Тсл1 выполняется первая операция сложения десятичных чисел 8, 6, 4, 2, 0, полученных с П1-П4 выходов МУ 4, и С2-С5 значений выходов ТС2. При этом суммирование значений первых двоичных разрядов ТС2, ТС3 и сигнала переноса из младшего десятичного разряда выполняется с помощью ОТС 6. Для выполнения первой операции сложения на ВУ 57 подается высокий потенциал, который поступает на вторые входы И 15, 17, 20, 22. Если на одном из выходов П1-П4 МУ 4 имеется высокий потенциал, соответствующий одному из десятичных чисел 8, 6, 4, 2, то на седьмой-десятый входы МС5 через элементы И 15, 18, 21, 23, ИЛИ 44-47 также поступит высокий потенциал. При отсутствии сигнала с выходов ИЛИ 44-47 на шестой вход МС 5 поступает высокий потенциал с НЕ 48, что означает выполнение сложения «нуля» разряда единиц произведения МУ4 с четным десятичным числом, хранящимся в ТС2. Подробно операция сложения рассмотрена в п.1.

анты

ведение МУ четных чисел

дение (регистр C) четных чисел

A, B, C - регистры множителя, множимого и частных произведений.

A1, B1, C1 - значение кодов первых двоичных разрядов тетрад ТА1, ТС2 и ТВ3. При A1=0, B1=0 числа тетрад четные, при A1=1, B1=1 - нечетные. A' - четные числа TA1.

По времени Тсл2 выполняется вторая операция сложения десятичных чисел 6, 4, 3, 2, 1, полученных с П5-П8 выходов МУ 4 i - того десятичного разряда с десятичным числом ТС2 i+1-го разряда. Для этого на ВУ 58 подается высокий потенциал, который поступает на вторые входы элементов И 12, 13, 16, 19. Если на одном из первых входов упомянутых элементов И имеется высокий потенциал, поступивший по информационным связям 53-56 с П5-П8 выходов МУ 4 i-1-го десятичного разряда, то с выходов элементов И 12, 13, 16, 19 через один из элементов ИЛИ 43-46 на седьмой-десятый входы МС 5 и первый S1 вход ОТС 6 могут поступить сигналы, соответствующие десятичным числам разряда десятков произведения i-1-го десятичного разряда. Четные десятичные числа, поступившие с выходов ИЛИ 44-47 и с С2-C5 выходов ТС2, будут просуммированы помощью МС5. Сложение сигналов с выхода ИЛИ 43 и с выхода С1 будет выполнено с помощью ОТС 6. При этом предварительная сумма, полученная с S1-S9 выходов МС5, будет увеличена на две единицы, если в первом двоичном разряде будет выработан сигнал переноса в старшие двоичные разряды. По результатам суммирования в каждом десятичном разряде при сумме, равной или большей десяти единиц, с помощью элементов ИЛИ 34, И 32 будет выработан сигнал переноса в старший десятичный разряд. По второму подтакту результат суммирования четных десятичных чисел, сформированный на входах элементов ИЛИ 39-42, будет преобразован в двоично-десятичный код и занесен в триггеры ТС2, одновременно значение суммы S'1 с выхода ОТС 6 будет занесено в первый разряд ТС2. Преобразование десятичного числа в двоично-десятичный код осуществляется подключением выхода ИЛИ 41 к входам ИЛИ 39 и 40. Для занесения суммы в ТС2 на ВУ 66 поступает импульс занесения кода суммы в ТС2.

По времени Тсл3, при условии  B1=1, выполняется третья операция сложения десятичного числа ТС2 с десятичным числом TA1. Для ее выполнения на ВУ 59, И 14, 17, 20, 23 поступает высокий потенциал, который с выходов ИЛИ 44-47 поступает на седьмой-десятый входы МС 5. С первого-девятого выходов МС 5 на входы элементов И 24, 26, 28, 30 поступит результат суммирования десятичных чисел TA1 и ТС2. При наличии сигнала переноса из ОТС 6 эта сумма увеличится на две единицы. Откорректированный результат суммирования десятичных чисел преобразуется в двоично-десятичный код и поступает на S2-S4 входы ТС2, а на S'1 вход поступит сигнал с первого входа ОТС 6. После поступления на ВУ66 исполнительного импульса окончательное значение суммы заносится в триггеры упомянутой тетрады.

B1=1, выполняется третья операция сложения десятичного числа ТС2 с десятичным числом TA1. Для ее выполнения на ВУ 59, И 14, 17, 20, 23 поступает высокий потенциал, который с выходов ИЛИ 44-47 поступает на седьмой-десятый входы МС 5. С первого-девятого выходов МС 5 на входы элементов И 24, 26, 28, 30 поступит результат суммирования десятичных чисел TA1 и ТС2. При наличии сигнала переноса из ОТС 6 эта сумма увеличится на две единицы. Откорректированный результат суммирования десятичных чисел преобразуется в двоично-десятичный код и поступает на S2-S4 входы ТС2, а на S'1 вход поступит сигнал с первого входа ОТС 6. После поступления на ВУ66 исполнительного импульса окончательное значение суммы заносится в триггеры упомянутой тетрады.

По времени Тсл3, при условии A1=1, выполняется операция сложения чисел ТС2 с числом ТВ3. Выполнение такой операции рассмотрено в п.1 описания работы устройства.

По времени Тсл4, при условии A1B1=1, выполняется четвертая операция сложения десятичных чисел ТС2 и TА1. Для ее выполнения по ВУ 59 подается высокий потенциал. Дальнейшее выполнение операции рассмотрено выше (абзац первый выполнения третьей операции сложения).

По времени Tcд5 двоично-десятичные коды, хранящиеся в ТА1 и ТС2, сдвигаются на один десятичный разряд вправо. Для выполнения этой ЭО на ВУ 65 подается исполнительный импульс сдвига кодов вправо. На этом операция умножения ТВ3 на младшую ТА1 завершается.

Операция умножения множимого на все тетрады множителя завершается, когда все тетрады множимого будут умножены на все тетрады множителя. Пример выполнения операции умножения приведен в таблице 1.

Основные технические характеристики одного десятичного разряда устройства приведены в таблице 2.

емый объект

Таки образом предлагаемые способ и устройство умножения двоично-десятичных кодов обеспечивают повышение быстродействия выполнения операции умножения при минимальных затратах оборудования по сравнению с известными устройствами аналогичного назначения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Устройство для умножения чисел | 1985 |

|

SU1259254A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ЕДИНИЦ | 2014 |

|

RU2540787C1 |

| Устройство для умножения | 1983 |

|

SU1180881A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия выполнения операции умножения. Способ заключается в последовательном выполнении операций приема сомножителей в тетрады ТА1 и ТВ3, преобразования кодов сомножителей из кода 8, 4, 2, 1 в десятичные числа 8, 6, 4, 2, I, умножения четных десятичных чисел тетрад ТА1 и ТВЗ одного десятичного разряда с помощью матрицы умножения, сложения частичных значений произведения ТС2 с числом разрядов единиц и разрядов десятков произведения, сложения чисел ТС2 с десятичными числами ТВ3, ТА2 с помощью матрицы сложения. Устройство, реализующее данный способ, содержит в каждом десятичном разряде элементы И, элементы ИЛИ, элементы НЕ, три четырехразрядных триггерных регистра А, В, С, одноразрядный трехвходовый сумматор, матрицу умножения, матрицу сложения, шесть входов управления. 2 н.п. ф-лы, 3 ил., 2 табл.

1. Способ умножения двоично-десятичных кодов, заключающийся в сложении кодов регистров множимого В и частичных произведений С столько раз, сколько единиц содержит младший десятичный разряд регистра множителя А, и сдвига кодов регистров А и С на четыре двоичных разряда в сторону младших разрядов с последовательным умножением всех тетрад регистра В на тетрады регистра А, отличающийся тем, что множитель, множимое и частичные произведения принимают и хранят соответственно в регистрах А, В и С или тетрадах А, В и С в кодах 8, 4, 2, 1, после приема преобразуют коды второго и третьего двоичных разрядов тетрад В, С и младшей тетрады регистра А в четные десятичные числа 6, 4, 2; выполняют умножение четных десятичных чисел 8, 6, 4, 2 тетрад В на аналогичные числа младшей тетрады А с помощью матрицы умножения, на вертикальные и горизонтальные входы которой подают соответственно значения упомянутых чисел тетрад В и А, получают в каждом десятичном разряде произведения четных десятичных чисел младшей тетрады А на все тетрады В, равные одному из десятичных чисел, 4, 8, 12, 16, 24, 32, 36, 48 и 64, по первому временному такту суммируют четные десятичные числа разряда единиц произведения матрицы умножения всех тетрад В с соответствующими тетрадами С, при этом суммирование выполняют с помощью матрицы сложения, на горизонтальные входы которой подают четные десятичные числа 8, 6, 4, 2, 0 тетрады С, а на ее вертикальные входы поступают четные десятичные числа 8, 6, 4, 2, 0 разряда единиц матрицы умножения, с выходов матрицы сложения получают предварительную сумму, равную одному из десятичных чисел 0, 2, 4, 6, 8, 10, 12, 14 и 16, при этом суммирование кодов первых двоичных разрядов тетрад В, С производят с помощью одноразрядного трехвходового сумматора в каждом десятичном разряде, по результатам предварительной суммы и сигнала переноса из одноразрядного трехвходового сумматора первого разряда формируют значения переноса в старший десятичный разряд и окончательные значения суммы каждого десятичного разряда, при этом при наличие сигнала переноса из одноразрядного трехвходового сумматора прибавляют к значениям предварительной суммы две единицы, окончательное значение суммы i-го десятичного разряда преобразуют в код 8, 4, 2, 1 и заносят его в тетрады С; по второму временному такту суммируют десятичные числа 6, 4, 2, 1 разряда десятков матрицы умножения I-го десятичного разряда с числом i+1-й тетрады С; по третьему временному такту, если код первого разряда младшей тетрады А равен нулю, а первый разряд i-й тетрады В равен единице, суммируют четные числа младшей тетрады А с кодами i-х тетрад С, по этому же третьему такту суммируют числа тетрад В и С, если код первого разряда тетрады А равен единице; по четвертому временному такту при равенстве единице кодов первых разрядов младшей тетрады А и i-той тетрады В выполняют сложение четного десятичного числа тетрады А с десятичным числом тетрады С; после выполнения умножения чисел тетрад В на младшую тетраду А производят сдвиг кодов регистров А и С на один десятичный разряд вправо, операцию умножения заканчивают после умножения всех кодов тетрад регистра А на коды тетрад регистра В.

2. Устройство умножения двоично-десятичных кодов, выполненное на логических элементах И, ИЛИ, НЕ, содержащее в каждом десятичном разряде первый, второй и третий четырехразрядные триггерные регистры А, В и С для хранения кодов множителя А, множимого В и частичных произведений С, соответственно тетрады А, В, С, входы управления выполнением отдельных элементарных операций, одноразрядный трехвходовый сумматор, при этом все тетрады А и С выполняют элементарные операции приема, хранения и сдвига кода на один десятичный разряд вправо, все тетрады В выполняют элементарные операции приема и хранения кода множимого, отличающееся тем, что каждый двоичный разряд тетрад А, В, С содержит RS-триггер, кроме того, каждый двоичный разряд тетрад С и А содержит первый и второй элементы И, подключенные через первый и второй элементы НЕ к нулевому и единичному входам RS-триггера, выход первого элемента И соединен с входом первого элемента ИЛИ, второй вход которого подключен к единичному выходу RS-триггера, а выход упомянутого элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго элемента НЕ, выход третьего элемента И соединен с первым входом первого элемента И и входом третьего элемента НЕ, выход этого элемента НЕ соединен с первым входом второго элемента И, вторые входы первого и второго элементов И подключены к выходам второго и третьего элементов ИЛИ, первые входы четвертого и седьмого элементов И подключены к входу управления сдвигом кода вправо в тетрадах А и С, вторые входы упомянутых элементов И соединены с выходами третьих элементов НЕ, И соответственно первого разряда старшей тетрады, первые входы пятого и шестого элементов И соединены с выходом и входом четвертого элемента НЕ, вторые входы упомянутых элементов И подключены к входу управления занесением кода суммы в тетрады С, вход четвертого элемента НЕ первого двоичного разряда тетрады С соединен с первым выходом одноразрядного трехвходового сумматора упомянутого разряда; входы четвертых элементов НЕ второго-четвертого двоичных разрядов являются входами суммы соответствующих разрядов, каждая тетрада В, С и младшая тетрада А содержат восьмой, девятый и десятый элементы И для преобразования двоично-десятичных кодов второго и третьего двоичных разрядов в четные десятичные числа 6, 4, 2, при этом выходы третьих элементов И второго и третьего разрядов соединены с входами восьмого элемента И, входы пятого элемента И связаны с выходами третьего элемента И третьего разряда и третьего элемента НЕ второго разряда, входы десятого элемента И соединены с выходами третьего элемента И второго разряда и третьего элемента НЕ третьего разряда; каждый десятичный разряд устройства содержит: матрицу умножения четных десятичных чисел 8, 6, 4, 2 младшей тетрады А и тетрады В, выполненную на шестнадцати логических элементах И-ИЛИ, расположенных в точках пересечения горизонтальных входов А2-А5 тетрады А и вертикальных входов В2-В5 тетрады В, выходы элементов И-ИЛИ, расположенных в точке пересечения упомянутых линий, соответствуют значениям произведения одного из четных десятичных чисел 4, 8, 12, 16, 24, 32, 36, 48, и 64, выходы элементов ИЛИ, расположенных в точках пересечения линий горизонтальных и вертикальных входов, соединены с точками, соответствующими равным числам произведения, выходы объединенных элементов ИЛИ соединены с входами первого, второго, третьего и четвертого элементов ИЛИ, выходы которых, соответствуют четным десятичным числам 8, 6, 4, 2 разряда единиц произведения i-го десятичного разряда, соответствующие выходы объединенных элементов ИЛИ связаны с входами пятого и шестого элементов ИЛИ, выходы которых соответствуют десятичным числам 1, 2 разряда десятков произведения i+1-го десятичного разряда, а выходы элементов ИЛИ, соответствующие произведению 48 и 64 являются выходами чисел 4 и 6 в i+1-й десятичный разряд; матрицу сложения четных десятичных чисел 8, 6, 4, 2 и нулевого значения триггеров второго-четвертого разрядов тетрады С с четными десятичными числами слагаемых тетрад А, В, разряда единиц произведения i-го десятичного разряда и разряда десятков произведения i+1-го десятичного разряда матрицы умножения и нулевого значения упомянутых слагаемых, выполненную на двадцати пяти логических элементах И-ИЛИ, расположенных в точках пересечения горизонтальных и вертикальных входов матрицы сложения, выходы элементов ИЛИ, расположенные на диагональных линиях матрицы сложения соединены между собой, каждая диагональная линия является одним из девяти выходов матрицы сложения и соответствует предварительной сумме одного из четных десятичных чисел от 0 до 16; логические элементы ИЛИ, НЕ определения нулевых значений первого и второго слагаемых матрицы сложения; схему суммирования предварительной суммы с выходов матрицы сложения и сигнала переноса с выхода одноразрядного сумматора; схему формирования переноса в старший десятичный разряд при значении предварительной или окончательной суммы i-го десятичного разряда, равной или более 10; первый вход управления выдачей числа разрядов единиц произведения матриц умножения на входы матриц сложения всех десятичных разрядов, второй вход управления выдачей числа разрядов десятков произведения матрицы умножения i-го разрядов на входы матриц сложения i+I-х десятичных разрядов, третий вход управления выдачей четных десятичных чисел 8, 6, 4, 2 младшей тетрады А на входы матрицы сложения i-го разряда, если коды первых разрядов тетрад А и В равны нулю и единице соответственно, четвертый вход управления выдачей числа тетрады В на входы матрицы сложения и одноразрядного трехвходового сумматора, если код младшей тетрады А равен единице, пятый вход управления занесением кода суммы, представленной в коде 8, 4, 2, 1, в тетрады С, шестой вход управления сдвигом кодов вправо регистров А и С, при этом первый-пятый выходы тетрады В соединены с первыми входами первого-пятого элементов И, вторые входы которых подключены к четвертому входу управления, а выходы упомянутых элементов И соединены с первыми входами двенадцатого-пятнадцатого элементов ИЛИ соответственно, выходы которых связаны с седьмым-десятым входами матрицы сложения и с входами первого элемента ИЛИ, выход которого через первый элемент НЕ связан с шестым входом матрицы сложения, второй-пятый выходы тетрады В подключены к пятому-восьмому вертикальным входам матрицы умножения, второй-пятый выходы младшей тетрады А подключены к первому-четвертому горизонтальным входам матриц умножения всех десятичных разрядов, второй-пятый выходы тетрады С каждого десятичного разряда соединены с вторым-пятым входами матрицы сложения соответственно и с входами второго элемента ИЛИ, выход которого через второй элемент НЕ соединен с первым входом матрицы сложения, первый-четвертый выходы матрицы умножения соединены с первыми входами пятнадцатого, восемнадцатого, двадцать первого и двадцать третьего элементов И, вторые входы которых подключены к первому входу управления, а выходы упомянутых элементов И подключены к вторым входам двенадцатого-пятнадцатого элементов ИЛИ, пятый-восьмой выходы матрицы умножения I-го десятичного разряда подключены к первым входам двенадцатого, тринадцатого, шестнадцатого и девятнадцатого элементов И i+1-го десятичного разряда, вторые входы которых связаны с вторым входом управления, а выходы упомянутых элементов И подключены к третьим входам одиннадцатого-четырнадцатого элементов ИЛИ, первые входы четырнадцатого, семнадцатого, двадцатого и двадцать второго элементов И соединены с вторым-пятым выходами тетрады А соответственно, вторые входы этих элементов подключены к третьему входу управления, выход упомянутых элементов И соединен с четвертыми входами двенадцатого-пятнадцатого элементов ИЛИ, выход одиннадцатого элемента ИЛИ соединен с первым входом одноразрядного трехвходового сумматора, второй и третий входы которого связаны с первым выходом тетрады С и с входом переноса из младшего десятичного разряда соответственно, первый выход матрицы сложения через третий элемент ИЛИ соединен с первым входом двадцать пятого элемента И, второй-четвертый выходы матрицы сложения подключены к входам четвертого-шестого элементов ИЛИ, пятый выход соединен с первыми входами тридцатого и тридцать второго элементов И, шестой-девятый выходы матрицы сложения соединены с входами третьего-шестого элементов ИЛИ соответственно и с входами шестнадцатого элемента ИЛИ, выход которого является сигналом переноса в старший десятичный разряд, выход четвертого элемента ИЛИ соединены с первыми входами двадцать четвертого и двадцать седьмого элементов И, выход пятого элемента ИЛИ соединен с первыми входами двадцать шестого и двадцать девятого элементов И, выход шестого элемента ИЛИ соединен с первыми входами двадцать восьмого и тридцать первого элемента И, вторые входы двадцать пятого, двадцать седьмого, двадцать девятого, тридцать первого и тридцать второго элементов И связаны с вторым выходом одноразрядного трехвходового сумматора, третий выход которого соединен с вторыми входами двадцать четвертого, двадцать шестого, двадцать восьмого и тридцатого элементов И, выходы двадцать четвертого и двадцать пятого элементов И подключены к входам седьмого элемента ИЛИ, выходы двадцать шестого и двадцать седьмого элементов И соединены с восьмым элементом ИЛИ, выходы двадцать восьмого и двадцать девятого элементов i через девятый элемент ИЛИ подключены к седьмому и восьмому элементам ИЛИ выходы тридцатого и тридцать первого элементов И соединены с входами десятого элемента ИЛИ, выходы седьмого, восьмого и десятого элементов ИЛИ соединены соответственно с вторым-четвертым входами тетрады С, пятый, шестой входы упомянутой тетрады соединены с пятым и шестым входами управления, выход тридцать второго элемента И соединен с входом шестнадцатого элемента ИЛИ.

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| - М.: Наука, 1969, с.168-170, 346-354 | |||

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| DE 3934898 А1, 02.05.1991 | |||

| JP 60186933 А, 24.09.1985 | |||

| DE 3844014 А1, 28.06.1990. | |||

Авторы

Даты

2011-01-27—Публикация

2009-07-06—Подача