Изобретение относится к вычислительной технике и может быть использовано для реализации логических функций в программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее группу из четырёх инверторов четырёх переменных, четыре группы передающих транзисторов по  транзисторов в группе, группу из шестнадцати инверторов настройки, выходной инвертор, входы четырёх переменных, шестнадцать входов настройки и выход устройства. (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С. 56-62 Рис. 9, 12 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 07.05.24 г.).

транзисторов в группе, группу из шестнадцати инверторов настройки, выходной инвертор, входы четырёх переменных, шестнадцать входов настройки и выход устройства. (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С. 56-62 Рис. 9, 12 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 07.05.24 г.).

Недостатком известного устройства является невозможность его использования в самосинхронных проектах.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее блок вычисления логической функции,  входов настройки, n входов переменных, информационный выход, причём

входов настройки, n входов переменных, информационный выход, причём  входов настройки подключены к

входов настройки подключены к  входам настройки блока вычисления логической функции, n входов переменных подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, блок вычисления двойственной логической функции, элемент ИЛИ-НЕ,

входам настройки блока вычисления логической функции, n входов переменных подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, блок вычисления двойственной логической функции, элемент ИЛИ-НЕ,  входов инверсной настройки, n входов инверсий переменных, инверсный информационный выход, выход индикации, блок вычисления логической функции содержит выходной инвертор, n групп передающих транзисторов 1.2.i (n - число входных переменных) по

входов инверсной настройки, n входов инверсий переменных, инверсный информационный выход, выход индикации, блок вычисления логической функции содержит выходной инвертор, n групп передающих транзисторов 1.2.i (n - число входных переменных) по  транзисторов в группе, группу

транзисторов в группе, группу инверторов настройки, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных, истоки

инверторов настройки, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных, истоки  транзисторов n-ой группы подключены к выходам инверторов группы

транзисторов n-ой группы подключены к выходам инверторов группы  инверторов настройки, входы которых являются группой

инверторов настройки, входы которых являются группой  входов настройки, стоки чётных и нечётных транзисторов n-ой группы объединены и подключены к истокам соответствующих

входов настройки, стоки чётных и нечётных транзисторов n-ой группы объединены и подключены к истокам соответствующих  транзисторов n-1-ой группы, стоки которых объединены и подключены к истокам соответствующих

транзисторов n-1-ой группы, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2-ой группы и так далее, стоки двух последних транзисторов 1-ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, причём

транзисторов n-2-ой группы и так далее, стоки двух последних транзисторов 1-ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, причём  входов инверсной настройки устройства подключены к

входов инверсной настройки устройства подключены к  входам настройки блока вычисления двойственной логической функции, n входов переменных подключены к n входам переменных блока вычисления двойственной логической функции, n входов инверсий переменных подключены к n входам инверсий переменных блока вычисления двойственной логической функции и блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к первому входу элемента ИЛИ-НЕ, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства и подключен ко второму входу элемента ИЛИ-НЕ, выход которого является выходом индикации устройства, причём в блоки вычисления логической функции и двойственной логической функции введены: группа 2n транзисторов инверсной проводимости, дополнительный инвертор, вход подключения шины «Ноль вольт», каждый нечётный транзистор группы 2n транзисторов инверсной проводимости которой подключен к соответствующему входу n входов инверсий переменных, а каждый чётный транзистор которой подключен к соответствующему входу n входов переменных, сток первого транзистора группы 2n транзисторов инверсной проводимости подключен к выходному инвертору блока, исток первого транзистора группы 2n транзисторов инверсной проводимости подключен к стоку второго транзистора группы 2n транзисторов инверсной проводимости, исток которого подключен к стоку третьего транзистора группы 2n транзисторов инверсной проводимости и так далее, исток 2n транзистора группы 2n транзисторов инверсной проводимости подключен к выходу дополнительного инвертора, вход которого подключен к шине «Ноль вольт», затвор каждого нечётного транзистора i-й группы передающих транзисторов

входам настройки блока вычисления двойственной логической функции, n входов переменных подключены к n входам переменных блока вычисления двойственной логической функции, n входов инверсий переменных подключены к n входам инверсий переменных блока вычисления двойственной логической функции и блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к первому входу элемента ИЛИ-НЕ, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства и подключен ко второму входу элемента ИЛИ-НЕ, выход которого является выходом индикации устройства, причём в блоки вычисления логической функции и двойственной логической функции введены: группа 2n транзисторов инверсной проводимости, дополнительный инвертор, вход подключения шины «Ноль вольт», каждый нечётный транзистор группы 2n транзисторов инверсной проводимости которой подключен к соответствующему входу n входов инверсий переменных, а каждый чётный транзистор которой подключен к соответствующему входу n входов переменных, сток первого транзистора группы 2n транзисторов инверсной проводимости подключен к выходному инвертору блока, исток первого транзистора группы 2n транзисторов инверсной проводимости подключен к стоку второго транзистора группы 2n транзисторов инверсной проводимости, исток которого подключен к стоку третьего транзистора группы 2n транзисторов инверсной проводимости и так далее, исток 2n транзистора группы 2n транзисторов инверсной проводимости подключен к выходу дополнительного инвертора, вход которого подключен к шине «Ноль вольт», затвор каждого нечётного транзистора i-й группы передающих транзисторов  блоков вычисления логической функции и двойственной логической функции подключен к i-му входу n входов инверсий переменных (патент РФ № 2601145 от 27.10.2016, кл. G11С17/00). Данное устройство принято за прототип.

блоков вычисления логической функции и двойственной логической функции подключен к i-му входу n входов инверсий переменных (патент РФ № 2601145 от 27.10.2016, кл. G11С17/00). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения: блок вычисления логической функции,  входов настройки, n входов переменных, первый информационный выход, блок вычисления двойственной логической функции, элемент 2ИЛИ-НЕ,

входов настройки, n входов переменных, первый информационный выход, блок вычисления двойственной логической функции, элемент 2ИЛИ-НЕ,  входов инверсной настройки, n входов инверсий переменных, второй инверсный информационный выход, выход индикации, причем

входов инверсной настройки, n входов инверсий переменных, второй инверсный информационный выход, выход индикации, причем  входов настройки устройства подключены к

входов настройки устройства подключены к  входам настройки блока вычисления логической функции, n входов переменных устройства подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, выход элемента 2ИЛИ-НЕ является выходом индикации;

входам настройки блока вычисления логической функции, n входов переменных устройства подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, выход элемента 2ИЛИ-НЕ является выходом индикации;

блок вычисления логической функции содержит выходной инвертор, n групп передающих транзисторов (n - число входных переменных) по  транзисторов в группе, группу

транзисторов в группе, группу  инверторов настройки; стоки чётных и нечётных транзисторов n-ой группы передающих транзисторов объединены и подключены к истокам соответствующих

инверторов настройки; стоки чётных и нечётных транзисторов n-ой группы передающих транзисторов объединены и подключены к истокам соответствующих  транзисторов n-1-ой группы передающих транзисторов, стоки которых объединены и подключены к истокам соответствующих

транзисторов n-1-ой группы передающих транзисторов, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2-ой группы передающих транзисторов и так далее, стоки двух последних транзисторов первой группы передающих транзисторов объединены и подключены ко входу выходного инвертора, выход которого является первым информационным выходом устройства; затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных блока вычисления логической функции; затвор каждого нечётного транзистора i-й группы передающих транзисторов

транзисторов n-2-ой группы передающих транзисторов и так далее, стоки двух последних транзисторов первой группы передающих транзисторов объединены и подключены ко входу выходного инвертора, выход которого является первым информационным выходом устройства; затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных блока вычисления логической функции; затвор каждого нечётного транзистора i-й группы передающих транзисторов  блока вычисления логической функции подключен к i-му входу n входов инверсий переменных блока вычисления логической функции; истоки

блока вычисления логической функции подключен к i-му входу n входов инверсий переменных блока вычисления логической функции; истоки  транзисторов n-ой группы передающих транзисторов подключены к выходам инверторов группы

транзисторов n-ой группы передающих транзисторов подключены к выходам инверторов группы  инверторов настройки, входы которых являются группой

инверторов настройки, входы которых являются группой  входов настройки блока вычисления логической функции, являющихся в свою очередь

входов настройки блока вычисления логической функции, являющихся в свою очередь  входами настройки устройства; блок вычисления двойственной логической функции аналогичен блоку вычисления логической функции;

входами настройки устройства; блок вычисления двойственной логической функции аналогичен блоку вычисления логической функции;  входов инверсной настройки устройства подключены к

входов инверсной настройки устройства подключены к  входам настройки блока вычисления двойственной логической функции; информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства.

входам настройки блока вычисления двойственной логической функции; информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства.

Недостатком известного устройства, принятого за прототип, является отсутствие универсальности и средств выбора режима синхронизации, а также невозможность использования его в синхронных устройствах ПЛИС для вычисления двух разных логических функций от разных переменных.

Это обусловлено следующими обстоятельствами.

Технические средства прототипа ориентированы на самосинхронную реализацию логических функций в совершенной дизъюнктивной нормальной форме с использованием одних и тех же парафазных переменных, подаваемых на n входов переменных и n входов инверсных переменных. Для вычисления одной заданной логической функции используются два блока: блок вычисления логической функции и блок вычисления двойственной логической функции. Поэтому в синхронных проектах, где нет парафазных переменных, также придется использовать оба блока, возможности синхронного вычисления двух разных логических функций в блоке вычисления логической функции и блоке вычисления двойственной логической функции нет.

В связи с этим, при использовании в синхронных проектах второй блок оказывается избыточным, избыточными становятся и n входов инверсий переменных.

Задачей изобретения является обеспечение возможности универсальности с выбором режима синхронизации и реализация вычисления двух разных логических функций от разных переменных в синхронных устройствах ПЛИС.

Поставленная задача была решена за счет того, что в заявляемом устройстве, содержащем блок вычисления логической функции,  входов настройки, n входов переменных, первый информационный выход, блок вычисления двойственной логической функции, элемент 2ИЛИ-НЕ,

входов настройки, n входов переменных, первый информационный выход, блок вычисления двойственной логической функции, элемент 2ИЛИ-НЕ,  входов инверсной настройки, n входов инверсий переменных, второй инверсный информационный выход, выход индикации, причем

входов инверсной настройки, n входов инверсий переменных, второй инверсный информационный выход, выход индикации, причем  входов настройки устройства подключены к

входов настройки устройства подключены к  входам настройки блока вычисления логической функции, n входов переменных устройства подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, выход элемента 2ИЛИ-НЕ является выходом индикации;

входам настройки блока вычисления логической функции, n входов переменных устройства подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, выход элемента 2ИЛИ-НЕ является выходом индикации;

блок вычисления логической функции содержит группу 2n входов настройки, информационный выход, группы n входов переменных, группы n входов инверсий переменных, выходной инвертор, n групп передающих транзисторов (n - число входных переменных) по  транзисторов в группе, группу

транзисторов в группе, группу  инверторов настройки, стоки чётных и нечётных транзисторов n-ой группы передающих транзисторов объединены и подключены к истокам соответствующих

инверторов настройки, стоки чётных и нечётных транзисторов n-ой группы передающих транзисторов объединены и подключены к истокам соответствующих  транзисторов n-1-ой группы передающих транзисторов, стоки которых объединены и подключены к истокам соответствующих

транзисторов n-1-ой группы передающих транзисторов, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2-ой группы передающих транзисторов и транзисторы в группах n-3, n-4…2 соединены аналогично, стоки двух последних транзисторов первой группы передающих транзисторов объединены и подключены ко входу выходного инвертора, выход которого является первым информационным выходом устройства, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных блока вычисления логической функции, затвор каждого нечётного транзистора i-й группы передающих транзисторов

транзисторов n-2-ой группы передающих транзисторов и транзисторы в группах n-3, n-4…2 соединены аналогично, стоки двух последних транзисторов первой группы передающих транзисторов объединены и подключены ко входу выходного инвертора, выход которого является первым информационным выходом устройства, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных блока вычисления логической функции, затвор каждого нечётного транзистора i-й группы передающих транзисторов  блока вычисления логической функции подключен к i-му входу n входов инверсий переменных блока вычисления логической функции, истоки

блока вычисления логической функции подключен к i-му входу n входов инверсий переменных блока вычисления логической функции, истоки  транзисторов n-ой группы передающих транзисторов подключены к выходам инверторов группы

транзисторов n-ой группы передающих транзисторов подключены к выходам инверторов группы  инверторов настройки, входы которых являются группой

инверторов настройки, входы которых являются группой  входов настройки блока вычисления логической функции, являющихся в свою очередь

входов настройки блока вычисления логической функции, являющихся в свою очередь  входами настройки устройства;

входами настройки устройства;

блок вычисления двойственной логической функции аналогичен блоку вычисления логической функции,  входов инверсной настройки устройства подключены к

входов инверсной настройки устройства подключены к  входам настройки блока вычисления двойственной логической функции, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства, согласно изобретению дополнительно введены.

входам настройки блока вычисления двойственной логической функции, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства, согласно изобретению дополнительно введены.

n блоков подключения переменных, первый вход управления, второй вход управления, группа первых выходов управления, второй выход управления, группа из четырех транзисторов элементом 2ИЛИ-НЕ, вход источника питания, причем первые входы всех блоков подключения переменных подключены ко входу источника питания, вторые входы всех блоков подключения переменных подключены ко второму входу управления, третьи входы каждого j-го блока подключения переменных подключены к соответствующему j-му входу переменных j=1… n, четвертые входы каждого j-го блока подключения переменных подключены к соответствующему j-му входу инверсии переменных, j=1…n, пятые входы всех блоков подключения переменных подключены к первому входу управления, первые выходы каждого j-го блока подключения переменных подключены к соответствующему j-му входу инверсий переменных, j=1…n блока вычисления логической функции, вторые выходы каждого j-го блока подключения переменных подключены к соответствующему j-му входу переменных, j=1…n блока вычисления логической функции, третьи выходы каждого j-го блока подключения переменных подключены к соответствующему j-му входу инверсий переменных блока вычисления двойственной логической функции, четвертые выходы каждого j-го блока подключения переменных подключены к соответствующему j-му входу переменных блока вычисления двойственной логической функции, пятые выходы каждого j-го блока подключения переменных являются соответствующим j-м выходом группы первых выходов управления, второй выход управления последнего, n-го блока подключения переменных подключен к затворам первого и второго транзисторов управления элементом 2ИЛИ-НЕ, истоки которых подключены а первому и второму информационным выходам устройства соответственно, а стоки подключены к первому и второму входам элемента 2ИЛИ-НЕ соответственно, а также к стокам третьего и четвертого транзисторов управления элементом 2ИЛИ-НЕ соответственно, истоки которых подключены ко входу источника питания устройства, а затворы третьего и четвертого транзисторов управления элементом 2ИЛИ-НЕ объединены и подключены ко второму входу управления устройства.

Каждый j-ый, j=1…n блок подключения переменных содержит три элемента 2И-НЕ, пять инверторов, восемь транзисторов, пять входов, шесть выходов, причем вторые входы первого и второго элементов 2И-НЕ объединены и подключены к пятому входу блока подключения переменных, первый вход первого элемента 2И-НЕ подключен к третьему входу блока подключения переменных и к истоку первого транзистора, первый вход второго элемента 2И-НЕ подключен к четвертому входу блока подключения переменных и к истоку третьего транзистора, выход первого элемента 2И-НЕ подключен ко входу первого инвертора, а также к истокам четвертого и седьмого транзистора, выход второго элемента 2И-НЕ подключен ко входу третьего инвертора, а также к истоку второго транзистора и к истоку восьмого транзистора, выходы первого, второго, третьего и четвертого инверторов являются соответствующими первым, вторым, третьим и четвертым выходами блока подключения переменных, выход третьего элемента 2И-НЕ является пятым выходом блока подключения переменных, выход пятого инвертора является шестым выходом блока подключения переменных, выход пятого инвертора также подключен к затворам второго, четвертого, седьмого и восьмого транзисторов, второй вход блока подключения переменных подключен к затворам первого и третьего транзисторов, ко входу пятого инвертора и затворам пятого и шестого транзисторов, истоки которых подключены к первому входу блока подключения переменных, сток пятого транзистора подключен к первому входу третьего элемента 2И-НЕ и стоку седьмого транзистора, сток шестого транзистора подключен ко второму входу третьего элемента 2И-НЕ и стоку восьмого транзистора, стоки первого и второго транзисторов объединены и подключены ко входу второго инвертора, стоки третьего и четвертого транзисторов объединены и подключены ко входу третьего инвертора.

Блок вычисления логической функции дополнительно содержит также группу 2n транзисторов реализации спейсера, транзистор отключения спейсера, первый вход, второй вход.

Каждый нечётный транзистор группы 2n транзисторов реализации спейсера подключен к соответствующему из n входов инверсий переменных.

Каждый чётный транзистор группы 2n транзисторов реализации спейсера подключен к соответствующему из n входов переменных.

Сток первого транзистора группы 2n транзисторов реализации спейсера подключен к истоку транзистора отключения спейсера, сток которого подключен ко входу выходного инвертора, а затвор является входом блока, который подключен к первому входу управления, исток 2n -го транзистора группы 2n транзисторов реализации спейсера подключен к первому входу блока вычисления логической функции.

Признаки заявляемого технического решения, отличительные от прототипа: содержит n блоков подключения переменных, первый вход управления, второй вход управления, группу первых выходов управления, второй выход управления, группу из четырех транзисторов управления элементом 2ИЛИ-НЕ, вход источника питания; блок вычисления логической функции дополнительно содержит группу 2n транзисторов реализации спейсера, транзистор отключения спейсера, первый вход, второй вход, а также новые связи между элементами устройства.

Отличительные признаки в сочетании с известными позволяют обеспечить универсальность с выбором режима синхронизации и реализацию вычисления двух разных логических функций от разных переменных в синхронных устройствах ПЛИС.

Введение n блоков подключения переменных позволяет обеспечить по сигналу на втором входе управления выбор режима синхронизации, в случае самосинхронизации этот сигнал равен нулю и обеспечивается передача на соответствующие входы n переменных и n инверсий переменных блоков вычисления логической функции и вычисления двойственной функции парафазных переменных с соответствующими входами n переменных и n инверсий переменных устройства через вторые третьи входы блоков подключения переменных и его первый и второй выходы. При этом используется сигнал на первом входе управления всех блоков подключения переменных, который формирует внешний Г-триггер и реализуется двух фазная дисциплина, состоящая из фаз спейсера и рабочей фазы, использующая также сигнал индикации с пятого выхода всех блоков подключения переменных и сигнал с выхода индикации устройства. В случае же синхронного режима втором входе управления равен единице, что обеспечивает передачу на каждый из блоков вычисления логической функции и вычисления двойственной функции своей переменной и ее инверсии, сигналы со входов n переменных - на блок вычисления логической функции, а сигналы со входов n инверсий переменных устройства - на блок вычисления логической функции, который теперь вычисляет свою собственную (а не двойственную функцию блока вычисления логической функции) функцию, задаваемую по  входам инверсной настройки, при этом функцию блока вычисления логической функции определяют

входам инверсной настройки, при этом функцию блока вычисления логической функции определяют  входов настройки.

входов настройки.

При этом сигнал на первом входе управления равен единице, то есть принимает нейтральное значение, не препятствующее синхронной, обычной работе устройства.

Кроме этого, второй выход управления последнего блока подключения переменных переводит в нейтральное состояние элемента 2ИЛИ-НЕ с помощью введенных четырех транзисторов управления элементом 2ИЛИ-НЕ, которые обеспечивают его работы в самосинхронном режиме.

Введение первого входа управления позволяет принимать сигнал внешнего Г-триггера для обеспечения режима самосинхронной работы.

Введение второго входа управления позволяет осуществлять конфигурирование режима работы устройства: либо синхронный (на входе 1), либо самосинхронный (на входе 0).

Введение группы первых выходов управления позволяет внешнему устройству в самосинхронном режиме оценивать завершение переходного процесса приема нулевого спейсера (ноль по всем входам n переменных и n инверсий переменных) в фазе спейсера.

Введение второго выхода управления с последнего блока подключения переменных позволяет управлять состоянием элемента 2ИЛИ-НЕ, который в самосинхронном режиме индицирует рабочую фазу, либо находится в нейтральном состоянии в синхронном режиме.

Введение группы из четырех транзисторов управления элементом 2ИЛИ-НЕ позволяет управлять состоянием элемента 2ИЛИ-НЕ, который в самосинхронном режиме индицирует рабочую фазу, либо находится в нейтральном состоянии в синхронном режиме, когда на его входы поданы сигналы логической единицы со входа источника питания.

Введение в блок вычисления логической функции группу 2n транзисторов реализации спейсера позволяет обеспечить в случае нулей по всем входам n переменных и n инверсий переменных подачу логической единицы со входа источника питания устройства через первый вход блок вычисления логической функции, через транзистор отключения спейсера на выходной инвертор.

Введение транзистора отключения спейсера позволяет отключать группу 2n транзисторов реализации спейсера в синхронном режиме работы по второму входу блока вычисления логической функции, на который поступает сигнал со второго выход управления устройства.

Введение первого входа блока вычисления логической функции позволяет принимать уровень логической единицы со входа источника питания устройства для обеспечения самосинхронной работы в соответствующем режиме.

Введение второго входа блока вычисления логической функции позволяет принимать сигнал со второго выход управления устройства для управления транзистором отключения спейсера.

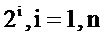

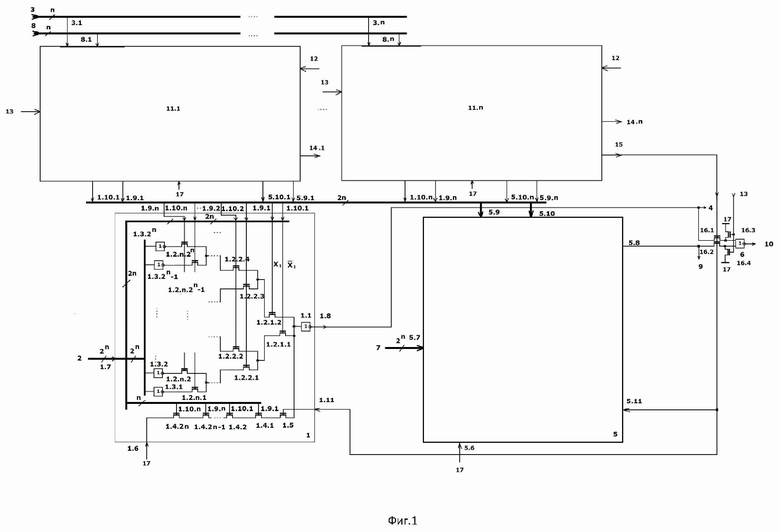

На Фиг. 1 изображена схема электрическая принципиальная программируемого логического устройства.

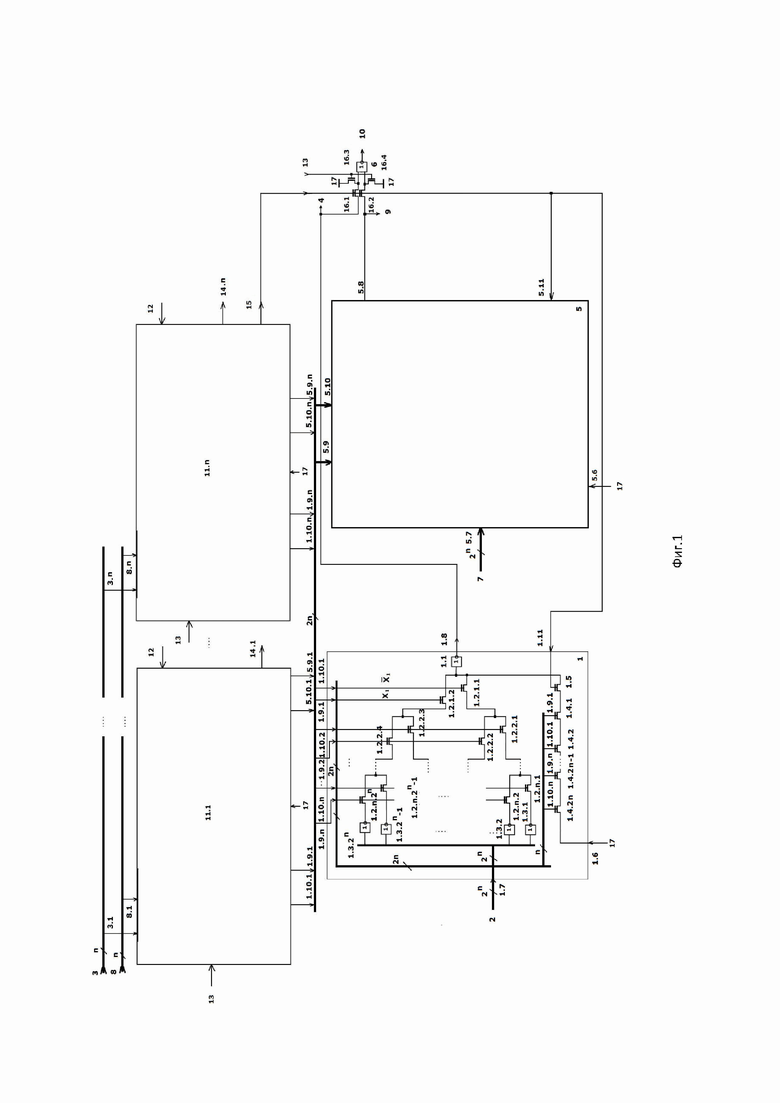

На Фиг. 2 изображена схема электрическая принципиальная блока подключения переменных.

Программируемое логическое устройство (фиг.1) содержит блок вычисления логической функции 1,  входов настройки 2, n входов переменных 3, первый информационный выход 4, блок вычисления двойственной логической функции 5, элемент 2ИЛИ-НЕ 6,

входов настройки 2, n входов переменных 3, первый информационный выход 4, блок вычисления двойственной логической функции 5, элемент 2ИЛИ-НЕ 6,  входов инверсной настройки 7, n входов инверсий переменных 8, второй инверсный информационный выход 9, выход индикации 10, причём

входов инверсной настройки 7, n входов инверсий переменных 8, второй инверсный информационный выход 9, выход индикации 10, причём  входов настройки 2 устройства подключены к

входов настройки 2 устройства подключены к  входам 1.7 настройки блока вычисления логической функции 1, n входов переменных 3 устройства подключены к n входам 1.9.1-1.9.n переменных блока вычисления логической функции, информационный выход 1.8 блока вычисления логической функции 1 подключен к информационному 4 выходу устройства. В устройство введены n блоков подключения переменных 11 (фиг.2), первый вход управления 12, второй вход управления 13, группа первых выходов управления 14.1, 14.2, … 14.n, второй выход управления 15, группа из четырех транзисторов 16 управления 16.1, 16.2, 16.3, 16.4 элементом 2ИЛИ-НЕ 6, вход источника питания 17. Первые входы всех блоков подключения переменных 11 подключены ко входу источника питания 17, вторые входы всех блоков подключения переменных 11 подключены ко второму входу управления 13, третьи входы каждого блока подключения переменных 11.j подключены к соответствующему входу переменных 3.j, j=1… n, четвертые входы каждого блока подключения переменных 11.j подключены к соответствующему входу инверсии переменных 8.j, j=1… n, пятые входы всех блоков подключения переменных 11 подключены к первому входу управления 12.

входам 1.7 настройки блока вычисления логической функции 1, n входов переменных 3 устройства подключены к n входам 1.9.1-1.9.n переменных блока вычисления логической функции, информационный выход 1.8 блока вычисления логической функции 1 подключен к информационному 4 выходу устройства. В устройство введены n блоков подключения переменных 11 (фиг.2), первый вход управления 12, второй вход управления 13, группа первых выходов управления 14.1, 14.2, … 14.n, второй выход управления 15, группа из четырех транзисторов 16 управления 16.1, 16.2, 16.3, 16.4 элементом 2ИЛИ-НЕ 6, вход источника питания 17. Первые входы всех блоков подключения переменных 11 подключены ко входу источника питания 17, вторые входы всех блоков подключения переменных 11 подключены ко второму входу управления 13, третьи входы каждого блока подключения переменных 11.j подключены к соответствующему входу переменных 3.j, j=1… n, четвертые входы каждого блока подключения переменных 11.j подключены к соответствующему входу инверсии переменных 8.j, j=1… n, пятые входы всех блоков подключения переменных 11 подключены к первому входу управления 12.

Первые выходы каждого блока подключения переменных 11.j подключены к соответствующему j-му входу инверсий переменных 1.10.j, j=1… n блока вычислений логической функции 1,

вторые выходы каждого блока подключения переменных 11.j подключены к соответствующему j-му входу переменных 1.9.j, j=1… n блока вычислений логической функции 1,

третьи выходы каждого блока подключения переменных 11.j подключены к соответствующему j-му входу инверсий переменных 5.10.j, j=1… n блока вычисления двойственной логической функции 5,

четвертые выходы каждого блока подключения переменных 11.j подключены к соответствующему j-му входу переменных 5.9.j, j=1… n блока вычисления двойственной логической функции 5,

пятые выходы каждого блока подключения переменных 11.j являются соответствующим j-м выходом группы первых выходов управления,

второй выход управления 15 последнего, n-го блока подключения переменных 11.n подключен к затворам первого 16.1 и второго 16.2 транзисторов управления 16, истоки которых подключены а первому 4 и второму 9 информационным выходам соответственно, а стоки подключены к первому и второму входам элемента 2ИЛИ-НЕ 6 соответственно, а также к стокам третьего 16.3 и четвертого 16.4 транзисторов управления 16 соответственно, истоки которых подключены ко входу источника питания 17, а затворы третьего 16.3 и четвертого 16.4 транзисторов управления 16 объединены и подключены ко второму входу управления 13.

Блок вычисления логической функции 1 содержит выходной инвертор 1.1, n групп передающих транзисторов 1.2.i (n - число входных переменных) по  транзисторов в группе, группу

транзисторов в группе, группу инверторов настройки 1.3.

инверторов настройки 1.3.

Стоки чётных и нечётных транзисторов n-ой группы передающих транзисторов 1.2 объединены и подключены к истокам соответствующих  транзисторов n-1 ой группы передающих транзисторов 1.2, стоки которых объединены и подключены к истокам соответствующих

транзисторов n-1 ой группы передающих транзисторов 1.2, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2 ой группы передающих транзисторов 1.2 и так далее, стоки двух последних транзисторов 1.2.1.2, 1.2.1.1 первой группы передающих транзисторов 1.2 объединены и подключены ко входу выходного инвертора 1.1, выход которого 1.8 является информационным выходом 4 устройства.

транзисторов n-2 ой группы передающих транзисторов 1.2 и так далее, стоки двух последних транзисторов 1.2.1.2, 1.2.1.1 первой группы передающих транзисторов 1.2 объединены и подключены ко входу выходного инвертора 1.1, выход которого 1.8 является информационным выходом 4 устройства.

Блоки вычисления логической функции 1 содержит также группу 2n транзисторов реализации спейсера 1.4, транзистор отключения спейсера 1.5, первый вход 1.6, группы 2n входов настройки 1.7, информационный выход 1.8, группы n входов переменных 1.9, группы n входов инверсий переменных 1.10, второй вход 1.11.

Каждый нечётный транзистор группы 2n транзисторов реализации спейсера 1.4: 1.4.1, 1.4.3, 1.4.5 и так далее до 1.4. 2n-1 подключен к соответствующему входу 1.10.1, 1.10.2, 1.10.3…1.10.n n входов 1.10 инверсий переменных.

Каждый чётный транзистор группы 2n транзисторов реализации спейсера 1.4: 1.4.2, 1.4.4, 1.4.6 и так далее до 1.4. 2n подключен к соответствующему входу 1.9.1, 1.9.2, 1.9.3…1.9. n n входов переменных 1.9.

Сток первого транзистора 1.4.1 группы 2n транзисторов реализации спейсера 1.4 подключен к истоку транзистора отключения спейсера 1.5, сток которого подключен ко входу выходного инвертора 1.1, а затвор является входом 1.11 блока 1, который подключен к первому входу управления 15, исток 2n-го транзистора 1.4.2n группы 2n транзисторов реализации спейсера 1.4 подключен ко входу 1.6

Блок вычисления двойственной логической функции 5 аналогичен блоку вычисления логической функции 1.

входов инверсной настройки 7 устройства подключены к

входов инверсной настройки 7 устройства подключены к  входам настройки блока вычисления двойственной логической функции 5.

входам настройки блока вычисления двойственной логической функции 5.

n входов переменных 3 подключены к n входам переменных блока вычисления двойственной логической функции 5.

n входов инверсий переменных 8 подключены к n входам инверсий переменных блока вычисления двойственной логической функции 5 и блока вычисления логической функции 1.

Информационный выход 1.8 блока вычисления логической функции 1 подключен ко первому входу элемента ИЛИ-НЕ 6.

Информационный выход блока вычисления двойственной логической функции 5 является инверсным информационным выходом устройства 9 и подключен ко второму входу элемента ИЛИ-НЕ 6, выход которого является выходом индикации устройства 10.

Затвор каждого чётного транзистора i-й группы передающих транзисторов 1.2 подключен к i-му входу n входов переменных 1.9. Истоки  транзисторов n-ой группы передающих транзисторов 1.2 подключены к выходам инверторов группы

транзисторов n-ой группы передающих транзисторов 1.2 подключены к выходам инверторов группы  инверторов настройки 1.3, входы которых являются группой

инверторов настройки 1.3, входы которых являются группой  входов настройки 1.7 блока вычисления логической функции 1.

входов настройки 1.7 блока вычисления логической функции 1.

Затвор каждого нечётного транзистора i-й группы передающих транзисторов 1.2  блока вычисления логической функции 1 подключен к i-му входу n входов инверсий переменных 1.10 блока 1.

блока вычисления логической функции 1 подключен к i-му входу n входов инверсий переменных 1.10 блока 1.

Каждый j-ый, j=1…n блок подключения переменных 11 содержит три элемента 2И-НЕ 11.j.1, 11.j.2, 11.j.3, пять инверторов 11.j.4, 11.j.5, 11.j.6, 11.j.7, 11.j.8, восемь транзисторов 11.j.9, 11.j.10, 11.j.11, 11.j.12,11.j.13, 11.j.14, 11.j.15, 11.j.16, пять входов 11.j.17, 11.j.18, 11.j.19, 11.j.20, 11.j.21, шесть выходов 11.j.22, 11.j.23, 11.j.24, 11.j.25, 11.j.26, 11.j.27, причем вторые входы первого и второго элементов 2И-НЕ 11.j.1, 11.j.2 объединены и подключены к пятому входу 11.j.21 блока подключения переменных, первый вход первого элемента 2И-НЕ 11.j.1 подключен к третьему входу 11.j.19 блока подключения переменных и к истоку первого транзистора 11.j.9, первый вход второго элемента 2И-НЕ 11.j.2 подключен к четвертому входу 11.j.20 блока подключения переменных и к истоку третьего транзистора 11.j.11, выход первого элемента 2И-НЕ 11.j.1 подключен ко входу первого инвертора 11.j.4, а также к истокам четвертого 11.j.12 и седьмого транзистора 11.j.15, выход второго элемента 2И-НЕ 11.j.2 подключен ко входу третьего инвертора 11.j.6, а также к истоку второго транзистора 11.j.10 и к истоку восьмого транзистора 11.j.16, выходы первого 11.j.4, второго 11.j.5, третьего 11.j.6 и четвертого 11.j.7 инверторов являются соответствующими первым 11.j.22, вторым 11.j.23, третьим 11.j.24 и четвертым 11.j.25 выходами блока подключения переменных 11.j, выход третьего элемента 2И-НЕ 11.j.3 является пятым выходом 11.j.26 блока подключения переменных 11.j, выход пятого инвертора 11.j.8 является шестым выходом 11.j.27 блока подключения переменных11.j, выход пятого инвертора 11.j.8 также подключен к затворам второго 11.j.10, четвертого 11.j.12, седьмого 11.j.15 и восьмого 11.j.16 транзисторов,

второй вход 11.j.18 блока подключения переменных 11.j подключен к затворам первого 11.j.9 и третьего 11.j.11 транзисторов, ко входу пятого инвертора 11.j.8 и затворам пятого 11.j.13 и шестого 11.j.14 транзисторов, истоки которых подключены к первому входу 11.j.17 блока подключения переменных 11.j, сток пятого транзистора 11.j.13 подключен к первому входу третьего элемента 2И-НЕ 11.j.3 и стоку седьмого 11.j.15 транзистора, сток шестого транзистора 11.j.14 подключен ко второму входу третьего элемента 2И-НЕ 11.j.3 и стоку восьмого 11.j.16 транзистора, стоки первого 11.j.9 и второго 11.j.10 транзисторов объединены и подключены ко входу второго инвертора 11.j.5, стоки третьего 11.j.11 и четвертого 11.j.12 транзисторов объединены и подключены ко входу третьего инвертора 11.j.8.

Программируемое логическое устройство работает в следующих режимах: 1) Программирования; 2) Самосинхронной реализации логической функции; 3) Синхронной реализации двух разных логических функций от разных переменных в каждом из двух блоков вычисления логической функции 1 и 5.

1) Программирование

В этом режиме устройство работает аналогично прототипу, за исключением того, что кроме всего прочего, задается и режим синхронизации по второму входу управления 13: либо синхронный (на входе 1), либо самосинхронный (на входе 0).

В синхронном режиме (на входе 13 устанавливается 1), на  входах настройки 2 и

входах настройки 2 и  входах инверсной настройки 7 устанавливаются константы, соответствующие значениям двух различных логических функций от различных переменных на n входах переменных 3 и n входов инверсий переменных 8. В блоках вычисления логической функции 1 и вычисления двойственной логической функции 5 отключаются транзисторы отключения спейсера 1.5. Элемент 2ИЛИ-НЕ 6 отключается от входов блоков вычисления логической функции 1 и вычисления двойственной логической функции 5 и на его выходе устанавливается сигнал логического нуля.

входах инверсной настройки 7 устанавливаются константы, соответствующие значениям двух различных логических функций от различных переменных на n входах переменных 3 и n входов инверсий переменных 8. В блоках вычисления логической функции 1 и вычисления двойственной логической функции 5 отключаются транзисторы отключения спейсера 1.5. Элемент 2ИЛИ-НЕ 6 отключается от входов блоков вычисления логической функции 1 и вычисления двойственной логической функции 5 и на его выходе устанавливается сигнал логического нуля.

В блоках подключения переменных 11 третьи элементы 2И-НЕ 11.j.3, j=1…n, отключаются от выходов первого 11.j.1 и второго 11.j.2 элементов 2И-НЕ и на его выходе устанавливается сигнал логического нуля.

В самосинхронном режиме (на входе 13 устанавливается 0) на  входах настройки 2 устанавливаются константы, соответствующие значениям заданной логической функции, а на

входах настройки 2 устанавливаются константы, соответствующие значениям заданной логической функции, а на  входах инверсной настройки 7 устанавливаются константы, соответствующие значениям инверсной логической функции.

входах инверсной настройки 7 устанавливаются константы, соответствующие значениям инверсной логической функции.

Соответственно, n блоков подключения переменных 11 в синхронном режиме (на входе 13 устанавливается 1) обеспечивают передачу с n входов переменных 3 на соответствующие входы блока вычисления логической функции 1 значения переменных и их инверсий, а на соответствующие входы блока вычисления двойственной логической функции 5 значения переменных и их инверсий с n входов инверсий переменных 8.

В блоках вычисления логической функции 1 и вычисления двойственной логической функции 5 подключаются транзисторы отключения спейсера 1.5. Элемент 2ИЛИ-НЕ 6 подключается к выходам блоков вычисления логической функции 1 и вычисления двойственной логической функции 5 для фиксации рабочей фазы и фазы спейсера.

В блоках подключения переменных 11 третьи элементы 2И-НЕ 11.j.3, j=1…n, подключаются ко выходам первого 11.j.1 и второго 11.j.2 элементов 2И-НЕ для фиксации рабочей фазы и фазы спейсера.

2) Самосинхронной реализации логической функции

В этом режиме устройство работает аналогично прототипу, за исключением того, что подача парафазных сигналов переменных в рабочей фазе и реализация нулевого спейсера в фазе спейсера осуществляется с помощью блоков подключения переменных 11, настроенных соответствующим образом в режиме программирования. Кроме того, соответствующим образом настроены в блоках подключения переменных 11 третьи элементы 2И-НЕ 11.j.3, элемент 2ИЛИ-НЕ 6.

В блоках вычисления логической функции 1 и вычисления двойственной логической функции 5 подключаются транзисторы отключения спейсера 1.5.

Вычисления осуществляются в соответствие с двухфазной дисциплиной функционирования.

2.1. Фаза гашения

В фазе гашения внешний гистерезисный триггер устанавливает на входе 12 устройства уровень логического нуля, поэтому в блоках подключения переменных 11 выходы первого 11.j.1 и второго 11.j.2 элементов 2И-НЕ устанавливаются в состояние логической единицы, а выходы соответствующих инверторов 11.j.4, 11.j.5 - в состояние логического нуля, переводя в состояние логического нуля затворы всех транзисторов n групп передающих транзисторов 1.2.i в блоках вычисления логической функции 1 и вычисления двойственной логической функции 5. Одновременно в блоках вычисления логической функции 1 и вычисления двойственной логической функции 5 переводятся в состояние логической единицы затворы всех транзисторов группы 2n транзисторов реализации спейсера 1.4, поэтому логическая единица со входа источника питания 17, через вход 1.6 (5.6) поступает на вход выходного инвертора 1.1 (5.1) и на его выходе устанавливается логический ноль.

В результате на выходе элемента 2ИЛИ-НЕ 6 устанавливается логическая единица, сигнализирующая по выходу индикации 10 устройства внешнему оборудованию о завершении фазы гашения.

2.2. Рабочая фаза

В рабочей фазе внешний гистерезисный триггер, получив сигнал завершения фазы гашения по выходу индикации 10 устройства устанавливается в состояние единицы, выдавая на вход 12 устройства уровень логической единицы, поэтому в блоках подключения переменных 11 первый 11.j.1 и второй 11.j.2 элементы 2И-НЕ, соответствующие инверторы 11.j.4, 11.j.5 принимают внешний парафазный сигнал (10, либо 01) соответствующей переменной и передают его как на входы блока вычисления логической функции 1, так и на входы блока вычисления двойственной логической функции 5.

В результате начинается вычисление логической функции в блоке вычисления логической функции 1 и двойственной логической функции в блоке вычисления двойственной логической функции 5.

Сигналы настройки логической функции со входов 2 (1.7 блока 1), 7 (5.7 блока 5) активируют одну 2n из цепочек транзисторов 1.2 блока вычисления логической функции 1 (5.2 блока вычисления двойственной логической функции 5), поэтому на выходах выходного инвертора 1.1 (выход 1.8 блока 1) появляется на первом информационном выходе устройства 4, значение инверсной функции появляется на выходах выходного инвертора 5.1 (выход 5.8 блока 1) и на втором информационном выходе устройства 9. Поэтому выход элемента 2ИЛИ-НЕ 6 устанавливается логический ноль, сигнализирующий по выходу индикации 10 устройства внешнему оборудованию о завершении рабочей фазы.

Далее снова может следовать фаза гашения, установка нового значения входов 3.i, 8.i далее очередная рабочая фаза и т.д., и т.п.

3) Синхронная реализация двух логических функций от разных переменных в каждом из двух блоков вычисления логической функции 1 и 5.

В этом режиме на входе 13 установлена 1 (во время программирования), на  входах настройки 2 и

входах настройки 2 и  входах инверсной настройки 7 установлены константы, соответствующие значениям двух различных логических функций от различных переменных на n входах переменных 3 и n входов инверсий переменных 8. В блоках вычисления логической функции 1 и вычисления двойственной логической функции 5 отключены транзисторы отключения спейсера 1.5. Элемент 2ИЛИ-НЕ 6 отключен от входов блоков вычисления логической функции 1 и вычисления двойственной логической функции 5 и на его выходе установлен сигнал логического нуля. Блок вычисления логической функции 1 и вычисления двойственной логической функции 5 вычисляют две различные логические функции от разных переменных, которые поступают в эти блоки через блоки подключения переменных 11 в формате «переменная», «инверсия этой переменной» через соответствующие выходы:

входах инверсной настройки 7 установлены константы, соответствующие значениям двух различных логических функций от различных переменных на n входах переменных 3 и n входов инверсий переменных 8. В блоках вычисления логической функции 1 и вычисления двойственной логической функции 5 отключены транзисторы отключения спейсера 1.5. Элемент 2ИЛИ-НЕ 6 отключен от входов блоков вычисления логической функции 1 и вычисления двойственной логической функции 5 и на его выходе установлен сигнал логического нуля. Блок вычисления логической функции 1 и вычисления двойственной логической функции 5 вычисляют две различные логические функции от разных переменных, которые поступают в эти блоки через блоки подключения переменных 11 в формате «переменная», «инверсия этой переменной» через соответствующие выходы:

11.j.22 и второй 11.j.23 - на блок вычисления логической функции 1, 11.j.24 и второй 11.j.25 - на блок вычисления двойственной логической функции 5, но это не двойственная функция, это совершенно произвольная функция.

Таким образом на первом информационном выходе 4 и на втором информационном выходе устройства 9 появляются значения двух заданных в режиме программирования логических функций, которые могут быть записаны во внешние по отношению к устройству синхронные элементы памяти. При необходимости может быть проведено новое программирование и заданы другие режимы синхронизации и логические функции.

Таким образом, в отличие от прототипа, устройство универсально и может быть использовано в одной ПЛИС в зависимости от настройки (программирования) с помощью средств выбора режима как для самосинхронной, так и для синхронной реализации логических функций.

Достижение технического результата изобретения подтверждается приведённым описанием работы устройства в различных режимах.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832937C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| Программируемое логическое устройство | 2023 |

|

RU2826302C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2547229C1 |

Изобретение относится к вычислительной технике и может быть использовано для реализации логических функций в программируемых логических интегральных схемах (ПЛИС). Технический результат заключается в обеспечении возможности выбора режима синхронизации и реализации вычисления двух разных логических функций от разных переменных в синхронных устройствах ПЛИС. Технический результат достигается за счёт введения в программируемое логическое устройство n блоков подключения переменных, первого входа управления, второго входа управления, группы первых выходов управления, второго выхода управления, группы из четырех транзисторов управления элементом 2ИЛИ-НЕ, входа источника питания, введения в блок вычисления логической функции группы 2n транзисторов реализации спейсера, транзистора отключения спейсера, первого входа, второго входа. 2 ил.

Программируемое логическое устройство, содержащее блок вычисления логической функции,  входов настройки, n входов переменных, первый информационный выход, блок вычисления двойственной логической функции, элемент 2ИЛИ-НЕ,

входов настройки, n входов переменных, первый информационный выход, блок вычисления двойственной логической функции, элемент 2ИЛИ-НЕ,  входов инверсной настройки, n входов инверсий переменных, второй инверсный информационный выход, выход индикации, причем

входов инверсной настройки, n входов инверсий переменных, второй инверсный информационный выход, выход индикации, причем  входов настройки устройства подключены к

входов настройки устройства подключены к  входам настройки блока вычисления логической функции, n входов переменных устройства подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, выход элемента 2ИЛИ-НЕ является выходом индикации,

входам настройки блока вычисления логической функции, n входов переменных устройства подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, выход элемента 2ИЛИ-НЕ является выходом индикации,

блок вычисления логической функции содержит группу 2n входов настройки, информационный выход, группы n входов переменных, группы n входов инверсий переменных, выходной инвертор, n групп передающих транзисторов, n - число входных переменных,

по  транзисторов в группе, группу

транзисторов в группе, группу инверторов настройки, стоки чётных и нечётных транзисторов n-ой группы передающих транзисторов объединены и подключены к истокам соответствующих

инверторов настройки, стоки чётных и нечётных транзисторов n-ой группы передающих транзисторов объединены и подключены к истокам соответствующих  транзисторов n-1-ой группы передающих транзисторов, стоки которых объединены и подключены к истокам соответствующих

транзисторов n-1-ой группы передающих транзисторов, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2-ой группы передающих транзисторов и транзисторы в группах n-3, n-4…2 соединены аналогично, стоки двух последних транзисторов первой группы передающих транзисторов объединены и подключены ко входу выходного инвертора, выход которого является первым информационным выходом устройства, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных блока вычисления логической функции, затвор каждого нечётного транзистора i-й группы передающих транзисторов

транзисторов n-2-ой группы передающих транзисторов и транзисторы в группах n-3, n-4…2 соединены аналогично, стоки двух последних транзисторов первой группы передающих транзисторов объединены и подключены ко входу выходного инвертора, выход которого является первым информационным выходом устройства, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных блока вычисления логической функции, затвор каждого нечётного транзистора i-й группы передающих транзисторов  блока вычисления логической функции подключен i-му входу n входов инверсий переменных блока вычисления логической функции, истоки

блока вычисления логической функции подключен i-му входу n входов инверсий переменных блока вычисления логической функции, истоки  транзисторов n-ой группы передающих транзисторов подключены к выходам инверторов группы

транзисторов n-ой группы передающих транзисторов подключены к выходам инверторов группы  инверторов настройки, входы которых являются группой

инверторов настройки, входы которых являются группой  входов настройки блока вычисления логической функции, являющихся в свою очередь

входов настройки блока вычисления логической функции, являющихся в свою очередь  входами настройки устройства,

входами настройки устройства,

блок вычисления двойственной логической функции аналогичен блоку вычисления логической функции,  входов инверсной настройки устройства подключены к

входов инверсной настройки устройства подключены к  входам настройки блока вычисления двойственной логической функции, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства, отличающееся тем, что в него дополнительно введены

входам настройки блока вычисления двойственной логической функции, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства, отличающееся тем, что в него дополнительно введены

n блоков подключения переменных, первый вход управления, второй вход управления, группа первых выходов управления, второй выход управления, группа из четырех транзисторов элементом 2ИЛИ-НЕ, вход источника питания, причем первые входы всех блоков подключения переменных подключены ко входу источника питания, вторые входы всех блоков подключения переменных подключены ко второму входу управления, третьи входы каждого j-го блока подключения переменных подключены к соответствующему j-му входу переменных j=1… n, четвертые входы каждого j-го блока подключения переменных подключены к соответствующему j-му входу инверсии переменных, j=1… n, пятые входы всех блоков подключения переменных подключены к первому входу управления, первые выходы каждого j-го блока подключения переменных подключены к соответствующему j-му входу инверсий переменных, j=1… n блока вычисления логической функции, вторые выходы каждого j-го блока подключения переменных подключены к соответствующему j-му входу переменных, j=1… n блока вычисления логической функции, третьи выходы каждого j-го блока подключения переменных подключены к соответствующему j-му входу инверсий переменных блока вычисления двойственной логической функции, четвертые выходы каждого j-го блока подключения переменных подключены к соответствующему j-му входу переменных блока вычисления двойственной логической функции, пятые выходы каждого j-го блока подключения переменных являются соответствующим j-м выходом группы первых выходов управления, второй выход управления последнего, n-го блока подключения переменных подключен к затворам первого и второго транзисторов управления элементом 2ИЛИ-НЕ, истоки которых подключены а первому и второму информационным выходам устройства соответственно, а стоки подключены к первому и второму входам элемента 2ИЛИ-НЕ соответственно, а также к стокам третьего и четвертого транзисторов управления элементом 2ИЛИ-НЕ соответственно, истоки которых подключены ко входу источника питания устройства, а затворы третьего и четвертого транзисторов управления элементом 2ИЛИ-НЕ объединены и подключены ко второму входу управления устройства;

каждый j-ый, j=1…n блок подключения переменных содержит три элемента 2И-НЕ, пять инверторов, восемь транзисторов, пять входов, шесть выходов, причем вторые входы первого и второго элементов 2И-НЕ объединены и подключены к пятому входу блока подключения переменных, первый вход первого элемента 2И-НЕ подключен к третьему входу блока подключения переменных и к истоку первого транзистора, первый вход второго элемента 2И-НЕ подключен к четвертому входу блока подключения переменных и к истоку третьего транзистора, выход первого элемента 2И-НЕ подключен ко входу первого инвертора, а также к истокам четвертого и седьмого транзистора, выход второго элемента 2И-НЕ подключен ко входу третьего инвертора, а также к истоку второго транзистора и к истоку восьмого транзистора, выходы первого, второго, третьего и четвертого инверторов являются соответствующими первым, вторым, третьим и четвертым выходами блока подключения переменных, выход третьего элемента 2И-НЕ является пятым выходом блока подключения переменных, выход пятого инвертора является шестым выходом блока подключения переменных, выход пятого инвертора также подключен к затворам второго, четвертого, седьмого и восьмого транзисторов, второй вход блока подключения переменных подключен к затворам первого и третьего транзисторов, ко входу пятого инвертора и затворам пятого и шестого транзисторов, истоки которых подключены к первому входу блока подключения переменных, сток пятого транзистора подключен к первому входу третьего элемента 2И-НЕ и стоку седьмого транзистора, сток шестого транзистора подключен ко второму входу третьего элемента 2И-НЕ и стоку восьмого транзистора, стоки первого и второго транзисторов объединены и подключены ко входу второго инвертора, стоки третьего и четвертого транзисторов объединены и подключены ко входу третьего инвертора,

блок вычисления логической функции дополнительно содержит группу 2n транзисторов реализации спейсера, транзистор отключения спейсера, первый вход, второй вход,

каждый нечётный транзистор группы 2n транзисторов реализации спейсера подключен к соответствующему из n входов инверсий переменных,

каждый чётный транзистор группы 2n транзисторов реализации спейсера подключен к соответствующему из n входов переменных,

сток первого транзистора группы 2n транзисторов реализации спейсера подключен к истоку транзистора отключения спейсера, сток которого подключен ко входу выходного инвертора, а затвор является входом блока, который подключен к первому входу управления, исток 2n-го транзистора группы 2n транзисторов реализации спейсера подключен к первому входу блока вычисления логической функции.

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2025-01-13—Публикация

2024-07-01—Подача