Изобретение относится к вычислительной технике и может быть использовано для реализации матриц коммутации сигналов в самосинхронных программируемых логических интегральных схемах (ПЛИС).

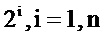

Известно программируемое логическое устройство, содержащее группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по  транзисторов в группе, группу

транзисторов в группе, группу инверторов настройки, выходной инвертор, входы n переменных, группу

инверторов настройки, выходной инвертор, входы n переменных, группу  входов настройки, выход устройства, причём затвор каждого нечётного транзистора i-й группы передающих транзисторов

входов настройки, выход устройства, причём затвор каждого нечётного транзистора i-й группы передающих транзисторов  подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки

подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки  транзисторов n-ой группы подключены к выходам инверторов группы

транзисторов n-ой группы подключены к выходам инверторов группы  инверторов настройки, входы которых являются группой

инверторов настройки, входы которых являются группой  входов настройки, стоки чётных и нечётных транзисторов n-ой группы объединены и подключены к истокам соответствующих

входов настройки, стоки чётных и нечётных транзисторов n-ой группы объединены и подключены к истокам соответствующих  транзисторов n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих

транзисторов n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2 ой группы и так далее, стоки двух последних транзисторов 1 ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. – 2010. – №11. С. 56-62 Рис.9,12 [Электронный ресурс]. – URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 23.02.22 г).

транзисторов n-2 ой группы и так далее, стоки двух последних транзисторов 1 ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. – 2010. – №11. С. 56-62 Рис.9,12 [Электронный ресурс]. – URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 23.02.22 г).

Недостатком известного устройства является невозможность использования его в самосинхронных ПЛИС.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее

блок вычисления логической функции,  входов настройки, n входов переменных, информационный выход, причём

входов настройки, n входов переменных, информационный выход, причём  входов настройки подключены к

входов настройки подключены к  входам настройки блока вычисления логической функции, n входов переменных подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, блок вычисления двойственной логической функции, элемент ИЛИ-НЕ,

входам настройки блока вычисления логической функции, n входов переменных подключены к n входам переменных блока вычисления логической функции, информационный выход блока вычисления логической функции подключен к информационному выходу устройства, блок вычисления двойственной логической функции, элемент ИЛИ-НЕ,  входов инверсной настройки, n входов инверсий переменных, инверсный информационный выход, выход индикации,

входов инверсной настройки, n входов инверсий переменных, инверсный информационный выход, выход индикации,

блок вычисления логической функции содержит выходной инвертор, n групп передающих транзисторов 1.2.i (n - число входных переменных) по  транзисторов в группе, группу

транзисторов в группе, группу инверторов настройки, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных, истоки

инверторов настройки, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу n входов переменных, истоки  транзисторов n-ой группы подключены к выходам инверторов группы

транзисторов n-ой группы подключены к выходам инверторов группы  инверторов настройки, входы которых являются группой

инверторов настройки, входы которых являются группой  входов настройки, стоки чётных и нечётных транзисторов n-ой группы объединены и подключены к истокам соответствующих

входов настройки, стоки чётных и нечётных транзисторов n-ой группы объединены и подключены к истокам соответствующих  транзисторов n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих

транзисторов n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2 ой группы и так далее, стоки двух последних транзисторов 1 ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, причём

транзисторов n-2 ой группы и так далее, стоки двух последних транзисторов 1 ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, причём  входов инверсной настройки устройства подключены к

входов инверсной настройки устройства подключены к  входам настройки блока вычисления двойственной логической функции,

входам настройки блока вычисления двойственной логической функции,

n входов переменных подключены к n входам переменных блока вычисления двойственной логической функции,

n входов инверсий переменных подключены к n входам инверсий переменных блока вычисления двойственной логической функции и блока вычисления логической функции,

информационный выход блока вычисления логической функции подключен к первому входу элемента ИЛИ-НЕ, информационный выход блока вычисления двойственной логической функции является инверсным информационным выходом устройства и подключен ко второму входу элемента ИЛИ-НЕ, выход которого является выходом индикации устройства.

причём в блоки вычисления логической функции и двойственной логической функции введены: группа 2n транзисторов инверсной проводимости, дополнительный инвертор, вход подключения шины «Ноль вольт», каждый нечётный транзистор группы 2n транзисторов инверсной проводимости которой подключен к соответствующему входу n входов инверсий переменных, а каждый чётный транзистор которой подключен к соответствующему входу n входов переменных, сток первого транзистора группы 2n транзисторов инверсной проводимости подключен к выходному инвертору блока, исток первого транзистора группы 2n транзисторов инверсной проводимости подключен к стоку второго транзистора группы 2n транзисторов инверсной проводимости, исток которого подключен к стоку третьего транзистора группы 2n транзисторов инверсной проводимости и так далее, исток 2n транзистора группы 2n транзисторов инверсной проводимости подключен к выходу дополнительного инвертора, вход которого подключен к шине «Ноль вольт», затвор каждого нечётного транзистора i-й группы передающих транзисторов  блоков вычисления логической функции и двойственной логической функции подключен к i-му входу n входов инверсий переменных (патент РФ № 2 601145 от 27.10.2016, кл. G11С17/00). Данное устройство принято за прототип.

блоков вычисления логической функции и двойственной логической функции подключен к i-му входу n входов инверсий переменных (патент РФ № 2 601145 от 27.10.2016, кл. G11С17/00). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения: содержит n входов настройки, n входов переменных, n входов переменных двойственного канала, группу n передающих транзисторов, группу n передающих транзисторов двойственного канала, группу n инверторов настройки, n входов настройки подключены к соответствующим инверторам группы n инверторов настройки.

Недостатком известного устройства, принятого за прототип, являются высокие аппаратурные затраты при реализации коммутации самосинхронных сигналов и невозможность коммутации сигнала с одного из n входов на один из m выходов. Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на самосинхронную реализацию логических функций в совершенной дизъюнктивной нормальной форме с использованием входного вектора переменных в позиционном двоичном коде. Это приводит к тому, что реализация самосинхронной коммутации двоичных сигналов при подаче их на входы настройки, когда требуемый сигнал задается кодом настройки, подаваемым на входы переменных, требует значительного количества передающих транзисторов. Кроме того, прототип имеет всего один парафазный выход, что делает невозможным коммутацию требуемого сигнала с одного из n входов на один из m выходов.

Задачей изобретения является снижение аппаратурных затрат на реализацию коммутации самосинхронных сигналов с обеспечением возможности коммутации требуемого сигнала с одного из n входов на один из m выходов.

Поставленная задача была решена за счет того, что в заявляемом устройстве, содержащем n входов настройки, n входов переменных, n входов переменных двойственного канала, группу n передающих транзисторов, группу n передающих транзисторов двойственного канала, группу n инверторов настройки, причём n входов настройки подключены к соответствующим инверторам группы n инверторов настройки, согласно изобретению дополнительно введены вторая группа m входов настройки, вторая группа m инверторов настройки, вторая группа m передающих транзисторов, вторая группа m передающих транзисторов двойственного канала, третья группа m передающих транзисторов подключения к индикатору, третья группа m передающих транзисторов подключения двойственного канала к индикатору,

первый элемент 2И-НЕ, второй элемент 2И-НЕ, первый элемент 2И, второй элемент 2И, трехвходовой гистерезисный триггер, группу m выходов, группу m двойственных выходов, выход подачи сигнала завершения переходного процесса для последующего устройства,

вход получения сигнала завершения переходного процесса от предыдущего устройства, либо внешнего сигнала сброса,

выходы инверторов группы n инверторов настройки подключены к затворам соответствующих транзисторов группы n передающих транзисторов и группы n передающих транзисторов двойственного канала, истоки которых подключены к соответствующим входам n входов переменных и n входов переменных двойственного канала,

а стоки передающих транзисторов группы n передающих транзисторов объединены и подключены к первому входу первого элемента 2И-НЕ,

стоки передающих транзисторов группы n передающих транзисторов двойственного канала объединены и подключены к первому входу второго элемента 2И-НЕ,

вторые входы первого элемента 2И-НЕ и второго элемента 2И-НЕ подключены к выходу гистерезисного триггера,

выход первого элемента 2И-НЕ подключен к первому входу первого элемента 2И, выход второго элемента 2И-НЕ подключен ко второму входу первого элемента 2И,

выход первого элемента 2И подключен к первому входу гистерезисного триггера,

кроме этого выход первого элемента 2И-НЕ подключен к объединенным истокам второй группы m передающих транзисторов, стоки которых являются группой m выходов устройства, подключенных также к истокам третьей группы m передающих транзисторов подключения к индикатору,

выход второго элемента 2И-НЕ также подключен к объединенным истокам второй группы m передающих транзисторов двойственного канала, стоки которых являются группой m двойственных выходов и также подключены к истокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору,

стоки третьей группы m передающих транзисторов подключения к индикатору объединены и подключены к первому входу второго элемента 2И, второй вход которого подключен к объединенным стокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору,

выход второго элемента 2И подключен ко второму входу гистерезисного триггера,

входы второй группы m инверторов настройки подключены ко второй группе m входов настройки, а выходы подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов и второй группы m передающих транзисторов двойственного канала, к затворам третьей группы m передающих транзисторов подключения к индикатору и затворам третьей группы m передающих транзисторов подключения двойственного канала к индикатору,

третий вход гистерезисного триггера подключен ко входу получения сигнала завершения переходного процесса от предыдущего устройства, , либо внешнего сигнала сброса

кроме этого выход гистерезисного триггера подключен к выходу подачи сигнала завершения переходного процесса для последующего устройства.

Признаки заявляемого технического решения, отличительные от прототипа: содержит вторую группу m входов настройки, вторую группу m инверторов настройки, вторую группу m передающих транзисторов, вторую группу m передающих транзисторов двойственного канала, третью группу m передающих транзисторов подключения к индикатору, третью группу m передающих транзисторов подключения двойственного канала к индикатору, первый элемент 2И-НЕ, второй элемент 2И-НЕ, первый элемент 2И, второй элемент 2И, трехвходовой гистерезисный триггер, группу m выходов, группу m двойственных выходов, а также новые связи между элементами устройства.

Отличительные признаки в сочетании с известными позволяют обеспечить снижение аппаратурных затрат на реализацию коммутации самосинхронных сигналов и коммутацию требуемого сигнала с одного из n входов на один из m выходов.

Введение второй группы m входов настройки позволяет настраивать устройство на самосинхронную коммутацию сигнала на один из m выбранных выходов.

Введение второй группы m инверторов настройки позволяет обеспечить требуемый логический уровень сигнала настройки, поступающий из внешнего оборудования.

Введение второй группы m передающих транзисторов позволяет реализовать подключение сигнала на один из m выходов основного канала при инверсном унитарном кодировании сигналов настройки.

Введение второй группы m передающих транзисторов двойственного канала позволяет реализовать подключение сигнала на один из m выходов двойственного канала при инверсном унитарном кодировании сигналов настройки.

Введение группы m выходов позволяет передавать коммутируемый сигнал с основного канала на внешнее оборудование.

Введение группы m двойственных выходов позволяет передавать коммутируемый сигнал с двойственного канала на внешнее оборудование.

Введение третьей группы m передающих транзисторов подключения к индикатору позволяет организовать подключение выбранного сигнала основного канала к индикатору.

Введение третьей группы m передающих транзисторов подключения к индикатору позволяет организовать подключение выбранного сигнала двойственного канала к индикатору.

Введение второго элемента 2И позволяет реализовать двухфазную дисциплину самосинхронизации путем управления вторым входом гистерезисного триггера.

Введение первого элемента 2И-НЕ позволяет реализовать фазу спейсера по основному каналу коммутации.

Введение второго элемента 2И-НЕ позволяет реализовать фазу спейсера по двойственному каналу коммутации.

Введение первого элемента 2И позволяет реализовать двухфазную дисциплину самосинхронизации путем управления первым входом гистерезисного триггера.

Введение трех входового гистерезисного триггера позволяет фиксировать завершение переходного процесса по основному и двойственному каналам, по 2n входам переменных и в самом себе для обеспечения самосинхронной коммутации сигналов с одного из n входов на один из m выходов, а также фиксировать состояние переходного процесса в предыдущем самосинхронном устройстве и передавать состояние переходного процесса следующему самоснхронному устройству.

Введение выхода подачи сигнала завершения переходного процесса для последующего устройства позволяет информировать следующее аналогичное устройство путем отображения фазы, в которой находится предлагаемое устройство.

Введение входа получения сигнала завершения переходного процесса от предыдущего устройства, либо внешнего сигнала сброса, предназначено для управления Г–триггером путем приема сигнала сброса, либо сигнала, указывающего, в какой состоянии находится предыдущее аналогичное устройство и, соответственно, фазу на входах n переменных и n входов переменных двойственного канала.

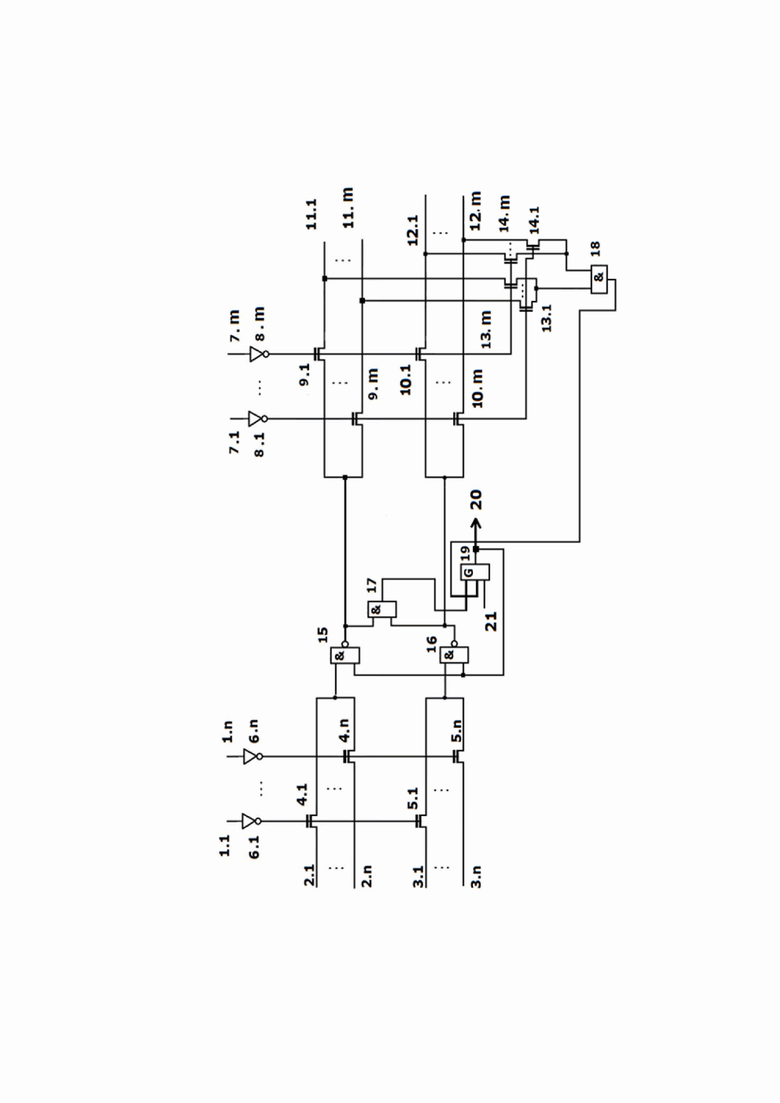

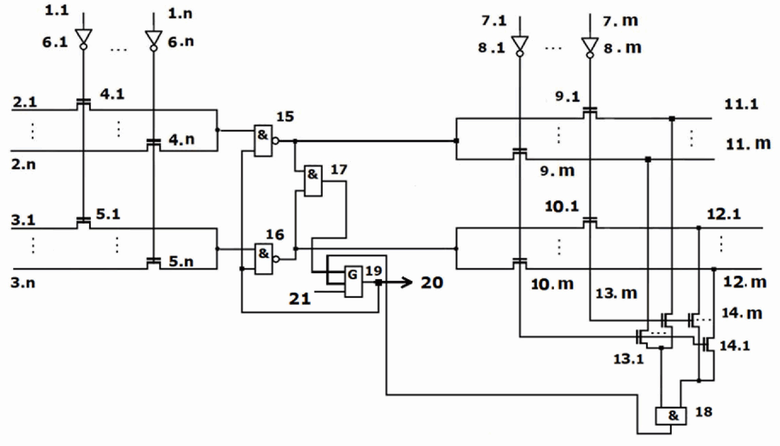

На фиг. изображена схема электрическая принципиальная программируемого логического устройства для самосинхронных схем.

Программируемое логическое устройство содержит:

n входов настройки 1 (1.1,…1.n), n входов переменных 2 (2.1,…2.n), n входов переменных двойственного канала 3 (3.1,…3.n), группу n передающих транзисторов 4 (4.1,…4.n), группу n передающих транзисторов двойственного канала 5 (5.1,…5.n), группу n инверторов настройки 6 (6.1,…6.n);

вторую группу m входов настройки 7 (7.1,…7. m) вторую группу m инверторов настройки 8 (8.1,…8.m), вторую группу m передающих транзисторов 9 (9.1,…9.m), вторую группу m передающих транзисторов двойственного канала 10 (10.1,…10.m), группу m выходов 11 (11.1,…11.m), группу m двойственных выходов 12 (12.1,…12.m);

третью группу m передающих транзисторов подключения к индикатору 13 (13.1,…13.m), третью группу m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.m);

первый элемент 2И-НЕ 15, второй элемент 2И-НЕ 16, первый элемент 2И 17, второй элемент 2И18, трех входовой гистерезисный триггер 19.

Входы группы n инверторов настройки 6 (6.1,…6.n) подключены к n входам настройки 1 (1.1,…1.n), а выходы подключены к затворам соответствующих транзисторов группы n передающих транзисторов 4 (4.1,…4.n) и группы n передающих транзисторов двойственного канала 5 (5.1,…5.n), истоки которых подключены к соответствующим входам группы n входов переменных 2 (2.1,…2.n) и n входов переменных двойственного канала 3 (3.1,…3.n), а стоки передающих транзисторов группы n передающих транзисторов 4 (4.1,…4.n) объединены и подключены к первому входу первого элемента 2И-НЕ 15. Стоки передающих транзисторов группы n передающих транзисторов двойственного канала 5 (5.1,…5.n) объединены и подключены к первому входу второго элемента 2И-НЕ 16. Вторые входы первого элемента 2И-НЕ 15 и второго элемента 2И-НЕ16 подключены к выходу гистерезисного триггера 19. Выход первого элемента 2И-НЕ 15 подключен к первому входу первого элемента 2И 17, выход второго элемента 2И-НЕ 16 подключен ко второму входу первого элемента 2И 17. Выход первого элемента 2И 17 подключен к первому входу гистерезисного триггера 19, второй вход которого подключен к выходу второго элемента 2И 18. Третий вход гистерезисного триггера 19 подключен ко входу 20 получения сигнала завершения переходного процесса от предыдущего устройства, либо сигнала внешнего сброса.

Выход первого элемента 2И-НЕ 15 также подключен к объединенным истокам второй группы m передающих транзисторов, 9 (9.1,…9.m) стоки которых подключены к группе m выходов 11 (11.1,…11.m) устройства, а также подключены к истокам соответствующей третьей группе m передающих транзисторов подключения к индикатору 13 (13.1,…13.m).

Выход второго элемента 2И-НЕ 16 также подключен к объединенным истокам второй группы m передающих транзисторов двойственного канала 10 (10.1,…10.m), выходы которых являются группой m двойственных выходов устройства 12 (12.1,…12.m), а также подключены к истокам соответствующей третьей группе m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.m).

Стоки m передающих транзисторов подключения к индикатору 13 (13.1,…13.m) объединены и подключены к первому входу второго элемента 2И 18, второй вход которого подключен к объединенным стокам m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.m).

Входы второй группы m инверторов настройки 8 (8.1,…8.m) подключены ко второй группе m входов настройки 7 (7.1,…7.m), а выходы подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов 9 (9.1,…9.m), второй группы m передающих транзисторов двойственного канала 10 (10.1,…10.m), а также подключены к затворам соответствующей третьей группы m передающих транзисторов подключения к индикатору 13 (13.1,…13.m) и к затворам m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.m).

Гистерезисный триггер 19 предназначен для управления элементами И 15, 16 с учетом состояний элементов первого элемента И 17 и второго элемента 18, приема сигнала завершения переходного процесса от предыдущего устройства по входу 20, а также для выдачи сигнала завершения переходного процесса на выход 21.

Выход 21 предназначен для подключения следующего самосинхронного устройства и управления элементами И 15, 16.

Вход 20 получения сигнала завершения переходного процесса от предыдущего устройства, либо сигнала внешнего сброса, если устройство одно.

Программируемое логическое устройство для самосинхронных схем работает в следующих режимах: 1) Программирования; 2) Самосинхронной коммутации требуемого сигнала с одного из n входов на один из m выходов.

1) Программирование.

В этом режиме устройство работает аналогично прототипу.

При этом с помощью внешних по отношению к устройству технических средств на n входах настройки 1 (1.1,…1.n) устанавливается инверсный унитарный код (только один i-ый из n входов равен нулю) требуемого i-го входа переменных 2 (2.1,…2.n) и i-го входа переменных 3 (3.1,…3.n) двойственного канала. Поэтому на выходах инверторов из группы n инверторов настройки 6 (6.1,…6.n) формируется унитарный код (только один i-ый из n входов равен единице) и активируются затворы i-х передающих транзисторов 4.i в группе n передающих транзисторов 4 (4.1,…4.n) и 5.i в группе n передающих транзисторов двойственного канала 5 (5.1,…5.n). Таким образом выбирается парафазный i-ый сигнал входа устройства.

Аналогично выбирается парафазный j-ый сигнал входа устройства путем установления с помощью внешних по отношению к устройству технических средств на m входах второй группы m входов настройки 7 (7.1,…7.m), устанавливается инверсный унитарный код (только один j-ый из m входов равен нулю) требуемого j-го выхода 11.j группы m выходов 11 (11.1,…11.m) и 12.j группы m двойственных выходов 12 (12.1,…12.m).

Поэтому на выходах инверторов из группы m инверторов второй группы m инверторов настройки 8 (8.1,…8.m), формируется унитарный код (только один j-ый из m входов равен единице) и активируются затворы j-х передающих транзисторов 9.j второй группы m передающих транзисторов9 (9.1,…9.m) и 10.j второй группы m передающих транзисторов двойственного канала 10 (10.1,…10.m).

Кроме того, активируются затворы j-х передающих транзисторов 13.j в третьей группе m передающих транзисторов подключения к индикатору 13 (13.1,…13.m) и 14.j третьей группы m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.m), подготавливая его работу в режиме самосинхронной коммутации требуемого сигнала с одного из n входов на один из m выходов. Пример настройки для i=1; j=4, n=m=4 приведен в таблице

Таблица

Настройка устройства для реализации коммутации первого входного сигнала из четырёх сигналов к четвертому выходу из четырёх выходов

2) Самосинхронная коммутация требуемого сигнала с одного из n входов на один из m выходов.

В этом режиме устройство может работать одно, либо в составе группы аналогичных устройств.

Для самосинхронной коммутации на входы 2.i, 3.i поступает парафазный сигнал (01 или 10), который надо коммутировать на выходы 11.j, 12.j. Это выполняется в соответствие с двухфазной дисциплиной функционирования.

2.1. Фаза гашения.

В фазе гашения гистерезисный триггер 19 учитывает сигнал со входа 20 и находится в нулевом состоянии, поэтому выходы первого элемента 2И-НЕ 17, второго элемент 2И-НЕ 18, на вторых входах которых установлен нулевой уровень, находятся в состоянии единицы. Поэтому на выходе первого элемента 2И 17 также единица. Единичные сигналы с выходов первого элемента 2И-НЕ 15, второго элемента 2И-НЕ проходят через активированные по своим затворам j-е передающие транзисторы 9.j, 10.j, 13.j, 14.j и устанавливают на выходах 11.j, 12.j и обоих входах второго элемента 2И 18 логические единицы. На выход 21 также выдается сигнал единицы, который передается следующему устройству.

2.2. Рабочая фаза.

Получив сигнал завершения фазы гашения по выходу индикатора 18, на выходе которого устанавливается единица, гистерезисный триггер 19, учитывая сигнал со входа 20, также активируемый единицей на своем первом входе, устанавливается в состояние единицы. Поэтому, через передающие транзисторы 4.i, 5.i, через первый 2И-НЕ 15 и второй элемент 2И-НЕ 16, на вторые входы которых теперь поступает единица, парафазный сигнал предаётся дальше и проходит через передающие транзисторы 9.j, 10.j и поступает на соответствующие выходы 11.j, 12.j и далее – на внешнее оборудование, в качестве которого, например, может выступать программируемое устройство – прототип. В результате этого на два входа индикатора 6 поступают взаимно инверсные сигналы, в связи с чем его выход переходит в состояние нуля, а также обнуляется и выход первого элемента 2И 17. Поэтому рабочая фаза заканчивается и гистерезисный триггер 19 переходит в состояние нуля. На выход 21 также выдается сигнал нуля, который передается следующему устройству.

Далее снова может следовать фаза гашения, установка нового значения входов 2.i, 3.i далее очередная рабочая фаза и т.д.

При необходимости возможна перенастройка устройства для коммутации других сигналов.

Таким образом, в отличие от прототипа, устройство может быть использовано для самосинхронной коммутации требуемого сигнала с одного из n входов на один из m выходов.

Оценка технико-экономической эффективности

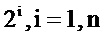

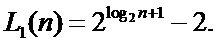

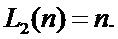

Оценим количество передающих транзисторов одного канала прототипа, необходимых для коммутации одного из n входов на выход:

В предлагаемом устройстве это количество оценивается как

Так, для коммутации восьми сигналов на один выход необходимо по 14 транзисторов для каждого из двух каналов прототипа на n =3, а у предлагаемого устройства необходимо по 8 передающих транзисторов групп 4 и 5.

Для коммутации шестнадцати сигналов на один выход необходимо по 32 транзистора для каждого из двух каналов прототипа на n = 4, а у предлагаемого устройства необходимо по 16 передающих транзисторов групп 4 и 5.

При этом временная задержка у предлагаемого устройства равна задержке одного транзистора, не зависимо от n, а у прототипа равна  , кроме того, в предлагаемом устройстве самосинхронная коммутация из n в один дополнена коммутацией из одного в m (группы передающих транзисторов 9 и 10), что в прототипе невозможно.

, кроме того, в предлагаемом устройстве самосинхронная коммутация из n в один дополнена коммутацией из одного в m (группы передающих транзисторов 9 и 10), что в прототипе невозможно.

Достижение технического результата изобретения подтверждается приведёнными оценками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832937C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| Г-ТРИГГЕР | 2007 |

|

RU2371842C2 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2811404C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в снижении аппаратурных затрат на реализацию коммутации самосинхронных сигналов с обеспечением возможности коммутации требуемого сигнала. Указанный технический результат достигается за счёт введения в программируемое логическое устройство второй группы m входов настройки, второй группы m инверторов настройки, второй группы m передающих транзисторов, второй группы m передающих транзисторов двойственного канала, третьей группы m передающих транзисторов подключения к индикатору, третьей группы m передающих транзисторов подключения двойственного канала к индикатору, первого элемента 2И-НЕ, второго элемента 2И-НЕ, первого элемента 2И, второго элемента 2И, трехвходового гистерезисного триггера, группы m выходов, группы m двойственных выходов. 1 табл., 1 ил.

Программируемое логическое устройство содержит n входов настройки, n входов переменных, n входов переменных двойственного канала, группу n передающих транзисторов, группу n передающих транзисторов двойственного канала, группу n инверторов настройки, причём n входов настройки подключены к соответствующим инверторам группы n инверторов настройки, отличающееся тем, что дополнительно введены вторая группа m входов настройки, вторая группа m инверторов настройки, вторая группа m передающих транзисторов, вторая группа m передающих транзисторов двойственного канала, третья группа m передающих транзисторов подключения к индикатору, третья группа m передающих транзисторов подключения двойственного канала к индикатору, первый элемент 2И-НЕ, второй элемент 2И-НЕ, первый элемент 2И, второй элемент 2И, трехвходовой гистерезисный триггер, группа m выходов, группа m двойственных выходов, вход получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса, выход подачи сигнала завершения переходного процесса для последующего устройства, выходы инверторов группы n инверторов настройки подключены к затворам соответствующих транзисторов группы n передающих транзисторов и группы n передающих транзисторов двойственного канала, истоки которых подключены к соответствующим входам группы n входов переменных и n входов переменных двойственного канала, а стоки передающих транзисторов группы n передающих транзисторов объединены и подключены к первому входу первого элемента 2И-НЕ, стоки передающих транзисторов группы n передающих транзисторов двойственного канала объединены и подключены к первому входу второго элемента 2И-НЕ, вторые входы первого элемента 2И-НЕ и второго элемента 2И-НЕ подключены к выходу гистерезисного триггера, выход первого элемента 2И-НЕ подключен к первому входу первого элемента 2И, выход второго элемента 2И-НЕ подключен ко второму входу первого элемента 2И, выход первого элемента 2И подключен к первому входу гистерезисного триггера, выход первого элемента 2И-НЕ также подключен к объединенным истокам второй группы m передающих транзисторов, стоки которых являются группой m выходов устройства, выход второго элемента 2И-НЕ также подключен к объединенным истокам второй группы m передающих транзисторов двойственного канала, стоки которых являются группой m двойственных выходов, входы второй группы m инверторов настройки подключены ко второй группе m входов настройки, а выходы подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов и второй группы m передающих транзисторов двойственного канала, к затворам третьей группы m передающих транзисторов подключения к индикатору и затворам третьей группы m передающих транзисторов подключения двойственного канала к индикатору, к истокам третьей группы m передающих транзисторов подключения к индикатору подключена группа m выходов устройства, к истокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору подключена группа m двойственных выходов устройства, стоки третьей группы m передающих транзисторов подключения к индикатору объединены и подключены к первому входу второго элемента 2И, второй вход которого подключен к объединенным стокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору, выход второго элемента 2И подключен ко второму входу гистерезисного триггера, третий вход гистерезисного триггера подключен ко входу получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса, кроме этого выход гистерезисного триггера подключен к выходу подачи сигнала завершения переходного процесса для последующего устройства.

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2016 |

|

RU2637462C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2023-10-23—Публикация

2023-07-28—Подача