Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов датчиков с высоким внутренним сопротивлением, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях, широкополосных и избирательных усилителях, фильтрах и т.п.).

В современной радиоэлектронике находят применение каскодные дифференциальные усилители (ДУ) на основе входных параллельно-балансных каскадов, нагрузкой которых являются эмиттерно-базовые р-n переходы биполярных транзисторов. Такие ДУ являются основой многих широкополосных усилителей, фазорасщепителей, аналоговых перемножителей напряжения, удвоителей частоты и т.п. [1-13].

Ближайшим прототипом заявляемого устройства фиг.1 является ДУ, представленный в патентной заявке США №2002/0053935. Он содержит входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 токовые выходы, связанные с первым 6 и вторым 7 двухполюсниками нагрузки, имеющими общий узел.

Существенный недостаток известного устройства состоит в том, что он имеет сравнительно небольшое входное сопротивление для дифференциального сигнала, существенно зависящее от коэффициента усиления по току базы (β) входных транзисторов VT1, VT2 и статического режима (I0) их общей эмиттерной цепи:

где  - сопротивления эмиттерных переходов входных транзисторов каскада VT1 и VT2;

- сопротивления эмиттерных переходов входных транзисторов каскада VT1 и VT2;

φт≈26 мВ - температурный потенциал;

Iэ.р.=0,5I0 - эмиттерный ток входных транзисторов.

Для повышения Rвх приходится выбирать микрорежим для входных транзисторов ДУ. Однако при этом деградирует коэффициент усиления по напряжению ДУ:

Таким образом, обобщенный показатель качества ДУ - произведение KyRвх=Q, не зависит от статического режима и может быть улучшен только ценой увеличения β транзисторов и Rн.экв.:

Основная цель предлагаемого изобретения состоит в повышении входного сопротивления Rвх без ухудшения Ку и токопотребления ДУ. В целом это позволяет обеспечить повышение обобщенного показателя качества Q. Дополнительная цель - в уменьшении статических входных токов ДУ.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 токовые выходы, связанные с первым 6 и вторым 7 двухполюсниками нагрузки, имеющими общий узел, предусмотрены новые элементы и связи - в схему введены первый 8 дополнительный транзистор, эмиттер которого соединен с общим узлом первого 6 и второго 7 двухполюсников нагрузки, база - подключена ко входу дополнительного токового зеркала 9, выход которого связан со входом 10 дополнительного делителя токов, первый 12 выход дополнительного делителя токов 10 соединен с первым 2 входом входного параллельно-балансного каскада 1, а его второй 13 выход подключен ко второму 3 входу входного параллельно-балансного каскада 1.

На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

В схемах фиг.3 - 6 показаны примеры выполнения делителя тока 11.

На чертеже фиг.7 приведена схема заявляемого устройства в соответствии с П1 и П4 формулы изобретения.

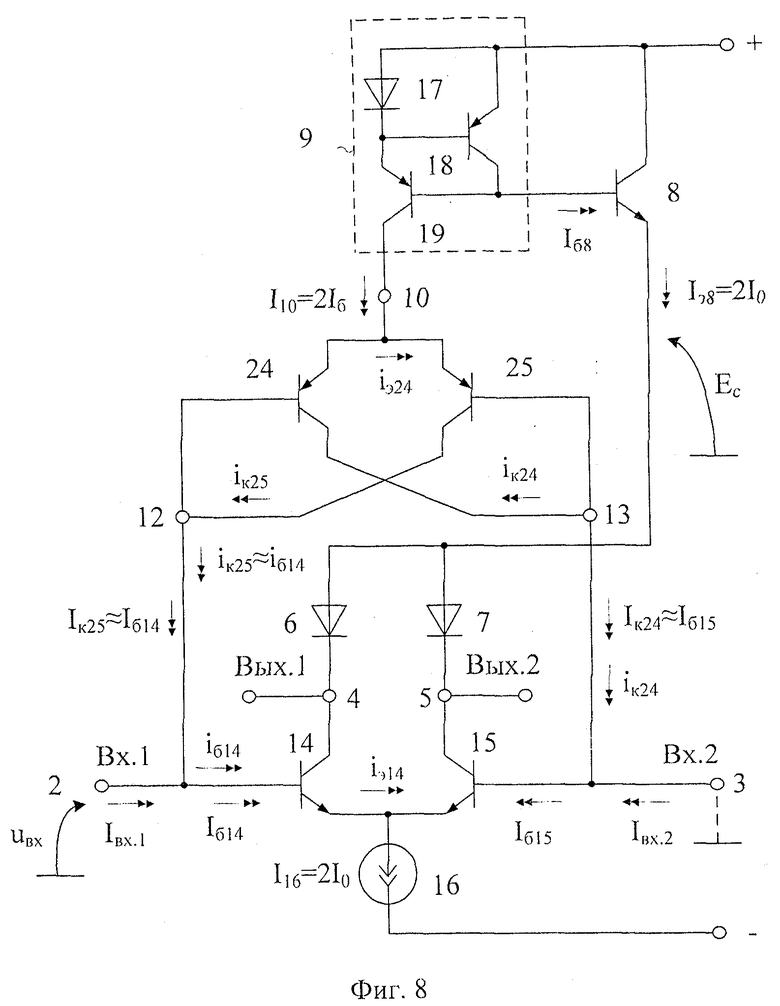

На чертеже фиг.8 показана схема фиг.2 для случая, когда в качестве токового зеркала 9 используется токовое зеркало на транзисторах 18 и 19 и р-n переходе 17. В частном случае делитель тока 10 выполнен здесь по схеме фиг.5.

На чертеже фиг.9 представлена схема ДУ-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на чертеже фиг.10 показана схема заявляемого устройства фиг.8.

Графики фиг.11 характеризуют температурные зависимости входных токов ДУ фиг.9 и ДУ фиг.10, из которых следует, что предлагаемое устройство имеет более чем в 10 раз меньший входной ток.

На графиках фиг.12 представлена частотная зависимость входных сопротивлений заявляемого ДУ и ДУ-прототипа, из которых следует, что предлагаемое устройство имеет более чем в 10 раз большее входное сопротивление.

Дифференциальный усилитель фиг.2 содержит входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 токовые выходы, связанные с первым 6 и вторым 7 двухполюсниками нагрузки, имеющими общий узел. В схему введены первый 8 дополнительный транзистор, эмиттер которого соединен с общим узлом первого 6 и второго 7 двухполюсников нагрузки, база подключена ко входу дополнительного токового зеркала 9, выход которого связан со входом 10 дополнительного делителя токов, первый 12 выход дополнительного делителя токов 10 соединен с первым 2 входом входного параллельно-балансного каскада 1, а его второй 13 выход подключен ко второму 3 входу входного параллельно-балансного каскада 1. Входной каскад 1 реализован на основе транзисторов 14 и 15 и двухполюсника 16. Токовое зеркало 9 реализовано здесь на базе транзисторов 18, 19 и диода 17.

На чертеже фиг.3, в соответствии с П2 формулы изобретения, дополнительный делитель токов 11 содержит первый 20 и второй 21 вспомогательные резисторы, первые выводы которых подключены ко входу 10 дополнительного делителя токов 11, а вторые - к соответствующим выходам 12 и 13 дополнительного делителя токов 11.

На чертеже фиг.4, в соответствии с п.3 формулы изобретения, дополнительный делитель токов 11 содержит первый 22 и второй 23 вспомогательные р-n переходы, первые выводы которых подключены ко входу 10 дополнительного делителя токов 11, а вторые - к соответствующим выходам 12 и 13 дополнительного делителя токов 11.

На чертеже фиг.5, в соответствии с п.4 формулы изобретения, дополнительный делитель токов 11 содержит первый 24 и второй 25 вспомогательные транзисторы, эмиттеры которых подключены ко входу 10 дополнительного делителя тока 11, база первого 24 и коллектор второго 25 вспомогательных транзисторов соединены с первым выходом 12 дополнительного делителя токов 11, а база второго 25 и коллектор первого 24 вспомогательных транзисторов соединены со вторым 13 входом дополнительного делителя токов 11.

На чертеже фиг.6 показан делитель тока на транзисторах 28 и 29 и р-n переходах 26, 22.

Рассмотрим работу ДУ фиг.8.

В статическом режиме статический входной ток ДУ Iвх.1 определяется разностью токов базы Iб14 входного транзистора 14 дифференциального каскада 1 и коллекторного тока транзистора 25:

где β14- коэффициент усиления по току базы транзистора 14. В свою очередь,

где Ki12.9=1 - коэффициент передачи по току токового зеркала 9;

β8 - коэффициент усиления по току базы транзисторов 8;

I10=2I0 - суммарный ток общей эмиттерной цепи транзисторов 14 и 15. Таким образом, статический входной ток ДУ фиг.8

Так как транзисторы 8, 14 и 15 идентичны и имеют одинаковый тип проводимости, то у них β8=β14=β15, поэтому входной ток ДУ существенно уменьшается.

Это первое достоинство предлагаемой схемы.

Второе преимущество предлагаемого устройства состоит в том, что в схеме фиг.8 обеспечивается компенсация не только статических входных токов Iвх.1 и Iвх.2, но и их приращений iвх.1 и iвх.2. Как следствие, входное сопротивление ДУ фиг.8 для переменного тока существенно повышается. Действительно, при увеличении напряжения uвх на входе Вх.1 относительно входа Вх.2 увеличивается ток базы iб14:

где

rэ14, rэ15 - сопротивления эмиттерного перехода входного транзистора 11 каскада 1;

φт=25 мВ - температурный потенциал;

- эмиттерный ток транзисторов 14 и 15.

- эмиттерный ток транзисторов 14 и 15.

Поэтому

С другой стороны, приращения коллекторных токов транзисторов 24 и 25

где rэ25=rэ24 - сопротивления эмиттерных переходов транзисторов 25 и 24.

Причем

где I10=Кi12.9Iб8 - выходной ток токового зеркала 9;

Ki12.9≈1 - коэффициент усиления по току токового зеркала 9.

Таким образом,

где β8 - коэффициент усиления по току базы транзистора 8.

Следовательно, суммарный входной ток ДУ и его входная дифференциальная проводимость

В ДУ-прототипе фиг.1 входная проводимость

Следовательно, в заявляемом ДУ входное сопротивление увеличивается в Ny-раз, где

Наиболее высокая степень компенсации Iвх и  заявляемом устройстве получается при Uкб8≈Uкб14≈Uкб15, где Uкi - напряжение коллектор-база i-го транзистора.

заявляемом устройстве получается при Uкб8≈Uкб14≈Uкб15, где Uкi - напряжение коллектор-база i-го транзистора.

Полученные выше теоретические выводы подтверждаются результатами моделирования известной и предлагаемой схем в среде РSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» (фиг.11, 12). При этом заявляемый ДУ имеет более чем на порядок лучшие значения входного сопротивления. Данный результат обеспечивается без ухудшения других параметров ДУ - крутизны и общего токопотребления. Кроме этого, статические входные токи заявляемого ДУ значительно меньше, чем в схеме ДУ-прототипа (фиг.11).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5256984.

2. Патентная заявка США №2002/0053935.

3. Патент США №5767741.

4. Патент США №5550512.

5. Патент США №4439696.

6. Патент США №5914639.

7. Патент США №5521544.

8. Патент США №4288707.

9. Патент США №5774020.

10. Патент США №6111463 fig.1.

11. Патент США№5610547 fig.19.

12. Патент США №4721920.

13. Патентная заявка США №2004/0032298.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2393628C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2394360C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346388C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ ДИФФЕРЕНЦИАЛЬНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2396699C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402153C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2008 |

|

RU2346387C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411639C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450423C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов датчиков с высоким внутренним сопротивлением, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях, широкополосных и избирательных усилителях, фильтрах и т.п.). Технический результат: повышение входного сопротивления. Дифференциальный усилитель (ДУ) содержит входной параллельно-балансный каскад (1), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) токовые выходы, связанные с первым (6) и вторым (7) двухполюсниками нагрузки, имеющими общий узел. В схему введены первый (8) дополнительный транзистор (Т), эмиттер которого соединен с общим узлом первого (6) и второго (7) двухполюсников нагрузки, база подключена ко входу дополнительного токового зеркала (9), выход которого связан со входом (10) дополнительного делителя токов (11), первый (12) выход дополнительного делителя токов (11) соединен с первым (2) входом входного параллельно-балансного каскада (1), а его второй (13) выход подключен ко второму (3) входу входного параллельно-балансного каскада (1). 3 з.п. ф-лы, 12 ил.

1. Дифференциальный усилитель, содержащий входной параллельно-балансный каскад (1), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) токовые выходы, связанные с первым (6) и вторым (7) двухполюсниками нагрузки, имеющими общий узел, отличающийся тем, что в схему введены первый (8) дополнительный транзистор, эмиттер которого соединен с общим узлом первого (6) и второго (7) двухполюсников нагрузки, база подключена ко входу дополнительного токового зеркала (9), выход которого связан со входом (10) дополнительного делителя токов, первый (12) выход дополнительного делителя токов (10) соединен с первым (2) входом входного параллельно-балансного каскада (1), а его второй (13) выход подключен ко второму (3) входу входного параллельно-балансного каскада (1).

2. Дифференциальный усилитель по п.1, отличающийся тем, что дополнительный делитель токов (11) содержит первый (20) и второй (21) вспомогательные резисторы, первые выводы которых подключены ко входу (10) дополнительного делителя токов (11), а вторые - к соответствующим выходам (12) и (13) дополнительного делителя токов (11).

3. Дифференциальный усилитель по п.1, отличающийся тем, что дополнительный делитель токов (11) содержит первый (22) и второй (23) вспомогательные р-n переходы, первые выводы которых подключены ко входу (10) дополнительного делителя токов (11), а вторые - к соответствующим выходам (12) и (13) дополнительного делителя токов (11).

4. Дифференциальный усилитель по п.1, отличающийся тем, что дополнительный делитель токов (11) содержит первый (24) и второй (25) вспомогательные транзисторы, эмиттеры которых подключены ко входу (10) дополнительного делителя токов (11), база первого (24) и коллектор второго (25) вспомогательных транзисторов соединены с первым выходом (12) дополнительного делителя токов (12), а база второго (25) и коллектор первого (24) вспомогательных транзисторов соединены со вторым (13) входом дополнительного делителя токов (11).

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Дифференциальный усилитель | 1985 |

|

SU1246340A1 |

| EP 0762629 A1, 12.03.1977 | |||

| СИНТАКТИЧЕСКИЕ ПОЛИУРЕТАНОВЫЕ ЭЛАСТОМЕРЫ ДЛЯ ИСПОЛЬЗОВАНИЯ В КАЧЕСТВЕ ИЗОЛЯЦИИ ПРОЛЕГАЮЩИХ ПО ДНУ МОРЯ ТРУБОПРОВОДОВ | 2014 |

|

RU2673340C2 |

Авторы

Даты

2010-08-10—Публикация

2009-03-25—Подача