Область техники

Настоящее раскрытие имеет отношение в целом к способам для выборки команд из памяти, имеющей кэш команд и кэш данных, и, более конкретно, к усовершенствованному подходу к выборке команд, после неудачного обращения к кэшу команд, посредством прямой выборки команды из кэша данных, если команда находится там.

Предшествующий уровень техники

Обычно переносные изделия, типа сотовых телефонов, портативных компьютеров, персональных помощников данных (PDA) или подобных средств, требуют использования процессора, выполняющего программы, такие как программы связи и мультимедиа. Система обработки для таких изделий включает в себя комплекс процессора и памяти для хранения команд и данных. Например, команды и данные могут быть сохранены в иерархической памяти, состоящей из многоуровневых кэшей, включая, например, кэш команд, кэш данных, и системной памяти. Использование отдельного кэша команд и отдельного кэша данных известно как архитектура Гарварда (Harvard). Так как архитектура Гарварда изолирует кэш команды от кэша данных, проблемы могут возникнуть, когда команды сохраняются в кэше данных.

В общей системе обработки с архитектурой Гарварда есть ситуации, которые возникают, когда команды могут быть сохранены в кэше данных. Например, если программа зашифрована или находится в сжатой форме, то она должна быть расшифрована или декомпрессирована до предоставления программе возможности выполняться. Процесс расшифровки/декомпрессии обрабатывает зашифрованную/сжатую программу как данные, чтобы обработать ее, и сохраняет расшифрованные/декомпрессированные команды как данные в кэше данных, например в кэше данных уровня 1, на своем пути к системной памяти. Генерация команд из байтовых кодов Java является другой ситуацией, в которой команды первоначально обрабатываются как данные, которые сохраняются, используя путь данных, включающий в себя кэш данных, к системной памяти. Исходное состояние программы, в которой команды программы обрабатываются как данные, создает проблему когерентности (согласованности) в пределах иерархии памяти, поскольку, по меньшей мере, некоторые части программы могут постоянно находиться в кэше данных до выполнения программы.

Для решения проблемы согласованности в типовом случае применяется программный подход, при котором программа или сегменты программы в кэше данных перемещаются в системную память при программном управлении, кэш команд в типичном случае делается недействительным (инвалидируется) для очистки кэша от любых старых сегментов программы, и команды, включающие программу, затем извлекаются из системной памяти. Перемещение команд из кэша данных в системную память и выборка команд из системной памяти перед выполнением могут потребовать несколько циклов, снижая характеристики процессора из-за непроизводительных затрат времени обработки, которые должны иметь место, чтобы обратиться к командам, первоначально находящимся в кэше данных, прежде чем программа будет выполняться на процессоре.

Сущность изобретения

Настоящее раскрытие, среди его нескольких аспектов, исходит из того, что непроизводительные затраты на обращение с командами в кэше данных могут ограничивать производительность процессора и, возможно, ограничивать качество услуги, которое может быть достигнуто. Настоящее раскрытие также исходит из того, что может быть желательно обратиться к командам, которые находятся в кэше данных.

Кроме того, настоящее раскрытие описывает устройство, способы и машиночитаемый носитель для прямой выборки команды из кэша данных, когда эта команда не была найдена в кэше команд, при неудачном обращении в кэш команд (промахе кэша), и когда определено, что команда находится в кэше данных. Путем выборки команды непосредственно из кэша данных, после неудачного обращения в кэш команд, производительность процессора может быть улучшена.

С этими целями вариант осуществления настоящего изобретения включает в себя способ обнаружения команды в кэше данных, который является отдельным от кэша команд. В таком способе определяется, что попытка выборки команды из кэша команд по адресу выборки команды была безуспешной. Адрес выборки команды преобразуется в адрес выборки данных. Затем делается попытка выборки в кэше данных для команды по преобразованному адресу выборки данных.

Другой вариант осуществления изобретения направлен на процессорный комплекс для выборки команд. Процессорный комплекс может соответственно включать в себя кэш команд, кэш данных и первый селектор. Первый селектор используется, чтобы выбрать адрес выборки команды или адрес выборки данных. Выбранный адрес выборки применяется к кэшу данных, посредством чего команды или данные могут избирательно выбираться из кэша данных.

Более полное понимание принципов настоящего изобретения, раскрытых здесь, а также других признаков, будет обеспечено последующим детальным описанием и иллюстрирующими чертежами.

Краткое описание чертежей

Фиг.1 - блок-схема иллюстративной системы радиосвязи, в которой может использоваться вариант осуществления заявленного изобретения;

Фиг.2 - функциональная блок-схема комплекса процессора и памяти, в котором операция кэша данных адаптирована для эффективных операций памяти по выборке команд в соответствии с вариантом осуществления настоящего изобретения;

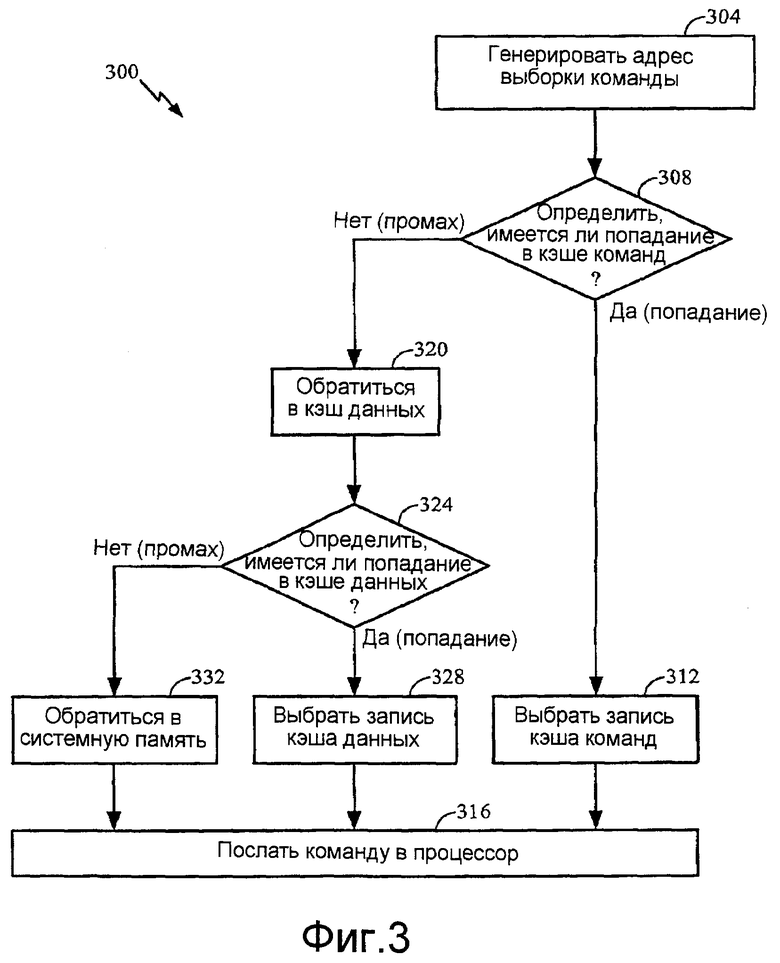

Фиг.3 - блок-схема приведенного для примера способа для выборки команды, сохраненной в кэше данных, чтобы снизить непроизводительные затраты на обработку промахов, ассоциированные с командой, первоначально сохраненной как данные в кэше данных в соответствии с настоящим раскрытием;

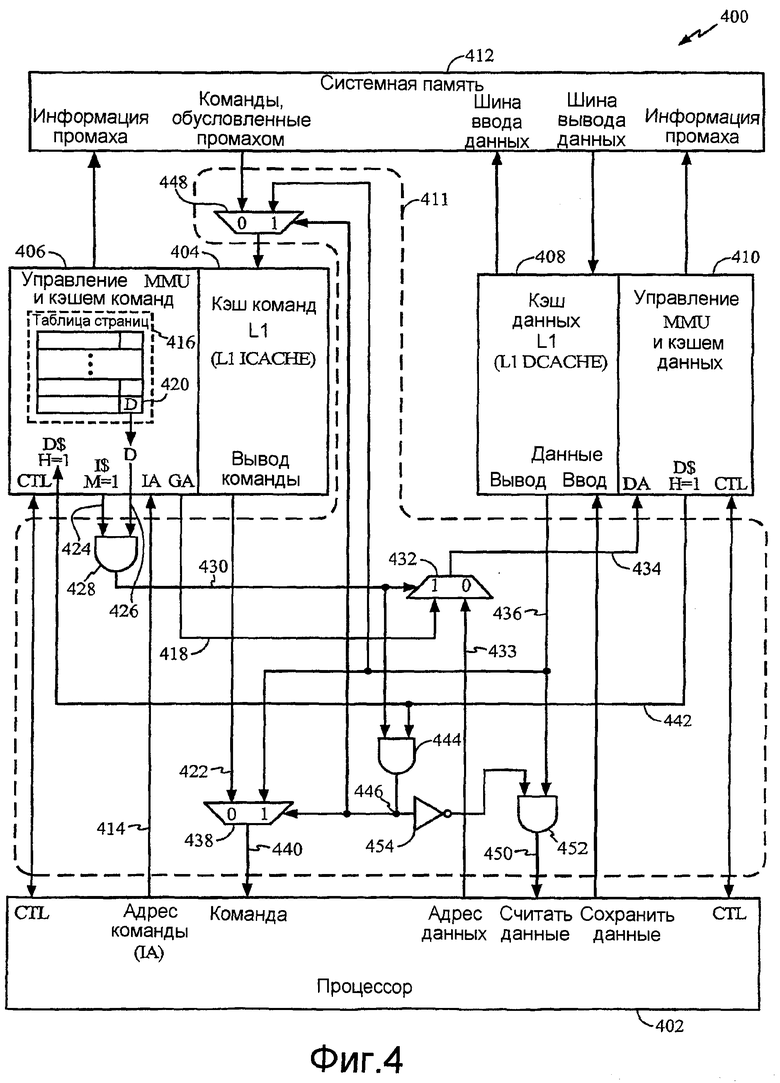

Фиг.4 - функциональная блок-схема комплекса процессора и памяти, который включает в себя таблицу страниц команд, в которой операция кэша данных адаптирована для эффективной выборки команды в соответствии с настоящим раскрытием;

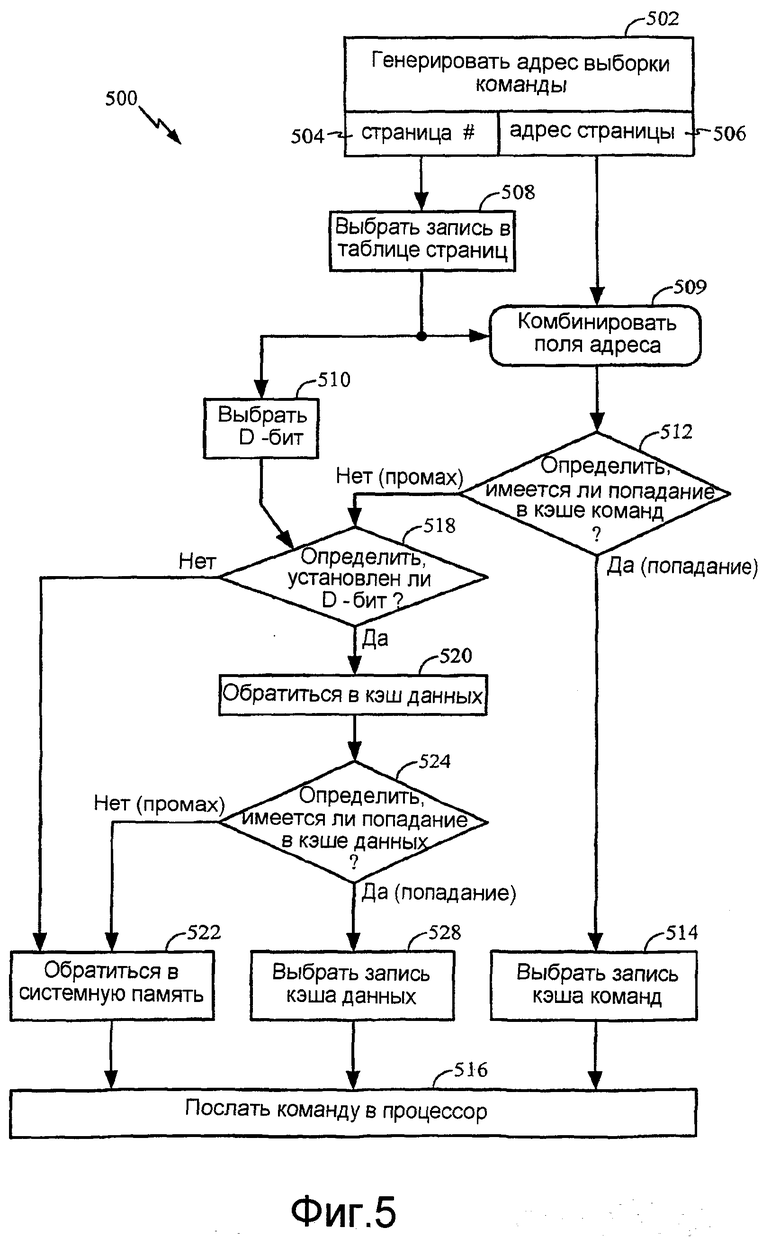

фиг.5 - блок-схема приведенного для примера способа для выборки команды, сохраненной в кэше данных, в соответствии с настоящим раскрытием; и

Фиг.6 - блок-схема приведенного для примера способа для выполнения кода, который сгенерирован как данные и сохранен в кэше данных, в соответствии с настоящим раскрытием.

Детальное описание

Аспекты изобретения в настоящем раскрытии будут проиллюстрированы более полно со ссылкой на иллюстрирующие чертежи, на которых показаны несколько вариантов осуществления. Однако воплощение настоящего изобретения может быть реализовано в различных формах и не должно рассматриваться как ограниченное вариантами осуществления, изложенными здесь. Скорее, эти варианты осуществления предоставлены для того, чтобы настоящее раскрытие было полным и завершенным и полностью передавало объем настоящего раскрытия специалистам в данной области техники.

Должно быть понятно, что настоящее раскрытие может быть воплощено как способы, системы или компьютерные программные продукты. Соответственно, принципы настоящего изобретения, раскрытые здесь, могут принимать форму аппаратного варианта осуществления, программного варианта осуществления или варианта осуществления, объединяющего аспекты программного обеспечения и аппаратных средств. Кроме того, принципы настоящего изобретения, раскрытые здесь, могут принимать форму компьютерного программного продукта на используемом компьютером носителе для хранения данных, воплощающем пригодный для использования компьютером программный код, воплощенный на носителе. Может использоваться любой соответствующий машиночитаемый носитель, включая жесткие диски, CD-ROM (ПЗУ на компакт-диске), оптические запоминающие устройства (ЗУ), флэш-память или магнитные ЗУ.

Компьютерный программный код, который может компилироваться, ассемблироваться и загружаться на процессор, может быть первоначально написан на языке программирования типа C, C++, внутреннего Ассемблера, JAVA (R), Smalltalk, JavaScript (R), Visual Basic (R), TSQL, Perl или на различных других языках программирования в соответствии с идеями настоящего раскрытия. Программный код или машиночитаемый носитель относятся к коду на машинном языке типа объектного кода, формат которого понятен процессору. Программные варианты осуществления раскрытия не зависят от их реализации с использованием конкретного языка программирования. Когда программный код выполняется, создается новая задача, которая определяет операционную среду для программного кода.

Фиг.1 показывает примерную систему 100 радиосвязи, в которой может использоваться вариант осуществления настоящего раскрытия. Для целей иллюстрации, фиг. 1 показывает три удаленных блока 120, 130 и 150 и две базовых станции 140. Понятно, что типичные системы беспроводной связи могут иметь дистанционные блоки и базовые станции. Дистанционные блоки 120, 130 и 150 включают в себя аппаратные компоненты, программные компоненты или оба эти вида компонентов, как представлено компонентами 125A, 125C и 125B, соответственно, которые были адаптированы для воплощения заявленного изобретения, как обсуждено ниже. Фиг. 1 показывает сигналы 180 прямой линии от базовой станции 140 к дистанционным блокам 120, 130 и 150, и сигналы 190 обратной линии от дистанционных блоков 120, 130 и 150 к базовым станциям 140.

На фиг.1 дистанционный блок 120 показан как мобильный телефон, дистанционный блок 130 показан как переносной компьютер, и дистанционный блок 150 показан как дистанционный блок в стационарном местоположении в системе локального беспроводного шлейфа. Например, дистанционные блоки могут быть сотовыми телефонами, портативными блоками систем персональной связи (PCS), портативными блоками данных типа персональных цифровых помощников или блоками данных в стационарном местоположении такими, как оборудование снятия показаний приборов. Хотя фиг.1 иллюстрирует дистанционные блоки согласно принципам раскрытия, раскрытие не ограничено этими примерными проиллюстрированными модулями. Данное раскрытие может соответственно использоваться в любом устройстве, имеющем процессор с кэшем команд, кэшем данных и системной памятью.

Фиг.2 представляет функциональную блок-схему комплекса 200 процессора и памяти, в котором нормальная операция кэша данных адаптирована для более эффективной выборки команд, как описано далее. Комплекс 200 процессора и памяти включает в себя процессор 202, кэш 204 команд уровня 1 (Ll), блок 206 управления кэшем команд Ll, кэш 208 данных Ll, блок 210 управления кэшем данных Ll, секцию 211 управления и системную память 212. Блок 206 управления кэшем команд Ll может включать в себя адресуемую содержанием команды память для согласования тега команды, как может использоваться в модульно-ассоциативном кэше. Секция 211 управления включает в себя элементы 220, 226 и 234 мультиплексирования, вентильные устройства 232 и 238 и инвертор 240. Периферийные устройства, которые могут соединяться с процессорным комплексом, не показаны для ясности обсуждения настоящего раскрытия. Комплекс 200 процессора и памяти может соответственно использоваться в компонентах 125 A-C для выполнения программного кода, который сохранен в системной памяти 212.

Для того чтобы выполнить выборку команды в комплексе 200 процессора и памяти 200, процессор 202 генерирует адрес 214 выборки команды (IA) для желательной команды и посылает адрес выборки команды на блок 206 управления кэшем команд Ll. Блок 206 управления кэшем команд Ll проверяет, присутствует ли команда в кэше 204 команд Ll. Эта проверка выполняется, например, с помощью внутренней памяти с адресацией по содержимому (внутренней ассоциативной памяти) (САМ) в ассоциативном поиске соответствия с введенным адресом выборки команды. Если команда присутствует, то имеет место соответствие, и блок 206 управления кэшем команд Ll указывает, что команда присутствует в кэше 204 команд Ll. Если команда не присутствует, никакое соответствие не будет найдено при ассоциативном поиске контекстно-адресуемой памяти, и блок 206 управления кэшем команд Ll указывает, что команда не присутствует в кэш 204 команд Ll.

Если команда присутствует, то команда в адресе выборки команды выбирается из кэша 204 команд Ll. Команда затем посылается по шине 216 вывода команд через элемент 226 мультиплексирования на процессор 202.

Если команда не присутствует в кэше команд, то сигнал (I$M=1) 218 неудачного обращения в кэш команды устанавливается в активное состояние, указывая, что имел место промах кэша. После обнаружения неудачного обращения в кэш команды комплекс 200 процессора и памяти пытается извлечь желательную команду из кэша 208 данных Ll. С этой целью элемент 220 мультиплексирования запускается сигналом (I$M=1) 218 промаха для выбора адреса 214 выборки команды. Адрес 214 выборки команды проходит затем через элемент 200 мультиплексирования 220 в шину 222 Daddress и посылается в блок 210 управления кэшем данных Ll как адрес выборки данных. Следует отметить, что комплекс 200 процессора и памяти представляет логическое представление системы, поскольку, например, применение адреса 214 выборки команды к шине 222 Daddress может потребовать арбитража или периода ожидания, прежде чем будет получен доступ к шине 222 Daddress. Принятый подход, заключающийся в мультиплексировании адреса 214 выборки команды со сгенерированным процессором адресом 223 данных, может варьироваться в зависимости от конкретного подхода, принятого в структурах кэша команд и кэша данных.

Блок 210 управления кэшем данных Ll проверяет, имеет ли место совпадение (попадание) в кэше 208 данных Ll по введенному адресу выборки команды, посредством внутреннего ассоциативного поиска, например, по введенному адресу выборки команды. Совпадение указывает, что есть данные, присутствующие по введенному адресу выборки команды. Эти данные являются фактически командой, и запись кэша данных извлекается из кэша 208 данных Ll и помещается в шину 224 данных. Чтобы подать данные, извлеченные из кэша 208 данных Ll, как команду на процессор, может соответственно использоваться элемент 226 мультиплексирования. Шина 224 вывода данных выбирается элементом 226 мультиплексирования, помещающим данные, выбранные из кэша данных, в шину 228 команд процессора, когда имеет место промах в кэше команд с последующим совпадением в кэше данных по адресу выборки команды. Возникновение промаха в кэше команд, обозначенного сигналом (I$M=1) 218 промаха в активном состоянии высокого уровня, с последующим совпадением в кэше данных в том же самом адресе выборки команды, обозначенном сигналом (D$H=1) 230 удачного обращения к кэшу (попадания) в активном состоянии высокого уровня, логически представлено схемой И 232. Выход схемы И 232 является сигналом 233 выбора для элемента 226 мультиплексирования 226. Команда, найденная в кэше данных, также мультиплексируется для загрузки в кэш 204 команд элементом 234 мультиплексирования с использованием сигнала 233 выбора, логически обеспечиваемого схемой И 232. В то время как шина 224 данных направляет команду процессору, вход 236 данных считывания процессора деактивируется схемой И 238 с использованием инвертора 240 для обеспечения инверсии сигнала 233 выбора.

Если было определено, что имелся промах в кэше данных по введенному адресу выборки команды, то команда не находится в кэше данных, и команда выбирается из системной памяти 212. Сигнал (D$H=1) 230 попадания также посылается на блок 206 управления кэшем команд Ll, чтобы указать его неактивным состоянием, что имел место промах при попытке отыскать команду в кэше 208 данных. Отметим, что может использоваться другой способ сигнализации, чтобы указать, что имел место промах при попытке отыскать команду в кэше 208 данных. Так как команда не находится ни в кэше 204 команд, ни в кэше 208 данных, то она должна быть извлечена из системной памяти 212. Как только команда получена от системной памяти 212, она посылается процессору 202. Отметим, что пути из системной памяти для подачи команды вследствие неудачного обращения в кэш команд или кэш данных и для подачи данных вследствие неудачного обращения в кэш данных, не показаны, в целях наглядности иллюстрации настоящего раскрытия.

На фиг.3 показана приведенная для примера блок-схема способа 300 для непосредственного выбора команды в кэше данных после неудачного обращения в кэш команд, чтобы минимизировать непроизводительные затраты, обычно связанные с обработкой команды, первоначально сохраненной как данные в кэше данных. Приведенные для примера соотношения между этапами на фиг.3 и элементами на фиг.2 указаны путем описания того, как элементы из комплекса 200 процессора и памяти 200 могут соответственно взаимодействовать, чтобы выполнить этапы способа 300.

Чтобы выполнить выборку команды, адрес выборки команды генерируется на этапе 304. Например, процессор, такой как процессор 202, генерирует адрес выборки команды для желательной команды и посылает адрес 214 выборки команды контроллеру 206 кэша команд Ll. На этапе 308 определяется, имеет ли место удачное обращение в кэш команды или промах. Например, контроллер 206 кэша команд Ll проверяет, присутствует ли команда в кэше 204 команд. Если команда присутствует, ее присутствие указывается как удачное обращение (попадание). Если команда присутствует, способ 300 переходит на этап 312, и команда выбирается по адресу выборки команды. На этапе 316 команда посылается процессору. Например, выбранная команда помещается в шину 216 команд и посылается процессору 202 через элемент 226 мультиплексирования.

Если команда не присутствует в кэше команд, как определено на этапе 308, выдается индикация, что имело место неудачное обращение (промах), и делается попытка выбрать команду из кэша данных на этапе 320. Например, адрес 214 выборки команды посылается через элемент 220 мультиплексирования в качестве адреса 222 выборки данных в кэш 208 данных. На этапе 324 выполняется проверка, например, контроллером 210 кэша данных Ll, чтобы проверить, есть ли действительные данные, существующие по введенному адресу выборки команды. Если есть действительные данные, существующие по введенному адресу выборки команды, то данные по существу представляют собой команду, и запись кэша данных извлекается на этапе 328. На этапе 316 данные, извлеченные из кэша данных, посылаются как команда процессору. Например, выбранные данные по шине 224 вывода данных из кэша 208 данных посылаются через элемент 226 мультиплексирования и вводятся как команда в процессор 202 по шине 228 команды 228.

На этапе 324, если имел место промах в кэше данных по введенному адресу выборки команды, то команда не находится в кэше данных, и на этапе 332 команда извлекается из системной памяти. Например, сигнал D$H=1 230 попадания кэша данных посылается в блок 206 управления кэшем команд Ll, чтобы указать его неактивным состоянием, что произошел промах при попытке отыскать команду в кэше 208 данных. Так как команда не находится ни в кэше 204 команд, ни в кэше 208 данных, то она должна быть извлечена из системной памяти 212. Как только команда получена из системной памяти 212, команда посылается процессору 202, как указано на этапе 316.

На фиг.4 представлена функциональная блок-схема комплекса 400 процессора и памяти, который включает в себя таблицу страниц команд, в которой нормальная операция кэша данных адаптирована к эффективной операции выборки команды в соответствии с настоящим раскрытием. Комплекс 400 процессора и памяти включает в себя процессор 402, кэш 404 команд уровня 1 (Ll), блок 406 управления памятью команд (IMMU) и управления кэшем (IMMU/$Control) 406, кэш 408 данных Ll, блок 410 управления памятью данных (DMMU) и управления кэшем (DMMU/$Control), секцию 411 управления и иерархию 412 памяти. Блок 406 IMMU/$Control может включать в себя, например, процесс трансляции адреса команды из виртуального к физическому. Секция 411 управления включает в себя элементы 432, 438 и 448 мультиплексирования, вентильные устройства 428, 444 и 452 и инвертор 454. Периферийные устройства, которые могут соединиться с процессорным комплексом, не показаны для наглядности иллюстрации настоящего раскрытия. Комплекс 400 процессора и памяти 400 может соответственно использоваться в компонентах 125A-C для выполнения программного кода, который сохранен в системной памяти 412.

Кэш команд может использовать буфер предыстории трансляции (TLB), который содержит таблицу страниц команд, чтобы улучшить характеристику кэша команд. Таблица страниц команд имеет, например, список номеров физических страниц, ассоциированных с номерами виртуальных страниц, и дополнительную информацию, ассоциированную с каждой записью номера страницы. Запись таблицы страниц команды создается, когда страница памяти в диапазоне адресов команд загружается в кэш команд или кэш данных. Загрузка страницы памяти может происходить при диспетчеризации операционной системы (OS). При работе таблица страниц команд проверяется на соответствие с номером виртуальной страницы, введенным в TLB. В то время как TLB, имеющий таблицу страниц команд, описан здесь как часть блока 406 MMU и управления кэшем, понятно, что могут использоваться альтернативные подходы.

Чтобы выбрать команду в комплекс 400 процессора и памяти, процессор 402 генерирует адрес выборки команды (IA) 414 для желательной команды и посылает адрес выборки команды в блок 406 IMMU/$Control. Соответствующая запись в таблице страниц команд, типа таблицы 416 страниц, расположенной в блоке 406 IMMU/$Control, выбирается на основе введенного номера страницы, который является частью IA 414. Адрес команды, основанный на выбранной записи таблицы страниц, объединяется с адресом страницы, также частью IA 414, генерируя адрес команды (GA) 418, который применяется внутренне к кэшу 404 команд Ll. Запись, выбранная из таблицы 416 страниц, включает в себя дополнительную информацию, сохраненную в этой записи. Один из дополнительных битов информации, который может быть сохранен в каждой записи таблицы страниц, является атрибутом проверки кэша данных, обозначен как D-бит 420.

D-бит установлен на "1", когда запись в таблице страниц команд создана ввиду загрузки страницы команд в кэш данных или при генерации команд, которые сохраняются в странице в кэше данных в процессе обработки. D-бит типично устанавливается операционной системой (OS), чтобы указать, что содержание страницы может использоваться как данные и команды. В примерном сценарии, программа, генерирующая данные, которые будут использоваться как команды, вызывает операционную систему, чтобы запросить, что соответствующие страницы будут маркированы путем установки D-бита в ассоциированных записях таблицы страниц. В другом сценарии, программа может также запрашивать страницы из операционной системы, которые уже установлены с установленным D-битом. D-бит не обязательно должен быть явно сброшен. Если программа определяет, что кэш данных может содержать команды, вызывая установку соответствующего D-бита или соответствующих D-битов, то такая спецификация может быть действительной в течение срока службы программы. D-бит или D-биты могут затем быть сброшены, когда таблица страниц используется для другого процесса.

Блок 406 IMMU/$Control проверяет, присутствует ли команда в кэше 404. Если команда присутствует, то это присутствие указывается как успешное обращение (попадание). Если команда присутствует, то команда по адресу выборки команды выбирается из кэша 404. Команда затем посылается по шине 422 вывода команд через элемент мультиплексирования 438 на процессор 402. Если команда не присутствует, то блок 406 IMMU/$Control выдает индикацию, что имело место неудачное обращение (промах), и сигнал (I$M=1) 424 неудачного обращения в кэш команд устанавливается активным, указывая наличие промаха.

После обнаружения промаха в кэше команд вместе с выбранным D-битом, установленным на "1", комплекс 400 процессора и памяти пытается осуществить выборку желательной команды из кэша 408 данных Ll. Эта попытка может быть соответственно реализована, например, использованием выбранного D-бита в логической функции. D-бит 420 из выбранной записи таблицы страниц выводится как сигнал 426 D-бита 426. Сигналы 426 D-бит, например, подвергается логической операции И в схеме И 428, с индикацией промаха (1$M=1) 424. Выходной сигнал 430 схемы И 428 используется затем элементом мультиплексирования 432, чтобы выбрать сгенерированный адрес (GA) 418 команды или адрес 433 данных из процессора 402. Когда выбор сделан, GA 418 проходит через элемент 432 мультиплексирования на шину Daddress (DA) 434 и посылается на блок 410 MMU данных и управления кэшем, чтобы определить, находится ли команда в кэше 408 данных по адресу выборки данных. Следует отметить, что комплекс 400 процессора и памяти представляет логическое представление системы, поскольку, например, применение сгенерированного адреса 418 команды к шине 434 Daddress может потребовать арбитража или периода ожидания, прежде чем будет получен доступ к шине 434 Daddress. Подход, принятый для мультиплексирования сгенерированного адреса 418 команды с адресом 433 данных, сгенерированного процессором, может варьироваться в зависимости от конкретного подхода, принятого в структурах кэша команд и кэша данных.

Кэш данных затем проверяет, присутствуют ли действительные данные по введенному адресу выборки команды. Если имеются действительные данные, существующие по введенному адресу выборки команды, то данные в действительности являются командой, и запись кэша данных извлекается из кэша 408 данных Ll и помещается в шину 436 вывода данных. Для того чтобы ввести запись кэша данных в качестве команды в процессор, используется, например, элемент 438 мультиплексирования. Элемент 438 мультиплексирования запускается для пропускания данных из шины 436 в шину 440 команд процессора, когда имеет место промах в кэше команд, и выбранный D-бит установлен на 1, с последующим попаданием в кэше данных по адресу выборки команды. Появление промаха в кэше команд, указываемого сигналом (T$M=1) 424 промаха в активном состоянии высокого уровня и сигналом 426 D-бита, установленным на 1, за которым следует удачное обращение в кэше данных по сгенерированному адресу команды, указанное сигналом (D$H=1) 442 попадания в активном состоянии высокого уровня, логически представлено схемой И 444. Выходной сигнал схемы И 444 представляет собой сигнал 446 выбора для элемента 438 мультиплексирования. Команда в шине вывода данных также мультиплексируется для загрузки в кэш команд элементом 448 мультиплексирования, использующим сигнал 446 выбора. В то время как шина 436 вывода данных кэша данных Ll направляет команду на процессор 402, шина 436 вывода данных стробируется для переноса на вход 450 считывания данных процессора посредством схемы И 452 с использованием инверсии сигнала 446 выбора, обеспечиваемого инвертором 454.

Если было определено, что имел место промах в кэше данных по введенному адресу выборки команды, команда не находится в кэше данных, и команда извлекается из системной памяти 412. Сигнал (D$H=1) 442 попадания также посылается на блок 406 IMMU/$Control, чтобы указать его неактивным состоянием, что имело место неудачное обращение при попытке отыскания команды в кэше 408 данных. Как только команда получена из системной памяти 412, она посылается на процессор 402. Отметим, что пути из иерархии памяти для подачи команды, вследствие промаха в кэше команд или кэше данных, и для подачи данных, вследствие промаха в кэше данных, не показаны, но любой из широкого разнообразия методов соединения может использоваться в соответствии с используемыми приложением и процессором.

На фиг.5 показана приведенная для примера блок-схема способа 500 для выборки команды в кэше данных после неудачного обращения в кэш команд, и атрибут проверки кэша данных указывает, что кэш данных должен быть проверен на наличие команды. Примерные соотношения между этапами на фиг.5 и элементами на фиг.4 указаны со ссылками на примерные элементы из комплекса 400 процессора и памяти, которые могут соответственно использоваться для выполнения этапов способа 500 по фиг.5.

Чтобы выполнить выборку команды, на этапе 502 генерируется адрес выборки команды для желательной команды. Например, процессор, такой как процессор 402, генерирует адрес выборки команды и посылает адрес 414 выборки команды на контроллер 414 кэша команд Ll. Адресом выборки команды может быть виртуальный адрес, сформированный из номера 504 страницы и адреса 506 страницы. На этапе 508 соответствующая запись в таблице страниц команд, такой как таблица 416 страниц команд, выбирается на основе введенного номера 504 страницы. Адрес, сгенерированный на основе выбранной записи таблицы страниц, комбинируется на этапе 509 с адресом 506 страницы, чтобы сформировать адрес кэша команд.

Запись, выбранная из таблицы 416 страниц команд, включает в себя дополнительную информацию, сохраненную с этой записью. Один из дополнительных битов информации, которая может быть сохранена с каждой записью таблицы страниц, является атрибутом проверки кэша данных, таким как бит, обозначенный как D-бит 420. Этот атрибут выбирается на этапе 510.

На этапе 512 определяется, имеет ли место удачное обращение в кэш команд или промах. Например, кэш команд проверяет, присутствует ли команда. Если команда присутствует, ее присутствие указывается как попадание. Если команда присутствует, то способ 500 переходит к этапу 514, и команда по адресу выборки команды выбирается. На этапе 516 команда посылается в процессор. Например, выбранная команда помещается в шину 422 команд и посылается посредством элемента 438 мультиплексирования в шину 440 команд процессора 402.

Если команда не присутствует в кэше команд, как определено на этапе 512, выдается индикация того, что имел место промах, и способ 500 переходит к этапу 518. На этапе 518, D-бит, который был выбран на этапе 510, проверяется, установлен ли он на 1, указывая, что кэш данных должен быть проверен на наличие команды. Если D-бит был установлен на 1, то процессор пытается выбрать команду из кэша данных на этапе 520. Например, сгенерированный адрес 418 выборки команды посылается как адрес 434 выборки данных в кэш данных.

На этапе 524, кэш данных проверяет, присутствуют ли действительные данные, существующие по введенному адресу выборки команды. Если действительные данные существуют по введенному адресу выборки команды, то данные в действительности являются командой, и на этапе 528 запись выбирается из кэша данных. На этапе 516, данные, выбранные из кэша данных, посылаются как команда в процессор. Например, выбранные данные по шине 436 данных посылаются посредством элемента 438 мультиплексирования и подаются в качестве команды в процессор 402 по шине 440 команд.

Возвращаясь на этап 518, если на этапе 518 определено, что D-бит был равен 0, то это означает, что команда не присутствует в кэше данных, и способ 500 переходит к этапу 522. Этап 522 также достигается в ситуации, где имел место промах в кэше данных по введенному адресу выборки команды, как определено на этапе 524. В любом случае, это означает, что команда не присутствует в кэше команд или в кэше данных, и команда выбирается из системной памяти, как указано на этапе 522. Например, к системной памяти 412 будет выполняться доступ для извлечения команды. Как только команда получена от системной памяти 412, команда посылается в процессор 402, как указано на этапе 516.

На фиг.6 представлена приведенная для примера блок-схема способа 600 для выполнения программного кода, который сгенерирован как данные и сохранен в кэше данных. Программный код, следуя этому способу, может выполняться на комплексе процессора и памяти, имеющем кэш команд, кэш данных и системную память, такие как обсужденные в связи с фиг.2 и 4, и может соответственно использоваться в компонентах 125 A-C по фиг.1.

На этапе 602 программа генерирует код. Такая генерация может происходить, например, когда программа генерирует исполняемый код из сжатой программы. Сгенерированный код первоначально обрабатывается как данные и сохраняется в кэше данных после его генерации. Перед выполнением программы, кэш команд делается недействительным (инвалидируется) на этапе 604. Этап инвалидирования гарантирует, что нет никаких команд по тому же самому адресу, что и для сгенерированного кода. На этапе 606, сгенерированный код исполняется процессором путем выборки команд из адресного пространства программы в кэше команд и может включать в себя команды, которые сохранены в кэше данных. Для тех команд, которые сохранены в кэше данных, выполняются способы настоящего раскрытия, позволяя проверять кэш данных на наличие команд при возникновении промаха в кэше команд. После обнаружения команды в кэше данных, команда непосредственно выбирается из кэша данных для исполнения на процессоре.

Хотя настоящее раскрытие было представлено в предпочтительном в настоящее время контексте, следует иметь в виду, что представленные решения могут быть адаптированы к множеству контекстов, совместимых с настоящим раскрытием и пунктами формулы изобретения, как это изложено далее.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО И СПОСОБЫ ДЛЯ УМЕНЬШЕНИЯ ВЫТЕСНЕНИЙ В МНОГОУРОВНЕВОЙ ИЕРАРХИИ КЭША | 2008 |

|

RU2438165C2 |

| ФИЛЬТРАЦИЯ ОТСЛЕЖИВАНИЯ С ИСПОЛЬЗОВАНИЕМ КЭША ЗАПРОСОВ ОТСЛЕЖИВАНИЯ | 2008 |

|

RU2443011C2 |

| ИНДИКАТОР ИЗМЕНЕНИЙ ДЛЯ УМЕНЬШЕНИЯ ПОТРЕБЛЕНИЯ ЭНЕРГИИ ПРИ НЕУДАЧНЫХ ОБРАЩЕНИЯХ К КЭШ-ПАМЯТИ | 2006 |

|

RU2390855C2 |

| СПОСОБ И СИСТЕМА ВЫЧИСЛЕНИЯ УКАЗАТЕЛЯ ДЛЯ МАСШТАБИРУЕМОГО ПРОГРАММИРУЕМОГО КОЛЬЦЕВОГО БУФЕРА | 2006 |

|

RU2395835C2 |

| СТРУКТУРА СОВМЕСТНО ИСПОЛЬЗУЕМОГО КЭША ДЛЯ ВРЕМЕННЫХ И НЕВРЕМЕННЫХ КОМАНД | 1999 |

|

RU2212704C2 |

| РЕАЛИЗАЦИЯ УПРАВЛЕНИЯ ДОСТУПОМ К ПАМЯТИ С ИСПОЛЬЗОВАНИЕМ ОПТИМИЗАЦИЙ | 2004 |

|

RU2364932C2 |

| ИСПОЛЬЗОВАНИЕ КОНТЕКСТНОГО ИДЕНТИФИКАТОРА В КЭШ-ПАМЯТИ | 2003 |

|

RU2285286C2 |

| СИСТЕМА И СПОСОБ ДЛЯ ПРЕДВАРИТЕЛЬНОЙ ВЫБОРКИ ДАННЫХ В КЭШ-ПАМЯТИ, ОСНОВАННОЙ НА ИНТЕРВАЛЕ НЕУДАЧ | 2001 |

|

RU2260838C2 |

| ПОДСИСТЕМА ПАМЯТИ ЯДРА МИКРОПРОЦЕССОРА | 2011 |

|

RU2475822C1 |

| СПОСОБ МОДИФИКАЦИИ РАЗРЕШЕНИЙ НА ДОСТУП К ПАМЯТИ В ЗАЩИЩЕННОЙ ПРОЦЕССОРНОЙ СРЕДЕ | 2014 |

|

RU2602793C2 |

Изобретение относится к области вычислительной техники и относится в целом к способам для выборки команд из памяти, имеющей кэш команд и кэш данных, и, более конкретно, к усовершенствованному подходу к выборке команд, после неудачного обращения к кэшу команд, посредством прямой выборки команды из кэша данных, если команда находится там. Техническим результатом является расширение функциональных возможностей. В процессоре возможны ситуации, когда команды и некоторые части программы могут находиться в кэше данных до выполнения программы. Предложены аппаратные и программные способы для выборки команды в кэше данных после возникновения промаха в кэше команд, позволяющие улучшить характеристику процессора. Если команда не присутствует в кэше команд, то адрес выборки команды посылается в качестве адреса выборки данных в кэш данных. Если имеются действительные данные, присутствующие в кэше данных по введенному адресу выборки команды, то эти данные в действительности являются командой, и запись кэша данных извлекается и подается как команда в процессорный комплекс. Дополнительный бит может быть включен в таблицу страниц команд, чтобы указать на промах в кэше команд и что кэш данных должен быть проверен на наличие команды. 3 н. и 17 з.п. ф-лы, 6 ил.

1. Способ обнаружения команды в кэше данных, который является отдельным от кэша команд, причем способ содержит

определение того, что попытка выборки по адресу выборки команды в кэше команд для команды неудачна;

определение того, что атрибут проверки кэша данных установлен в активное состояние в записи таблицы страниц, ассоциированной с адресом выборки команды;

выбор адреса выборки команды в качестве адреса выборки данных в ответ на пребывание атрибута проверки кэша данных в активном состоянии;

выполнение попытки выборки в кэше данных для команды по выбранному адресу выборки данных; и

установку индикации присутствия информации в активное состояние, если команда найдена в кэше данных, в ответ на попытку выборки в кэше данных.

2. Способ по п.1, дополнительно содержащий

установку атрибута проверки кэша данных в активное состояние в ассоциированной записи таблицы страниц при генерации команд, которые сохранены как данные в кэше данных.

3. Способ по п.1, дополнительно содержащий

генерирование данных посредством программы, причем данные предназначены для использования в качестве команд; и

запрос посредством программы операционной системы на установку атрибута проверки кэша данных в активное состояние по меньшей мере в ассоциированной записи таблицы страниц.

4. Способ по п.2, в котором атрибут проверки кэша данных сбрасывается для использования посредством другой программы.

5. Способ по п.1, в котором этап выбора адреса выборки команд дополнительно содержит

мультиплексирование адреса выборки команды и адреса выборки данных; и

выбор адреса выборки команды для применения в кэше данных в качестве выбранного адреса выборки данных, при этом адрес выборки команды выбирается после определения того, что попытка выборки команды в кэше команд неудачна.

6. Способ по п.1, в котором этап выполнения попытки выборки в кэше данных дополнительно содержит

определение того, что команда найдена в кэше данных; и

выборку команды из кэша данных.

7. Способ по п.1, дополнительно содержащий

определение того, что попытка выборки в кэше данных неудачна; и

информирование управления памятью команд о том, что попытка выборки в кэше данных неудачна.

8. Способ по п.7, дополнительно содержащий

выборку команды из системной памяти.

9. Процессорный комплекс, содержащий

кэш команд;

блок управления памятью команд, имеющий таблицу страниц с записями, которые имеют один или более атрибутов проверки кэша данных;

кэш данных;

первый селектор для выбора адреса выборки команды или адреса выборки данных на основе сигнала выбора в ответ на атрибут проверки кэша данных и индикацию состояния операции выборки команды в кэше команд, причем сигнал выбора вызывает применение адреса выборки команды или адреса выборки данных к кэшу данных, посредством чего команды или данные могут избирательно выбираться из кэша данных; и

процессор для выборки команд или данных.

10. Процессорный комплекс по п.9, в котором сигнал выбора первого селектора выбирает адрес выборки данных в ответ на операцию доступа к данным.

11. Процессорный комплекс по п.9, в котором сигнал выбора первого селектора выбирает адрес выборки команды, если индикация состояния операции выборки команды указывает, что команда не найдена в кэше команд, и атрибут проверки кэша данных установлен в активное состояние.

12. Процессорный комплекс по п.9, дополнительно содержащий

второй селектор для выбора шины вывода команды из кэша команд или шины вывода данных из кэша данных для применения к вводу шины команд процессора.

13. Процессорный комплекс по п.12, в котором второй селектор выбирает шину вывода данных из кэша данных, если индикация состояния операции выборки команды указывает, что команда не найдена в кэше команд, атрибут проверки кэша данных установлен в активное состояние, и индикация состояния операции выборки данных указывает, что данные найдены в кэше данных по адресу выборки команды, выбранному посредством первого селектора.

14. Процессорный комплекс по п.12, в котором второй селектор выбирает шину вывода команды, если индикация состояния операции выборки команды указывает, что команда найдена в кэше команд.

15. Процессорный комплекс по п.9, дополнительно содержащий

третий селектор для выбора шины вывода из системной памяти или шины вывода данных из кэша данных для применения к вводу шины команд кэша команд.

16. Процессорный комплекс по п.15, в котором третий селектор выбирает шину вывода данных из кэша данных, если индикация состояния операции выборки команды указывает, что команда не найдена в кэше команд, атрибут проверки кэша данных установлен в активное состояние, и индикация состояния операции выборки данных указывает, что данные найдены в кэше данных по адресу выборки команды, выбранному посредством первого селектора.

17. Способ исполнения программного кода, содержащий

генерацию команд, которые являются частью программного кода, которые сохранены как данные в кэше данных;

запрос операционной системы на установку атрибута проверки кэша данных в активное состояние и по меньшей мере одной записи таблицы страниц, ассоциированной с командами;

установление недействительным кэша команд до выполнения программного кода, который использует сгенерированные команды; и

выборку команды непосредственно из кэша данных в ответ на активное состояние атрибутов проверки кэша данных, ассоциированных с командами, если команды не найдены; и

выполнение программного кода.

18. Способ по п.17, в котором этап генерации команд включает в себя операцию загрузки команд в кэш данных.

19. Способ по п.17, в котором установление недействительным кэша команд дополнительно содержит

установление недействительной только части кэша команд по адресам, где сохранены сгенерированные команды.

20. Способ по п.17, в котором таблица страниц размещена в блоке управления памятью.

| US 2002010837 A1, 24.01.2002 | |||

| RU 93012944 A, 27.08.1996 | |||

| US 5737749 А, 07.04.1998 | |||

| US 2002013892 A1, 31.01.2002 | |||

| US 2006004942 A1, 05.01.2006 | |||

| US 5377336 A, 27.12.1994. |

Авторы

Даты

2010-08-20—Публикация

2007-01-22—Подача