Предпосылки изобретения

1. Область техники, к которой относится изобретение

Данное изобретение относится вообще к области процессоров и, в частности, к технике обеспечения структуры совместно используемого кэша для временных и невременных команд.

2. Уровень техники

Использование кэш-памяти с процессором способствует уменьшению времени доступа к памяти. Основная идея организации кэша состоит в том, что при хранении наиболее часто запрашиваемых команд и данных в быстрой кэш-памяти среднее время доступа к памяти почти равно времени выборки из кэша. Для достижения максимально возможной скорости работы типовые процессоры используют кэш-иерархию, т. е. различные уровни кэш-памяти. Различные уровни кэша соответствуют различным расстояниям от процессорного ядра. Чем ближе кэш к процессору, тем быстрее доступ к данным. Тем не менее, чем быстрее доступ к данным, тем это дороже для хранения данных. В результате, чем ближе уровень кэша, тем быстрее и меньше кэш.

Рабочая характеристика кэш-памяти часто измеряется в показателях ее результативности. Когда процессор обращается к памяти и находит слово в кэше, говорят, что производится результативное обращение. Если слово не найдено в кэше, значит оно находится в основной памяти, и это считается промахом. Если появляется промах, тогда делается назначение в записи, индексированной при доступе. Доступ может производиться для загрузки данных в процессор или хранения данных из процессора в памяти. Кэшированная информация сохраняется кэш-памятью до тех пор, пока не отпадает в ней необходимость, пока она не становится недействительной или не заменяется другими данными, в этих случаях запись кэша переназначается.

В процессорах, использующих кэш-иерархию, например процессорах Pentium Pro, которые имеют кэш L1 и L2, более быстрый и более малый кэш L1 располагается ближе к процессору, чем кэш L2. Когда процессор запрашивает помещаемые в кэш данные, например команду загрузки, запрос сначала посылается в кэш L1. Если запрашиваемые данные находятся в кэше L1, они доставляются процессору. В противном случае имеет место неудачное (безрезультативное) обращение в кэш L1, и запрос передается к кэшу L2. Аналогично, если имеет место результативное обращение в кэш L2, данные передаются в кэш L1 и ядро процессора. Если имеет место неудачное обращение в кэш L2, запрос передается к основной памяти. Основная память реагирует на неудачное обращение в кэш L2 предоставлением запрошенных данных в кэш L2, кэш L1 и ядро процессора.

Тип данных, которые обычно хранятся в кэше, включает активные части программ и данных. Когда кэш полон, необходимо заменить существующие строки запомненных данных в кэш-памяти, чтобы освободить пространство для вновь запрашиваемых строк данных. Одна такая техника замещения включает использование алгоритма замещения наиболее давнего по использованию элемента (LRU), который замещает наиболее давнюю по использованию строку данных вновь запрошенной строкой. В процессорах Pentium Pro, поскольку кэш L2 больше кэша L1, кэш L2 обычно хранит все строки в кэш L1 и некоторые дополнительные строки, которые были замещены в кэше L1 алгоритмом LRU.

Заявка на патент США с серийным номером 08/767950, поданная 17 декабря 1996 г., в настоящее время - патент США 5829025 "Computer System and Method of Allocating Cache Memories in a Multilevel Cache Hierarchy utilizing a Locality Hint within an Instruction" (Milland Mittal) - раскрывает технику распределения кэш-памяти посредством использования указания места, связанного с командой. Когда процессор получает доступ к памяти для передачи данных между процессором и памятью, этот доступ может распределяться к различным уровням кэша или не распределяться к кэш-памяти вообще в соответствии с указанием места, связанным с командой. Некоторые команды используются редко. Например, невременные команды упреждающей выборки предварительно загружают данные, которые процессор не запрашивает немедленно, но которые ожидаются к запросу в ближайшем будущем. Такие данные обычно используются только один раз или не будут повторно использоваться в ближайшем будущем и называются "невременными данными". Команды, которые используются часто, называются "временными данными". Для невременных данных, поскольку они используются редко, оптимальная рабочая характеристика обусловливает, что кэшированные данные в кэше не перезаписываются этими редко используемыми данными. Патент США 5829025 решает эту проблему путем использования буфера, отдельного от кэш-памяти, для хранения редко используемых данных, таких, как невременные данные с упреждающей выборкой. Тем не менее, использование дополнительного отдельного буфера дорого как с точки зрения цены, так и используемого им пространства.

Таким образом, имеется необходимость в разработке структуры совместно используемого кэша для временных и невременных команд, которая исключает использование отдельного буфера.

Сущность изобретения

Объектами настоящего изобретения являются способ и система для обеспечения управления кэш-памятью. Система включает в себя основную память, процессор, соединенный с основной памятью, и по меньшей мере одну кэш-память, соединенную с процессором для размещения в кэше данных. По меньшей мере одна кэш-память имеет по меньшей мере две области кэша, каждая из которых включает множество наборов данных. Каждый из множества наборов данных имеет бит, который указывает, содержит ли одна из по меньшей мере двух областей кэша невременные данные. Процессор получает доступ к данным из одной основной памяти или по меньшей мере одной кэш-памяти.

Краткое описание чертежей

Изобретение иллюстрируется со ссылкой на сопроводительные чертежи, приведенные в качестве примера реализации изобретения и не ограничивающие объема патентных притязаний. Идентичные ссылочные позиции на этих чертежах обозначают аналогичные элементы.

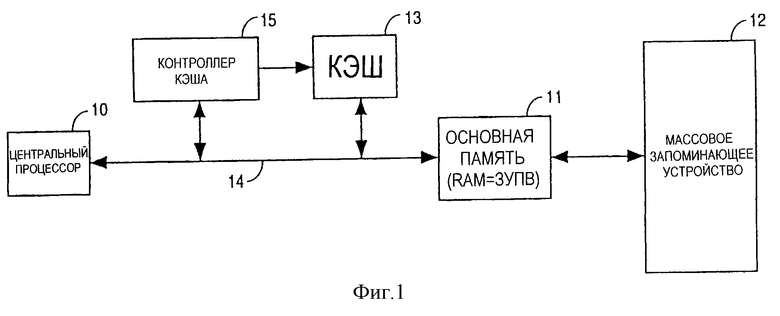

На фиг. 1 показана принципиальная блок-схема одного варианта реализации вычислительной системы, который использует данное изобретение, в котором кэш-память используется для доступов к данным между основной памятью и процессором вычислительной системы.

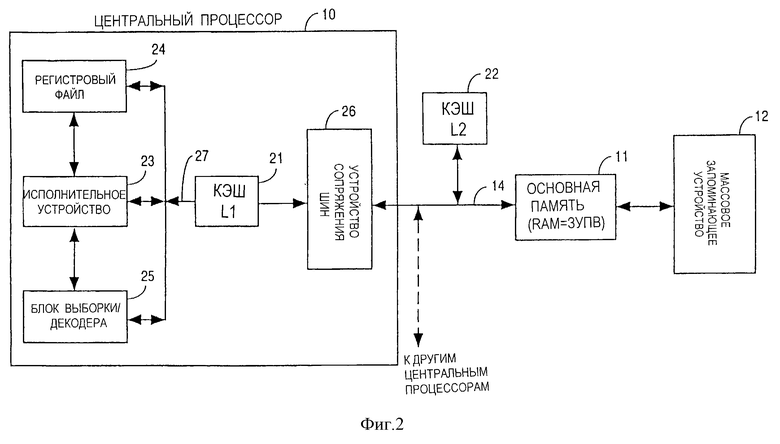

Фиг. 2 является принципиальной блок-схемой второго варианта реализации вычислительной системы, который использует данное изобретение, в котором две кэш-памяти организуются в уровни кэш-памяти для получения доступа к данным между основной памятью и процессором(ами) вычислительной системы.

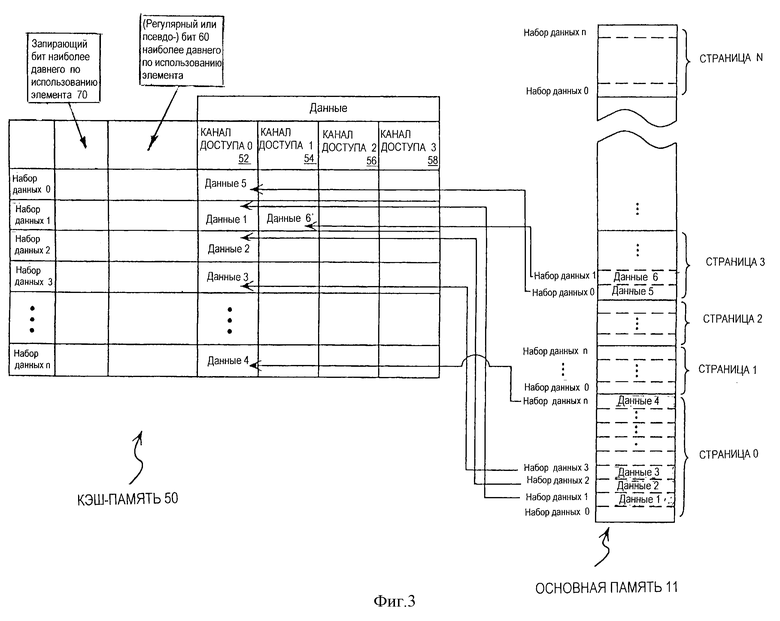

Фиг.3 является блок-схемой, иллюстрирующей один вариант реализации организационной структуры кэш-памяти, в которой используется техника данного изобретения.

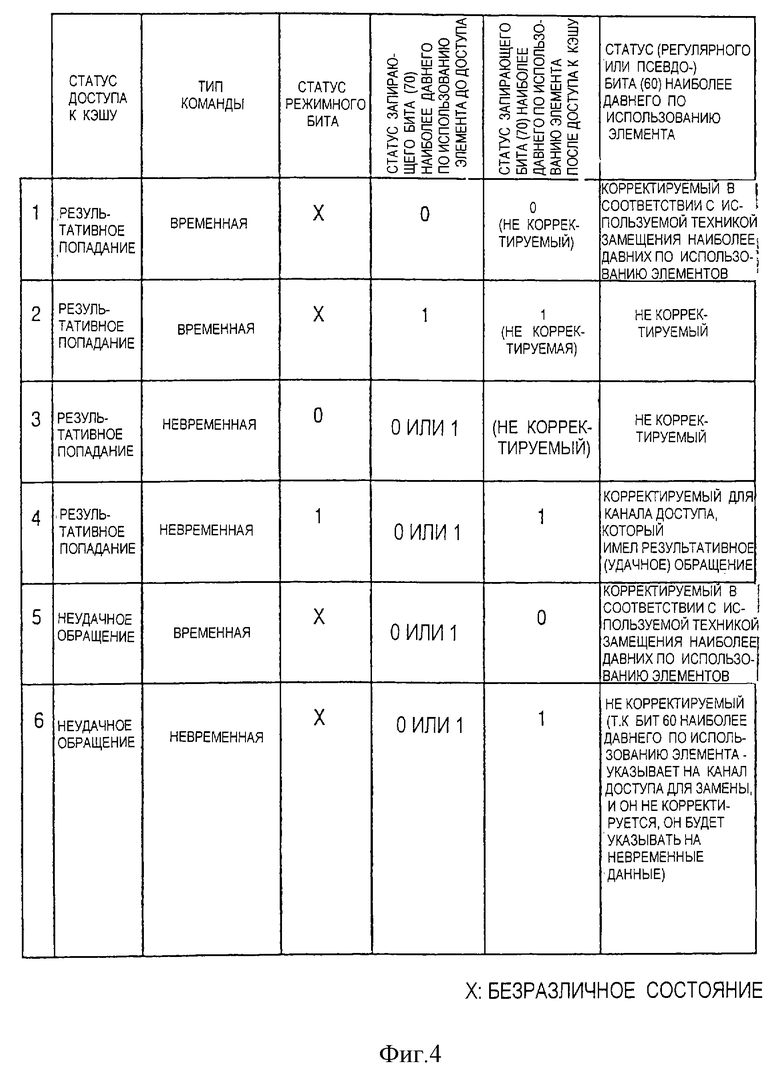

Фиг. 4 является таблицей, иллюстрирующей технику управления кэшем в соответствии с одним вариантом реализации данного изобретения.

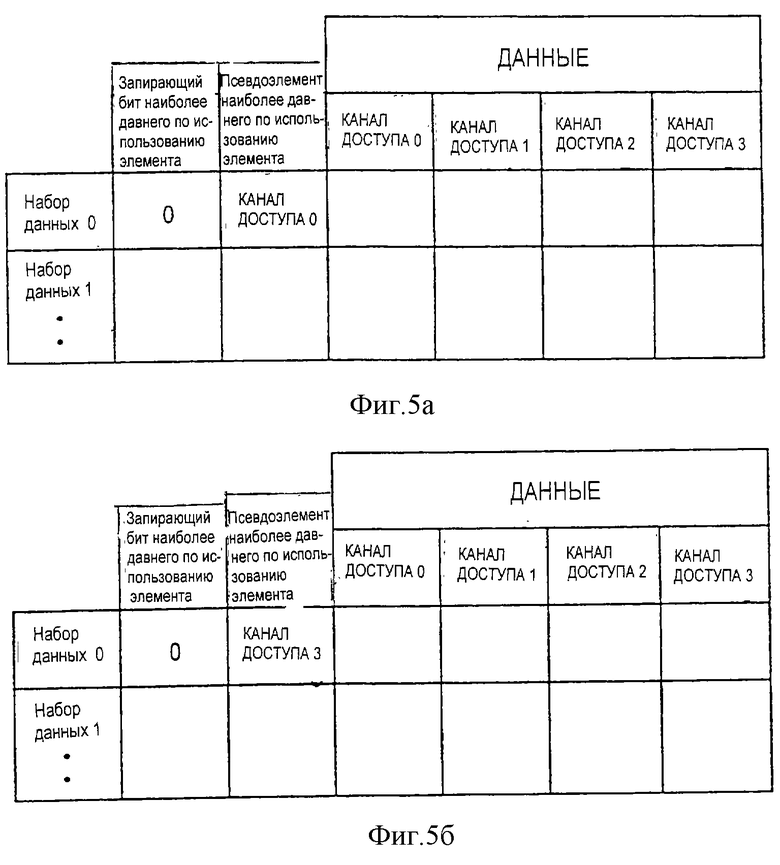

На фиг.5а и 5б проиллюстрирован один пример организации кэш-памяти перед и после результативных обращений временной команды в область 2 для набора 0 кэша в соответствии с одним вариантом реализации данного изобретения.

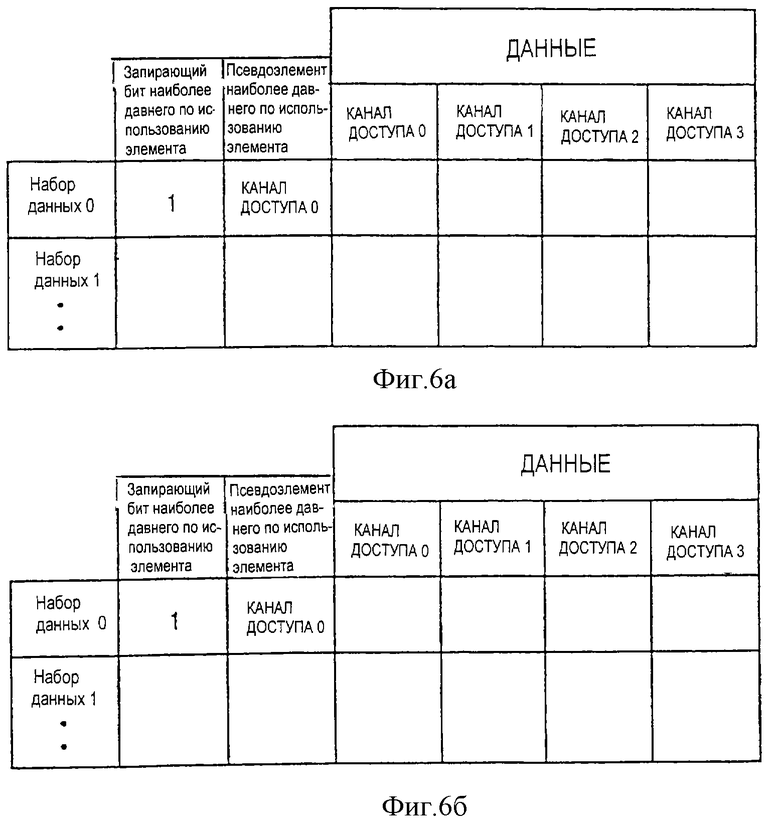

На фиг. 6а и 6б проиллюстрирован другой пример организации кэш-памяти перед и после результативных обращений временной команды в область 2 для набора 0 кэша в соответствии с одним вариантом реализации данного изобретения.

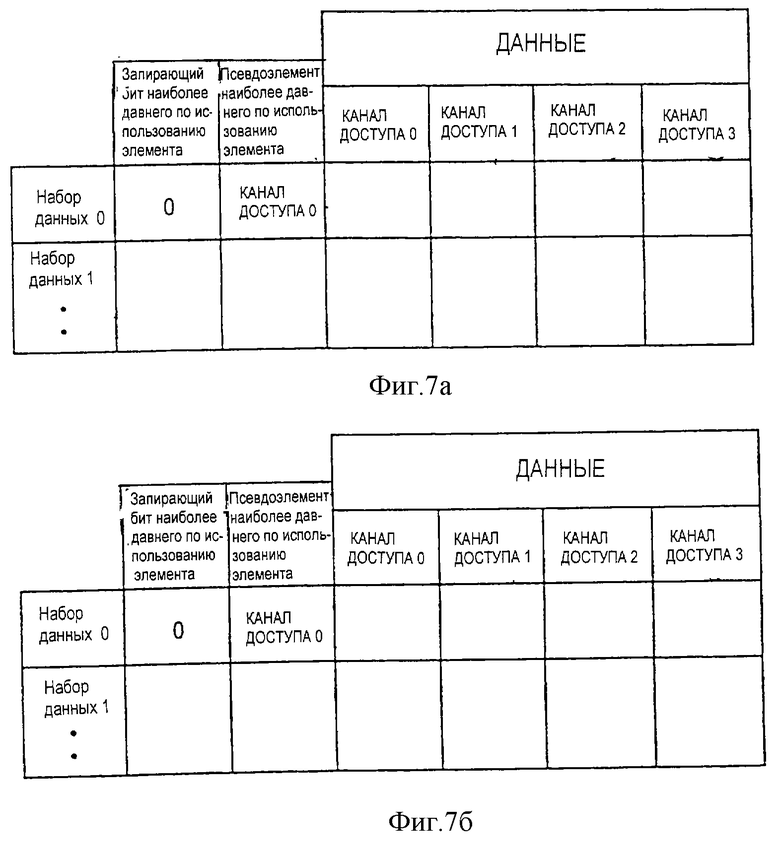

На фиг. 7а-7г проиллюстрирован пример организации кэш-памяти перед и после результативных обращений невременной команды в область 2 для набора 0 кэша в соответствии с одним вариантом реализации данного изобретения.

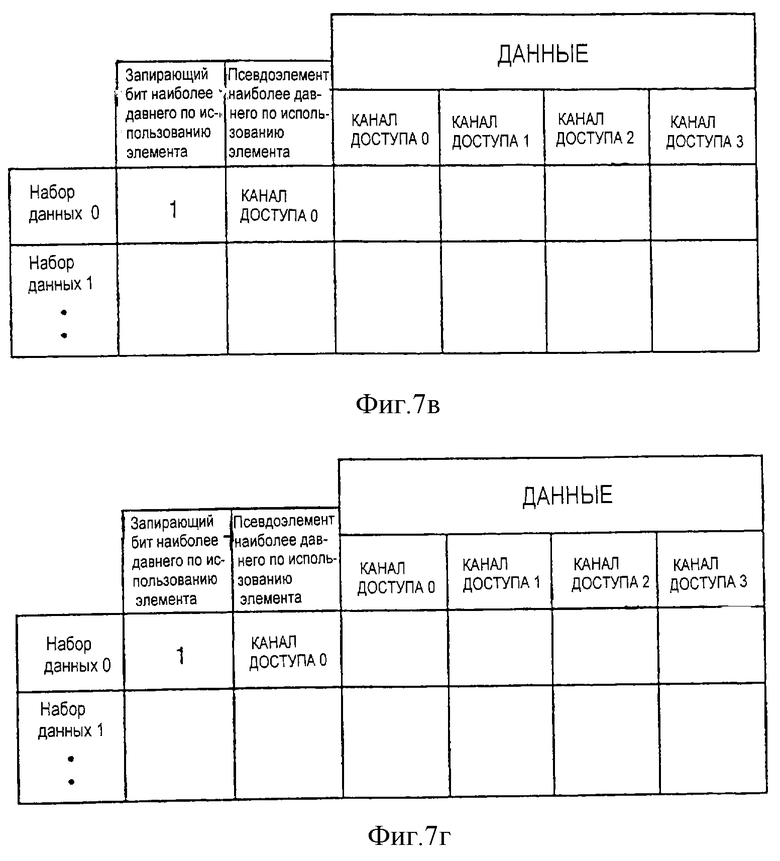

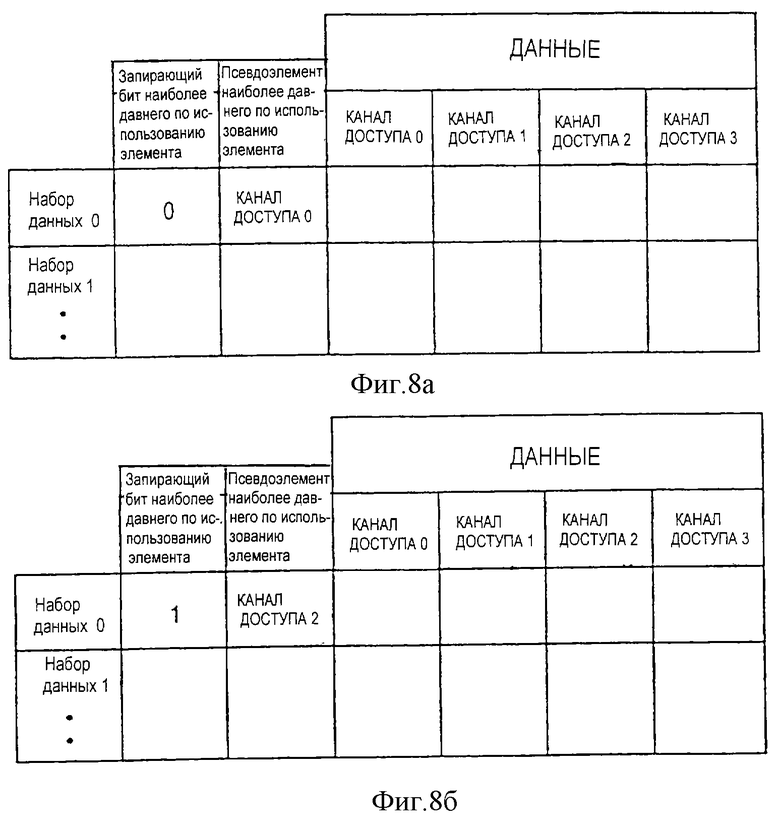

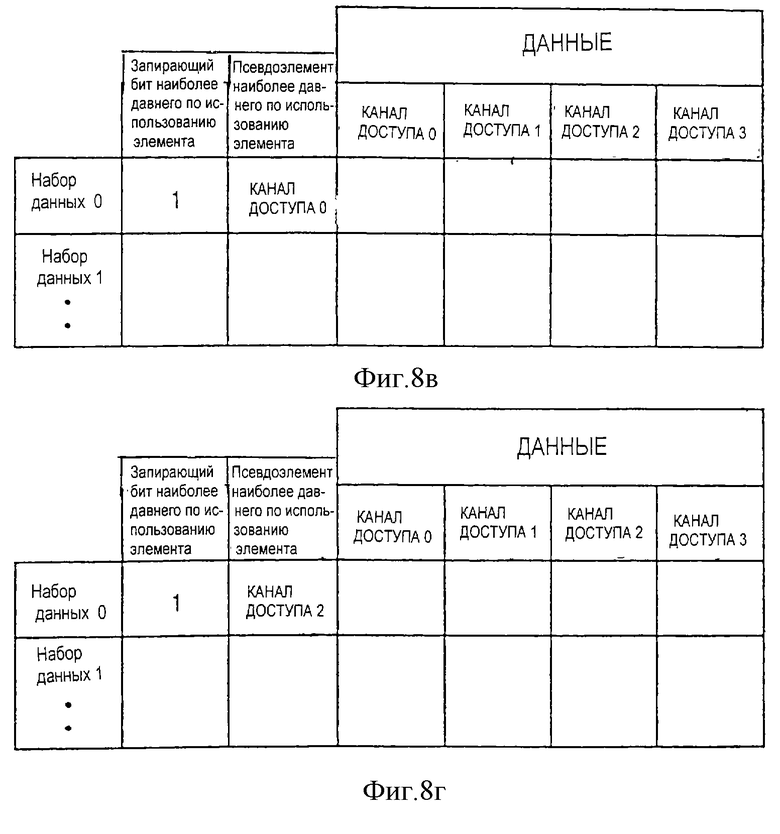

На фиг.8а-8г показан другой пример организации кэш-памяти перед и после результативных обращений невременной команды в область 2 для набора 0 кэша в соответствии с одним вариантом реализации данного изобретения.

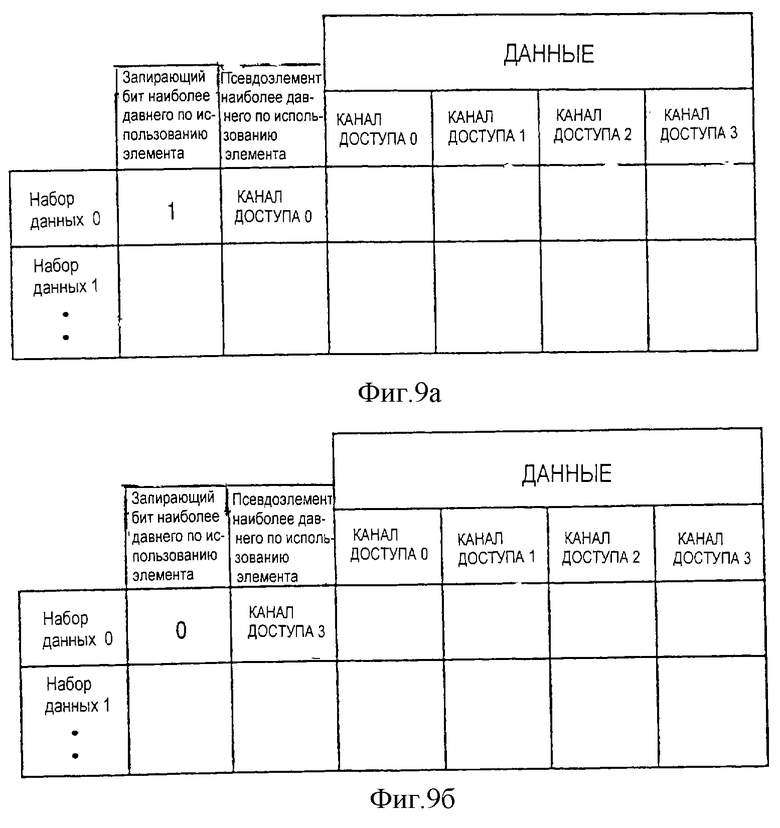

На фиг.9а-9б проиллюстрирован один пример организации кэш-памяти перед и после промаха временной команды к набору 0 кэша в соответствии с одним вариантом реализации данного изобретения.

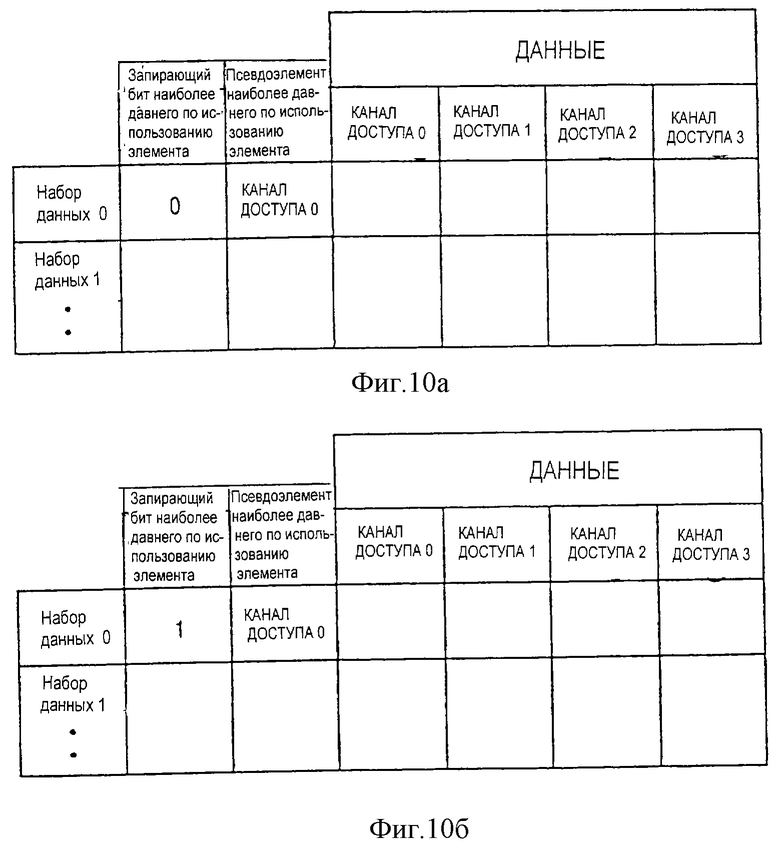

На фиг. 10а-10б проиллюстрирован пример организации кэш-памяти перед и после промаха невременной команды набора кэша 0 в соответствии с вариантом реализации данного изобретения.

Детальное описание изобретения

Описывается техника для обеспечения управления кэш-памятями, в которой распределение кэша определяется при использовании данных. В нижеприведенном тексте описания излагается ряд специфических деталей, таких, как специфические запоминающие устройства, принципиальные схемы, команды процессора и т. д. , для того, чтобы обеспечить исчерпывающее понимание сущности данного изобретения. Тем не менее, специалисту понятно, что данное изобретение может использоваться на практике без этих специфических деталей. В других случаях хорошо известные технологии и структуры не были описаны детально для того, чтобы не усложнять описания данного изобретения, тем не менее, вполне понятно, что другие варианты реализации, не выходящие за суть и рамки данного изобретения, могут быть разработаны и использованы. Кроме того, понятно, что данное изобретение описывается в отношении последовательно организованной системы иерархии кэша, но не обязательно строго ограничивается такой иерархией.

На фиг.1 показана типовая вычислительная система, где процессор 10, который образует центральный процессор ЦП (CPU) вычислительной системы, соединяется с основной памятью 11 шиной 14. Основная память 11 обычно включает в себя запоминающее устройство с произвольной выборкой и обычно называется ЗУПВ (RAM). Потом основная память 11, как правило, соединяется с массовым запоминающим устройством 12, таким, как магнитное или оптическое запоминающее устройство, для массового запоминания (или хранения) информации. Кэш-память 13 (ниже также называемая просто кэшем) соединяется также с шиной 14. Кэш 13 показан расположенным между CPU 11 и основной памятью 11 для того, чтобы привести пример функционального использования и передачи данных, связанных с кэшем 13. Понятно, что действительное физическое размещение кэша 13 может изменяться в зависимости от системы и конфигурации процессора. Кроме того, контроллер кэша 15 показан соединенным с кэшем 13 и шиной 14 для управления работой кэша 13. Работа контроллера кэша, такого, как контроллер 15, известна в технике и, таким образом, на последующих чертежах контроллеры кэша не иллюстрируются. Предполагается, что некоторый(е) контроллер(ы) находится(ятся) под управлением ЦП 10 для управления работой показанного(ых) кэша(ей).

При работе вычислительной системы передача информации между памятью 11 и ЦП 10 выполняется посредством доступов (обращений) к памяти от ЦП 10. Когда кэшируемые данные являются легко или быстро доступными для ЦП 10, эти данные сначала размещаются в кэше 13. То есть, когда ЦП 10 обращается к данной информации из памяти 11, он получает информацию из кэша 13. Если запрошенные данные находятся в кэше 13, происходит "результативное обращение". В противном случае следует "промах", и разыскивается распределение кэша для данных. Как практикуется в настоящее время, большая часть доступов (либо загрузка, либо хранение) требует распределения кэша 13. Только не кэшируемые обращения не распределяются в кэше. На фиг.2 показана вычислительная система, использующая компоновку со множеством кэшей. ЦП 10, по-прежнему, соединен с основной памятью 11 посредством шины 14, а память 11 затем соединяется с массовым запоминающим устройством 12. Тем не менее, на примере фиг. 2 показаны две отдельные кэш-памяти 21 и 22. Кэши 21-22 показаны организованными последовательно, и каждый является представителем уровня кэша, называемым кэшем уровня 1 (L1) и кэшем уровня 2 (L2) соответственно. Кроме того, кэш L1 21 показан как часть ЦП 10, в то время как кэш L2 22 показан внешним к ЦП 10. Эта структура приводит пример известной практики размещения кэша L1 на интегральной схеме процессора, в то время как кэши более низкого уровня размещаются внешними к нему, где кэши более низкого уровня находятся дальше от ядра процессора. Фактическое положение различных кэш-памятей является конструктивным выбором или продиктовано конфигурацией процессора. Таким образом, понятно, что кэш L1 мог бы располагаться внешним по отношению к ЦП 10.

Как правило, ЦП 10 включает исполнительное устройство 23, регистровый файл 24 и блок 25 выборки/декодера. Исполнительное устройство 23 является ядром процессора ЦП 10 для исполнения различных арифметических (или не предусматривающих использование ЗУ) команд процессора. Регистровый файл 24 является набором регистров общего назначения для запоминания (или хранения) различной информации, необходимой для исполнительного устройства 23. Может быть более одного регистрового файла в более современных системах. Блок 25 выборки/декодера выбирает команды из ячейки запоминающего устройства (например, основной памяти 11), содержащей команды программы, которые будут исполняться, и декодирует эти команды для выполнения исполнительным устройством 23. В более современных процессорах, использующих конвейерную архитектуру, будущие команды выбираются с упреждением и декодируются перед тем, как команды действительно необходимы, так что процессор не простаивает в ожидании команд, подлежащих выборке при необходимости.

Различные блоки 23-25 ЦП 10 соединяются со структурой внутренних шин 27. Устройство сопряжения шин (BIU) 26 обеспечивает интерфейс для соединения различных блоков ЦП 10 с шиной 14. Как показано на фиг.2, кэш L1 соединяется с внутренней шиной 27 и функционирует как внутренний кэш для ЦП 10. Тем не менее, снова следует подчеркнуть, что кэш L1 мог бы находиться вне ЦП 10 и соединяться с шиной 14. Кэши могут использоваться для данных в кэше, команд или и тех, и других. В некоторых системах кэш L1 фактически разделен на две секции: одна секция для данных, использующих кэш, и другая секция для команд, использующих кэш. Тем не менее, для простоты объяснения различные кэши, изображенные на чертежах, показаны как одиночные кэши с данными, командами и другой информацией, называемой здесь данными. Полагается, что функции блоков, показанных на фиг.2, известны. Кроме того, полагается, что ЦП 10 фактически включает значительно больше компонентов, чем непосредственно показанные компоненты. Таким образом, только те структуры, которые имеют отношение к пониманию сущности данного изобретения, показаны на фиг.2. В одном структурном варианте реализации изобретение используется в системах, имеющих кэши данных. Тем не менее, изобретение применимо к любому типу кэша.

Следует также заметить, что вычислительная система может включать в себя более одного ЦП (как показано пунктирной линией на фиг.2). В такой системе является обычным для нескольких ЦП совместно использовать основную память 11 и/или массовое запоминающее устройство 12. Следовательно, некоторые или все кэши, связанные с вычислительной системой, могут совместно использоваться различными процессорами вычислительной системы. Например, с системой фиг.2 кэш L1 21 каждого процессора мог быть использован только своим процессором, но основная память 11 могла быть использована совместно всеми ЦП системы. К тому же, каждый ЦП имеет связанный внешний кэш L2 22.

Изобретение может быть реализовано на практике в вычислительной системе с одним ЦП или в вычислительной системе с несколькими ЦП. Далее отмечается, что другие типы блоков (отличные от процессоров), которые имеют доступ к памяти, могут функционировать эквивалентно ЦП, описанным здесь, и, следовательно, способны выполнять функции доступа к памяти, подобные описанным ЦП. Например, устройства прямого доступа к памяти (DMA) легко могут получить доступ к памяти, подобно процессорам, описанным здесь. Таким образом, вычислительная система, имеющая один процессор ЦП, но один или более блоков доступа к памяти, работала бы эквивалентно показанной и описанной здесь системе с несколькими процессорами.

Как отмечалось, показаны только два кэша 21-22. Тем не менее, вычислительная система не обязательно ограничивается только двумя уровнями кэша. В настоящее время практикуется использование кэша третьего уровня (L3) в более усовершенствованных системах. Также практикуется иметь последовательную организацию кэш-памятей, так что данные, кэшированные в кэше L1, также кэшируются в кэше L2. Если, возможно, имеется кэш L3, тогда данные, размещенные в кэше L2, обычно размещаются (кэшируются) также в кэше L3. Таким образом, данные, размещенные на отдельном уровне кэша, также кэшируются на всех более высоких уровнях иерархии кэша.

Фиг.3 является блок-схемой, иллюстрирующей один структурный вариант реализации организационной структуры кэш-памяти, в которой используется техника данного изобретения. Вообще имеется "х" наборов данных в структуре кэша, "у" областей на один упомянутый набор (где у≥2), и причем каждая область содержит одну запись данных или одну строку кэша. Изобретение предусматривает фиксирующий бит LRU (наиболее давний по использованию), который показывает, содержит ли какая-либо одна из областей в этом наборе невременные (NT) данные. Если это имеет место, регулярные или псевдо LRU биты будут корректироваться для указания NT данных. Существуют также "z" регулярных или псевдо-LRU битов на один набор. Если не устанавливается фиксирующий бит LRU, регулярные или псевдо-LRU биты указывают на область в наборе в соответствии с используемой техникой наиболее давнего по использованию элемента. Число регулярных или псевдо-LRU битов на набор изменяется в зависимости от числа областей на один набор и используемой (регулярной или псевдо) техники наиболее давнего по использованию элемента (LRU).

В этом варианте реализации показано, что кэш 50 организуется как ассоциативный кэш с набором из четырех областей. На примере фиг.3 показана каждая страница, которая эквивалентна 1/4 размера кэша. В частности, кэш 50 разделяется на четыре области (например, область 0 (52), область 1 (54), область 2 (56) и область 3 (58)) одинакового размера, и основная память 11 (см. также фиг.1 и 2) показана разделенной на страницы (например, страница 0 - страница n). В другом варианте реализации каждая страница может быть больше или меньше размера кэша. Организационная структура кэша 50 (как показано на фиг.3) может использоваться в кэше 13 фиг.1, кэше L1 21 и/или кэше L2 22 фиг.2.

Кэш 50 также включает матрицу из битов наиболее давнего по использованию (LRU) 600-60п, каждый из которых указывает область в наборе с данными наиболее давними по использованию (или NT данными, если используется измененная техника замещения наиболее давнего по использованию элемента). Такая распечатка проводится в соответствии с техникой наиболее давнего по использованию элемента под управлением контроллера кэша 15 для определения, какую запись кэша перезаписать в том случае, если набор кэша полон. Логика замещения наиболее давнего по использованию элемента (не показана) отслеживает положения кэша в наборе, который является наиболее давним по использованию. В одном варианте реализации может использоваться техника замещения наиболее давних по использованию элементов (LRU), которая строго отслеживает алгоритм наиболее давнего по использованию элемента директории. В одном альтернативном варианте реализации используется псевдоалгоритм (LRU), который производит наилучшую попытку в прослеживании наиболее давнего по использованию элемента директории. Для дискуссионных целей биты 600-60п будут называться битами LRU 600-60п, в то время как матрица битов LRU 600-60п будет называться LRU битами 60.

Кэш 50 далее включает матрицу фиксирующих битов LRU 700-70п, которые показывают, содержит ли какая-либо из областей 52, 54, 56, 58 в данном наборе данные, которые не должны "засорять" кэш 50 (т.е. данные с редким использованием), как подробно описано в следующих разделах текста описания.

Фиг. 4 является таблицей, иллюстрирующей технику управления кэшем в соответствии с принципами данного изобретения. Изобретение использует матрицу фиксирующих битов LRU 700-70п для указания, являются ли какие-либо соответствующие хранимые в кэше данные текущими или невременными, а по существу, должна ли первая запись заменяться при неудачном обращении в кэш к соответствующему набору данных. В одном варианте реализации фиксирующий бит LRU 70, когда установлен на 1, указывает, что соответствующий набор данных имеет запись, которая является невременной. Если фиксирующий бит LRU 70 сбрасывается при удачном (результативном) обращении к кэшу при временной команде, соответствующий(ие) бит(ы) LRU 60 корректируется(ются) в соответствии с применяемой техникой замещения наиболее давних по использованию элементов (см. поз. 1 фиг.4), и связанный фиксирующий бит LRU не корректируется. Тем не менее, если фиксирующий бит LRU 70 уже установлен на 1 (указывая, что соответствующий набор данных имеет невременную команду), фиксирующий бит 70 LRU не корректируется, и бит 60 LRU не корректируется (см. поз. 2).

В случае результативного обращения к кэшу при невременной команде бит LRU 60 и фиксирующий бит LRU 70 не корректируются безотносительно к статусу фиксирующего бита LRU 70 (см. поз.3). В альтернативном варианте реализации при управлении посредством режимного бита в управляющем регистре в контроллере кэша L1, результативные обращения к кэшу при текущих или невременных командах вынуждают биты LRU указывать область, к которой имело место результативное обращение (см. позицию 4). Кроме того, фиксирующий бит LRU 70 устанавливается на 1. В этом варианте реализации результативное обращение к данным при текущей или невременной команде должно быть первым, подлежащим замене при неудачном обращении в кэш к соответствующему набору данных.

Если происходит неудачное обращение в кэш при временной команде, фиксирующий бит LRU сбрасывается, и корректируется бит LRU 60 (поз. 5), исходя из техники псевдо-LRU. Тем не менее, при неудачном обращении в кэш при текущей или невременной команде фиксирующий бит LRU 70 устанавливается на 1, и соответствующий бит LRU 60 не корректируется (поз. 6).

Теперь будут обсуждены примеры каждой из позиций, приведенных в таблице фиг.4. На фиг.5а и 5б проиллюстрирован один пример организации кэш-памяти до и после удачных обращений временной команды в область 2 для набора 0 кэша. Этот пример соответствует поз. 1 фиг. 4. Здесь фиксирующий бит LRU 700 предварительно был сброшен для набора 0 кэша и, так как к набору 0 кэша было результативное обращение временной командой, фиксирующий бит LRU 700 не корректируется. Тем не менее, бит LRU 600 корректируется в соответствии с используемой техникой LRU. В этом примере предполагается, что техника псевдо-LRU показывает, что область 3 является наиболее давней по использованию записью.

На фиг.6а и 6б проиллюстрирован другой пример организации кэш-памяти до и после результативных обращений временной команды в область 2 для набора 0 кэша. Этот пример соответствует поз. 2 фиг.4. Здесь фиксирующий LRU бит 700 прежде был установлен для набора 0 кэша, указывая, что соответствующий набор содержит невременные данные. Соответственно ни фиксирующий бит LRU 700, ни бит LRU 600 не корректируются.

На фиг. 7а-7г проиллюстрирован пример организации кэш-памяти до и после результативных обращений невременной команды в область 2 для набора 0 кэша. Этот пример соответствует поз. 3 фиг.4 и может использоваться при установке режимного бита, расположенного в контроллере кэша L1, на нуль (см. фиг.4). В первом случае (фиг.7а и 7б) фиксирующий бит LRU 700 прежде был сброшен для набора 0 кэша. В этом варианте реализации невременное результативное обращение к кэшу не корректирует фиксирующий бит LRU 70. Соответственно, так как к набору 0 кэша имело место результативное обращение согласно невременной команде, ни фиксирующий бит LRU 700, ни бит LRU 600 не корректируются. Во втором случае (фиг.7в и 7г) фиксирующий бит LRU 700 предварительно был установлен для набора 0 кэша, указывая на то, что соответствующий набор содержит невременные данные. Соответственно ни фиксирующий бит LRU 700, ни бит LRU 600 не корректируются.

На фиг. 8а-8г показан другой пример организации кэш-памяти до и после результативных обращений невременной команды к набору 0 кэша. Этот пример соответствует поз. 4 фиг.4 и может быть реализован при установке режимного бита, расположенного в контроллере кэша L1, на единицу (см. фиг.4). В первом случае (фиг.8а и 8б) фиксирующий бит LRU 70о прежде был сброшен для набора 0 кэша. В этом примере альтернативного варианта реализации примера, показанного на фиг.7а-7г, невременное результативное обращение к кэшу корректирует фиксирующий бит LRU 70. Соответственно, как показано на фиг.8а, так как к набору 0 кэша имело место результативное обращение согласно невременной команде, фиксирующий бит LRU 700 корректируется (устанавливается на 1), как показано на фиг.8б. Кроме того, биты LRU 600 корректируются для указания области, к которой имело место результативное обращение. В случае, когда фиксирующий бит LRU 700 прежде был установлен для набора 0 кэша (фиг.8в и 8г), фиксирующий бит LRU 700 остается установленным на 1. Кроме того, биты LRU 600 заставляют указывать область в наборе, к которой имело место результативное обращение.

На фиг.9а и 9б проиллюстрирован один пример организации кэш-памяти до и после неудачного обращения временной команды к набору 0 кэша. Этот пример соответствует позиции 5 фиг.4. Здесь фиксирующий бит LRU 700 ранее был установлен для набора 0 кэша, а так как имеет место неудачное обращение временной команды, указывающей на набор 0, фиксирующий бит LRU 700 сбрасывается для этого набора после замены временного неудачного обращения к кэшу. Тем не менее, бит LRU 600 корректируется в соответствии с используемой техникой LRU. В этом примере техника псевдо-LRU показывает, что область 3 является наиболее давней по использованию записью.

На фиг.10а-10б проиллюстрирован пример организации кэш-памяти до и после неудачного обращения невременной команды к набору 0 кэша. Этот пример соответствует поз. 6 фиг.4. В этом случае фиксирующий бит LRU 700 ранее был сброшен для набора 0 кэша. Так как имеется невременное неудачное обращение к набору 0 кэша, устанавливается фиксирующий бит LRU 700, и биты LRU 600 остаются теми же самыми для того, чтобы указать на невременные данные в соответствующем наборе 0.

При реализации устройства и способа данного изобретения обеспечивается совместно используемая структура кэша для управления временными и невременными командами, которая сводит к минимуму "засорение" данных в кэше или иерархии кэша. Реализация данного изобретения также устраняет необходимость в использовании отдельного буфера, реализация которого становится более эффективной с точки зрения как стоимости, так и функциональных характеристик.

Данное изобретение может быть реализовано в других специфических формах без отступления от его сути или существенных характеристик. Описанные варианты реализации следует рассматривать во всех аспектах только как иллюстративные, а неограничивающие объема патентных притязаний, определяемого приложенной формулой изобретения, а не вышеизложенным текстом описания. Все изменения в формах и деталях возможны, не отступая от сути и объема патентных притязаний настоящего изобретения,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТАНОВКА, СПОСОБ И СИСТЕМА КЭШИРОВАНИЯ | 2008 |

|

RU2483347C2 |

| НЕЧУВСТВИТЕЛЬНЫЙ К ЗАДЕРЖКЕ БУФЕР ТРАНЗАКЦИИ ДЛЯ СВЯЗИ С КВИТИРОВАНИЕМ | 2014 |

|

RU2598594C2 |

| СИСТЕМА И СПОСОБ ДЛЯ ПРЕДВАРИТЕЛЬНОЙ ВЫБОРКИ ДАННЫХ В КЭШ-ПАМЯТИ, ОСНОВАННОЙ НА ИНТЕРВАЛЕ НЕУДАЧ | 2001 |

|

RU2260838C2 |

| УПРАВЛЕНИЕ ВРЕМЕНЕМ ОБРАЩЕНИЯ К ПАМЯТИ | 2014 |

|

RU2618938C2 |

| ОТОБРАЖЕНИЕ ВСТРОЕННОГО АДРЕСА ЕСС | 2014 |

|

RU2644529C2 |

| КЛАССИФИКАЦИЯ ОБНАРУЖЕНИЯ СОБЫТИЙ С ПОМОЩЬЮ ИДЕНТИФИКАТОРА ПОТОКА И УРОВНЯ ПРИВИЛЕГИЙ ПОТОКА | 2001 |

|

RU2268483C2 |

| МОДУЛЬ СОПРОЦЕССОРА КЭША | 2011 |

|

RU2586589C2 |

| УСТРОЙСТВО, СПОСОБ И СИСТЕМА УПРАВЛЕНИЯ МАТРИЦАМИ | 2010 |

|

RU2491616C2 |

| СИСТЕМНЫЙ КОГЕРЕНТНЫЙ КЭШ С ВОЗМОЖНОСТЬЮ ФРАГМЕНТАЦИИ/ДЕФРАГМЕНТАЦИИ | 2013 |

|

RU2635255C2 |

| ПРОЦЕССОР, СПОСОБ, СИСТЕМА И ИЗДЕЛИЕ ДЛЯ ВЕКТОРНОГО ИНДЕКСИРОВАННОГО ДОСТУПА К ПАМЯТИ ПЛЮС АРИФМЕТИЧЕСКОЙ И/ИЛИ ЛОГИЧЕСКОЙ ОПЕРАЦИИ | 2014 |

|

RU2620930C1 |

Изобретение относится к области процессоров и, в частности, к технике обеспечения структуры совместно используемой кэш-памяти. Техническим результатом является возможность использования для временных и невременных команд одной и той же кэш-памяти. Вычислительная система содержит основную память, процессор, по меньшей мере одну кэш-память. Способ описывает работу данной системы. 2 с. и 22 з.п. ф-лы, 20 ил.

| US 5353425 А, 04.10.1994 | |||

| Устройство для управления доступом к памяти от двух ЦВМ | 1985 |

|

SU1304030A1 |

| Подвеска контактного провода электрических железных дорог | 1975 |

|

SU549366A1 |

| US 4905141 А, 27.02.1990 | |||

| Устройство для регазификации сжиженных газов | 1973 |

|

SU496439A1 |

Авторы

Даты

2003-09-20—Публикация

1999-03-24—Подача