Предлагаемое техническое решение относится к области вычислительной техники и предназначено для обработки данных, высокопроизводительных вычислений и компьютерного моделирования. Такие устройства могут успешно применяться в народном хозяйстве для обработки больших объемов информации при обработке сейсмических данных, аудио/видео информации в телекоммуникациях, проведении расчетов в области нанотехнологий, биотехнологии, а также при выполнении самых разнообразных научных и прикладных исследований.

Техническое решение может найти применение при создании универсального оборудования для обработки данных вообще с визуализацией результатов, в том числе для оборудования, отличающегося сочетанием двух и более вычислительных машин, каждая из которых, по меньшей мере, снабжена процессорным элементом, устройствами ввода/вывода, постоянной и оперативной памятью, позволяющих вести многозадачную обработку данных с воздействием на содержание или порядок расположения обрабатываемых данных.

Известно техническое решение Sony «ZEGO» BCU-100 (http://pro.sony.com/bbsccms/ext/ZEGO/files/BCU-100_Whitepaper.pdf), с целью сокращения числа оборудования содержит центральный процессор, блок оперативной памяти, контроллер системной логики, блок буферной памяти, контроллер шины Gigabit Ethernet, контроллер накопителей на жестких магнитных дисках, контроллер USB, контроллер шины РСТ Express х8, графический контроллер.

Недостатком данного решения является наличие единственного процессора и блока оперативной памяти, а также невозможность использования наиболее распространенных моделей периферийных карт, использующих интерфейс шины PCI Express х16.

Наиболее близким техническим решением, которое выбрано в качестве прототипа, является сервер Mercury 1U Dual Cell-Based System 2 (http://www.mc.com/uploadedFiles/1U-DCBS2-ds.pdf), содержащий, по меньшей мере, два центральных процессора (2, 4), подключенных к блокам оперативной памяти (1, 3), два контроллера системной логики, содержащие интерфейс шины PCI Express х8, первый (5) из которых подключен к первому центральному процессору, а второй (12) - ко второму центральному процессору, контроллер системной логики (5), подключенный к первому центральному процессору, имеющий интерфейс шины PCI-X и подключенный по этому интерфейсу к двухканальному контроллеру Gigabit Ethernet (10), а также порты ввода-вывода (18, 19, 22, 23, 24).

Блок оперативной памяти, используемый в данном решении, жестко размещен на плате и не предполагает какого-либо изменения объема оперативной памяти.

Данное устройство имеет нижеперечисленные недостатки:

- невозможность использования наиболее распространенных моделей периферийных карт, использующих интерфейс шины PCI Express х16;

- невозможность изменения/замены модулей оперативной памяти, что влечет за собой снижение производительности на тех приложениях, которые требуют большего объема оперативной памяти.

Задача, на решение которой направлено заявляемое техническое решение, заключается в преодолении указанных недостатков.

Технический результат, достигаемый при использовании заявляемого технического решения, заключается в расширении функциональных возможностей и гибкости сервера в части используемого центрального процессора с большей производительностью, блока оперативной памяти с возможностью изменения ее объема, контроллера накопителей на жестких магнитных дисках (НЖМД), контроллера USB, позволяющего увеличить количество подключаемых устройств, как внутренних, так и внешних, контроллера системной логики с интерфейсом PCI Express х16.

Указанный технический результат достигается тем, что в сервере, содержащем, по меньшей мере, два центральных процессора, соединенных между собой однонаправленными высокоскоростными шинами и подключенных к блокам оперативной памяти, два контроллера системной логики, содержащие интерфейс шины PCI Express х8, первый из которых подключен к первому центральному процессору, а второй - ко второму центральному процессору, контроллер системной логики, подключенный к первому центральному процессору, имеющий интерфейс шины PCI-X и подключенный по этому интерфейсу к двухканальному контроллеру Gigabit Ethernet, а также порты ввода-вывода Gigabit Ethernet и сервисный модуль, имеющий интерфейсы ввода-вывода Fast Ethernet, RS-232 и два USB, в линию связи шины PCI-X первого контроллера системной логики, подключен контроллер накопителей на жестких магнитных дисках, между вторым контроллером системной логики и сервисным модулем включен контроллер USB, который связан с разъемом USB, между двухканальным контроллером Gigabit Ethernet и одним из портов Gigabit Ethernet установлен коммутатор Ethernet, подключенный к сервисному модулю посредством шины Fast Ethernet.

А также тем, что в качестве центральных процессоров использованы процессоры IBM PowerXCell 8i.

А также тем, что в качестве блока оперативной памяти использован блок с разъемами, обеспечивающими возможность изменения объема оперативной памяти.

А также тем, что второй контроллер системной логики имеет интерфейс шины PCI Express х16.

А также тем, что суммарная пропускная способность однонаправленных высокоскоростных шин, которыми соединены центральные процессоры, составляет 20 ГБ/с.

А также тем, что в сервисном модуле расположена специальная энергонезависимая память, в которую контроллеры системной логики записывают информацию о не успешном прохождении тестов.

А также тем, что сервисный модуль выполнен с возможностью загружаться и конфигурироваться независимо от контроллеров системной логики, что позволяет вести протоколирование неисправностей, происходящих в системе.

А также тем, что сервисный модуль выполнен с возможностью выполнять свое собственное внутреннее тестирование и в случае выявления неисправности, с возможностью записи сообщения об этом в специальную энергонезависимую память.

Сущность изобретения поясняется графическими материалами.

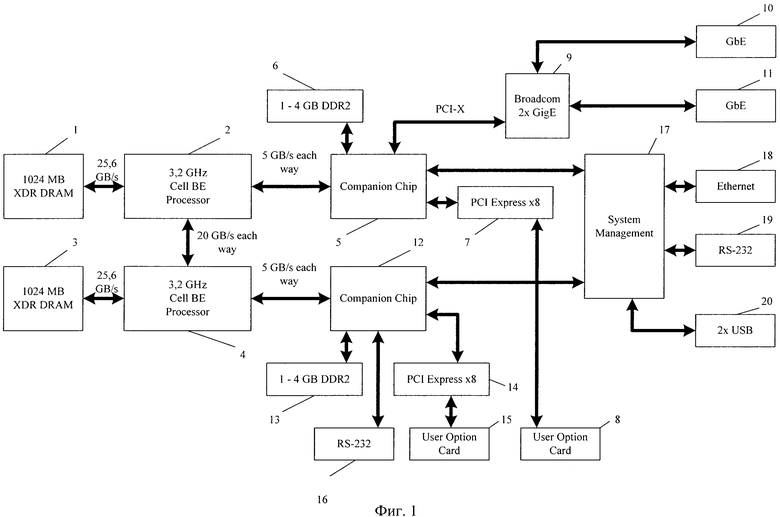

На фиг.1 представлена схема сервера, выбранного в качестве прототипа (http://www.mc.com/uploadedFiles/1U-DCBS2-ds.pdf).

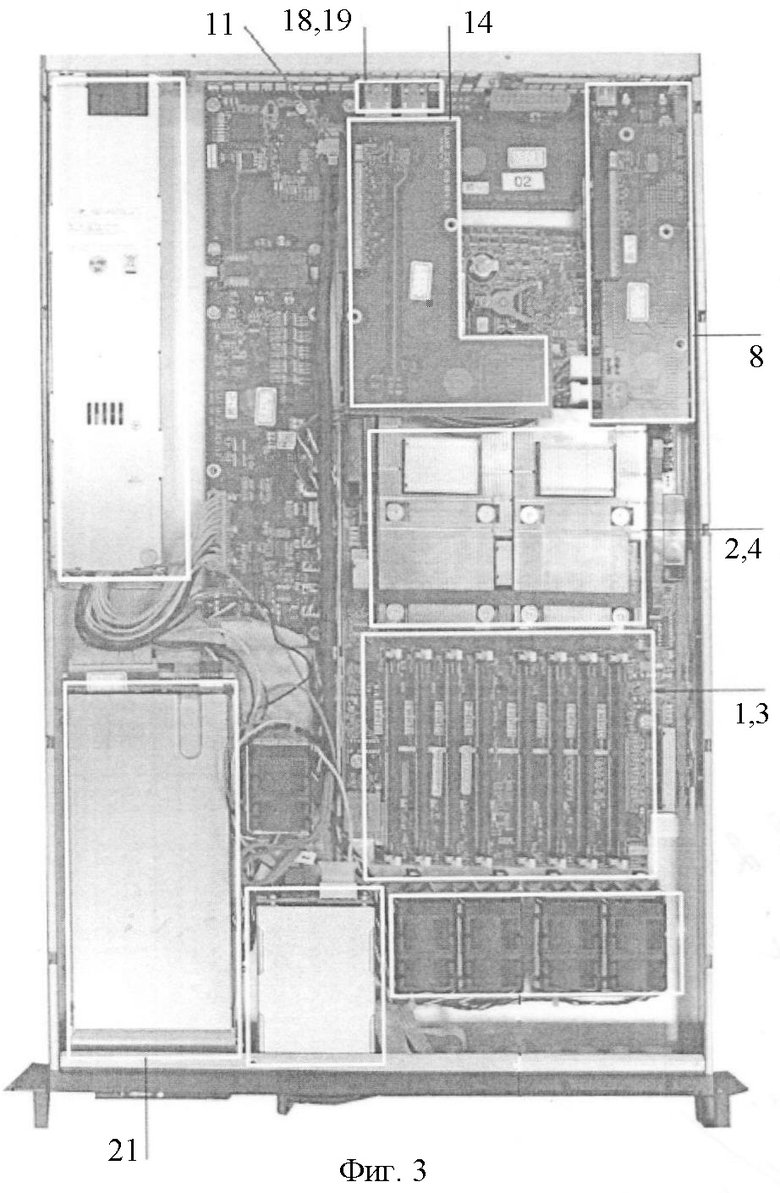

На фиг.2 представлена блок-схема предлагаемого технического решения.

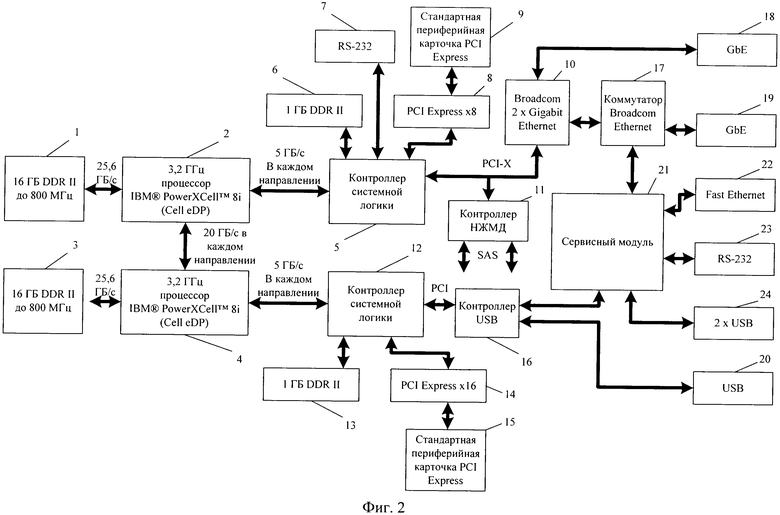

На фиг.3 - изображение сервера в сборе в корпусе.

Техническое решение, выбранное в качестве прототипа (фиг.1), содержит блок оперативной памяти 1, соединенный с первым центральным процессором 2 высокоскоростной шиной с суммарной пропускной способностью 25,6 ГБ/с. Второй блок оперативной памяти 3 также соединен высокоскоростной шиной с суммарной пропускной способностью 25,6 ГБ/с со вторым центральным процессором 4.

Процессоры 2 и 4 соединены между собой двумя однонаправленными высокоскоростными шинами с суммарной пропускной способностью 20 ГБ/с в каждом направлении.

Процессор 2 соединен двумя однонаправленными шинами с суммарной пропускной способностью 5 ГБ/с в каждом направлении с контроллером системной логики 5.

Контроллер системной логики 5 соединен с буферной памятью 6. Также контроллер имеет интерфейс 7 шины PCI Express х8, к которой имеется возможность подключать периферийные карточки 8 стандарта PCI Express x1, х2, х4 и х8. Контроллер 5 соединен с двухканальным контроллером Gigabit Ethernet 10 шиной PCI-X.

Контроллер системной логики 12 соединен с буферной памятью 13. Также контроллер имеет интерфейс 14 шины PCI Express х16, к которой имеется возможность подключать периферийные карточки 15 стандарта PCI Express x1, х2, х4, х8 и х16. Контроллер 12 содержит интерфейс 16 RS-232.

Двухканальный контроллер 9 соединен с портами ввода-вывода Gigabit Ethernet 10 и 11.

Сервисный модуль 21 подключается к контроллеру 5 и контроллеру 12.

Сервисный модуль 21 имеет интерфейсы ввода-вывода: Fast Ethernet 18, RS-232 19 и два USB 20.

Описанная схема не позволяет произвести изменение объема оперативной памяти, что резко снижает производительность сервера-прототипа. Отсутствует возможность применения наиболее распространенных периферийных карточек шины PCI Express х16, что ограничивает функциональные возможности сервера-прототипа.

Предлагаемое техническое решение, позволяющее преодолеть указанные недостатки и представленное на фиг.2, содержит блок оперативной памяти 1, соединенный с центральным процессором 2 высокоскоростной шиной с суммарной пропускной способностью 25,6 ГБ/с. Второй блок оперативной памяти 3 также соединен высокоскоростной шиной с суммарной пропускной способностью 25,6 ГБ/с с центральным процессором 4.

Процессоры 2 и 4 соединены между собой двумя однонаправленными высокоскоростными шинами с суммарной пропускной способностью 20 ГБ/с в каждом направлении.

Процессор 2 соединен двумя однонаправленными шинами с суммарной пропускной способностью 5 ГБ/с в каждом направлении с контроллером системной логики 5.

Контроллер системной логики 5 соединен с буферной памятью 6. Также контроллер имеет интерфейс RS-2327 и интерфейс 8 шины PCI Express х8, к которой имеется возможность подключать периферийные карточки 9 стандарта PCI Express x1, х2, х4 и х8. Контроллер 5 соединен с двухканальным контроллером Gigabit Ethernet 10 и контроллером накопителей на жестких магнитных дисках (НЖМД) 11 шиной PC 1-Х.

Контроллер системной логики 12 соединен с буферной памятью 13. Также контроллер имеет интерфейс 14 шины PCI Express х16, к которой имеется возможность подключать периферийные карточки 15 стандарта PCI Express x1, х2, х4, х8 и х16. Контроллер системной логики 12 соединен с контроллером USB 16 посредством шины PCI.

Двухканальный контроллер 10 соединен с коммутатором Ethernet 17. От контроллера 10 и коммутатора 17 идут интерфейсы Gigabit Ethernet 18 и 19.

От контроллера USB 16 идет интерфейс USB 20.

Сервисный модуль 21 подключается к контроллеру 16 и коммутатору 17 посредством шин USB и Fast Ethernet соответственно.

Сервисный модуль 21 имеет интерфейсы ввода-вывода Fast Ethernet 22, RS-232 23 и два USB 24.

В качестве центральных процессоров могут быть использованы процессоры IBM PowerXCell 8i. В качестве блока оперативной памяти использован блок с разъемами, обеспечивающими возможностью изменения объема оперативной памяти. Второй контроллер системной логики имеет интерфейс шины PCI Express х16.

Сервер функционирует следующим образом: после подачи электропитания контроллеры системной логики 5 и 12 независимо друг от друга опрашивают присоединенные к ним устройства и производят начальный тест системы. После успешного прохождения тестов контроллеры разрешают доступ ко всем интерфейсам центральным процессорам и периферийному оборудованию. В случае не успешного прохождения тестов контроллеры системной логики записывают информацию об этом в специальную энергонезависимую память, расположенную в сервисном модуле 21.

Каждый из центральных процессоров 2 и 4 проверяет наличие памяти в блоках оперативной памяти 1 и 3 соответственно, и определяет ее объем.

Контроллер НЖМД 11 по шине РС1-Х обращается к контроллеру системной логики 5 и запрашивает конфигурационную информацию, после получения которой считается сконфигурированным и готовым к работе.

Двухканальный контроллер Gigabit Ethernet 10 также конфигурируется по шине PCI-X.

Стандартная периферийная карточка 9 PCI Express х8, если таковая имеется, вставленная в разъем 8 PCI Express х8, конфигурируется по шине PCI Express от контроллера 5.

Последовательный порт ввода-вывода 7, имеющий интерфейс RS-232, конфигурируется контроллером системной логики и становится готовым к работе после успешного прохождения процесса тестирования контроллером системной логики 5.

Каждый из контроллеров системной логики 5 и 12 проверяет наличие буферной памяти 6 и 13 соответственно, и определяет ее объем.

Контроллер USB 16 становится готовым к работе после успешного прохождения процесса тестирования контроллером системной логики 12. После этого становится доступным (готовым к работе) порт USB 20.

Стандартная периферийная карточка 15 PCI Express х16, если таковая имеется, вставленная в разъем 14 PCI Express х16, конфигурируется по шине PCI Express от контроллера 12.

После конфигурирования двухканального контроллера Gigabit Ethernet 10 конфигурируется коммутатор 17. После выполнения данных процедур становятся доступными порты Gigabit Ethernet 18 и 19.

Сервисный модуль 21 загружается и конфигурируется независимо от контроллеров системной логики, что позволяет вести протоколирование неисправностей, происходящих в системе. Сервисный модуль выполняет свое собственное внутреннее тестирование. Если в результате этого тестирования выявляется какая-либо неисправность, то сообщение об этом записывается в специальную энергонезависимую память. Если тест прошел успешно, то сервисный модуль готов к использованию и все его порты ввода-вывода 22, 23 и 24 становятся доступны.

После выполнения всех вышеописанных процедур система готова к работе.

Работа системы начинается с обращения центрального процессора к контроллеру жестких дисков с целью получения информации о последних. Причем в качестве процессора, обращающегося к жестким дискам и фактически ведущего процессора, выступает первый процессор в сервере, номер которого жестко задан в контроллере системной логики. Если жесткие диски присутствуют, то контроллер НЖМД передает процессору извещение об этом. Далее процессор загружается с жесткого диска и управление сервером передается операционной системе (ОС).

Если жестких дисков не находится, то ведущий процессор пытается загрузиться по интерфейсам Gigabit Ethernet. Если и этого не произошло, то существует возможность загрузки ОС через порты USB.

После загрузки ОС возможно выполнение любых вычислительных действий, а также действий по передаче информации как в пределах сервера (от одного логического блока к другому), так и между несколькими серверами и внешними устройствами, посредством соответствующих интерфейсов, доступных извне.

На фигуре 3 представлено изображение конструктивной реализации предлагаемой блок-схемы. Испытания сервера, созданного в соответствии с настоящим изобретением, позволили получить следующие результаты, представленные ниже в таблице.

Сопоставление результатов с характеристиками прототипа показывает преимущество предлагаемого сервера, что свидетельствует о его промышленной применимости.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕРВЕР | 2022 |

|

RU2804258C1 |

| Плата системная вычислительного модуля | 2024 |

|

RU2822305C1 |

| Плата системная вычислительного модуля | 2024 |

|

RU2840229C1 |

| БЛЕЙД-СЕРВЕР | 2016 |

|

RU2616886C1 |

| Высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой | 2016 |

|

RU2635896C1 |

| Процессорный модуль системы хранения данных | 2018 |

|

RU2680744C1 |

| КЛАСТЕРНАЯ СИСТЕМА С ПРЯМОЙ КОММУТАЦИЕЙ КАНАЛОВ | 2011 |

|

RU2461055C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С МНОГОУРОВНЕВОЙ ПОДСИСТЕМОЙ МОНИТОРИНГА И АВТОМАТИЧЕСКИМ УПРАВЛЕНИЕМ | 2020 |

|

RU2748454C1 |

| ВИРТУАЛИЗАЦИЯ МАССОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА ДЛЯ ОБЛАЧНЫХ ВЫЧИСЛЕНИЙ | 2014 |

|

RU2649771C2 |

| Плата-переходник для установки в базовые устройства с процессорным модулем форм-фактора COM EXPRESS | 2024 |

|

RU2838350C1 |

Изобретение относится к области вычислительной техники и предназначено для обработки данных, высокопроизводительных вычислений и компьютерного моделирования. Техническим результатом изобретения является расширение функциональных возможностей сервера. Технический результат достигается благодаря тому, что сервер содержит, по меньшей мере, два центральных процессора, соединенных между собой однонаправленными высокоскоростными шинами и подключенных к блокам оперативной памяти, два контроллера системной логики, содержащие интерфейс шины PCI Express х8, первый из которых подключен к первому центральному процессору, а второй - ко второму центральному процессору, контроллер системной логики, подключенный к первому центральному процессору, имеющий интерфейс шины PCI-X и подключенный по этому интерфейсу к двухканальному контроллеру Gigabit Ethernet, а также порты ввода-вывода Gigabit Ethernet и сервисный модуль, имеющий интерфейсы ввода-вывода Fast Ethernet, RS-232 и два USB, в линию связи шины PCI-X первого контроллера системной логики, подключен контроллер накопителей на жестких магнитных дисках, между вторым контроллером системной логики и сервисным модулем включен контроллер USB, который связан с разъемом USB, между двухканальным контроллером Gigabit Ethernet и одним из портов Gigabit Ethernet установлен коммутатор Ethernet, подключенный к сервисному модулю посредством шины Fast Ethernet. 7 з.п. ф-лы, 3 ил., 1 табл.

1. Сервер, содержащий, по меньшей мере, два центральных процессора, соединенных между собой однонаправленными высокоскоростными шинами и подключенных к блокам оперативной памяти, два контроллера системной логики, содержащие интерфейс шины PCI Express х8, первый из которых подключен к первому центральному процессору, а второй - ко второму центральному процессору, контроллер системной логики, подключенный к первому центральному процессору, имеющий интерфейс шины PCI-X и подключенный по этому интерфейсу к двухканальному контроллеру Gigabit Ethernet, а также порты ввода-вывода Gigabit Ethernet и сервисный модуль, имеющий интерфейсы ввода-вывода Fast Ethernet, RS-232 и два USB, в линию связи шины PCI-X первого контроллера системной логики подключен контроллер накопителей на жестких магнитных дисках, между вторым контроллером системной логики и сервисным модулем включен контроллер USB, который связан с разъемом USB, между двухканальным контроллером Gigabit Ethernet и одним из портов Gigabit Ethernet установлен коммутатор Ethernet, подключенный к сервисному модулю посредством шины Fast Ethernet.

2. Сервер по п.1, отличающийся тем, что в качестве центральных процессоров использованы процессоры IBM PowerXCell 8i.

3. Сервер по п.1, отличающийся тем, что в качестве блока оперативной памяти использован блок с разъемами, обеспечивающими возможность изменения объема оперативной памяти.

4. Сервер по п.1, отличающийся тем, что второй контроллер системной логики имеет интерфейс шины PCI Express х16.

5. Сервер по п.1, отличающийся тем, что суммарная пропускная способность однонаправленных высокоскоростных шин, которыми соединены центральные процессоры, составляет 20 ГБ/с.

6. Сервер по п.1, отличающийся тем, что в сервисном модуле расположена специальная энергонезависимая память, в которую контроллеры системной логики записывают информацию о неуспешном прохождении тестов.

7. Сервер по п.1, отличающийся тем, что сервисный модуль выполнен с возможностью загружаться и конфигурироваться независимо от контроллеров системной логики, что позволяет вести протоколирование неисправностей, происходящих в системе.

8. Сервер по п.1, отличающийся тем, что сервисный модуль выполнен с возможностью выполнять свое собственное внутреннее тестирование и в случае выявления неисправности с возможностью записи сообщения об этом в специальную энергонезависимую память.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| ПЕРСОНАЛЬНЫЙ КОМПЬЮТЕР | 2004 |

|

RU2279708C1 |

Авторы

Даты

2010-10-20—Публикация

2008-10-31—Подача