Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Известны способы и устройства суммирования двоичных кодов, заключающиеся в последовательном выполнении элементарных операций (ЭО) приема слагаемых, формирования переноса и суммы в каждом разряде и занесение результата суммирования в триггеры регистра результата или в триггеры первого слагаемого. Способы и устройства суммирования двоичных кодов детально рассмотрены в книге Карцев М.А. «Арифметика цифровых машин», издательство «Наука», 1969 г., стр.288-345 и в книге Е.Л.Дроздова и др. «Электронные вычислительные машины Единой системы». - М.: Машиностроение, 1981 г., стр. 78-81. Общим недостатком известных способов и устройств является необходимость затраты, как минимум, трех временных тактов для выполнения операций сложения. Кроме того, требуется три RS- триггера в каждом разряде и существенные затраты оборудования для построения трехвходовых сумматоров комбинационного типа. Все это определяет быстродействие выполнения вычислительных операций, суммарный объем оборудования и стоимость устройства в целом. Наиболее близким, принятым за прототип, является суммирующее устройство по а.с. SU №1418705, которое содержит в каждом разряде два RS-триггера. Однако время выполнения операции сложения с приемом второго слагаемого также требует трех временных тактов, что является недостатком прототипа.

Предложенный способ и устройство устраняют отмеченный недостаток прототипа.

Целью изобретения является повышение быстродействия выполнения операции сложения при минимальных затратах оборудования, исчисляемого суммарным числом входов логических элементов одного разряда устройства.

Для этого предложен способ, заключающийся в последовательном выполнении элементарных операций приема кода второго слагаемого, формирования сигнала переноса в каждом разряде и формирования суммы в первых триггерах, отличающийся тем, что до начала выполнения операции в первых триггерах всех разрядов хранят первое слагаемое, вторые триггеры всех разрядов устанавливают в нуль, второе слагаемое поступает во все разряды, по информационным входам, по первому временному такту одновременно поразрядно выполняют элементарные операции логического сложения и логического умножения первого и второго слагаемых, при этом результат логического сложения принимают в первые триггеры, а результат логического умножения заносят во вторые триггеры, одновременно формируют потенциалы вспомогательного и основного переносов во всех разрядах, при этом вспомогательный перенос формируют выполнением операции логического умножения первого слагаемого, второго слагаемого и входа управления приемом кода второго слагаемого, основной перенос формируют выполнением операции логического умножения значения, полученного как результат выполнения операции логического сложения значений основного и вспомогательного переносов, выработанных в младшем разряде, и значения логического умножения текущего разряда, сохраненного во втором триггере, и значения, полученного как результат выполнения операции логического сложения первого слагаемого и результата выполнения операции логического умножения второго слагаемого и входом управления приемом кода второго слагаемого, по второму временному такту при наличие основного переноса из младшего разряда или единичного значения кода второго триггера формируют сумму i-го разряда путем инвертирования кода первого триггера, при этом сигнал инвертирования упомянутого триггера вырабатывается как результат логического умножения выходов четвертого элемента ИЛИ, пятого элемента НЕ и второго входа управления инвертированием первого триггера, в случае одновременного поступления основного переноса из младшего разряда и сигнала с выхода второго триггера, инвертирование первого триггера запрещается. Также предложено устройство сложения двоичных кодов, выполненное на элементах И, ИЛИ, НЕ, содержащее в каждом двоичном разряде первый и второй RS-триггеры, пять элементов И, два элемента ИЛИ, три элемента НЕ, информационный вход, первый вход управления приемом кода второго слагаемого, второй вход управления, при этом первый вход управления подключен к первому входу первого элемента И, второй вход которого соединен с информационным входом, отличающееся тем, что в каждый разряд введены три элемента И, два элемента ИЛИ, элемент НЕ, при этом в каждом разряде информационный вход соединен с первым входом первого элемента И, второй вход которого подключен к первому входу управления приемом кода второго слагаемого, выход первого элемента И соединен с первыми входами первого и третьего элементов ИЛИ и второго элемента И, выход второго элемента И подключен к единичному входу второго RS-триггера, второй вход управления инвертированием первого RS-триггера подключен к первому входу третьего элемента И, второй и третий входы которого связаны с выходами четвертого элемента ИЛИ и четвертого элемента НЕ соответственно, выход третьего элемента И соединен со вторым входом первого элемента ИЛИ, выходы третьего элемента И и первого элемента ИЛИ соединены с первыми входами шестого и седьмого элементов И соответственно, вторые входы которых подключены к входу и выходу первого элемента НЕ, выходы шестого и седьмого элементов И через второй и третий элементы НЕ соединены с нулевым и единичным входами первого RS-триггера, единичный выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого связан с выходом шестого элемента И, выход второго элемента ИЛИ соединен с первым входом восьмого элемента И, второй вход которого подключен к выходу третьего элемента НЕ, подключение выхода шестого элемента И через второй элемент ИЛИ к первому входу восьмого элемента И обеспечивает задержку выхода сигнала с восьмого элемента И при преключении первого RS-триггера из единичного состояния в нулевое; подключение выхода третьего элемента НЕ к второму входу восьмого элемента И обеспечивает задержку включения восьмого элемента И при переключении первого RS-триггера из нуля в единицу, упомянутая временная задержка сигнала с выхода восьмого элемента И равняется длительности сигнала входа управления инвертированием первого RS-триггера, выход восьмого элемента И соединен со вторым входом третьего элемента ИЛИ, входом первого элемента НЕ и вторым входом второго элемента И, единичный выход второго RS-триггера соединен с первыми входами четвертого элемента ИЛИ и пятого элемента И, первый вход четвертого элемента ИЛИ и второй вход пятого элемента И i-го разряда соединены с выходом четвертого элемента И (i-1)-го разряда, второй вход четвертого элемента ИЛИ i-го разряда является входом вспомогательного переноса в старший разряд и соединен с выходом второго элемента И (i-1)-го разряда, выходы третьего и четвертого элементов ИЛИ соединены с входами четвертого элемента И, выход которого является входом основного переноса в старший разряд, выход пятого элемента И подключен к входу четвертого элемента НЕ.

Отметим основные отличительные признаки предлагаемых способа и устройства, а также что позволяет получить каждый из этих признаков.

1. Предложенный способ за счет совмещения во времени приема кода и формирования переноса во всех разрядах сокращает время выполнения операции сложения до двух тактов. Это повышает быстродействие выполнения указанной операции по сравнению с прототипом в 1,5 раза.

2. Способ позволяет в ходе выполнения операции сложения получить после первого временного такта результат логического сложения и логического умножения кода первого слагаемого и кода, поступившего по информационным входам.

3. Соединение выхода второго элемента И i-го разряда с вторым входом четвертого элемента ИЛИ 1+i-го разряда позволяют формировать сигнал переноса во время первого временного такта, что обеспечивает выполнении операции сложения за два временных такта.

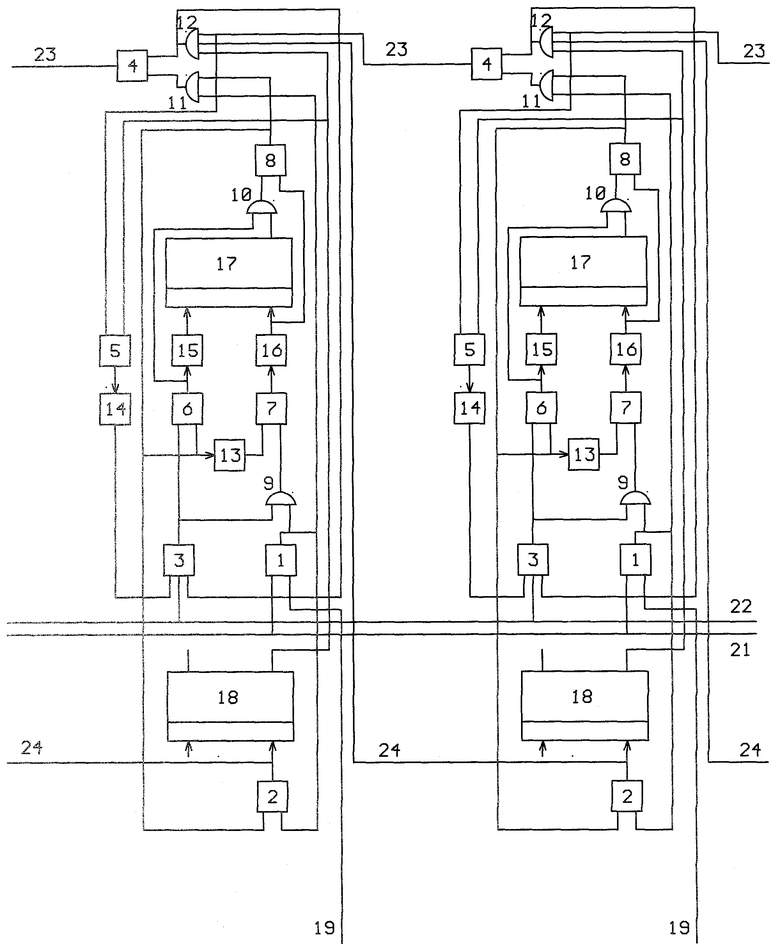

На фиг.1 приведена функциональная схема двух разрядов предлагаемого устройства. Каждый разряд содержит элементы И 1-8, RS-триггеры (Tr) 17, 18, элементы ИЛИ 9-12, элементы НЕ 13-16, информационный вход (ИВ) 19, вход управления (ВУ) приемом кода второго слагаемого 21, ВУ инвертированием первого RS-триггера (Tr) 22, основной вход переноса в старший разряд 23, вспомогательный вход переноса в старший разряд 24.

Рассмотрим работу устройства при выполнении операций сложения. В исходном состоянии (в статике) в Tr 17 хранится код первого слагаемого, Tr 18 установлен в нуль или прием в него осуществляется парафазным кодом, на ВУ 21, 22, на ИВ 19, на выходах 23, 24 отсутствуют высокие потенциалы.

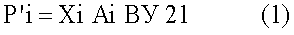

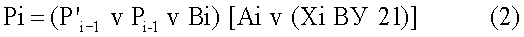

1. Операция сложения. Операция выполняется за два временных такта (t1, t2). По t1 выполняется прием кода второго слагаемого с информационных входов. Вместе с приемом второго слагаемого выполняются ЭО логического сложения и логического умножения первого и второго слагаемых. При этом на ВУ 21 поступает потенциал разрешения приема кода с ИВ 19. Если на ИВ 19 имеет место высокий потенциал, то с выхода И1 через ИЛИ 9, И 7, НЕ 16 на единичный вход Tr 17 поступает сигнал и устанавливает его в единицу, тем самым выполняется ЭО логического сложения первого и второго слагаемых с занесением результата в упомянутый триггер. Одновременно сигнал с выхода И1 поступит на вход И2. Если в Tr 17 хранится код единицы, то с выхода И2 на единичный вход Tr 18 поступит сигнал и установит его в единицу, тем самым выполняется ЭО логического умножения слагаемых i-го разряда с занесением результата в триггер 17. Одновременно с приемом кода по t1 формируются вспомогательный и основной переносы во всех разрядах устройства. Формирование переноса в i-м разряде выполняется согласно соотношениям (1) и (2).

Здесь Ai, Bi - значения слагаемых i-го разряда, хранящихся в Tr 17, 18;

P'i, Pi - впомогательный и основной переносы i-го разряда;

Pi-1, P'i-1 - основной и вспомогательный переносы, выработанные в младшем разряде;

Xi - код, поступающий по ИВ 19;

ВУ 21 - вход управления приемом кода второго слагаемого с ИВ 19.

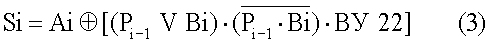

После завершения времени формирования максимального переноса, равного 2n τ (здесь n - число двоичных разрядов, 2τ - временная задержка переноса на элементах ИЛИ, И каждого разряда), по И формируется результат сложения согласно соотношению (3)

Здесь Si - сумма i-го разряда;

⊕ - знак сложения по модулю два;

ВУ 22 - вход управления инвертированием первого RS-триггера.

Первое логическое соотношение в (3), в простых скобках реализуется элементом ИЛИ 12, второе - элементами И 5, НЕ 14. При равенстве соотношения, заключенного в квадратные скобки, единице, сигнал с ВУ 22 через элементы И 3, ИЛИ 9 поступит на входы И 6, 7 и произведет инвертирование кода Tr 17, т.к. в случае хранения в Tr 17 кода единицы, элемент И 6 будет открыт и сигнал поступит на нулевой вход триггера. В том случае, если до прихода импульса, инвертирования, Tr 17 хранил код нуля, элемент И 7 будет открыт и сигнал поступит на единичный вход триггера.

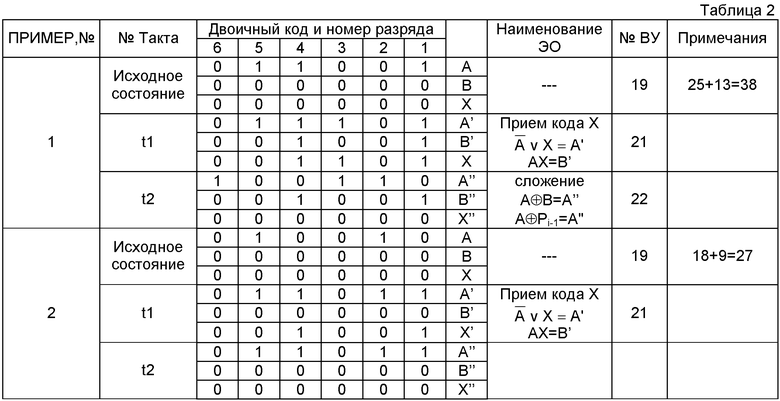

Варианты получения Si, Pi при различных значениях Ai, Bi, Pi-1. приведены в таблице 1.

В таблице 2 переведены примеры выполнения сложения кодов.

Таким образом, предложенные способ и устройство сложения двоичных кодов обеспечивают повышение быстродействия операции сложения по сравнению с прототипом в 1,5-3 раза, при тех же затратах оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ДВОИЧНЫХ КОДОВ | 2010 |

|

RU2410746C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| СПОСОБ И УСТРОЙСТВО СЧЕТА ИМПУЛЬСОВ | 2013 |

|

RU2538949C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ЕДИНИЦ | 2014 |

|

RU2540787C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2014 |

|

RU2551414C1 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и устройствах цифровой автоматики. Техническим результатом является повышение быстродействия. Устройство содержит в каждом разряде два RS-триггера, восемь элементов И, четыре элемента ИЛИ, четыре элемента НЕ. 2 н.п. ф-лы, 1 ил., 2 табл.

1. Способ сложения двоичных кодов, заключающийся в последовательном выполнении элементарных операций приема кода второго слагаемого, формирования сигнала переноса в каждом разряде и формирования суммы в первых триггерах, отличающийся тем, что до начала выполнения операции в первых триггерах всех разрядов хранят первое слагаемое, вторые триггеры всех разрядов устанавливают в нуль, второе слагаемое поступает во все разряды по информационным входам, по первому временному такту одновременно поразрядно выполняют элементарные операции логического сложения и логического умножения первого и второго слагаемых, при этом результат логического сложения принимают в первые триггеры, а результат логического умножения заносят во вторые триггеры, одновременно формируют потенциалы вспомогательного и основного переносов во всех разрядах, при этом вспомогательный перенос формируют выполнением операции логического умножения первого слагаемого, второго слагаемого и входа управления приемом кода второго слагаемого, основной перенос формируют выполнением операции логического умножения значения, полученного как результат выполнения операции логического сложения значений основного и вспомогательного переносов, выработанных в младшем разряде, и значения логического умножения текущего разряда, сохраненного во втором триггере, и значения, полученного как результат выполнения операции логического сложения первого слагаемого и результата выполнения операции логического умножения второго слагаемого и входа управления приемом кода второго слагаемого, по второму временному такту при наличии основного переноса из младшего разряда или единичного значения кода второго триггера формируют суму i-го разряда путем инвертирования кода первого триггера, при этом сигнал инвертирования упомянутого триггера вырабатывается как результат логического умножения выходов четвертого элемента ИЛИ, пятого элемента НЕ и второго входа управления инвертированием первого триггера, в случае одновременного поступления основного переноса из младшего разряда и сигнала с выхода второго триггера инвертирование первого триггера запрещается.

2. Устройство сложения двоичных кодов, выполненное на элементах И, ИЛИ, НЕ, содержащее в каждом двоичном разряде первый и второй RS-триггеры, пять элементов И, два элемента ИЛИ, три элемента НЕ, информационный вход, первый вход управления приемом кода второго слагаемого, второй вход управления, при этом первый вход управления подключен к первому входу первого элемента И, второй вход которого соединен с информационным входом, отличающееся тем, что в каждый разряд введены три элемента И, два элемента ИЛИ, элемент НЕ, при этом в каждом разряде информационный вход соединен с первым входом первого элемента И, второй вход которого подключен к первому входу управления приемом кода второго слагаемого, выход первого элемента И соединен с первыми входами первого и третьего элементов ИЛИ и второго элемента И, выход второго элемента И подключен к единичному входу второго RS-триггера, второй вход управления инвертированием первого RS-триггера подключен к первому входу третьего элемента И, второй и третий входы которого связаны с выходами четвертого элемента ИЛИ и четвертого элемента НЕ соответственно, выход третьего элемента И соединен со вторым входом первого элемента ИЛИ, выходы третьего элемента И и первого элемента ИЛИ соединены с первыми входами шестого и седьмого элементов И соответственно, вторые входы которых подключены к входу и выходу первого элемента НЕ, выходы шестого и седьмого элементов И через второй и третий элементы НЕ соединены с нулевым и единичным входами первого RS-триггера, единичный выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого связан с выходом шестого элемента И, выход второго элемента ИЛИ соединен с первым входом восьмого элемента И, второй вход которого подключен к выходу третьего элемента НЕ, подключение выхода шестого элемента И через второй элемент ИЛИ к первому входу восьмого элемента И, обеспечивает задержку выхода сигнала с восьмого элемента И при переключении первого RS-триггера из единичного состояния в нулевое; подключение выхода третьего элемента НЕ к второму входу восьмого элемента И обеспечивает задержку включения восьмого элемента И при переключении первого RS-триггера из нуля в единицу, упомянутая временная задержка сигнала с выхода восьмого элемента И равняется длительности сигнала управления инвертированием первого RS-триггера, выход восьмого элемента И соединен со вторым входом третьего элемента ИЛИ, входом первого элемента НЕ и вторым входом второго элемента И, единичный выход второго RS-триггера соединен с первыми входами четвертого элемента ИЛИ и пятого элемента И, третий вход четвертого элемента ИЛИ и второй вход пятого элемента И i-го разряда соединены с выходом четвертого элемента И (i-1)-го разряда, второй вход четвертого элемента ИЛИ i-го разряда является входом вспомогательного переноса в старший разряд и соединен с выходом второго элемента И (i-1)-го разряда, выходы третьего и четвертого элементов ИЛИ соединены с входами четвертого элемента И, выход которого является входом основного переноса в старший разряд, выход пятого элемента И подключен к входу четвертого элемента НЕ.

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2264646C2 |

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

| DE 3844384 A1, 05.07.1990 | |||

| DE 3904389 A1, 06.09.1990 | |||

| US 3822378 A, 02.07.1974. | |||

Авторы

Даты

2010-04-27—Публикация

2008-05-04—Подача