1

Изобретение относится к вычислительной технике и может использовано в процессорах ЭВМ.

Цель изобретения - повышение быстродействия двоично-десятичного сумматора ,

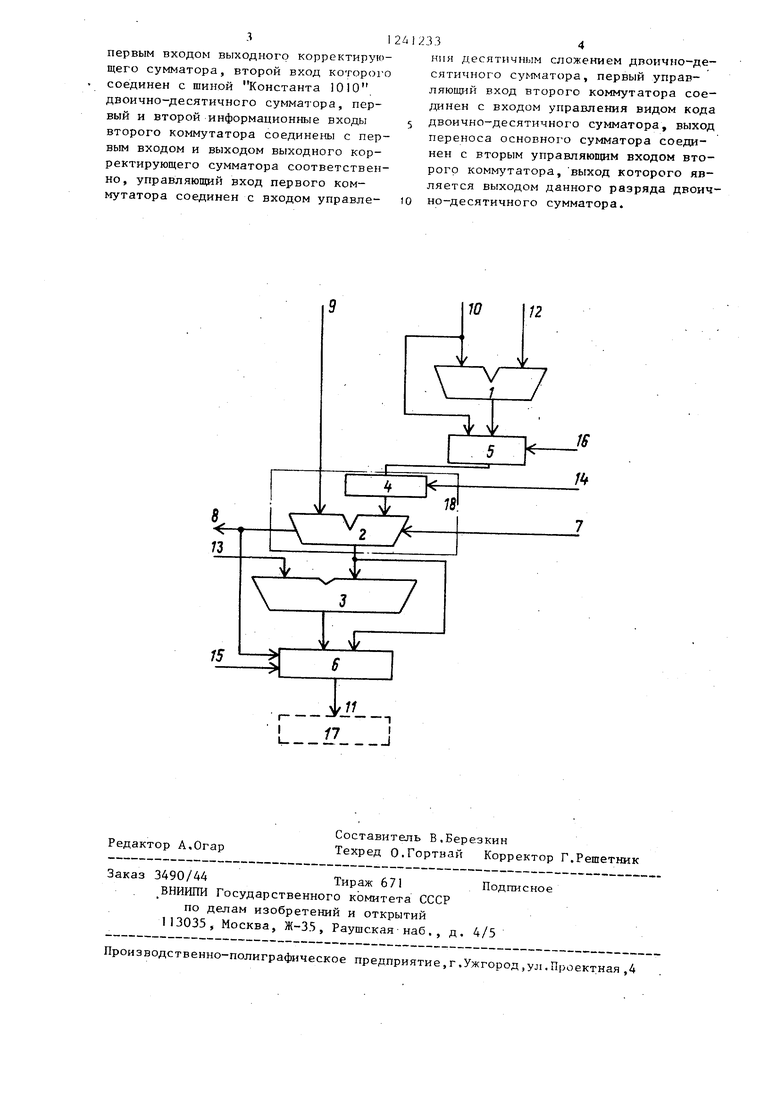

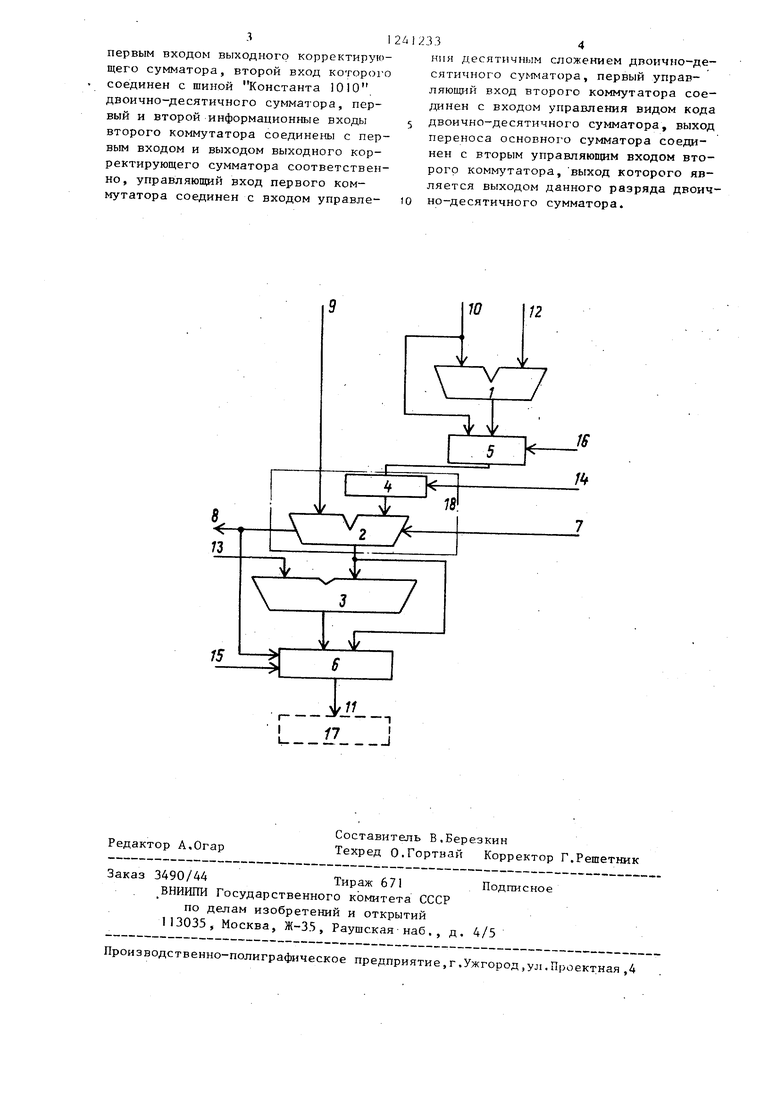

На чертеже приведена функциональная схема одного разряда двоично-десятичного сумматора.

Двоично-десятичный сумматор содержит в каждом разряде входной корректирующий сумматор 1, основной сумматор 2, выходной корректирующий сумматор 3, узел 4 управляющий инверсии, комму-тйттары 5 и 6, вход 7 переноса, выход 8 переноса, вход 9 первого операнда данного разряда, вход 10 второго операнда данного разряда и выход 11 результата данного разряда. Двоично-десятичный сумматор содержит также шину 12 Константа 0110, шину 13 Константа 1010, вход 14 управления видом операции, вход 15 управления видом кода и вход 16 управления десятичным сложением. Результаты двоично-десятичного сумматора могут быть.выведены на регистр 17. Сумматор 2 и узел 4 могут быть выполнены в виде единого арифметико- логического блока 18,

Дпя операции сложения десятичных данных, представленных в коде 8421, необходимы две коррекции. Для этого в каждой тетраде второго операнда, поступающей по входу 10, на сумматоре 1 добавляется, 6 (0110), Полученный на сумматоре результат по сигналу с шины 16 поступает на вход сумматора 2, где складывается с первым операндом с учетом входного переноса.. На выход II результат будет передан в зависимости от выходного переноса сумматора 2. Если перенос отсутствует, то через коммутатор 6 на выход 11 передается информация с выхода сумматора 3, где к полученной сумме сумматора 2 добавляется 10 (вычитается 6). При наличии пере- носа из сумматора 2 на выход 11 передается информация с выхода сумматора 2.

При операции десятичного вычитания второй операнд участвует в обработке на сумматоре 2 как дополнение, которое получается уже с избытком 6. Поэтому добавления 6 к второму операнду не производится, т.е. через коммутааор 5 передается второй

332

операнд с входа 10 по отсутствии управляющего сигнала на 16. После д)зоичной операции вычитания, как и при десятичном сложении, если не возник перенбс из данной тетрады, от результата вычитается 6 (добавляет ся 10) с разрывом переносов между тетрадами .(за результат принимается значение на выходе сумматоре 3). В противном случае за результат принимается значение на выходе сумматора 2.

При выполнении операции двоичного сумм - рования на входе 15 отсутству- ет управляющий сигнал, поэтому при получении результатов этой операции минуются сумматоры 1 и 3.

0

5

0

5

0

5

0

5

Формула изобретения

Двоично-десятичный сумматор, содержащий .в каждом разряде входной корректирующий сумматор, основной сумматор , выходной корректирующий сумматор , узел управляемой инверсии, причем первый вход входного- корректирующего сумматора соединен с шиной Константа 0110 двоично-десятичного сумматора, выход узла управляемой инверсии соединен с первым информационным входом основного сум- матбра, вход переноса основного сумматора соединен с входом переноса в данный разряд двоично-десятичного сумматора, вьгх;од переноса основного сумматора соединен с выходом переноса из данного разряда двоично-десятичного сумматора, управляющий вход узла управляемой,инверсии соединен с входом управления видом операции двоично-десятичного сумматора, о т- личающийся тем, что, с целью повышения быстродействия, в каждый раз ряд двоично-десятичного сумматора введены два ком гутатора, причем второй информационный вход основного сумматора соединен с входом первого операдда данного разряда двоично-десятичного сумматора, вход второго операцца данного разряда которого соединен с вторым входом входного корректирующего сумматора и первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом входного корректирующего сумматора, . а выход подключен к информационному входу уз.па управляемой инверсии, выход основного сумматора соединен с

3

первым входом выходного корректирующего сумматора, второй вход которо1Ю соединен с шиной Константа 1010 двоично-десятичного сумматора, первый и второй информационные входы второго коммутатора соединены с первым входом и выходом выходного корректирующего сумматора соответственно, управляющий вход первого коммутатора соединен с входом управле-

а

73

/

. jrj/

/7

Редактор А.Огар

3490/Д4Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-33, Раушская наб., д. 4/5

По

Производственно-полиграфическое предприятие,г.Ужгород,ул,Проектная ,4

334

НИН десятичным сложением дпоично-де- сятичного сумматора, первый управляющий вход второго ком1иутатора сое- ;5чнен с входом управления видом кода двоично-десятичного сумматора, выход переноса основного сумматора соединен с вторым управляющим входом второго коммутатора, выход которого является выходом данного разряда двоично-десятичного сумматора.

W

12

лт/

75

V

2/

Составитель В.Березкин

Техред О.Гортвай Корректор Г.Решетник

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| УСТРОЙСТВО для СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1972 |

|

SU332459A1 |

| Суммирующее устройство с контролем | 1983 |

|

SU1140112A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

Изобретение относится к области вычислительной техники. Его целью - является повышение быстродействия. Предлагаемый двоично-десятичный сумматор отличается от прототипа наличием двух коммутаторов-. Изобретение может быть использовано в процессоре ЭВМ. 1 ил. tc i ьо со со

| МЕХАНИЧЕСКАЯ ТРАМБОВКА ДЛЯ ИЗГОТОВЛЕНИЯ ИСКУССТВЕННЫХ ЖЕРНОВОВ | 1923 |

|

SU1033A1 |

| В.А.Комарниц- кого, Г.П.Сорокина | |||

| М.гМашинострое- ние, 1982, с.69, рис | |||

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-30—Публикация

1984-04-16—Подача