Изобретение относится к цифровым системам обработки сигналов и предназначено для перепаковки потоков данных.

При обработке информации на компьютерах часто возникает задача ввода данных по нескольким каналам, причем их число может оперативно меняться, например, от одного до восьми, что требует перепаковки данных.

Известны и широко используются такие устройства перепаковки потоков данных, как мультиплексоры и демультиплексоры [1], реализуемые на специализированных интегральных схемах или на ПЛИС.

Также в качестве аналогов можно привести выделенные схемные компоненты ISERDES, входящие в состав ПЛИС семейства Virtex4 фирмы Xilinx [2]. Их основным элементом являются сдвиговые регистры. Компонент ISERDES предусматривает перепаковку из 1 потока в 2-8 потоков. Эти схемные компоненты имеют существенные недостатки. Эти компоненты принципиально требуют жесткой синхронизации входных и выходных потоков. Для их работы требуется две кратные тактовые частоты. Для ISERDES выходная тактовая частота должна быть в 2-8 раз меньше входной (в зависимости от числа входных потоков). Эти компоненты обеспечивают лишь распараллеливания одного потока, поступающего на ПЛИС, на несколько потоков. Однако эти компоненты не обеспечивают решение задачи ввода нескольких параллельных потоков.

В качестве наиболее близкого к заявленному технического решения можно привести устройство, содержащее микросхемы SN74LV164 фирмы Texas Instruments [3], которые позволяют выполнить перепаковку сигналов из одного потока в 8, логический блок с входом тактового сигнала и восемью входами для данных, 64-разрядный регистр FIFO, имеющий вход управления и выходы, соединенные с соответствующими входами контроллера системной шины, соединенного с системной шиной ПЭВМ.

В известном устройстве на входы подается тактовый сигнал, частота которого соответствует частоте вводимых данных. Контроллер системной шины компьютера передает данные от регистра FIFO в системную шину.

Далее с помощью восьми микросхем SN74LV164 8 входных потоков данных распараллеливаются на 64 потока меньшей скорости. Для синхронизации работы микросхем SN74LV164 и записи данных в регистр FIFO используется тактовый сигнал частотой в 1/8 от частоты входного тактового сигнала, вырабатываемый счетчиком.

Недостатком этого устройства является фиксированная структура перепаковки.

Техническим результатом настоящего изобретения является осуществление перепаковки при любом числе входных потоков от 1 до 8 и без необходимости жесткой синхронизации входных потоков по тактовым частотам.

Предлагается устройство перепаковки потоков данных, решающее задачу путем промежуточного преобразования нескольких входных потоков данных, количество которых может меняться от 1 до 8, в единый 64-разрядный поток. Такой поток пригоден для обмена данных с буфером контроллера системной шины ПЭВМ, что и обеспечивает ввод данных в ПЭВМ.

Технический результат достигается тем, что в предлагаемом устройстве перепаковки потоков для ввода данных, имеющем логический блок с входом тактового сигнала и восемью выходами для данных, 64-разрядный регистр FIFO, выходы которого соединены с соответствующими входами контроллера системной шины ПЭВМ, соединенного с системной шиной, согласно изобретению в логический блок введены адаптивный демультиплексор, регистр-фиксатор с 448 ячейками, мультиплексор, 8 распределителей потоков данных, блок управления, при этом выходная 64-разрядная шина мультиплексора соединена с соответствующей входной шиной регистра FIFO, выходы регистра-фиксатора объединены в шины по 64 разряда, которые соединены с соответствующими входами мультиплексора, а входы регистра-фиксатора соединены с выходами адаптивного демультиплексора, 32 выхода распределителей потоков данных соединены с 32 входами адаптивного демультиплексора, а входы распределителей соединены с соответствующими входами данных, на один вход блока управления подается тактовый сигнал, на другой вход подается сигнал, соответствующий числу входных каналов, которое может меняться от 1 до 8; причем с выходов блока управления на вход управления регистра FIFO подается сигнал записи, на входы управления мультиплексора подается сигнал адресации 64-разрядных групп данных, на входы управления регистра-фиксатора подается сигнал четверти частоты входного тактового сигнала и сигнал адресации для записи данных в регистр-фиксатор, на вход управления адаптивного демультиплексора подается сигнал адресации, на входы управления распределителей данных подаются сигналы входной тактовой частоты и четверти входной тактовой частоты.

Дальнейшее описание поясняется с помощью следующих фигур.

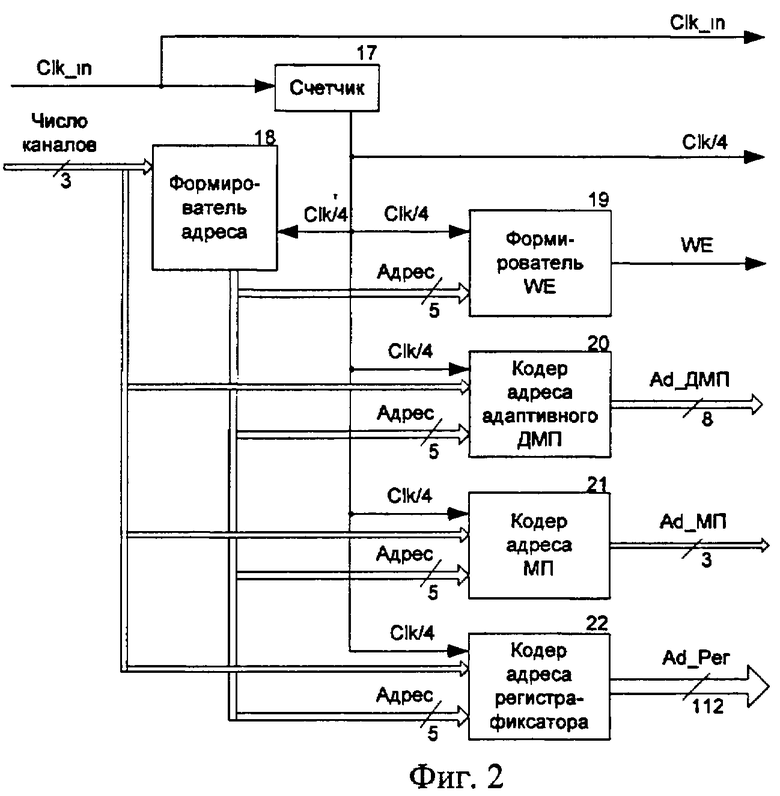

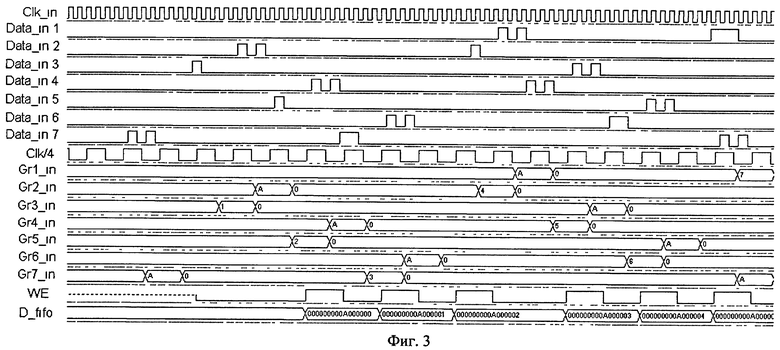

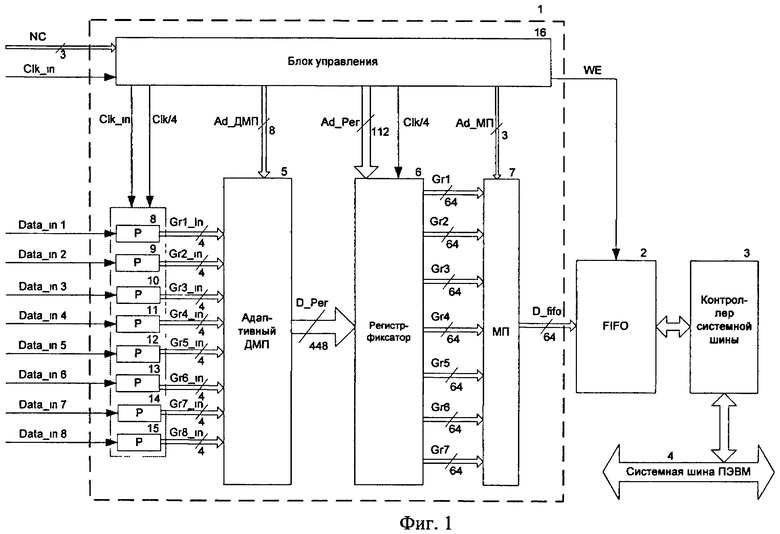

Фиг.1 - Структурная схема предлагаемого устройства для ввода данных. Фиг.2 - Структурная схема блока управления вводом. Фиг.3 - Временные диаграммы работы предлагаемого устройства для случая ввода данных по 7 каналам.

Устройство может быть реализовано следующим образом. Устройство перепаковки потоков для ввода данных содержит логический блок 1 с входом тактового сигнала Clk_in, входом для числа входных каналов NC и восемью входами данных, 64-разрядный регистр FIFO 2, выходы которого соединены с соответствующими входами контроллера системной шины 3, соединенного с системной шиной ПЭВМ 4. Логический блок 1 содержит адаптивный демультиплексор 5, регистр-фиксатор 6 с 448 ячейками, мультиплексор 7, 8 распределителей 8..15 потоков данных, блок управления 16, при этом выходная 64-разрядная шина мультиплексора 7 соединена с соответствующей входной шиной D_fifo регистра FIFO 2, выходы регистра-фиксатора 6 объединены в шины Gr1..Gr7 по 64 разряда, которые соединены с соответствующими входами мультиплексора 7, а входы D_Per регистра-фиксатора 6 соединены с выходами адаптивного демультиплексора 5, 8 4-разрядных выходов Gr1_in..Gr8_in распределителей потоков данных 8..15 соединены с соответствующими входами адаптивного демультиплексора, а входы объединителей 8.. 15 соединены с соответствующими входами данных Data_in1..Data_in8, на один вход блока управления 16 подается тактовый сигнал Clk_in, на другой вход подается сигнал NC, соответствующий числу входных каналов, которое может меняться от 1 до 8; причем с выходов блока управления на вход управления регистра FIFO 2 подается сигнал записи WE, на входы управления адаптивного демультиплексора 5 подается сигнал Аd_ДМП адресации 4-разрядных групп данных Grl_in..Gr7_in, на входы управления регистра-фиксатора 6 подается сигнал четверти входной тактовой частоты Clk/4 и сигнал адресации Ad_Per, на вход управления мультиплексора 7 подается сигнал адресации Ad_MП, на входы управления распределителей потоков данных 8.. 15 подаются сигналы входной тактовой частоты Clk_in и четверти входной тактовой частоты Clk/4.

На входы устройства подаются данные Data_inl..Data_in8, код числа каналов вывода NC (от 1 до 8) и тактовый сигнал Clk_in.

Логический блок 1 обеспечивает преобразование входного n-разрядного потока данных (n=1, 2…8) в 64-разрядный поток для ввода в ПЭВМ путем последовательной перезаписи данных в регистр FIFO 2, контроллер 3 системной шины и системную шину ПЭВМ 4.

Распределители Р 8…15 потоков предназначены для распараллеливания каждого входного потока Data_in на 4 потока Gr_in.

Адаптивный демультиплексор (ДМП) 5 производит демультиплексирование 4n-разрядных данных Gr_in по 448-разрядной входной шине D_Per регистра-фиксатора 6, предназначенного для промежуточного хранения данных.

Мультиплексор (МП) 7 производит мультиплексирование данных, получаемых от выходных шин Grl..Gr7 регистра-фиксатора 6, чтобы передать их в 64-разрядную шину для записи в регистр FIFO 2.

Контроллер 3 системной шины передает данные из регистра FIFO 2 в системную шину компьютера 4.

Блок управления 16 вырабатывает сигналы, необходимые для управления всеми остальными элементами логического блока 1 и регистра FIFO 2.

На входы блока 16 управления подаются тактовый сигнал Clk_in и код числа каналов при выводе NC (трехразрядное двоичное число).

Счетчик 17 используется для деления частоты входного тактового сигнала на 4.

Формирователь 18 адреса задает универсальный адрес для формирователя 19 сигнала записи WE, кодера 20 адреса адаптивного ДМП 5, кодера 21 адреса МП 7 и кодера 22 адреса регистра-фиксатора 6.

Формирователь 19 WE предназначен для формирования сигнала разрешения записи 64 бит данных в FIFO 2.

Кодер 20 адреса адаптивного ДМП представляет собой комбинационную логическую схему и формирует адрес для адаптивного ДМП 5.

Кодер 21 адреса МП представляет собой комбинационную логическую схему и формирует адрес для МП 7.

Кодер 22 адреса регистра-фиксатора представляет собой комбинационную логическую схему и предназначен для записи данных в 4-разрядную ячейку регистра-фиксатора 6.

Временные диаграммы работы устройства для ввода данных по 7 каналам представлены на фиг.3. На диаграммах использовано обычное обозначение логических единиц и нулей в виде соответствующих двух уровней напряжения. Здесь использованы такие же обозначения сигналов, что на структурной схеме предлагаемого устройства для вывода данных (фиг.1).

Из временных диаграмм видно, что 7 входных потоков Data_in преобразуются в 7 четырехразрядных потоков Gr_in, и затем в выходную возрастающую последовательность 64-разрядных данных D_fifo (которая является наглядной реализацией входных данных). Сигналы Clk/4 и WE формируются из входного тактового сигнала Clk_in.

Описанное устройство обеспечивает выполнение операций перепаковки данных из 1…8 потоков в 64 потока (требуемые для ввода данных в системную шину ПЭВМ) при любой частоте входных тактовых сигналов.

Таким образом выполняется поставленная цель решения сложной задачи перепаковки, причем исключительно простыми техническими средствами. Все преобразования цифровых сигналов осуществляются средствами логической схемотехники. Поэтому устройство перепаковки может быть легко реализовано как на дискретных логических элементах, так и на основе программируемых логических интегральных схем (ПЛИС).

Эффективность предлагаемого технического решения подтверждена экспериментально: соответствующее устройство перепаковки реализовано на ПЛИС серии XC4VFX20 семейства Virtex 4 фирмы Xilinx и проверено на функционирование в широком диапазоне тактовых частот (до 600 МГц).

Источники информации

[1] Калабеков Б.А. Цифровые устройства и микропроцессорные системы. - М.: Горячая линия - Телеком, 2003, с.123-126.

[2] Low-Voltage Logic Data Book. - Texas Instruments, 1996, p.10-47-10-57.

[3] Virtex-4 Libraries Guide for HDL Designs. - Xilinx, 2005, p.153-160, p.227-232.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПЕРЕПАКОВКИ ПОТОКОВ ДЛЯ ВЫВОДА ДАННЫХ | 2009 |

|

RU2413277C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| СИСТЕМА И СПОСОБ ПОДДЕРЖАНИЯ ВРЕМЕННОЙ СИНХРОНИЗАЦИИ В СЕТИ ЦИФРОВОГО ВИДЕО | 1998 |

|

RU2222116C2 |

| СИСТЕМА И СПОСОБ ПЕРЕДАЧИ ЦИФРОВОГО ВИДЕОСИГНАЛА И ДАННЫХ ЧЕРЕЗ КАНАЛ СВЯЗИ | 1998 |

|

RU2220512C2 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1476434A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ | 2012 |

|

RU2514092C2 |

Изобретение относится к цифровым системам обработки сигналов и предназначено для перепаковки потоков данных. Техническим результатом является осуществление перепаковки при любом числе входных потоков от 1 до 8 без необходимости жесткой синхронизации входных потоков по тактовым частотам. В устройстве имеется логический блок с входом тактового сигнала и восемью входами для данных, 64-разрядный регистр FIFO, входы которого соединены с соответствующими входами контроллера системной шины ПЭВМ, соединенного с системной шиной. В логический блок введены мультиплексор, регистр-фиксатор с 448 ячейками, адаптивный демультиплексор, 8 распределителей потоков данных, блок управления, при этом выходная 64-разрядная шина мультиплексора соединена с соответствующей входной шиной регистра FIFO, выходы регистра-фиксатора объединены в шины по 64 разряда, которые соединены с соответствующими входами мультиплексора, а входы регистра-фиксатора соединены с входами адаптивного демультиплексора, 32 выхода распределителей потоков данных соединены с 32 входами адаптивного демультиплексора, а входы распределителей соединены с соответствующими входами данных, на один вход блока управления подается тактовый сигнал, на другой вход подается сигнал, соответствующий числу входных каналов, которое может меняться от 1 до 8. 3 ил.

Устройство перепаковки потоков для ввода данных, имеющее логический блок с входом тактового сигнала и восемью входами для данных, 64-разрядный регистр FIFO, выходы которого соединены с соответствующими входами контроллера системной шины ПЭВМ, соединенного с системной шиной, отличающееся тем, что в логический блок введены мультиплексор, регистр-фиксатор с 448 ячейками, адаптивный демультиплексор, 8 распределителей потоков данных, блок управления, при этом выходная 64-разрядная шина мультиплексора соединена с соответствующей входной шиной регистра FIFO, выходы регистра-фиксатора объединены в шины по 64 разряда, которые соединены с соответствующими входами мультиплексора, а входы регистра-фиксатора соединены с выходами адаптивного демультиплексора, 32 выхода распределителей потоков данных соединены с 32 входами адаптивного демультиплексора, а входы распределителей соединены с соответствующими входами данных, на один вход блока управления подается тактовый сигнал, на другой вход подается сигнал, соответствующий числу входных каналов, которое может меняться от 1 до 8; причем с выходов блока управления на вход управления регистра FIFO подается сигнал записи, на входы управления мультиплексора подается сигнал адресации 64-разрядных групп данных, на входы управления регистра-фиксатора подается сигнал четверти входной тактовой частоты и сигнал адресации для записи в регистр-фиксатор, на вход управления адаптивного демультиплексора подается сигнал адресации, на входы управления распределителей потоков данных подаются сигналы входной тактовой частоты и четверти входной тактовой частоты.

| Многоканальное устройство для ввода информации | 1988 |

|

SU1569815A1 |

| Многоканальное устройство для обмена информацией | 1988 |

|

SU1564637A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| СПОСОБ ФОРМИРОВАНИЯ ПАКЕТОВ ДАННЫХ ИЗМЕРЕНИЙ БЕСКАБЕЛЬНОЙ ТЕЛЕМЕТРИЧЕСКОЙ СИСТЕМЫ В ПРОЦЕССЕ БУРЕНИЯ СКВАЖИНЫ | 2008 |

|

RU2394257C1 |

Авторы

Даты

2011-03-20—Публикация

2009-09-17—Подача