1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах для прдграммного логического управления технологическими процессами.

Цель изобретения - повышение производительности устройства.

Сущность изобретения состоит в повышении производительности устройства за счет введения режима адаптивней

Йь

адрессации массива данных, описывающих закон управления технологическим оборудованием, путем задания в соответствии с сигналами состояния технологического оборудования требуемого варианта адрессации подмножеств массива данных, выработки начальных адресов подмножества массива данных, соответствующих данному варианту адресации и обработки блоком задания подмножества данных, меньшего по мощности исходного без нарушения информационной целостности системы.

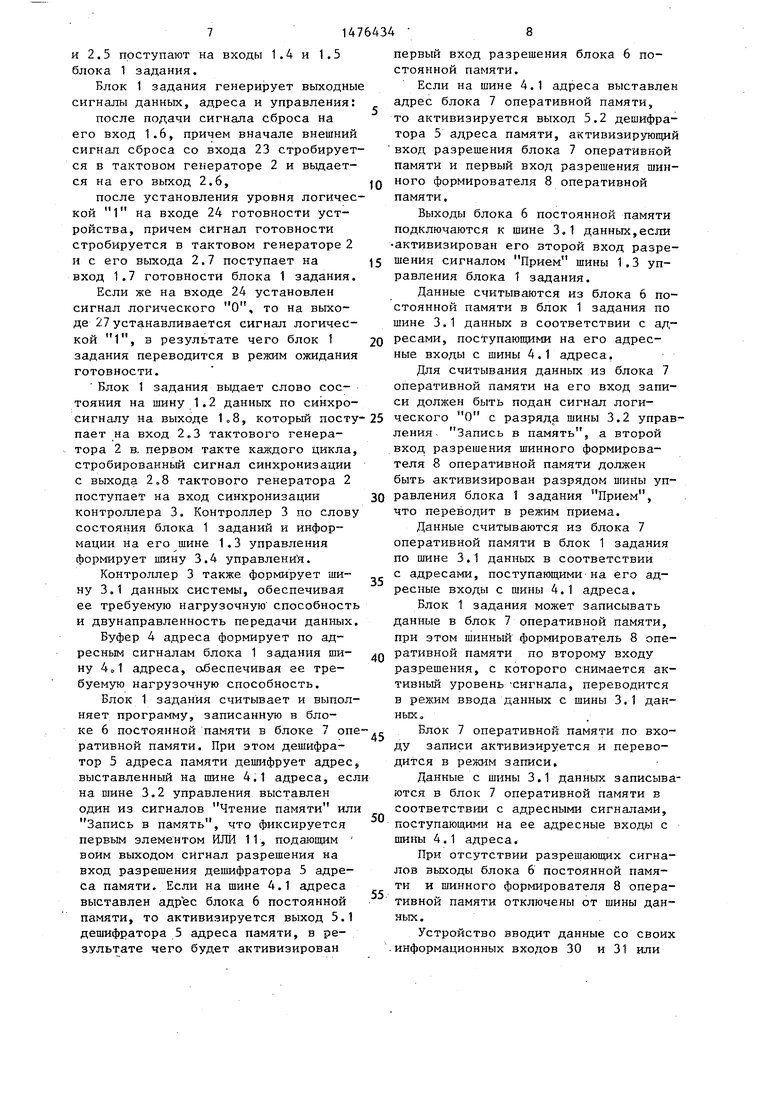

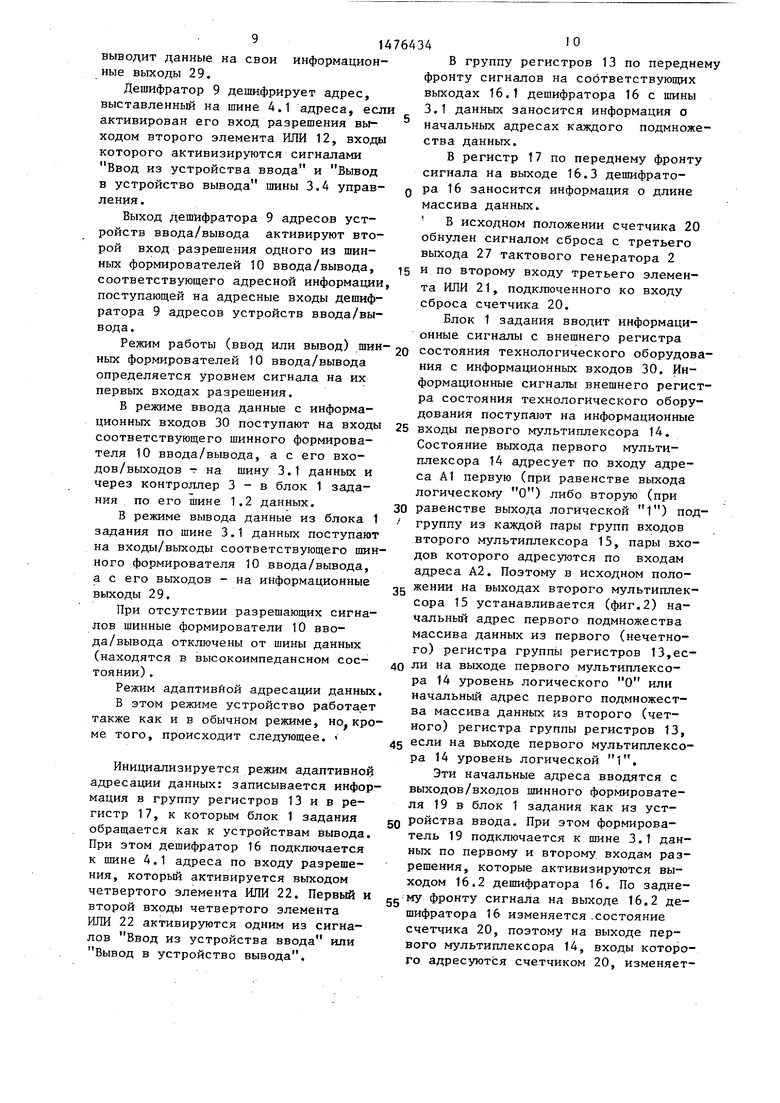

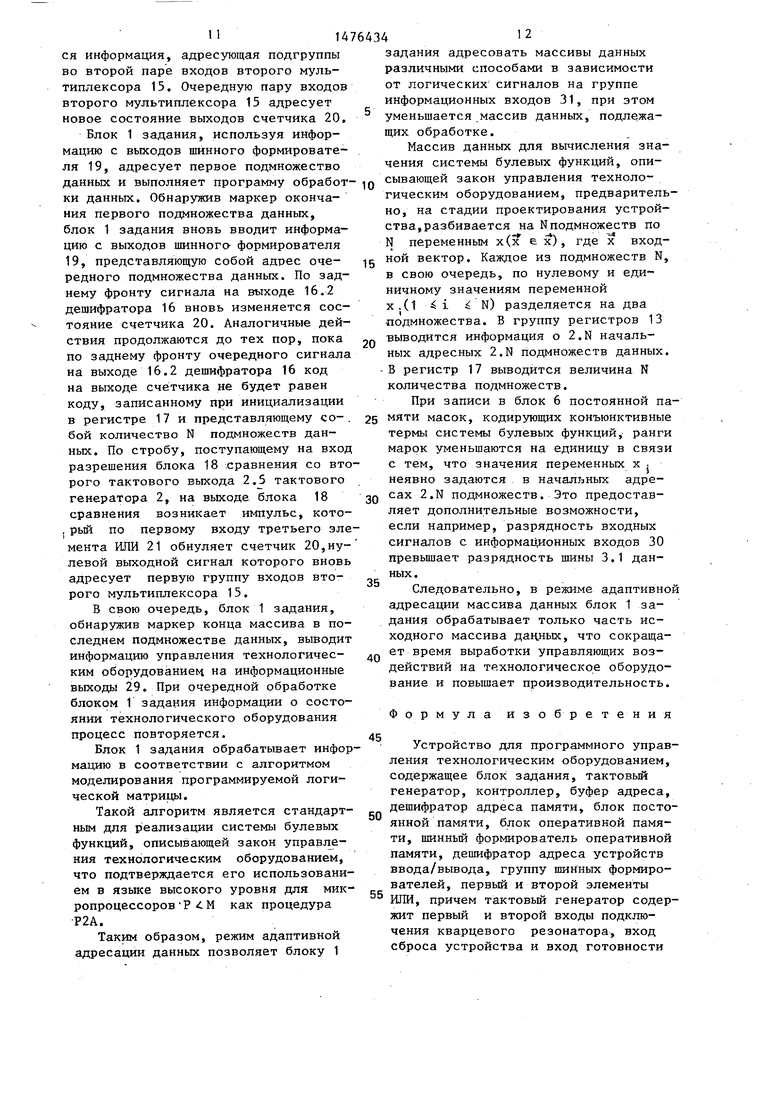

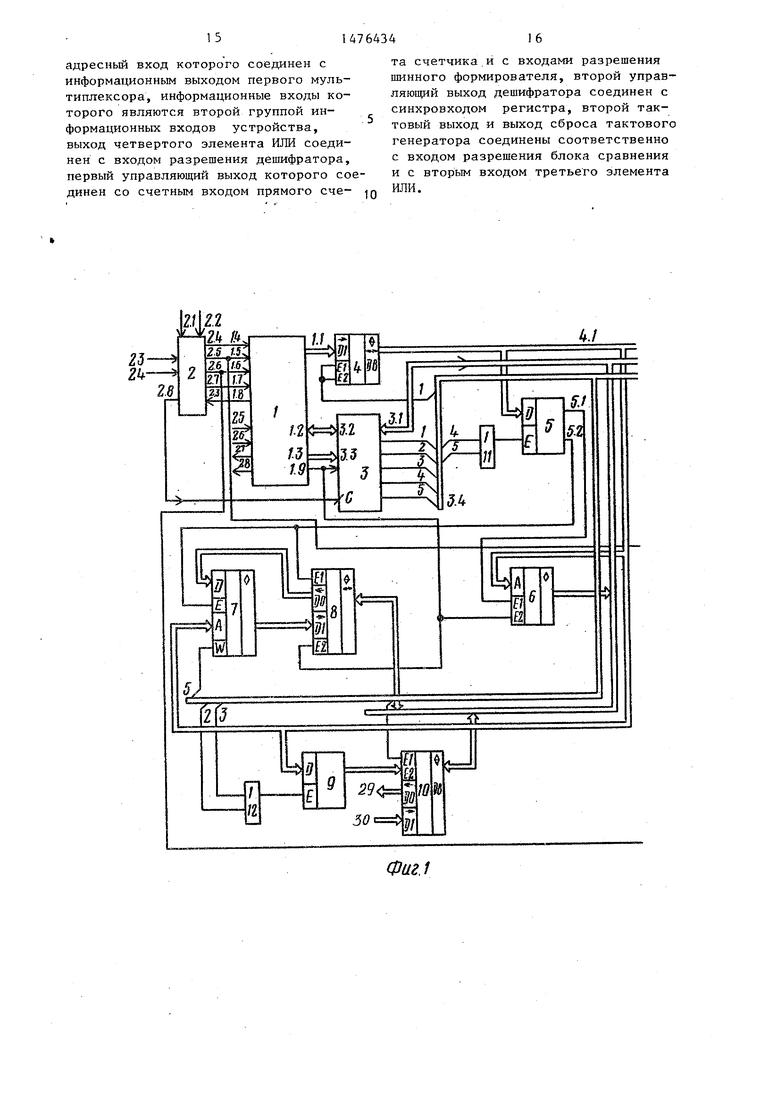

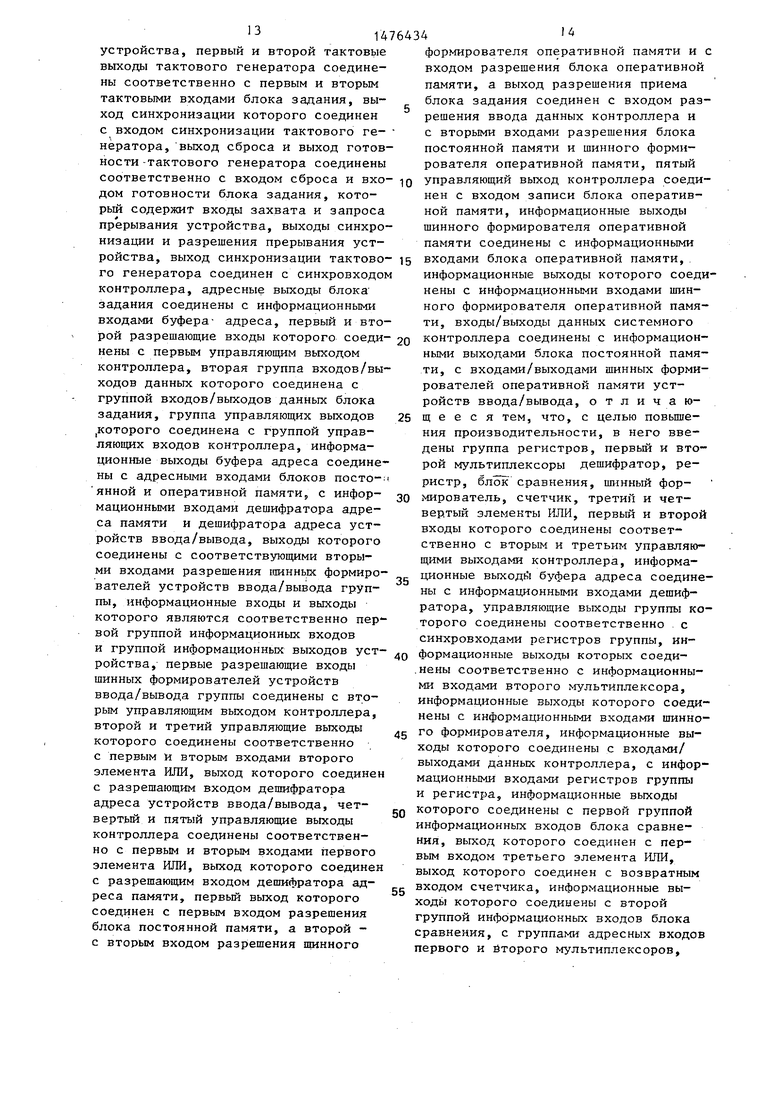

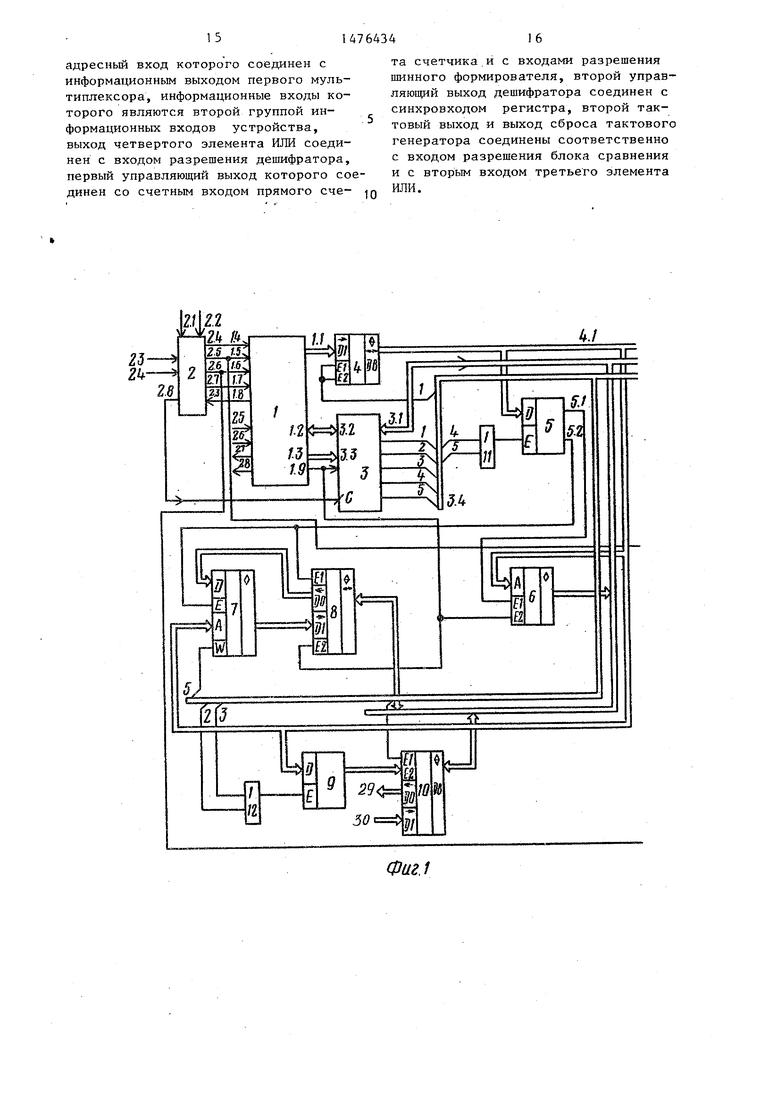

На фиг.1 и 2 изображена функциональная схема предлагаемого устрой- ства; на фиг.З - временные диаграммы, поясняющие работу устройства.

Устройство (фиг.1) содержит блок 1 задания, содержащий группу адресных выходов 1.1, группу входов/выхо- дов 1„2 данных, группу выходов 1.3 управления, первый 1.4 и второй 1.5 тактовые входы, вход 1.6 сброса, вход 1.7 готовности, выход 1.8 синхронизации и выход 1.9 разрешения приема, тактовый генератор 2, содержащий первый 2.1 и второй 2.2 входы подключения кварцевого резонатора, входы 2.3 синхронизации, первый 2.4 и второй 2.5 тактовые вхо ды, выход 2.6 сброса, выход 2.7 готовности, выход 2/8 синхронизации, контроллер 3, содержащий первую 3.1 и вторую 3.2 группы входов/выходов данных, группу входов 3.3 управления и группу выходов 3.4 управления, буфер 4 адреса, дешифратор 5 адреса памяти, блок б постоянной памяти, блок 7 оперативной памяти, шинный формирователь 8 оперативной памяти, дешифратор 9 адреса устройств ввода/ вывода, группу шинных формирователей 10 устройств ввода/вывода, первый 11 и второй 12 элементы ИЛИ, группу регистров 13, первый мультиплексор 14, второй мультиплексор 15, дешифратор 16, содержащий группу управляющих выходов 16.1, первый 16.2 и второй 16. управляющие выходы, регистр 17, блок 18 сравнения, шинный формирователь 19, счетчик 20, третий 21 и четвертый 22 элементы ИЛИ, вход 23 сброса, вход 24 готовности, вход 25 захвата и вход 26 запроса прерывания, выход 27 ожидания и выход 28 разрешения пр рывания, группу информационных выходов 29, первую 30 и вторую 31 группы информационных входов. I Блок 1 задания предназначен для формирования сигналов управления и массивов данных, принимаемых и вы- даваемых на внешние устройства.

Тактовый генератор 2 предназначен для формирования сигналов синхронизации блока 1 задания, контроллера 3 и сигналов сброса и готовности.

Контроллер 3 предназначен для организации двунаправленной передачи

Q ,, -

5

данных по шине данных и сигналов управления по шине управления.

Буфер 4 адреса предназначен для увеличения нагрузочной способности шины 4.1 адреса и для отключения своих входов/выходов от нее переводом в высокоимпедансное состояние по сигналу Подтверждение захвата на шине 3.4 управления, который поступает на первый и второй разрешающий вход.

Дешифратор 5 адреса памяти предназначен для дешифрации информации на шине 4.1 адреса системы по разрешающему сигналу на его входе Е управления формирования сигналов выборки кристалла для подключения блоков 6 и 7 постоянной или оперативной памяти соответственно.

Блок 6 постоянной памяти предназначен для долговременного хранения программ и данных, в том числе программы, реализующей закон управления технологическим оборудованием, представленным системой булевых Лункций, в том числе данных, кодирующих конъюнктивные члены системы булевых функций и представляющих выходные воздействия, соответствующие каждому конъюнктивному члену.

Блок 7 оперативной памяти предназначен для хранения программ данных и для их записи только во время работы устройства, а также для организации стека.

Режим работы определяется сочетанием разрешающего сигнала и сигнала записи.

Шинный формирователь 8 оперативной памяти предназначен для увеличения нагрузочной способности шины 3.1 данных и для организации подключенных к ней входов и выходов блока 7 оперативной памяти в зависимости от управляющих сигналов в следующих режимах:

Чтение памяти. При этом активированы первый и второй входы разрешения шинного Аормирователя 8 оперативной памяти. Данные с информационных выходов блока 7 оперативной памяти поступают на информационные входы шинного формирователя 8 оперативной памяти и с его информационных выходов на шину 3.1 данных.

Запись в память. При этом активирован первый вход разрешения шинного формирователя 8 оперативной памяти.

Данные с шины 3.1 данных поступают на его информационные входы/выходы, а с выходов - на входы данных блока 7 оперативной памяти.

Дешифратор 9 адресов устройств ввода/вывода предназначен для дешифрации по разрешающему сигналу адресной информации на шине 4.1 адреса. для подключения к шине 3.1 данных - соответствующего шинного формирователя 10 ввода/вывода по входам/выходам.

Шинные формирователи 10 ввода/вывода предназначены для увеличения нагрузочной способности шины 3.1 данных., для ввода данных с информационных входов 30 устройства. При этом активированы оба разрешающих входа одного из шинных формирователей 10 ввода/вывода, который выбран дешифратором 9 адресов устройства ввода/ вывода, а также для вывода данных из блока 1 задания на информационные выходы 29 устройства. При этом активирован второй разрешающий вход одного из шинных формирователей 10 ввода/вывода соответствующим выходам дешифратора 9 адресов устройств ввода/вывода и являющийся входом выбора кристалла.

Во всех остальных случаях входы/выходы шинных формирователей 10 ввода/ вывода находятся в высокоимпеданс- ном состоянии и не влияют на шину 3. данных.

Группа регистров 13 предназначена для записи, хранения и считывания начальных адресов подмножеств массива данных.

Первый мультиплексор 14 предназначен для адресации своим выходом четных либо нечетных подгрупп из каждой пары групп входов второго мультиплексора 15 в зависимости от информации на его информационных 31 и адресных входах.

Второй мультиплексор 15 предназначен для подключения к входам шинного 19 формирователя выхода четного или нечетного регистра каждой пары регистров из группы регистров 13. Выходы пар регистров адресуются по адресным входам А2, а адресация внутри пар осуществляется по адресному ходу А1, управляемому первым мультиплексором 14,

Дешифратор 16 предназначен для выработки по адресной информации на

0

5

0

шине 4.1 адреса сигналов синхронизации регистров 13 и 17 при записи в них информации в режиме вывода по разрешающему сигналу и для подключения шинного формирователя 19 по первому и второму разрешающим входам к шине 3.1 данных.

Регистр 17 предназначен для записи и хранения кода длины массива данных.

Блок 18 сравнения предназначен для выработки синхронизируемого тактовым сигналом со второго тактового входа 2.5 тактового генератора 2 сигнала сброса счетчика 20 по окончанию обработки мультиплексором 15 массива данных.

Пинный формирователь 19 предназначен для подключения выходных сигналов второго мультиплексора 15 к ши- не 3.1 данных в режиме ввода по сигналу дешифратора 16 по первому и второму входам разрешения.

Счетчик 20 предназначен для под- 5 счета количества обращений блока 1 задания к шинному формирователю 19 за очередным отдельным адресом подмножества массива данных.

Вход 23 устройства предназначен для приема внешнего сигнала сброса.

Блок 24 устройства предназначен для приема внешнего сигнала готовности.

Вход4 25 устройства предназначен для приема внешнего сигнала захвата.

Вход 26 устройства предназначен для приема внешнего сигнала запроса прерывания.

Выход 27 предназначен для выдачи сигнала ожидания, при отсутствии на входе 24 сигнала логической 1.

Выход 28 предназначен для выдачи сигнала разрешения прерывания, если вход 26 неактивирован.

Выходы 29 предназначены для выдачи управляющих воздействий на технологическое оборудование.

Входы 30 и 31 предназначены для ввода информации с внешних регистров состояния технологического оборудования.

Устройство работает в обычном режиме и в режиме адаптивной адрес- сации данных.

Обычный режим работы.

В этом режиме работы тактовый генератор 2 (фиг.1) формирует две непрекращающиеся тактовые последовательности, которые с его выходов 2.4

0

5

0

5

0

5

и 2.5 поступают на входы 1.4 и 1.5 блока 1 задания.

Блок 1 задания генерирует выходные сигналы данных, адреса и управления:

после подачи сигнала сброса на его вход 1.6, причем вначале внешний сигнал сброса со входа 23 стробирует- ся в тактовом генераторе 2 и выдается на его выход 2.6,

после установления уровня логической 1 на входе 24 готовности устройства, причем сигнал готовности стробируется в тактовом генераторе 2 и с его выхода 2.7 поступает на вход 1.7 готовности блока 1 задания.

Если же на входе 24 установлен сигнал логического О, то на выходе 27 устанавливается сигнал логической 1, в результате чего блок 1 задания переводится в режим ожидания готовности.

Блок 1 задания выдает слово состояния на шину 1.2 данных по синхропервый вход разрешения блока 6 постоянной памяти.

Если на шине 4.1 адреса выставлен адрес блока 7 оперативной памяти, то активизируется выход 5.2 дешифратора 5 адреса памяти, активизирующий вход разрешения блока 7 оперативной памяти и первый вход разрешения шинного формирователя 8 оперативной памяти.

Выходы блока 6 постоянной памяти подключаются к шине 3.1 данных,если активизирован его второй вход разрешения сигналом Прием шины 1.3 управления блока t задания.

Данные считываются из блока 6 постоянной памяти в блок 1 задания по шине 3.1 данных а соответствии с адо ресами, поступающими на его адресные входы с шины 4.1 адреса.

Для считывания данных из блока 7 оперативной памяти на его вход записи должен быть подан сигнал логи

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Микропроцессорная система для программного управления технологическим оборудованием | 1988 |

|

SU1525678A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах для программного логического управления технологическими процессами. Цель изобретения - повышение производительности устройства. Поставленная цель достигается тем, что в известное устройство, содержащее блок задания, тактовый генератор, системный контроллер, буфер адреса, дешифратор адреса памяти, блок постоянной памяти, блок оперативной памяти, шинный формирователь оперативной памяти, дешифратор адреса устройств ввода/вывода, группу шинных формирователей устройств ввода/вывода, первый и второй элементы ИЛИ, введены группа регистров, первый и второй мультиплексоры, дешифратор, регистр, блок сравнения, шинный формирователь, счетчик, третий и четвертый элементы ИЛИ. Введение новых элементов и соответствующих им связей позволяет организовать режим адаптивной адресации массива данных, описывающих закон управления технологическим оборудованием, существенно сократить время выработки управляющих воздействий на технологическое оборудование и повысить производительность системы. 3 ил.

сигналу на выходе 1,8, который посту-25 ческого 0 с разряда шины 3.2 управления Запись в память, а второй вход разрешения шинного формирователя 8 оперативной памяти должен быть активизирован разрядом шины управления блока 1 задания Прием, что переводит в режим приема.

пает на вход 2,3 тактового генератора 2 в- первом такте каждого цикла, стробированный сигнал синхронизации с выхода 2„8 тактового генератора 2 поступает на вход синхронизации контроллера 3. Контроллер 3 по слову состояния блока 1 заданий и информации на его шине 1.3 управления формирует шину 3.4 управления.

Контроллер 3 также формирует шину 3.1 данных системы, обеспечивая ее требуемую нагрузочную способность и двунаправленность передачи данных.

Буфер 4 адреса формирует по адресным сигналам блока 1 задания шину 4„1 адреса, обеспечивая ее требуемую нагрузочную способность.

Блок 1 задания считывает и выполняет программу, записанную в блоке 6 постоянной памяти в блоке 7 оперативной памяти. При этом дешифратор 5 адреса памяти дешифрует адрес, выставленный на шине 4.1 адреса, есл на шине 3.2 управления выставлен один из сигналов Чтение памяти или Запись в память, что фиксируется первым элементом ИЛИ 11, подающим воим выходом сигнал разрешения на вход разрешения дешифратора 5 адреса памяти. Если на шине 4.1 адреса выставлен адрес блока 6 постоянной памяти, то активизируется выход 5.1 дешифратора 5 адреса памяти, в результате чего будет активизирован

5 ческого 0 с разряда шины 3.2 управ0

5

0

5

0

5

ления Запись в память, а второй вход разрешения шинного формирователя 8 оперативной памяти должен быть активизирован разрядом шины управления блока 1 задания Прием, что переводит в режим приема.

Данные считываются из блока 7 оперативной памяти в блок 1 задания по шине 3.1 данных в соответствии с адресами, поступающими на его адресные входы с шины 4.1 адреса.

Блок 1 задания может записывать данные в блок 7 оперативной памяти, при этом шинный формирователь 8 оперативной памяти по второму входу разрешения, с которого снимается активный уровень сигнала, переводится в режим ввода данных с шины 3.1 данных

Блок 7 оперативной памяти по входу записи активизируется и переводится в режим записи.

Данные с шины 3.1 данных записываются в блок 7 оперативной памяти в соответствии с адресными сигналами, поступающими на ее адресные входы с шины 4.1 адреса.

При отсутствии разрешающих сигналов выходы блока 6 постоянной памяти и шинного формирователя 8 оперативной памяти отключены от шины данных.

Устройство вводит данные со своих информационных входов 30 и 31 или

выводит данные на свои ные выходы 29.

Дешифратор 9 дешифрирует адрес, выставленный на шине 4.1 адреса, если активирован его вход разрешения выходом второго элемента ИЛИ 12, входы которого активизируются сигналами Ввод из устройства ввода и Вывод в устройство вывода шины 3.4 управления .

Выход дешифратора 9 адресов устройств ввода/вывода активируют второй вход разрешения одного из шинных формирователей 10 ввода/вывода, соответствующего адресной информации, поступающей на адресные входы дешифратора 9 адресов устройств ввода/вывода.

147643410

информацион- В группу регистров 13 по переднему фронту сигналов на соответствующих выходах 16.1 дешифратора 16 с шины 3.1 данных заносится информация о начальных адресах каждого подмножества данных.

В регистр 17 по переднему фронту сигнала на выходе 16.3 дешифрато- g pa 16 заносится информация о длине массива данных.

1 В исходном положении счетчика 20 обнулен сигналом сброса с третьего выхода 27 тактового генератора 2 15 и по второму входу третьего элемента ИЛИ 21, подключенного ко входу сброса счетчика 20.

Блок 1 задания вводит информационные сигналы с внешнего регистра

Режим работы (ввод или вывод) шин- 20 состояния технологического оборудованых формирователей 10 ввода/вывода определяется уровнем сигнала на их первых входах разрешения.

В режиме ввода данные с информационных входов 30 поступают на входы соответствующего шинного формирователя 10 ввода/вывода, а с его входов/выходов т на шину 3.1 данных и через контроллер 3 - в блок 1 задания по его шине 1.2 данных.

В режиме вывода данные из блока 1 задания по шине 3.1 данных поступают на входы/выходы соответствующего шинного формирователя 10 ввода/вывода, а с его выходов - на информационные выходы 29.

При отсутствии разрешающих сигналов шинные формирователи 10 ввода/вывода отключены от шины данных (находятся в высокоимпедансном состоянии) .

Режим адаптивйой адресации данных.

В этом режиме устройство работает также как и в обычном режиме, но,кроме того, происходит следующее.

Инициализируется режим адаптивной адресации данных: записывается информация в группу регистров 13 и в регистр 17, к которым блок 1 задания обращается как к устройствам вывода. При этом дешифратор 16 подключается к шине 4.1 адреса по входу разрешения, который активируется выходом

ния с информационных входов 30. Информационные сигналы внешнего регистра состояния технологического оборудования поступают на информационные 25 входы первого мультиплексора 14. Состояние выхода первого мультиплексора 14 адресует по входу адреса А1 первую (при равенстве выхода логическому О) либо вторую (при 30 равенстве выхода логической 1) под- 1 группу из каждой пары групп входов второго мультиплексора 15, пары входов которого адресуются по входам адреса А2. Поэтому в исходном поло- ос жении на выходах второго мультиплексора 15 устанавливается (фиг.2) начальный адрес первого подмножества массива данных из первого (нечетного) регистра группы регистров 13,ее- 40 ли на выходе первого мультиплексора 14 уровень логического О или начальный адрес первого подмножества массива данных из второго (четного) регистра группы регистров 13, 45 если на выходе первого мультиплексора 14 уровень логической 1.

Эти начальные адреса вводятся с выходов/входов шинного формирователя 19 в блок 1 задания как из уст- 50 ройства ввода. При этом формирователь 19 подключается к шине 3.1 данных по первому и второму входам разрешения, которые активизируются выходом 16.2 дешифратора 16. По заднечетвертого элемента ИЛИ 22. Первый и gg му фронту сигнала на выходе 16.2 девторой входы четвертого элемента ИЛИ 22 активируются одним из сигналов Ввод из устройства ввода или Вывод в устройство вывода.

шифратора 16 изменяется состояние счетчика 20, поэтому на выходе первого мультиплексора 14, входы которого адресуются счетчиком 20, изменяетния с информационных входов 30. Информационные сигналы внешнего регистра состояния технологического оборудования поступают на информационные входы первого мультиплексора 14. Состояние выхода первого мультиплексора 14 адресует по входу адреса А1 первую (при равенстве выхода логическому О) либо вторую (при равенстве выхода логической 1) под- группу из каждой пары групп входов второго мультиплексора 15, пары входов которого адресуются по входам адреса А2. Поэтому в исходном поло- жении на выходах второго мультиплексора 15 устанавливается (фиг.2) начальный адрес первого подмножества массива данных из первого (нечетного) регистра группы регистров 13,ее- ли на выходе первого мультиплексора 14 уровень логического О или начальный адрес первого подмножества массива данных из второго (четного) регистра группы регистров 13, если на выходе первого мультиплексора 14 уровень логической 1.

Эти начальные адреса вводятся с выходов/входов шинного формирователя 19 в блок 1 задания как из уст- ройства ввода. При этом формирователь 19 подключается к шине 3.1 данных по первому и второму входам разрешения, которые активизируются выходом 16.2 дешифратора 16. По заднему фронту сигнала на выходе 16.2 дешифратора 16 изменяется состояние счетчика 20, поэтому на выходе первого мультиплексора 14, входы которого адресуются счетчиком 20, изменяется информация, адресующая подгруппы во второй паре входов второго мультиплексора 15. Очередную пару входов второго мультиплексора 15 адресует новое состояние выходов счетчика 20. Блок 1 задания, используя информацию с выходов шинного формирователя 19, адресует первое подмножество

задания адресовать массивы данных различными способами в зависимости от логических сигналов на группе информационных входов 31, при этом уменьшается массив данных, подлежа щих обработке.

Массив данных для вычисления зн чения системы булевых функций, опи

данных и выполняет программу обработ- 10 сывающей закон управления технолоки данных. Обнаружив маркер окончания первого подмножества данных, блок 1 задания вновь вводит информацию с выходов шинного- формирователя 19, представляющую собой адрес очередного подмножества данных. По заднему фронту сигнала на выходе 16.2 дешифратора 16 вновь изменяется состояние счетчика 20. Аналогичные действия продолжаются до тех пор, пока по заднему фронту очередного сигнала на выходе 16.2 дешифратора 16 код на выходе счетчика не будет равен коду, записанному при инициализации в регистре 17 и представляющему со-, бой количество N подмножеств данных. По стробу, поступающему на вход разрешения блока 18 сравнения со второго тактового выхода 2.5 тактового генератора 2, на выходе блока 18 сравнения возникает импульс, кото- рый по первому входу третьего элемента ИЛИ 21 обнуляет счетчик 20,ну- левой выходной сигнал которого вновь адресует первую группу входов второго мультиплексора 15.

В свою очередь, блок 1 задания, обнаружив маркер конца массива в последнем подмножестве данных, выводит информацию управления технологическим оборудованием, на информационные выходы 29. При очередной обработке блоком 1 задания информации о состоянии технологического оборудования процесс повторяется.

Блок 1 задания обрабатывает информацию в соответствии с алгоритмом моделирования программируемой логической матрицы.

Такой алгоритм является стандартным для реализации системы булевых функций, описывающей закон управления технологическим оборудованием, что подтверждается его использованием в языке высокого уровня для микропроцессоров Р СМ как процедура Р2А.

Таким образом, режим адаптивной адресации данных позволяет блоку 1

20

25

гическим оборудованием, предварите но, на стадии проектирования устро ства, разбивается на N подмножеств по N переменным х(х е it), где х вход 15 ной вектор. Каждое из подмножеств в свою очередь, по нулевому и единичному значениям переменной х.(1 i N) разделяется на два подмножества. В группу регистров 1 выводится информация о 2.N начальных адресных 2.N подмножеств данны В регистр 17 выводится величина N количества подмножеств.

При записи в блок 6 постоянной мяти масок, кодирующих конъюнктивн термы системы булевых функций, ран марок уменьшаются на единицу в свя с тем, что значения переменных х , неявно задаются в начальных адре сах 2.N подмножеств. Это предостав ляет дополнительные возможности, если например, разрядность входных сигналов с информационных входов 3 превышает разрядность шины 3.1 дан ных.

Следовательно, в режиме адаптив адресации массива данных блок 1 за дания обрабатывает только часть ис ходного массива данных, что сокращ ет время выработки управляющих воз действий на технологическое оборуд вание и повышает производительност

30

35

40

45

50

55

Формула изобретени

Устройство для программного упр ления технологическим оборудованием содержащее блок задания, тактовый генератор, контроллер, буфер адрес дешифратор адреса памяти, блок пос янной памяти, блок оперативной пам ти, шинный формирователь оперативн памяти, дешифратор адреса устройст ввода/вывода, группу шинных формир вателей, первый и второй элементы ИЛИ, причем тактовый генератор соде жит первый и второй входы подключения кварцевого резонатора, вход сброса устройства и вход готовности

задания адресовать массивы данных различными способами в зависимости от логических сигналов на группе информационных входов 31, при этом уменьшается массив данных, подлежащих обработке.

Массив данных для вычисления значения системы булевых функций, описывающей закон управления техноло0

5

гическим оборудованием, предварительно, на стадии проектирования устройства, разбивается на N подмножеств по N переменным х(х е it), где х вход- 5 ной вектор. Каждое из подмножеств N, в свою очередь, по нулевому и единичному значениям переменной х.(1 i N) разделяется на два подмножества. В группу регистров 13 выводится информация о 2.N начальных адресных 2.N подмножеств данных. В регистр 17 выводится величина N количества подмножеств.

При записи в блок 6 постоянной памяти масок, кодирующих конъюнктивные термы системы булевых функций, ранги марок уменьшаются на единицу в связи с тем, что значения переменных х , неявно задаются в начальных адресах 2.N подмножеств. Это предоставляет дополнительные возможности, если например, разрядность входных сигналов с информационных входов 30 превышает разрядность шины 3.1 данных.

Следовательно, в режиме адаптивной адресации массива данных блок 1 задания обрабатывает только часть исходного массива данных, что сокращает время выработки управляющих воздействий на технологическое оборудование и повышает производительность.

0

5

0

Формула изобретения

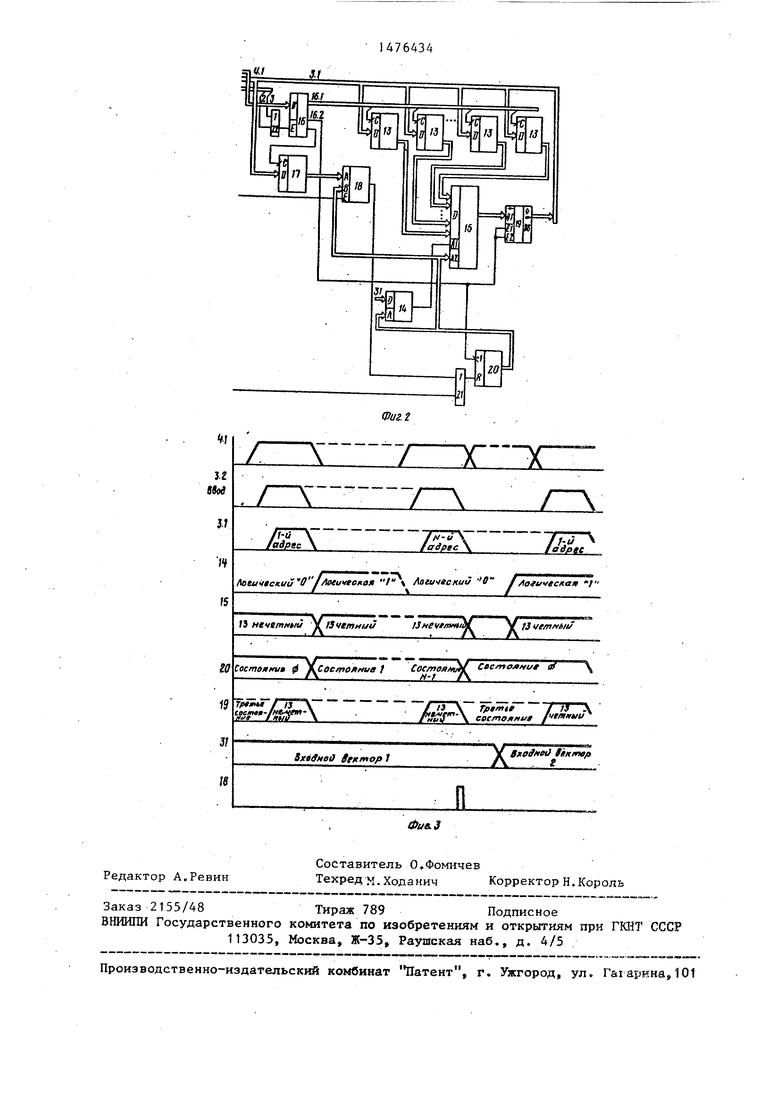

Устройство для программного управления технологическим оборудованием, содержащее блок задания, тактовый генератор, контроллер, буфер адреса, дешифратор адреса памяти, блок постоянной памяти, блок оперативной памяти, шинный формирователь оперативной памяти, дешифратор адреса устройств ввода/вывода, группу шинных формирователей, первый и второй элементы ИЛИ, причем тактовый генератор содержит первый и второй входы подключения кварцевого резонатора, вход сброса устройства и вход готовности

устройства, первый и второй тактовые выходы тактового генератора соединены соответственно с первым и вторым тактовыми входами блока задания, выход синхронизации которого соединен с входом синхронизации тактового ге- нератора, выход сброса и выход готовности -тактового генератора соединены соответственно с входом сброса и вхо- дом готовности блока задания, который содержит входы захвата и запроса прерывания устройства, выходы синхронизации и разрешения прерывания устройства, выход синхронизации тактово- го генератора соединен с синхровходом контроллера, адресные выходы блока задания соединены с информационными входами буфера адреса, первый и второй разрешающие входы которого соеди- нены с первым управляющим выходом контроллера, вторая группа входов/выходов данных которого соединена с группой входов/выходов данных блока задания, группа управляющих выходов (которого соединена с группой управляющих входов контроллера, информационные выходы буфера адреса соединены с адресными входами блоков посто-

янной и оперативной памяти, с информационными входами дешифратора адреса памяти и дешифратора адреса устройств ввода/вывода, выходы которого соединены с соответствующими вторыми входами разрешения шинных формирователей устройств ввода/вывода группы, информационные входы и выходы которого являются соответственно пер вой группой информационных входов и группой информационных выходов устройства, первые разрешающие входы шинных формирователей устройств ввода/вывода группы соединены с вторым управляющим выходом контроллера, второй и третий управляющие выходы которого соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с разрешающим входом дешифратора адреса устройств ввода/вывода, четвертый и пятый управляющие выходы контроллера соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с разрешающим входом дешифратора адреса памяти, первый выход которого соединен с первым входом разрешения блока постоянной памяти, а второй - с вторым входом разрешения шинного

g 5 0 5

0

5

0

5

0

5

формирователя оперативной памяти и с входом разрешения блока оперативной памяти, а выход разрешения приема блока задания соединен с входом разрешения ввода данных контроллера и с вторыми входами разрешения блока постоянной памяти и шинного формирователя оперативной памяти, пятый управляющий выход контроллера соединен с входом записи блока оперативной памяти, информационные выходы шинного формирователя оперативной памяти соединены с информационными входами блока оперативной памяти, информационные выходы которого соединены с информационными входами шинного формирователя оперативной памяти, входы/выходы данных системного контроллера соединены с информационными выходами блока постоянной памяти, с входами/выходами шинных формирователей оперативной памяти устройств ввода/вывода, отличающееся тем, что, с целью повышения производительности, в него введены группа регистров, первый и второй мультиплексоры дешифратор, ре- ристр, блок: сравнения, шинный формирователь, счетчик, третий и четвертый элементы ИЛИ, первый и второй входы которого соединены соответственно с вторым и третьим управляющими выходами контроллера, информационные выходи буфера адреса соединены с информационными входами дешифратора, управляющие выходы группы которого соединены соответственно с синхровходами регистров группы, информационные выходы которых соединены соответственно с информационными входами второго мультиплексора, информационные выходы которого соединены с информационными входами шинного формирователя, информационные выходы которого соединены с входами/ выходами данных контроллера, с информационными входами регистров группы и регистра, информационные выходы которого соединены с первой группой информационных входов блока сравнения, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с возвратным входом счетчика, информационные выходы которого соединены с второй группой информационных входов блока сравнения, с группами адресных входов первого и второго мультиплексоров,

адресный вход которого соединен с информационным выходом первого мультиплексора, информационные входы которого являются второй группой информационных входов устройства, выход четвертого элемента ИЛИ соединен с входом разрешения дешифратора, первый управляющий выход которого соединен со счетным входом прямого сче- IQ

Z3- 2kта счетчика и с входами разрешения шинного формирователя, второй управляющий выход дешифратора соединен с синхровходом регистра, второй тактовый выход и выход сброса тактового генератора соединены соответственно с входом разрешения блока сравнения и с вторым входом третьего элемента ИЛИ.

Фиг.1

М№

Щ

И

л, ffinmHmmn

-i lisa и lit 5 /з |Lj0 /J Ikff/J

И

| Микропроцессорная система | 1981 |

|

SU1172455A3 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство программного управления | 1981 |

|

SU1012205A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Лазарев В.Г., Пийль Е.И., Туру- та Е.Н | |||

| Построение программируемых управляющих систем | |||

| М.: Энергоиздат, 1984, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

Авторы

Даты

1989-04-30—Публикация

1987-04-13—Подача