ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее раскрытие изобретения в целом относится к связи, а конкретнее к приемнику для беспроводной связи.

УРОВЕНЬ ТЕХНИКИ

Сети беспроводной связи широко используются для предоставления различных услуг связи, например данных, речи, видео и т.д. Эти сети включают в себя беспроводные региональные сети радиосвязи (WWAN), которые обеспечивают зону радиосвязи для больших географических областей (например, городов), беспроводные локальные вычислительные сети (WLAN), которые обеспечивают зону радиосвязи для географических областей среднего размера (например, зданий и кампусов), и персональные беспроводные сети (WPAN), которые обеспечивают зону радиосвязи для небольших географических областей (например, домов). Беспроводная сеть обычно включает в себя одну или несколько точек доступа (или базовых станций), которые поддерживают связь для одного или нескольких терминалов пользователей (или беспроводных устройств).

IEEE 802.11 является семейством стандартов, разработанных Институтом инженеров по электротехнике и электронике (IEEE) для WLAN. Эти стандарты описывают беспроводной интерфейс между точкой доступа и терминалом пользователя или между двумя терминалами пользователя. Стандарт IEEE 802.11 редакции 1999 (или просто «802.11»), который озаглавлен «Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications» (Часть 11: Спецификации протокола управления доступом к среде передачи (MAC) и протокола физического уровня (PHY) для беспроводной LAN), поддерживает скорости передачи данных в 1 и 2 мегабит в секунду (Мбит/с) в частотном диапазоне 2,4 гигагерц (ГГц), используя либо расширение спектра путем скачкообразной перестройки частоты (FHSS), либо расширение спектра методом прямой последовательности (DSSS). Стандарт IEEE 802.11a-1999 (или просто «802.11a») является дополнением к 802.11, использует мультиплексирование с ортогональным частотным разделением каналов (OFDM) вместо FHSS или DSSS и поддерживает скорости передачи данных до 54 Мбит/с в частотном диапазоне 5 ГГц. Стандарт IEEE 802.11b-1999 (или просто «802.11b») является другим дополнением к 802.11 и использует DSSS для поддержки скоростей передачи данных до 11 Мбит/с. Стандарт IEEE 802.11g-2003 (или просто «802.11g») является еще одним дополнением к 802.11, использует DSSS и OFDM и поддерживает скорости передачи данных до 54 Мбит/с в полосе 2,4 ГГц. Эти разные стандарты общеизвестны в данной области техники и являются общедоступными.

Наименьшая скорость передачи данных, поддерживаемая 802.11, 802.11a, 802.11b и 802.11g, равна 1 Мбит/с. Для 802.11b и 802.11g (или просто «802.11b/g») для отправки передачи (передаваемых данных) на наименьшей скорости передачи (данных) в 1 Мбит/с используются особая схема DSSS и особая схема модуляции. DSSS и схема модуляции для 1 Мбит/с требуют определенного минимального отношения уровня сигнала к совокупному уровню взаимных помех и шумов (SNR) для надежного приема передачи (передаваемых данных). Диапазон передачи (передаваемых данных) затем определяется географической областью, в пределах которой приемная станция может достигать требуемого или лучшего SNR. В некоторых случаях желательно отправлять передачи (передаваемые данные) с диапазоном, который больше диапазона для наименьшей скорости передачи данных, поддерживаемой 802.11b/g.

Следовательно, в данной области техники имеется необходимость в сети беспроводной связи и станции, допускающих функционирование с расширенным диапазоном покрытия.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В этом документе описываются методики для обнаружения и демодуляции сигнала/передачи (передаваемых данных) в плохих канальных условиях (например, низкое SNR). В одном аспекте обнаружение сигнала выполняют в несколько этапов, используя разные типы обработки сигнала для достижения хорошей эффективности обнаружения. В варианте осуществления обнаружение сигналов выполняют с использованием корреляции во временной области для первого этапа, обработки в частотной области для второго этапа и обработки во временной области для третьего этапа. Обнаружение сигнала для каждого этапа можно дополнительно выполнять на основе адаптивной (самонастраивающейся) пороговой величины, которую выводят на основании принятой энергии для интервала (окна) символов, для того чтобы эффективность обнаружения была менее чувствительной к уровню принятого сигнала. Наличие сигнала может быть объявлено на основании результатов всех трех этапов.

В аспекте первого этапа входные выборки на приемной станции могут быть кодированы с сужением спектра с помощью кодовой последовательности для формирования суженных символов. Затем формируют произведения суженных символов по меньшей мере для двух задержек, например 1-символьной и 2-символьной задержек. Выполняют корреляцию между произведениями для каждой задержки и известными значениями для той задержки. Затем объединяют результаты корреляции для всех задержек, например, некогерентно или когерентно для множества предполагаемых фаз. Наличие сигнала и синхронизация сигнала могут быть определены на основании объединенных результатов корреляции.

В другом аспекте демодуляцию выполняют таким образом, чтобы достичь хорошей эффективности при плохих канальных условиях. В варианте осуществления синхронизацию входных выборок регулируют (например, с помощью многофазного фильтра) для получения отрегулированных по времени выборок. Уход частоты оценивают и удаляют из отрегулированных по времени выборок для получения выборок с частотной коррекцией, которые обрабатывают с помощью оценки канала (например, используя многоотводный (рейк) приемник) для получения обнаруженных символов. Фазы обнаруженных символов корректируют для получения символов с фазовой коррекцией. Затем над символами с фазовой коррекцией выполняют демодуляцию для получения демодулированных символов, которые обратно перемежают и декодируют для получения декодированных данных.

Обработка сигнала для каждого этапа обнаружения и для демодуляции подробно описывается ниже. Различные аспекты и варианты осуществления изобретения также описываются ниже.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Признаки и сущность настоящего изобретения станут более очевидными из изложенного ниже подробного описания, рассматриваемого совместно с чертежами, на которых одинаковые номера позиций определяют соответственно по всему документу.

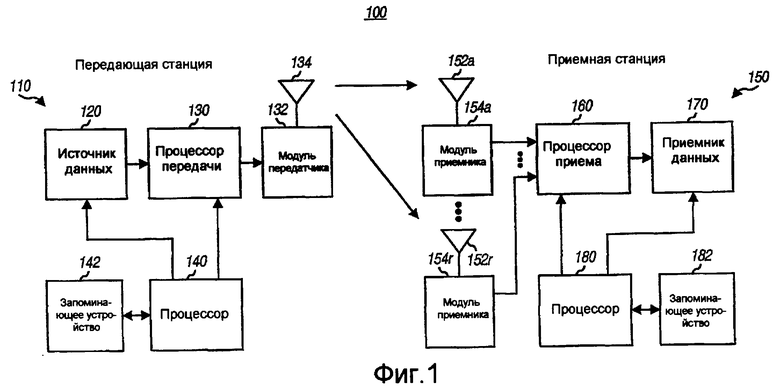

Фиг.1 показывает передающую станцию и приемную станцию.

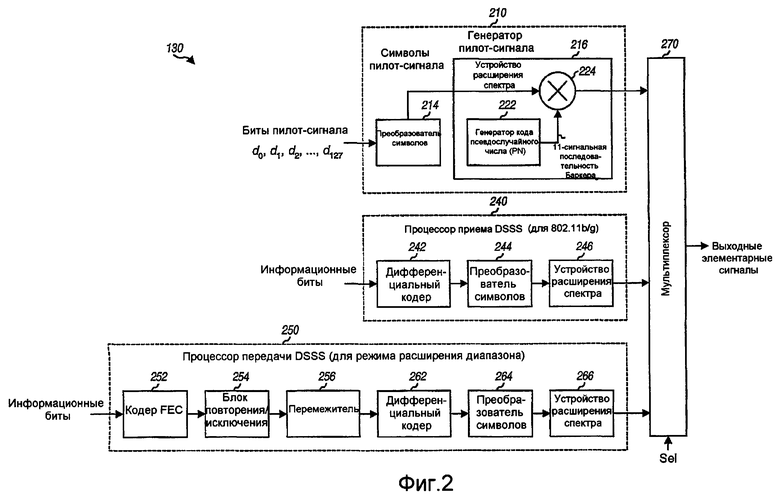

Фиг.2 показывает процессор передачи в передающей станции.

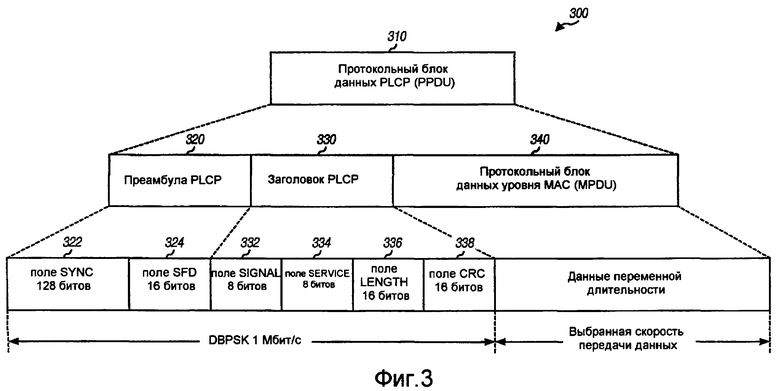

Фиг.3 показывает структуру PPDU, используемую 802.11b/g.

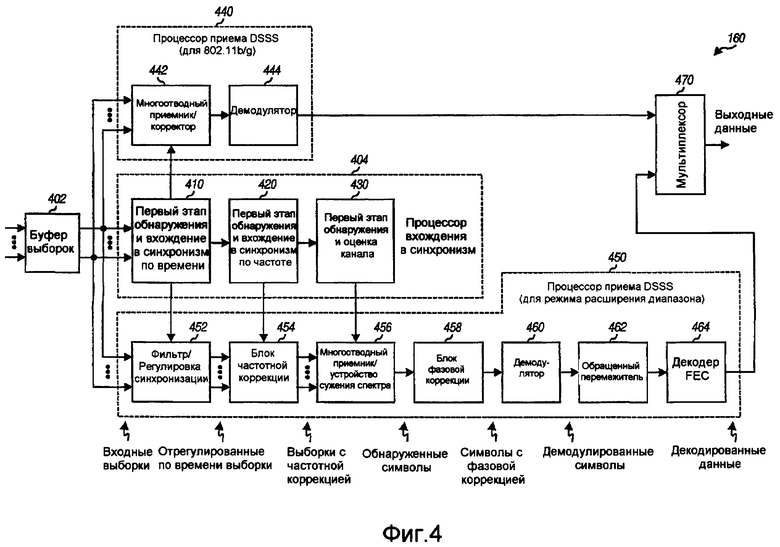

Фиг.4 показывает процессор приема в приемной станции.

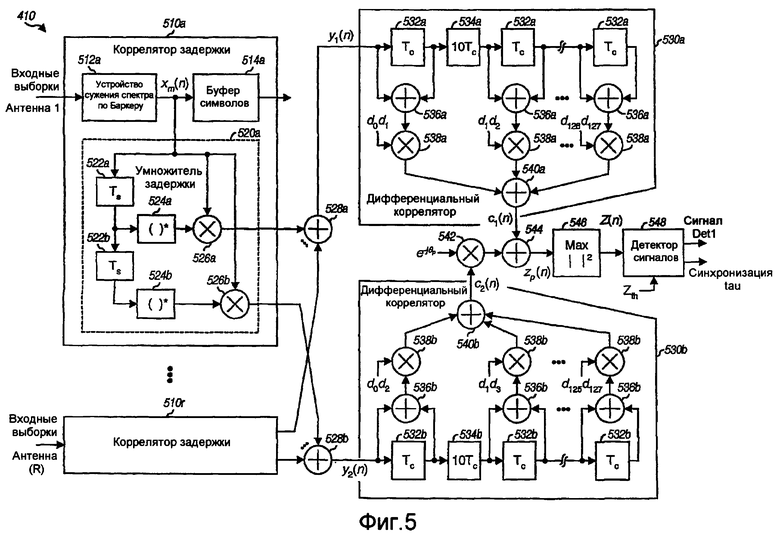

Фиг.5 показывает первый этап обнаружения и блок вхождения в синхронизм по времени.

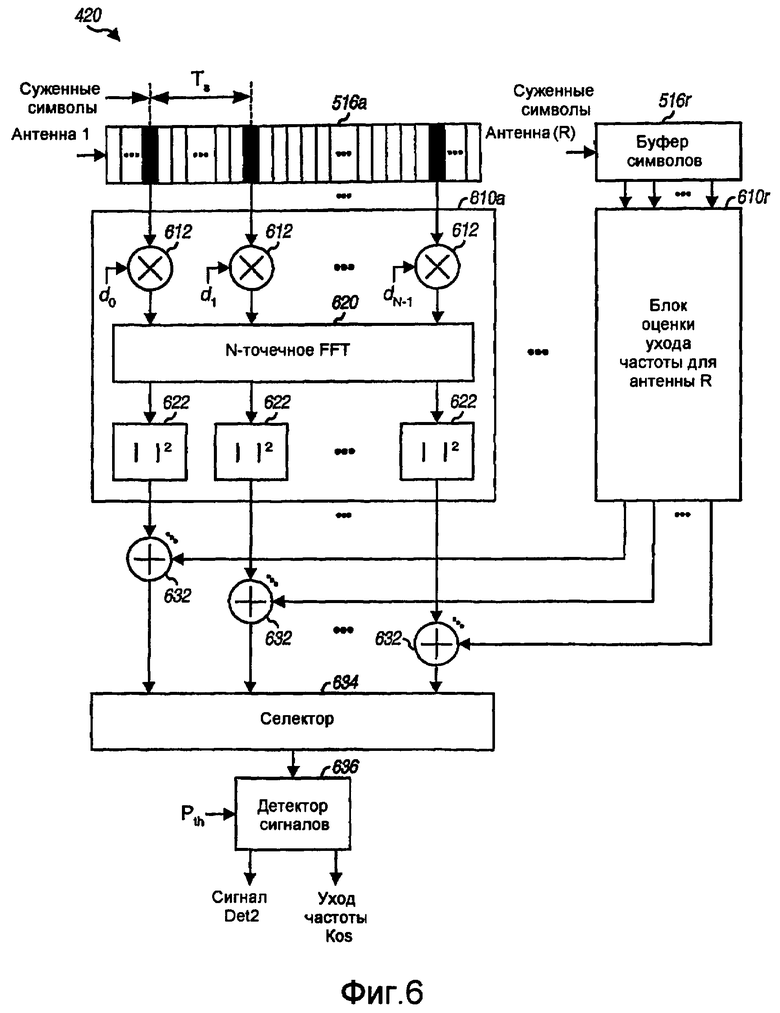

Фиг.6 показывает второй этап обнаружения и блок вхождения в синхронизм по частоте.

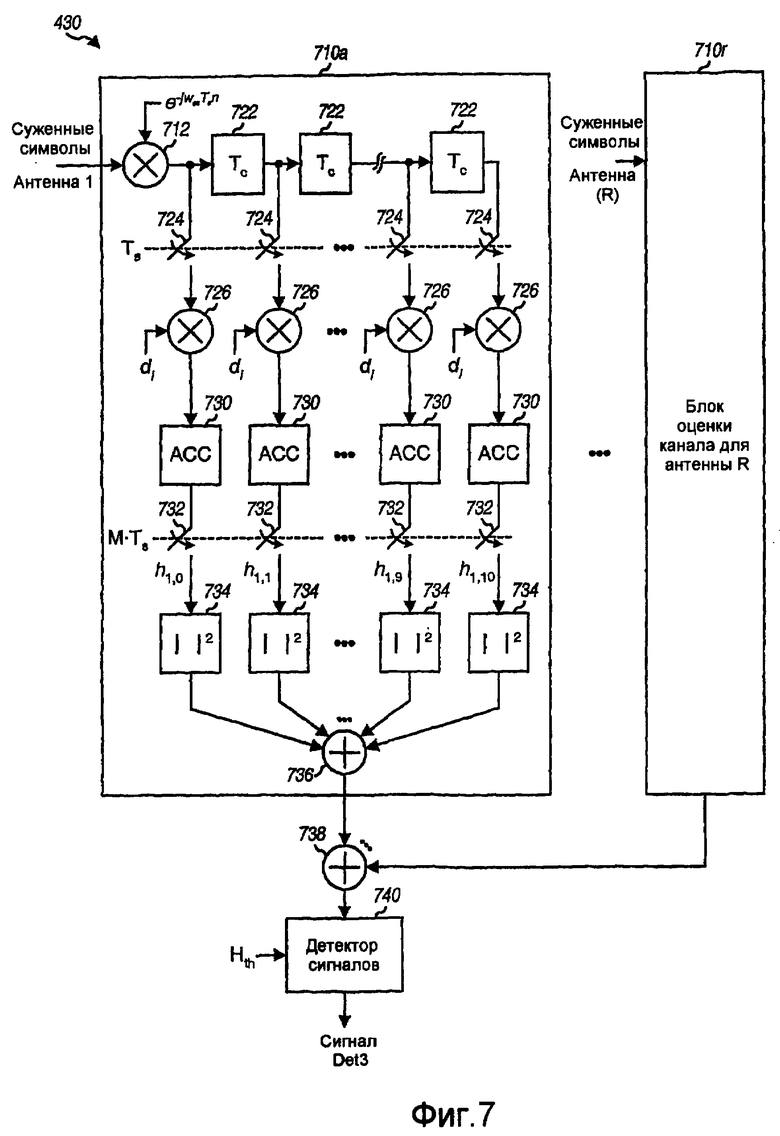

Фиг.7 показывает третий этап обнаружения и блок оценки канала.

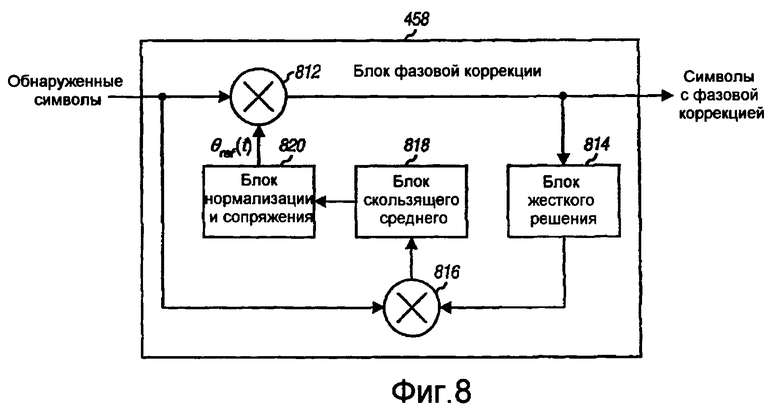

Фиг.8 показывает блок фазовой коррекции.

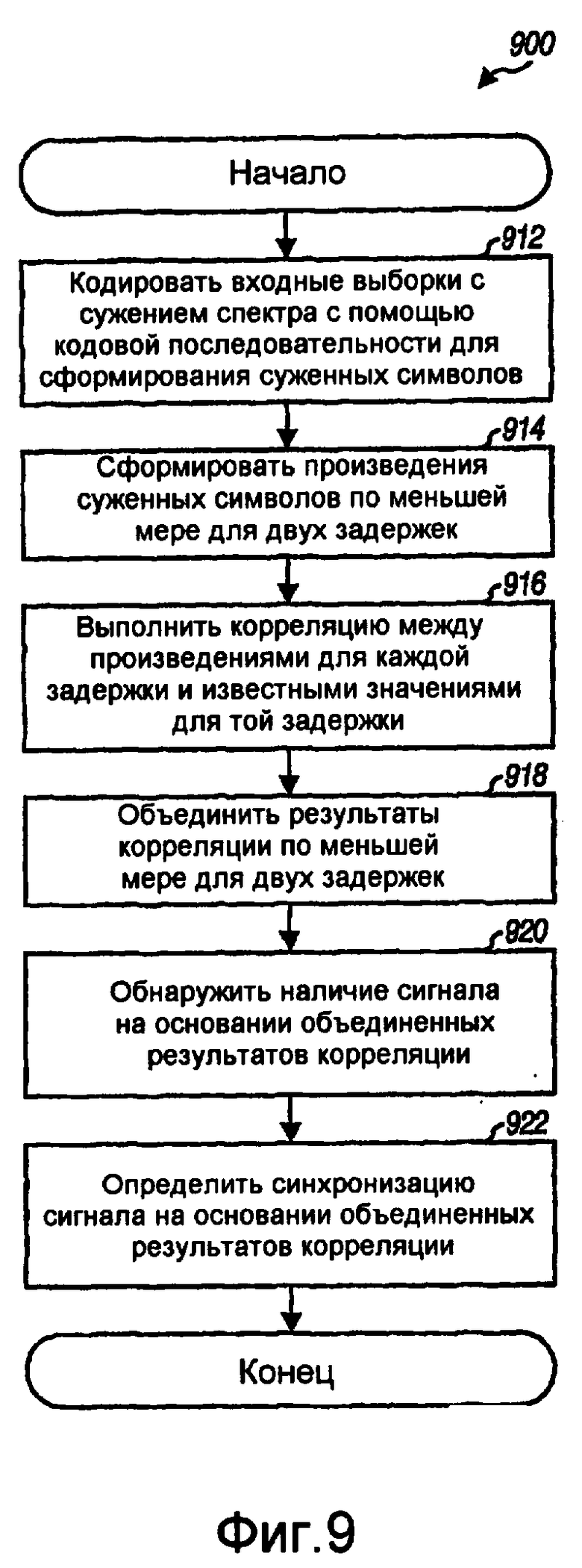

Фиг.9 показывает процесс для выполнения обнаружения сигнала для первого этапа.

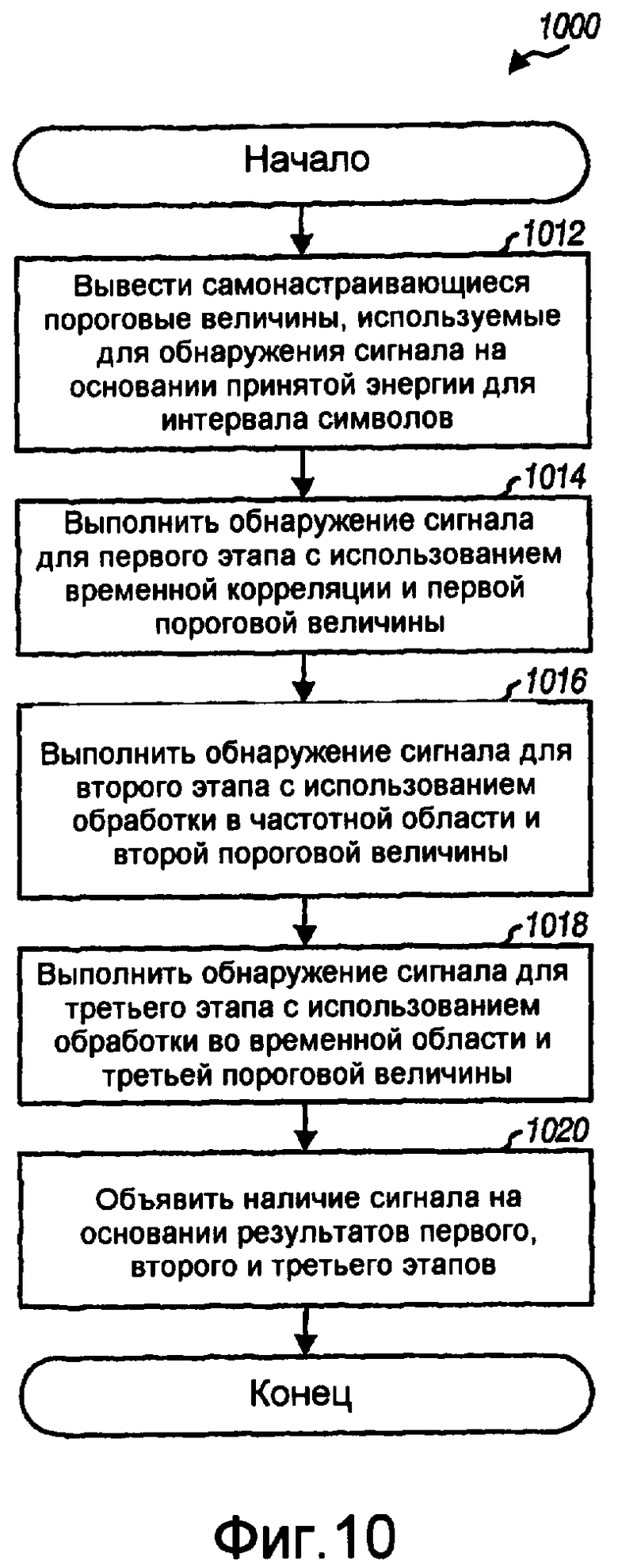

Фиг.10 показывает процесс для выполнения обнаружения сигнала с несколькими этапами.

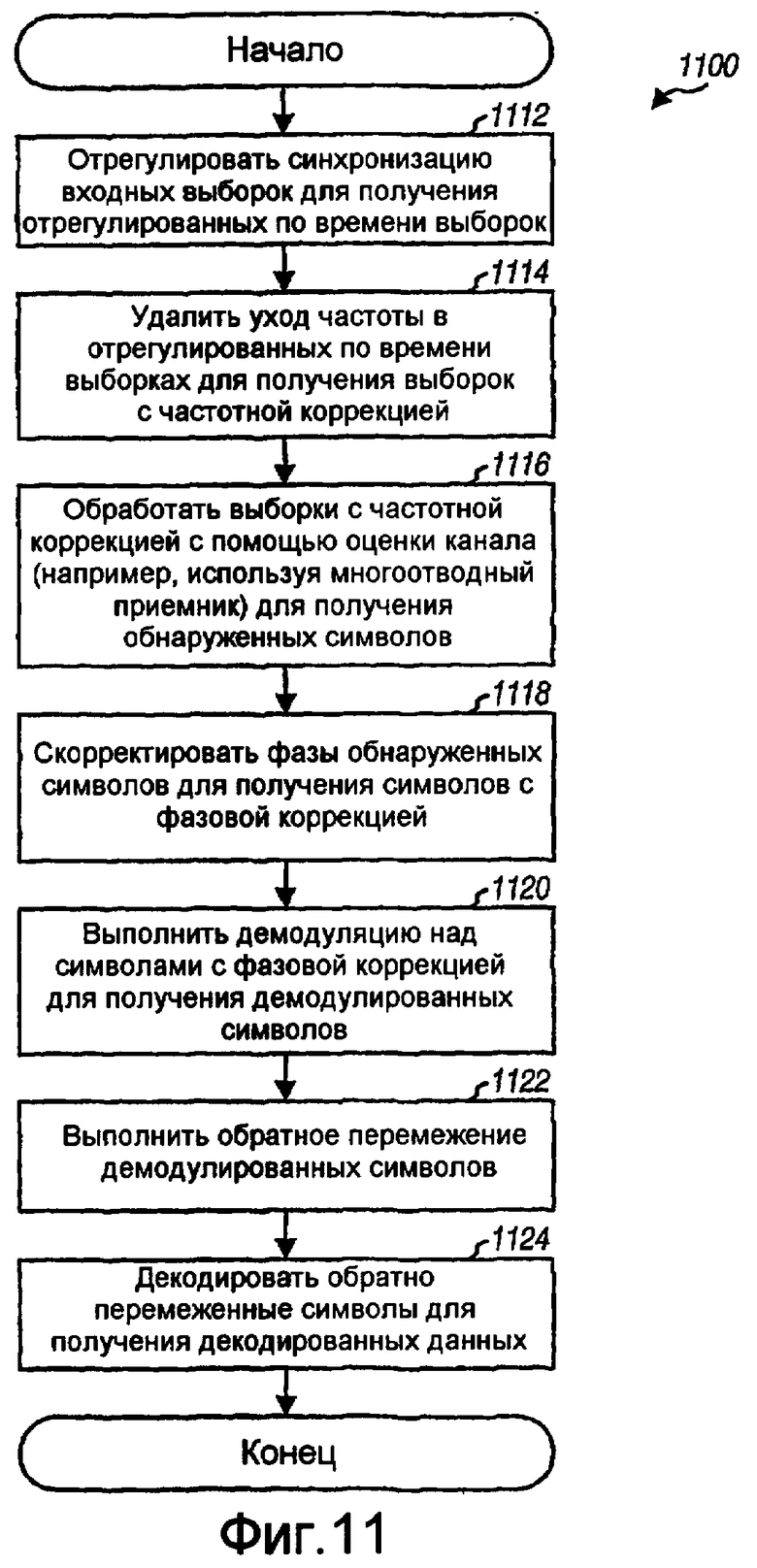

Фиг.11 показывает процесс для приема передачи (передаваемых данных).

ПОДРОБНОЕ ОПИСАНИЕ

Слово «типовой» используется в данном документе, чтобы обозначать «служащий в качестве примера, отдельного случая или иллюстрации». Любой вариант осуществления или образец, описанный в данном документе как «типовой», не обязательно должен быть истолкован как предпочтительный или выгодный по сравнению с другими вариантами осуществления или образцами.

Фиг.1 показывает блок-схему передающей станции 110 и приемной станции 150 в беспроводной сети 100. Передающая станция 110 оборудована одной антенной и может быть точкой доступа или терминалом пользователя. Приемная станция 150 оборудована несколькими (например, R=2) антеннами и также может быть точкой доступа или терминалом пользователя. Вообще, каждая станция может быть оборудована любым количеством антенн, которые могут использоваться для передачи и приема данных. Точкой доступа обычно является стационарная станция, которая обменивается информацией с терминалами пользователя и также может называться базовой станцией, базовой приемопередающей системой (BTS) или какой-либо другой терминологией. Терминал пользователя может быть стационарным или мобильным и также может называться мобильной станцией, беспроводным устройством, абонентским оборудованием (UE) или какой-либо другой терминологией.

На передающей станции 110 процессор 130 передачи принимает данные трафика от источника 120 данных, обрабатывает данные трафика в соответствии со скоростью передачи данных, выбранной для передачи, и предоставляет выходные элементарные сигналы. Ниже описывается обработка процессором 130 передачи. Модуль 132 передатчика (TMTR) обрабатывает (например, преобразует в аналоговую форму, усиливает, фильтрует и преобразует с повышением частоты) выходные элементарные сигналы и формирует модулированный сигнал, который передается через антенну 134.

На приемной станции 150 R антенн 152a-152r принимают переданный сигнал, и каждая антенна 152 предоставляет принятый сигнал соответствующему модулю 154 приемника (RCVR). Антенна также может называться «разнесением», и R приемных антенн обеспечивают кратность R разнесения. Каждый модуль 154 приемника обрабатывает свой принятый сигнал и предоставляет поток входных выборок процессору 160 приема. Процессор 160 приема обрабатывает входные выборки от всех R модулей 154a-154r приемника способом, дополнительным к обработке, выполненной процессором 130 передачи, и предоставляет декодированные данные приемнику 170 данных. Декодированные данные являются оценкой данных трафика, отправленных передающей станцией 110.

Процессоры 140 и 180 управляют работой блоков обработки на передающей станции 110 и приемной станции 150 соответственно. Запоминающие устройства 142 и 182 хранят данные и/или программные коды, используемые процессорами 140 и 180 соответственно.

Станции 110 и 150 могут поддерживать 802.11b и/или 802.11g. 802.11g обратно совместим с 802.11b и поддерживает все режимы работы, определенные 802.11b. Станции 110 и 150 могут дополнительно поддерживать режим расширения диапазона, который поддерживает по меньшей мере одну скорость передачи данных, которая меньше наименьшей скорости передачи данных в 802.11b/g. Меньшая скорость (скорости) передачи данных может использоваться для расширения диапазона покрытия, который выгоден для некоторых применений, например портативных раций.

Таблица 1 перечисляет две наименьшие скорости передачи данных, поддерживаемые 802.11b и 802.11g и обработку для каждой скорости передачи данных. Таблица 1 также перечисляет три скорости передачи данных, поддерживаемые режимом расширения диапазона, и обработку для каждой скорости передачи данных в соответствии с вариантом осуществления. В Таблице 1 DBPSK обозначает дифференциальную двухпозиционную фазовую манипуляцию, а DQPSK обозначает дифференциальную квадратурную фазовую манипуляцию.

Для ясности в последующем описании термин «бит» относится к количеству до модуляции (или преобразованию символов) на передающей станции, термин «символ» относится к количеству после преобразования символов и термин «элементарный сигнал» относится к количеству после спектрального кодирования с расширением спектра. Термин «выборка» относится к количеству до спектрального кодирования с сужением спектра на приемной станции.

Фиг.2 показывает вариант осуществления процессора 130 передачи на передающей станции 110. Процессор 130 передачи включает в себя генератор 210 пилот-сигнала, процессор 240 передачи DSSS для 802.11b/g, процессор 250 передачи DSSS для режима расширения диапазона и мультиплексор (Mux) 270.

Генератор 210 пилот-сигнала формирует пилот-сигнал (который также называется преамбулой или опорным сигналом) как для 802.11b/g, так и для режима расширения диапазона. В генераторе 210 пилот-сигнала преобразователь 214 символов принимает биты пилот-сигнала, преобразует эти биты в символы модуляции на основе BPSK и предоставляет символы пилот-сигнала устройству 216 расширения спектра. Для целей данного документа символом пилот-сигнала является символ модуляции для пилот-сигнала, символом данных является символ модуляции для данных трафика, символ модуляции является комплексной величиной для точки в сигнальном созвездии для схемы модуляции (например, для M-PSK или M-QAM), и символ является любой комплексной величиной. Устройство 216 расширения спектра спектрально расширяет символы пилот-сигнала и предоставляет выходные элементарные сигналы. В устройстве 216 расширения спектра генератор 222 кода псевдослучайного числа (PN) формирует кодовую последовательность PN. В некоторых вариантах осуществления это может называться последовательностью Баркера. Последовательность Баркера длиной в 11 элементарных сигналов обладает скоростью передачи в 11 миллионов элементарных сигналов в секунду (Mcps) и состоит из следующей 11-сигнальной последовательности {+1, -1, +1, +1, -1, +1, +1, +1, -1, -1, -1}. Умножитель 224 принимает символы пилот-сигнала на скорости в 1 миллион символов в секунду (Msps) от преобразователя 214 символов и последовательность Баркера от генератора 222 кода PN. Умножитель 224 умножает каждый символ пилот-сигнала на все 11 элементарных сигналов из последовательности Баркера, формирует 11 выходных элементарных сигналов для каждого символа пилот-сигнала и предоставляет последовательность выходных элементарных сигналов для пилот-сигнала. Выходная скорость передачи элементарного сигнала в 11 раз выше скорости передачи символа пилот-сигнала, или 11 Mcps. Каждый выходной элементарный сигнал является комплексной величиной, которую необходимо отправить в один период Tc элементарного сигнала, который равен приблизительно 90,9 наносекунд (нс) для 802.11b/g.

Процессор 240 передачи DSSS выполняет дифференциальную модуляцию и спектральное кодирование с расширением спектра для 802.11b/g. В процессоре 240 дифференциальный кодер 242 принимает информационные биты для данных трафика, выполняет дифференциальное кодирование информационных битов для DBPSK или DQPSK и предоставляет дифференциально-кодированные биты. Для DBPSK информационный бит «0» приводит к изменению фазы в 0°, а информационный бит «1» приводит к изменению фазы в 180°. Для DQPSK пара информационных битов «00» приводит к изменению фазы в 0°, пара информационных битов «01» приводит к изменению фазы в +90°, пара информационных битов «11» приводит к изменению фазы в +180° и пара информационных битов «10» приводит к изменению фазы в +270°. В некоторых вариантах осуществления преобразователь 244 символов преобразует дифференциально-кодированные биты в символы модуляции на основе BPSK для скорости передачи данных в 1 Мбит/с и на основе QPSK для скорости передачи данных в 2 Мбит/с. Тем не менее, могут использоваться другие схемы модуляции для скоростей передачи. Преобразователь 244 символов предоставляет символы модуляции BPSK на скорости в 1 Msps для скорости передачи данных 1 Мбит/с и предоставляет символы модуляции QPSK на скорости 1 Msps для скорости передачи данных 2 Мбит/с. Устройство 246 расширения спектра спектрально расширяет символы данных из преобразователя 244 символов и предоставляет выходные элементарные сигналы для данных трафика.

Процессор 250 передачи DSSS выполняет кодирование с прямым исправлением ошибок (FEC), преобразование символов и спектральное кодирование с расширением спектра для режима расширения диапазона. В процессоре 250 кодер 252 FEC принимает информационные биты для данных трафика, кодирует информационные биты в соответствии со схемой кодирования FEC и предоставляет кодовые биты. Кодер 252 FEC может обеспечивать выполнение сверточного кода, турбо-кода, кода разреженного контроля четности (LDPC), блочного кода, какого-либо иного кода или их сочетания. Блок 254 повторения/исключения может либо повторять, либо исключать некоторые или все кодовые биты для получения нужной кодовой скорости. Перемежитель 256 перемежает или переупорядочивает кодовые биты на основе схемы перемежения. Дифференциальный кодер 262 выполняет дифференциальное кодирование перемеженных битов, например для DBPSK или DQPSK, и предоставляет дифференциально-кодированные биты. Преобразователь 264 символов преобразует дифференциально-кодированные биты в символы модуляции на основе схемы модуляции, например BPSK или QPSK. Устройство 266 расширения спектра спектрально расширяет символы данных из преобразователя 264 символов и предоставляет выходные элементарные сигналы для данных трафика. Устройства 246 и 266 расширения спектра могут реализовываться так же, как и устройство 216 расширения спектра, и могут расширять каждый символ данных с помощью 11-сигнальной последовательности Баркера для формирования 11 выходных элементарных сигналов для этого символа данных.

Мультиплексор 270 принимает выходные элементарные сигналы от генератора 210 пилот-сигнала и процессоров 240 и 250 передачи DSSS, предоставляет выходные элементарные сигналы для пилот-сигнала в нужное время, предоставляет выходные элементарные сигналы от процессора 240, если выбирается режим 802.11b/g, и предоставляет выходные элементарные сигналы от процессора 250, если выбирается режим расширения диапазона.

Для IEEE 802.11 данные обрабатываются посредством уровня протокола управления доступом к среде передачи (MAC) в качестве протокольных блоков данных уровня MAC (MPDU). Каждый MPDU обрабатывается протоколом конвергенции физического уровня (PLCP) и помещается в протокольный блок данных PLCP (PPDU). Каждый PPDU обрабатывается физическим уровнем (как показано на фиг.2) и передается через радиоканал.

Фиг.3 показывает структуру 300 PPDU, используемую 802.11b/g. Для структуры 300 PPDU, PPDU 310 включает в себя преамбулу 320 PLCP, заголовок 330 PLCP и MPDU 340. MPDU 340 служит носителем данных трафика для PPDU 310 и имеет переменную длину. Преамбула 320 PLCP включает в себя поле 322 синхронизации PLCP (SYNC) и поле 324 ограничителя начала кадра (SFD). Поле 322 SYNC служит носителем фиксированной 128-битной последовательности, которая может использоваться приемной станцией для обнаружения сигнала, вхождения в синхронизм и других целей. Биты в 128-битной последовательности обозначаются d 0, d 1,…, d 127 . Поле 324 SFD служит носителем фиксированной 16-битной последовательности, которая указывает начало заголовка PLCP. Заголовок 330 PLCP включает в себя поле 332 SIGNAL, которое указывает скорость передачи данных для MPDU, поле 334 SERVICE, которое устанавливается в «0» для обозначения соответствия IEEE 802.11, поле 336 LENGTH, которое указывает количество времени (в единицах, равных миллисекундам), требуемое для отправки MPDU 340, и поле 338 CRC, которое служит носителем значения CRC, сформированного на основе полей SIGNAL, SERVICE и LENGTH. Преамбула 320 PLCP и заголовок 330 PLCP отправляются на скорости 1 Мбит/с с использованием DBPSK. Преамбула 320 PLCP содержит в целом 144 бита, которые обрабатываются для формирования 144 символов BPSK. Каждый символ BPSK состоит из 11 выходных элементарных сигналов, которые получаются путем кодирования с расширением спектра этого символа BPSK с помощью 11 элементарных сигналов из последовательности Баркера. 144 символа BPSK передаются в 144 периодах символов, при этом каждый период символа имеет длительность в 1 микросекунду (мкс).

Для режима расширения диапазона может использоваться структура 300 PPDU или другая структура PPDU. Структура PPDU для режима расширения диапазона может включать в себя поле SYNC, поле CHANEST, которое служит носителем фиксированной (например 32-битной) последовательности, используемой для оценки канала, одно или несколько полей сигнализации и MPDU.

Приемная станция 150 выполняет вхождение в синхронизм для обнаружения PPDU, отправленных передающей станцией 110. Вхождение в синхронизм для режима расширения диапазона более перспективно, чем обычное вхождение в синхронизм для 802.11b/g вследствие следующих отличий:

1. Низкое SNR/разнесение. Требуемое отношение энергии бита к общему уровню шума (Eb/No) ниже, например для 802.11b/g оно приблизительно 8 децибел (дБ), тогда как требуемое Eb/No для режима расширения диапазона приблизительно равно 3 дБ. Требуемое отношение энергии символа к общему уровню шума на кратность разнесения (Es/No/div) приблизительно равно -6 дБ при наименьшей скорости передачи данных 250 кбит/с. Желательно достигать обнаружения лучше 90% при этой пороговой величине Es/No/div в диспергирующих канальных условиях.

2. Вхождения в синхронизм по частоте. Приемник стандарта 802.11b/g обычно выполняет дифференциальную демодуляцию. Приемник для режима расширения диапазона может выполнять когерентную демодуляцию для повышения эффективности. Для получения хорошей оценки канала, используемой для когерентной демодуляции, приемнику может потребоваться определить отклонение частоты между генераторами на передающей и приемной станциях. Отклонение частоты ±20 промилле (ppm) на приемной станции интерпретируется в отклонение частоты ±232 кГц на частоте 5,8 ГГц, что может ухудшить эффективность.

3. Оценка канала. Мощность шума в оценке канала должна быть гораздо ниже, чем общая мощность шума, чтобы достигать хорошей эффективности для когерентной демодуляции.

Фиг.4 показывает вариант осуществления процессора 160 приема на приемной станции 150 на фиг.1. В процессоре 160 приема буфер 402 выборок принимает поток входных выборок от каждого из модулей 154a-154r приемника. Процессор 404 вхождения в синхронизм выполняет вхождение в синхронизм для PPDU. В процессоре 404 первый этап обнаружения и блок 410 вхождения в синхронизм по времени принимает входные выборки из буфера 402, обнаруживает PPDU и определяет синхронизацию каждого обнаруженного PPDU. Второй этап обнаружения и блок 420 вхождения в синхронизм по частоте также обнаруживает PPDU и дополнительно оценивает отклонение частоты во входных выборках. Третий этап обнаружения и блок 430 оценки канала также обнаруживает PPDU и дополнительно оценивает отклик радиоканала между передающей станцией 110 и приемной станцией 150. Блоки 410, 420 и 430 могут выполнять обработку на основе 128-битной последовательности в поле SYNC из преамбулы PPDU, как описано далее.

Фиг.5 показывает вариант осуществления первого этапа обнаружения и блока 410 вхождения в синхронизм по времени, который выполняет обнаружение сигнала с использованием корреляции во временной области. Блок 410 производит действия над комплекснозначными входными выборками на частоте выборки, которая больше либо равна скорости передачи элементарного сигнала. Для простоты последующее описание предполагает, что входные выборки предоставляются со скоростью передачи элементарного сигнала. В последующем описании «m» является индексом для приемной антенны, «n» является индексом для периода элементарного сигнала, «k» является индексом для элемента разрешения по частоте и «i» является индексом для 128 битов в фиксированной последовательности, отправленной в поле SYNC. Скорость передачи символов равна скорости передачи битов для пилот-сигнала, отправленного в поле SYNC. Когерентная сумма относится к сумме комплексных величин, а некогерентная сумма относится к сумме действительных величин (например, значений величин).

В блоке 410 корреляторы 510a-510r задержки принимают входные выборки от модулей 154a-154r приемника соответственно. В корреляторе 510a задержки для антенны 1 (или m=1) устройство 512a сужения спектра по Баркеру декодирует с сужением спектра входные выборки с помощью 11-сигнальной последовательности Баркера и предоставляет суженные символы на скорости передачи элементарного сигнала. Для каждого периода n элементарного сигнала устройство 512a сужения спектра по Баркеру умножает 11 входных выборок для периодов элементарного сигнала с n по n-10 на 11 элементарных сигналов из последовательности Баркера, суммирует результаты умножения и предоставляет суженный символ x m(n) для этого периода элементарного сигнала. Устройство 512a сужения спектра по Баркеру выполняет корреляцию с перестраиваемым опорным сигналом последовательности Баркера с входными выборками для получения суженного символа для каждого периода элементарного сигнала (вместо каждого периода символа) и предоставляет суженные символы буферу 514a символов и умножителю 520a задержки.

Умножитель 520a задержки формирует 1-символьные и 2-символьные произведения с задержкой из суженных символов. В умножителе 520a задержки суженные символы предоставляются двум последовательно соединенным блокам 522a и 522b задержки, при этом каждый блок задержки обеспечивает задержку в один период Ts символа, который равен 11 периодам элементарных сигналов, или Ts=11·Tc. Блоки 524a и 524b обеспечивают комплексное сопряжение суженных символов от блоков 522a и 522b задержки соответственно. Умножитель 526a умножает суженный символ для каждого периода n элементарного сигнала на выходной сигнал блока 524a и предоставляет 1-символьное произведение y1,m(n) с задержкой для этого периода элементарного сигнала. Аналогично умножитель 526b умножает суженный символ для каждого периода n элементарного сигнала на выходной сигнал блока 524b и предоставляет 2-символьное произведение y2,m(n) с задержкой для этого периода элементарного сигнала.

Коррелятор задержки для каждой оставшейся антенны обрабатывает входные выборки для этой антенны способом, описанным выше для антенны 1. Каждый коррелятор задержки предоставляет 1-символьные произведения y 1,m(n) с задержкой и 2-символьные произведения y 2,m(n) с задержкой для ассоциированной антенны m. Для каждого периода n элементарного сигнала сумматор 528a когерентно суммирует произведения y 1,m(n) для m=1, …, R от всех R корреляторов 510a-510r задержки и предоставляет произведение y 1(n) для этого периода элементарного сигнала. Для каждого периода n элементарного сигнала сумматор 528b суммирует произведения y 2,m(n) для m=1, …, R от всех корреляторов 510a-510r задержки и предоставляет произведение y 2(n) для этого периода элементарного сигнала. Произведения y 1(n) и y 2(n) могут выражаться в виде:

,

,

1-символьное произведение y 1,m(n) с задержкой свидетельствует о разности фаз между двумя суженными символами x m(n) и x m(n-Ts), которые разделены одним периодом символа для антенны m. 2-символьное произведение y 2,m(n) с задержкой свидетельствует о разности фаз между двумя суженными символами x m(n) и x m(n-2Ts), которые разделены двумя периодами символов для антенны m. Фиг.5 показывает использование 1-символьного и 2-символьного произведений с задержкой для обнаружения сигнала. Вообще, для обнаружения сигнала могут использоваться произведения для любого количества различных задержек (например, 1, 2, 3 периода символов и т.д.). Использование произведений для больших задержек может улучшить SNR и эффективность обнаружения. Однако, поскольку уход частоты вызывает чередование фаз во входных выборках, максимальная задержка может быть ограничена уходом частоты. Величина задержки также влияет на сложность дифференциальных корреляторов 530a и 530b. Например, имеются 127 операций умножения и суммирования для задержки в один период символа, 126 операций умножения и суммирования для задержки в два периода символов и т.д.

Дифференциальные корреляторы 530a и 530b принимают произведения y

1(n) и y

2(n) соответственно. В дифференциальном корреляторе 530a произведения y

1(n) предоставляются последовательности чередующихся элементов 532a и 534a задержки. Каждый элемент 532a задержки обеспечивает задержку в один период элементарного сигнала, каждый элемент 534a задержки обеспечивает задержку в 10 периодов элементарного сигнала, каждая пара соседних элементов 532a и 534a задержки обеспечивает задержку в 11 периодов элементарного сигнала (которая равна одному периоду символа), и вся последовательность элементов 532a и 534a задержки обеспечивает задержку примерно в 126 периодов символов. Группа из 127 сумматоров 536a соединяется со 127 элементами 532a задержки. Каждый сумматор 536a суммирует входной сигнал и выходной сигнал ассоциированного элемента 532a задержки и предоставляет выходной сигнал y

1(n-11·i)·y

1(n-11·i-1), где i

{0, …, 126}. Группа из 127 умножителей 538a соединяется с группой из 127 сумматоров 536a и также принимает 1-символьную дифференциальную последовательность, содержащую 127 известных значений. Эта последовательность образуется посредством побитового произведения первой последовательности d

0 - d

126 на вторую последовательность d

1-d

127, где d

0-d

127 являются 128 битами фиксированной последовательности (или битами пилот-сигнала), используемой для поля SYNC. Поскольку биты пилот-сигнала являются действительными значениями,

{0, …, 126}. Группа из 127 умножителей 538a соединяется с группой из 127 сумматоров 536a и также принимает 1-символьную дифференциальную последовательность, содержащую 127 известных значений. Эта последовательность образуется посредством побитового произведения первой последовательности d

0 - d

126 на вторую последовательность d

1-d

127, где d

0-d

127 являются 128 битами фиксированной последовательности (или битами пилот-сигнала), используемой для поля SYNC. Поскольку биты пилот-сигнала являются действительными значениями,  для i

для i

{0, …, 126}. Каждый умножитель 538a умножает выходной сигнал ассоциированного сумматора 536a на d

i

d

i+1

. Для каждого периода n элементарного сигнала сумматор 540a добавляет выходные сигналы от всех 127 умножителей 538a и предоставляет результат c

1(n) корреляции для этого периода элементарного сигнала.

{0, …, 126}. Каждый умножитель 538a умножает выходной сигнал ассоциированного сумматора 536a на d

i

d

i+1

. Для каждого периода n элементарного сигнала сумматор 540a добавляет выходные сигналы от всех 127 умножителей 538a и предоставляет результат c

1(n) корреляции для этого периода элементарного сигнала.

Дифференциальный коррелятор 530b аналогичен дифференциальному коррелятору 530a. Произведения y

2(n) предоставляются последовательности чередующихся элементов 532b и 534b задержки, которые обеспечивают задержку приблизительно в 125 периодов символов. Группа из 126 сумматоров 536b соединяется со 126 элементами 532b задержки. Каждый сумматор 536b суммирует входной сигнал и выходной сигнал ассоциированного элемента 532b задержки и предоставляет выходной сигнал y

2(n-11·i)·y

2(n-11·i-1), где i

{0, …, 125}. Группа из 126 умножителей 538b соединяется с группой из 126 сумматоров 536b и также принимает 2-символьную дифференциальную последовательность, содержащую 126 известных значений. Эта последовательность образуется посредством побитового произведения последовательности d

0-d

125 с последовательностью d

2-d

127. Каждый умножитель 538b умножает выходной сигнал ассоциированного сумматора 536b на d

i

d

i+2

. Для каждого периода n элементарного сигнала сумматор 540b добавляет выходные сигналы от всех 126 умножителей 538b и предоставляет результат c

2(k) корреляции для этого периода элементарного сигнала.

{0, …, 125}. Группа из 126 умножителей 538b соединяется с группой из 126 сумматоров 536b и также принимает 2-символьную дифференциальную последовательность, содержащую 126 известных значений. Эта последовательность образуется посредством побитового произведения последовательности d

0-d

125 с последовательностью d

2-d

127. Каждый умножитель 538b умножает выходной сигнал ассоциированного сумматора 536b на d

i

d

i+2

. Для каждого периода n элементарного сигнала сумматор 540b добавляет выходные сигналы от всех 126 умножителей 538b и предоставляет результат c

2(k) корреляции для этого периода элементарного сигнала.

Дифференциальный коррелятор 530a выполняет корреляцию между 1-символьными произведениями y 1(n) с задержкой с 1-символьной дифференциальной последовательностью. Дифференциальный коррелятор 530b выполняет корреляцию между 2-символьными произведениями y 2(n) с задержкой с 2-символьной дифференциальной последовательностью. Показанный на фиг.5 вариант осуществления предполагает, что радиоканал имеет разброс задержек (т.е. рассеяние или загрязнение) из небольшого количества элементарных сигналов. Сумматоры 536a и 536b используются для накопления энергии на этом разбросе задержек. Энергия также может накаливаться на большем количестве элементарных сигналов для большего разброса задержек либо может пропускаться, если радиоканал обладает нулевым или очень маленьким разбросом задержек (например, для строгой траектории радиоволны при распространении в пределах прямой видимости).

Каждый дифференциальный коррелятор 530 предоставляет результат корреляции для каждого периода элементарного сигнала. Фазы результатов c

2(n) корреляции из дифференциального коррелятора 530b могут не совпадать с фазами соответствующих результатов c

1(n) корреляции из дифференциального коррелятора 530a. Умножитель 542 умножает каждый результат c

2(n) корреляции из дифференциального коррелятора 530b на комплексный вектор  для L различных предполагаемых фаз и предоставляет множество из L повернутых по фазам результатов корреляции. Например, предполагаемыми фазами могут быть {0, 90°, 180°, -90°} для L=4, {0, 60°, -60°} для L=3 и т.д. L предполагаемых фаз могут выбираться для охвата возможного диапазона относительных фаз. Например, максимальный уход частоты может составлять 232 кГц для отклонения частоты в ±20 ppm и 5,8 ГГц несущей частоты. Максимальная разность фаз между 1-символьными и 2-символьными корреляциями с задержкой равна ±232 кГц умножить на 1 мкс, что приблизительно равно 90 градусам. Отсюда, если используются предполагаемые фазы 0, 60° и -60°, то по меньшей мере одна предполагаемая фаза находится в пределах 30°. Если разность фаз больше (например, вследствие использования большей задержки или большего ухода частоты), то предполагаемые фазы должны охватывать больший диапазон, вплоть до полных ±180°.

для L различных предполагаемых фаз и предоставляет множество из L повернутых по фазам результатов корреляции. Например, предполагаемыми фазами могут быть {0, 90°, 180°, -90°} для L=4, {0, 60°, -60°} для L=3 и т.д. L предполагаемых фаз могут выбираться для охвата возможного диапазона относительных фаз. Например, максимальный уход частоты может составлять 232 кГц для отклонения частоты в ±20 ppm и 5,8 ГГц несущей частоты. Максимальная разность фаз между 1-символьными и 2-символьными корреляциями с задержкой равна ±232 кГц умножить на 1 мкс, что приблизительно равно 90 градусам. Отсюда, если используются предполагаемые фазы 0, 60° и -60°, то по меньшей мере одна предполагаемая фаза находится в пределах 30°. Если разность фаз больше (например, вследствие использования большей задержки или большего ухода частоты), то предполагаемые фазы должны охватывать больший диапазон, вплоть до полных ±180°.

Умножитель 542 поворачивает c 2(n) на разные фазы. Для каждого периода n элементарного сигнала сумматор 544 когерентно складывает результат c 1(n) корреляции из сумматора 540a с каждым из L соответствующих повернутых по фазам результатов корреляции из умножителя 542 и предоставляет L объединенных результатов z p(n) корреляции для p=1,…, L. Если используются K дифференциальных корреляторов для K разных задержек, где K>1, то один дифференциальный коррелятор может использоваться в качестве опорного (без фазового сдвига). Тогда один объединенный результат корреляции получается для каждого предположения, соответствующего определенной фазе для каждого из K-1 оставшихся дифференциальных корреляторов. Например, если K=3, то один объединенный результат корреляции получается для каждого предположения, соответствующего другой паре предполагаемых фаз для двух дифференциальных корреляторов. Для LK-1 возможных предположений получаются вплоть до LK-1 объединенных результатов корреляции. Для каждого периода n элементарного сигнала блок 546 вычисляет возведенную в квадрат величину каждого из L объединенных результатов корреляции (для K=2), определяет наибольшее значение величины в квадрате среди L значений величин в квадрате и предоставляет это наибольшее значение Z(n) величины в квадрате. Для каждого периода n элементарного сигнала детектор 548 сигналов сравнивает наибольшее значение Z(n) величины в квадрате с заранее установленной пороговой величиной Zth и объявляет наличие PPDU, если Z(n) превосходит пороговую величину, или Z(n)>Zth. Детектор 548 сигналов продолжает наблюдать за значениями величин в квадрате для поиска максимального значения и предоставляет период элементарного сигнала для этого максимального значения как начальную синхронизацию tau для обнаруженного PPDU.

В качестве альтернативы результаты c 1(n) и c 2(n) корреляции для каждого периода элементарного сигнала могут некогерентно объединяться. Это может достигаться путем вычисления величины c 1(n) в квадрате, вычисления величины c 2(n) в квадрате и суммирования двух возведенных в квадрат величин для получения Z(n). Пороговая величина Zth может устанавливаться в различные значения в зависимости от того, как выводится Z(n).

Пороговая величина Zth, используемая для первого этапа обнаружения, может быть самонастраивающейся пороговой величиной, которая изменяется, например, вместе с принятой энергией Erx для 128-битного поля SYNC. Например, пороговая величина Zth может быть задана равной принятой энергии Erx, умноженной на масштабный коэффициент S1, или Zth=Erx·S1. Использование нормализованной принятой энергии для обнаружения сигнала приводит к сходной эффективности обнаружения для широкого диапазона принятых уровней сигнала. Компьютерное моделирование показывает, что вероятность обнаружения порядка 90% и частота ложных тревог меньше 1% могут достигаться для 2 равных некоррелированных каналов Релея при общем SNR в -3 дБ, используя S1=22. Вероятность обнаружения относится к правдоподобию безошибочного объявления наличия PPDU, когда PPDU отправляется. Частота ложных тревог относится к правдоподобию ложного объявления наличия PPDU, когда ничего не отправляется. Компромисс между вероятностью обнаружения и частотой ложных тревог может быть достигнут путем выбора подходящей величины для масштабного коэффициента S1.

Фиг.6 показывает вариант осуществления второго этапа обнаружения и блока 420 вхождения в синхронизм по частоте, который выполняет обнаружение сигнала с использованием обработки в частотной области. Для этого варианта осуществления блок 420 включает в себя R блоков 610a-610r оценки ухода частоты для R приемных антенн. Каждый блок оценки ухода частоты обнаруживает энергии в различных элементах разрешения по частоте для определения ухода частоты во входных выборках от ассоциированной антенны.

Для приемной антенны 1 (m=1) буфер 516a символов предоставляет N суженных символов, которые разнесены 11 периодами элементарных сигналов (или одним периодом символа), начиная с начальной синхронизации tau, предоставленной блоком 410 вхождения в синхронизм по времени. Первый суженный символ, таким образом, выравнивается по времени с наилучшим предположением синхронизации из этапа вхождения в синхронизм по времени. Вообще, N может быть любым целым числом, являющимся степенью двойки, и не превышает 128, например N может быть 32, 64 или 128. В блоке 610a оценки ухода частоты группа из N умножителей 612 принимает N суженных символов из буфера 514a символов и N соответствующих битов пилот-сигнала в 128-битной последовательности. Каждый умножитель 612 умножает суженный символ на его бит пилот-сигнала для удаления модуляции из этого суженного символа. Блок 620 N-точечного быстрого преобразования Фурье (FFT) принимает N выходных сигналов от N умножителей 612, выполняет N-точечное FFT над этими N выходными сигналами и предоставляет N значений частотной области для N элементов разрешения по частоте. Группа из N блоков 622 принимает N значений частотной области из блока 620 FFT. Каждый блок 622 вычисляет возведенную в квадрат величину его значения частотной области и предоставляет обнаруженную энергию для соответствующего элемента k разрешения по частоте.

После удаления модуляции с помощью умножителей 612 N выходных сигналов из этих умножителей могут иметь периодическую составляющую. Эта периодическая составляющая обусловлена уходом частоты в генераторе на приемной станции 150, что приводит к тому, что принятый сигнал не преобразуется с понижением частоты точно в DC. Блок 620 FFT предоставляет спектральную чувствительность N выходных сигналов от умножителей 612. Элемент k разрешения по частоте с наибольшей обнаруженной энергией свидетельствует об уходе частоты для входных выборок от антенны m.

Блок оценки ухода частоты для каждой оставшейся приемной антенны обрабатывает суженные символы для этой антенны способом, описанным для антенны 1. Группа из N сумматоров 632 принимает R множеств из N обнаруженных энергий от R блоков 610a-610r оценки ухода частоты для R приемных антенн. Каждый сумматор 632 суммирует обнаруженные энергии от всех R блоков 610a-610r оценки ухода частоты для ассоциированного элемента k разрешения по частоте и предоставляет общую обнаруженную энергию E(k) для этого элемента разрешения по частоте. Селектор 634 выбирает наибольшую общую обнаруженную энергию E max(k) среди N общих обнаруженных энергий для N элементов разрешения по частоте. Детектор 636 сигналов сравнивает наибольшую общую обнаруженную энергию E max(k) с заранее установленной пороговой величиной Eth, объявляет обнаружение сигнала, если E max(k) больше пороговой величины Eth, и предоставляет элемент разрешения по частоте с наибольшей общей обнаруженной энергией в качестве предполагаемого отклонения k os частоты. Пороговая величина Eth может быть задана равной, например, принятой энергии Erx для 128-битного поля SYNC, умноженной на масштабный коэффициент S2, или Em=Erx·S2.

Показанный на фиг.6 вариант осуществления использует N-точечное FFT, где N≤128. Если N=64, что является размером FFT, обычно используемым для 802.11b и 802.11g для OFDM, то расстояние между соседними элементами разрешения по частоте равно 15,625 кГц для скорости передачи символов 1 Msps и неточность в оценке ухода частоты равна половине расстояния между элементами разрешения, или 7,812 кГц. Эта неточность может быть уменьшена путем выполнения интерполяции и/или использования большего 128-точечного FFT.

Выигрыш от обработки для когерентного накопления посредством FFT приблизительно равен 18 дБ для N=64. Наихудшая потеря когерентного накопления - около 4 дБ, которая возникает, когда фактический уход частоты находится точно между двумя элементами разрешения по частоте. Минимальное общее объединенное SNR почти в 14 дБ может достигаться для N=64. Большинство потерь когерентного накопления может быть восстановлено путем суммирования обнаруженных энергий для пар соседних элементов разрешения по частоте (например, аналогично суммированию, выполненному сумматорами 536a и 536b на фиг.5) перед выбором наибольшей общей обнаруженной энергии. Суммирование обнаруженных энергий для соседних пар элементов разрешения по частоте повышает вероятность обнаружения ценой небольшого увеличения в частоте ложных тревог. Вероятность обнаружения лучше 90% при SNR, равном -7 дБ, и лучше 99.9% при SNR, равном -4 дБ, может достигаться с использованием пороговой величины S2=8. Вероятность ложных тревог составляет менее 0,5% для второго этапа обнаружения, приводя в результате к совокупной частоте ложных тревог в 5·10-5 для первого и второго этапов обнаружения.

Многолучевое распространение может ухудшить вероятность обнаружения, поскольку вся энергия не используется на втором этапе обнаружения (вследствие FFT, функционирующего на расстоянии между символами вместо расстояния между элементарными сигналами). В варианте осуществления повышенная эффективность может достигаться для второго этапа обнаружения путем выполнения 128-точечного FFT, а отсюда интегрирования по всей 128-битной последовательности для поля SYNC. В другом варианте осуществления одно 64-точечное FFT может выполняться для первой половины 128-битной последовательности, как описано выше, другое 64-точечное FFT может выполняться для второй половины 128-битной последовательности и обнаруженные энергии для двух FFT могут быть некогерентно суммированы сумматорами 632.

В другом варианте осуществления оценки ухода частоты входные выборки коррелируются с известной 128-битной последовательностью для различных предполагаемых уходов частоты. Для каждого предполагаемого ухода частоты входные выборки поворачиваются на этот уход частоты, повернутые выборки коррелируются с 128-битной последовательностью, результат корреляции сравнивается снова с пороговой величиной и объявляется обнаружение сигнала, если результат корреляции превышает пороговую величину. Корреляция может выполняться во временной области с помощью устройства фильтра конечной импульсной характеристики (FIR) или в частотной области с помощью операции FFT-умножения-IFFT. Оценка ухода частоты определяется посредством предполагаемого отклонения частоты, которое приводит к наибольшему результату корреляции, превышающему пороговую величину.

В еще одном варианте осуществления оценки ухода частоты входные выборки сначала кодируются с сужением спектра для получения суженных символов на скорости передачи элементарного сигнала, как показано на фиг.5. Суженные символы затем умножаются на соответствующие биты пилот-сигнала для удаления модуляции пилот-сигнала. Результирующие символы используются для формирования 1-символьного и 2-символьного произведений с задержкой, используя, например, умножитель 520a задержки на фиг.5. Произведения с задержкой для каждой задержки обрабатываются для формирования комплексной величины для этой задержки. Для каждой задержки d, где d={1, 2}, d-символьные произведения с задержкой предоставляются группе из 10 последовательно соединенных элементов задержки, разделенных элементарными сигналами (например, аналогичные элементам 722 задержки на фиг.7) для получения d-символьных произведений с задержкой на 11 разных интервалах элементарных сигналов. d-символьные произведения с задержкой для каждого интервала элементарного сигнала когерентно суммируются по полю SYNC (например, используя переключатели 724 и накопители 730 на фиг.7). 11 суммированных результатов для 11 интервалов элементарных сигналов могут объединяться (например, используя суммирование дифференциально взвешенных сигналов каждого канала) для формирования комплексной величины Vd для задержки d. Разность фаз между комплексными величинами V1 и V2 для 1-символьных и 2-символьных задержек может вычисляться и использоваться для выведения ухода частоты. R приемных антенн могут объединяться различными способами, например произведения с задержкой могут объединяться по антеннам, как показано на фиг.5, комплексные величины для различных антенн могут объединяться для каждой задержки d и т.д. Более двух задержек и/или большая задержка также могут использоваться для частотного анализа. Большая задержка приводит к большей разности фаз, которая обеспечивает лучшую разрешающую способность для ухода частоты. Однако большая задержка может привести к погрешности, например фазовый сдвиг больше 180° может интерпретироваться как отрицательный сдвиг меньше 180°. Для заданного количества задержек и заданного максимального ухода частоты для оптимизации разрешающей способности без погрешности может быть выбрано множество задержек.

Независимо от методики, используемой для частотного анализа, предполагаемый уход k os частоты из блока 420 вхождения в синхронизм по частоте обычно содержит остаточное отклонение частоты. Чтобы оценить это остаточное отклонение частоты, первая 11-отводная оценка канала может выводиться на основе первых 64 битов поля SYNC (например, как описано ниже), вторая 11-отводная оценка канала может выводиться на основе последних 64 битов поля SYNC, с обеими оценками канала, выводимыми с исключенным уходом k os частоты. На основе отвода может вычисляться произведение второй оценки канала и комплексного сопряжения первой оценки канала. 11 результирующих произведений могут быть когерентно суммированы для получения разности фаз между двумя оценками канала. Сравнение с пороговой величиной может выполняться на (1) каждом канальном отводе перед вычислением произведения и/или (2) каждом произведении перед суммированием произведений. Сравнение с пороговой величиной удаляет канальные отводы с низкой энергией, ниже заранее установленной пороговой величины. Остаточное отклонение частоты может быть оценено на основе разности фаз между двумя оценками каналов и может предоставляться фильтру 452 и/или блоку 454 частотной коррекции и использоваться для коррекции синхронизации и/или частоты входных выборок (не показано на фиг.4). Это обновление ухода k os частоты с оценкой остаточного отклонения частоты может повысить эффективность демодуляции.

Фиг.7 показывает вариант осуществления третьего этапа обнаружения и блока 430 оценки канала, который выполняет обнаружение сигнала с использованием обработки во временной области. Для этого варианта осуществления блок 430 включает в себя R блоков 710a-710r оценки канала для R приемных антенн. Каждый блок оценки канала может выводить оценку импульсной характеристики канала, содержащую канальные отводы, которые располагаются с интервалами частоты выборки. Например, могут быть получены до 11 канальных отводов, разделенных одним элементарным сигналом, если суженные символы получаются на скорости передачи элементарного сигнала, могут быть получены до 22 канальных отводов, разделенных половиной элементарного сигнала, если суженные символы получаются на удвоенной скорости передачи элементарного сигнала (или элементарного сигнала х 2), и т.д. Для показанного на фиг.7 варианта осуществления каждый блок оценки канала выводит 11-отводную оценку импульсной характеристики канала на интервале элементарного сигнала для ассоциированной антенны.

В блоке 710a оценки канала для антенны 1 (m=1) умножитель 712 умножает суженные символы для антенны m на комплексный вектор  для удаления отклонения k

os частоты, определенного блоком 420 вхождения в синхронизм по частоте. Умножитель 712 предоставляет символы с частотной коррекцией на скорости передачи элементарного сигнала группе из 10 последовательно соединенных элементов 722 задержки. Каждый элемент 722 задержки обеспечивает задержку в один период элементарного сигнала. Группа из 11 переключателей 724 соединяется с выходом умножителя 712 и выходами 10 элементов 722 задержки. Переключатели 724 задействуются для одного периода элементарного сигнала в каждом периоде символа и предоставляют 11 символов с частотной коррекцией для этого периода символа. Управляющий сигнал для переключателей 724 определяется начальной синхронизацией tau от блока 410 вхождения в синхронизм по времени и формируется из условия, чтобы символ с частотной коррекцией из пятого элемента 722 задержки (который предназначен для центрального отвода 11-отводной оценки импульсной характеристики канала) соответствовал наилучшему предположению синхронизации, предоставленному этапом вхождения в синхронизм по времени.

для удаления отклонения k

os частоты, определенного блоком 420 вхождения в синхронизм по частоте. Умножитель 712 предоставляет символы с частотной коррекцией на скорости передачи элементарного сигнала группе из 10 последовательно соединенных элементов 722 задержки. Каждый элемент 722 задержки обеспечивает задержку в один период элементарного сигнала. Группа из 11 переключателей 724 соединяется с выходом умножителя 712 и выходами 10 элементов 722 задержки. Переключатели 724 задействуются для одного периода элементарного сигнала в каждом периоде символа и предоставляют 11 символов с частотной коррекцией для этого периода символа. Управляющий сигнал для переключателей 724 определяется начальной синхронизацией tau от блока 410 вхождения в синхронизм по времени и формируется из условия, чтобы символ с частотной коррекцией из пятого элемента 722 задержки (который предназначен для центрального отвода 11-отводной оценки импульсной характеристики канала) соответствовал наилучшему предположению синхронизации, предоставленному этапом вхождения в синхронизм по времени.

Оценка канала выполняется в течение заранее установленного временного интервала W, который выбирается для достижения адекватного SNR или качества для оценок канала. Временной интервал W может быть M периодов символов длиной, где M может быть, например, M>31. Группа из 11 умножителей 726 принимает бит d i пилот-сигнала для каждого периода символа, в котором выполняется оценка канала. Каждый умножитель 726 умножает выходной сигнал соответствующего переключателя 724 на бит d i пилот-сигнала, удаляет модуляцию посредством бита пилот-сигнала и предоставляет свой выходной сигнал соответствующему накопителю 730. Группа из 11 накопителей 730 обнуляется в начале оценки канала. Каждый накопитель 730 когерентно суммирует выходной сигнал соответствующего умножителя 726 в течение временного интервала W. Группа из 11 переключателей 732 соединяется с группой из 11 накопителей 730. Переключатели 732 задействуются в конце временного интервала W и предоставляют 11 канальных отводов h m,0-h m,10 для оценки импульсной характеристики канала для антенны m. Эта оценка канала может использоваться для демодуляции данных, как описано далее. Группа из 11 блоков 734 принимает 11 канальных отводов, и каждый блок 734 вычисляет возведенную в квадрат величину своего канального отвода. Сумматор 736 суммирует выходные сигналы от всех 11 блоков 734 и предоставляет общую энергию для всех канальных отводов для антенны m. В качестве альтернативы выходной сигнал каждого блока 734 может сравниваться с пороговой величиной и сумматор 736 может суммировать только выходные сигналы, которые превышают пороговую величину. Пороговая величина может быть установлена в заранее установленное процентное отношение от общей энергии для всех 11 канальных отводов.

Блок оценки канала для каждой оставшейся приемной антенны обрабатывает суженные символы для этой антенны способом, описанным выше для антенны 1. Сумматор 738 суммирует общие энергии для всех R блоков 710a-710r оценки канала и предоставляет общую энергию H для всех R антенн. Детектор 740 сигналов сравнивает общую энергию H с заранее установленной пороговой величиной Hth и объявляет обнаружение сигнала, если H превышает пороговую величину Hth. Пороговая величина Hth может быть задана равной, например, принятой энергии Erx для 128-битного поля SYNC, умноженной на масштабный коэффициент S3, или Hth=Erx·S3.

Вероятность обнаружения больше 99% и частота ложных тревог менее 10-5 могут достигаться при SNR в -4 дБ, используя пороговую величину S3=14. Суммарная частота ложных тревог менее 10-9 может достигаться со всеми тремя этапами обнаружения. Это допускает, что три этапа обнаружения являются некоррелированными, так как для трех этапов используются разные типы обработки сигнала.

Для описанных выше вариантов осуществления обнаружение сигнала может достигаться на основе корреляции во временной области (фиг.5), обработки в частотной области (фиг.6) и обработки во временной области (фиг.7). Все три типа обработки сигнала могут использоваться для обеспечения хорошей эффективности обнаружения (например, высокая вероятность обнаружения и низкая частота ложных тревог) для плохих канальных условий (например, низкого SNR). Также может использоваться любая комбинация обработки сигнала для обнаружения сигнала.

Фиг.5, 6 и 7 показывают определенные варианты осуществления обнаружения сигнала, вхождения в синхронизм по времени, вхождения в синхронизм по частоте и оценки канала, которые могут выполняться другими способами. Например, обнаружение сигнала и вхождение в синхронизм по времени могут выполняться только с помощью 1-битного дифференциального коррелятора 530a с задержкой. Также может использоваться комбинация методик. Например, входные выборки могут поворачиваться на небольшое количество (например, два) предполагаемых уходов частоты. Остаточное отклонение частоты меньше для одного из предполагаемых уходов частоты, так что кодирование с сужением спектра по Баркеру (или когерентное накопление) может выполняться за большую длительность (например, 22 элементарных сигнала). Суженные символы от более длительного когерентного накопления могут предоставляться умножителю задержки и дифференциальному коррелятору, показанным на фиг.5. Обнаружение сигнала может достигаться для меньшего действующего SNR, поскольку когерентное накопление выполняется за большую длительность.

Фиг.5, 6 и 7 показывают типовую обработку сигнала блоками 410, 420 и 430 соответственно. Обработка может реализовываться различными способами, используя аппаратные средства, программное обеспечение и/или микропрограммное обеспечение. Например, блоки 410, 420 и 430 могут реализовываться с помощью выделенных аппаратных средств либо могут совместно использовать аппаратные средства. Цифровой процессор сигнала (DSP) и/или какой-нибудь другой тип процессора может выполнять обработку для блоков 410, 420 и 430 способом мультиплексирования с временным разделением. Буфер 402 выборок, буфер 514 символа и/или какой-нибудь другой буфер могут использоваться для буферизации данных для обработки.

Возвращаясь к фиг.4, после того как обнаружен PPDU, выполняется определение, предназначается ли принятый PPDU для 802.11b/g либо режима расширения диапазона, например, на основе преамбулы PLCP и/или заголовка PLCP. Процессор 440 приема DSSS обрабатывает принятый PPDU, если он предназначен для 802.11b/g. Процессор 450 приема DSSS обрабатывает принятый PPDU, если он предназначен для режима расширения диапазона.

Процессор 440 приема DSSS выполняет спектральное кодирование с сужением спектра и демодуляцию для 802.11b/g. В процессоре 440 многоотводный когерентный приемник/корректор 442 кодирует с сужением спектра входные выборки с помощью последовательности Баркера, корректирует суженные символы на основе оценок канала, объединяет компоненты сигнала по R приемным антеннам и предоставляет обнаруженные символы. Демодулятор (Demod) 444 преобразует обнаруженные символы на основе схемы модуляции (например, BPSK или QPSK), использованной для передачи, выполняет дифференциальное декодирование и предоставляет выходные биты, которые являются оценками информационных битов, отправленных передающей станцией 110.

Процессор 450 приема DSSS выполняет спектральное кодирование с сужением спектра, демодуляцию и декодирование FEC для режима расширения диапазона. В процессоре 450 фильтр 452 фильтрует входные выборки для каждой приемной антенны для удаления внеполосного шума и взаимных помех. Фильтр 452 также может производить повторную выборку входных выборок для каждой приемной антенны (1) для преобразования частоты дискретизации из частоты дискретизации в скорость передачи элементарного сигнала и/или (2) для компенсации ухода синхронизации по принятому PPDU. Для 802.11g входные выборки обычно имеют скорость в несколько раз выше скорости передачи элементарного сигнала OFDM в 20 МГц. В этом случае фильтр 452 может выполнять повторную дискретизацию от многократно 20 МГц до либо 11 МГц для многоотводного когерентного приемника, разделенного элементарными сигналами, либо 22 МГц для многоотводного когерентного приемника, разделенного половинами элементарных сигналов. Сигнал гетеродина (LO), используемый для преобразования с понижением частоты, и тактовый сигнал, используемый для формирования входных выборок, обычно получаются из одного и того же генератора опорной частоты. В этом случае отклонение частоты в тактовом сигнале может быть определено исходя из отклонения k os частоты, определенного блоком 420 вхождения в синхронизм по частоте для сигнала LO. Затем может быть определен уход синхронизации во входных выборках исходя из ухода k os частоты и несущей частоты. Фильтр 452 может выполнять периодическую регулировку ± Tadj исходя из ухода k os частоты, где Tadj может быть частью периода выборки.

В варианте осуществления фильтр 452 реализуется как многофазный фильтр, состоящий из блока из N базовых фильтров, где N>1. Каждый базовый фильтр ассоциируется с определенным множеством коэффициентов для определенного временного сдвига. В типовой конструкции фильтр 452 включает в себя 11 фильтров FIR, где каждый фильтр FIR имеет четыре отвода. Для создания каждой последующей выходной выборки может использоваться другой базовый фильтр. Если уход частоты равен нулю, то 11 базовых фильтров могут быть циклически пройдены в неизменном порядке, где каждая 11-я выборка образуется из того же базового фильтра. Чтобы компенсировать уход синхронизации, заданный базовый фильтр может пропускаться, а вместо него использоваться следующий базовый фильтр, либо один и тот же базовый фильтр может использоваться для двух последовательных выходных выборок. Регулировка синхронизации, таким образом, может достигаться путем выбора соответствующего базового фильтра, находящегося в употреблении.

Блок 454 частотной коррекции удаляет уход частоты в отрегулированных по времени выборках для каждой приемной антенны. Блок 454 может быть реализован с помощью генератора с числовым программным управлением (NCO) и комплексного умножителя, аналогичного умножителю 712 на фиг.7. NCO формирует вектор, вращающийся на уходе k os частоты, предоставленном блоком 420 вхождения в синхронизм по частоте. Умножитель умножает отрегулированные по времени выборки для каждой приемной антенны на вектор и предоставляет выборки с частотной коррекцией для этой антенны.

Многоотводный когерентный приемник/устройство 456 сужения спектра выполняет когерентное обнаружение выборок с частотной коррекцией с помощью оценок канала и объединяет компоненты сигнала по приемным антеннам и многолучевым распространениям. Многоотводный когерентный приемник 456 умножает выборки с частотной коррекцией для каждой приемной антенны на 11 канальных отводов, предоставленных блоком 430 оценки канала для этой антенны. Многоотводный когерентный приемник/устройство 456 сужения спектра также выполняет кодирование с сужением спектра с помощью последовательности Баркера, накапливает суженные символы для всех R антенн и предоставляет обнаруженные символы. В варианте осуществления оценки канала для R приемных антенн выводятся один раз исходя из поля SYNC и, возможно, других полей принятого PPDU, и эти оценки канала используются для всего принятого PPDU. Для этого варианта осуществления многоотводный когерентный приемник 456 не является отслеживающим радиоканал по принятому PPDU. В другом варианте осуществления оценки канала обновляются с использованием жестких решений, полученных из обнаруженных символов и/или решений, полученных путем перекодирования и повторного преобразования выходного сигнала декодера 464 FEC.

Блок 458 фазовой коррекции удаляет фазовую ошибку в обнаруженных символах. Фазовая ошибка обусловлена остаточным отклонением частоты, которое происходит от приемника 160 без фазовой синхронизации.

Фиг.8 показывает блок-схему варианта осуществления блока 458 фазовой коррекции. В блоке 458 умножитель 812 поворачивает каждый обнаруженный символ от многоотводного когерентного приемника 456 на опорную фазу θ ref(t) и предоставляет соответствующий символ с фазовой коррекцией. Блок 814 формирует жесткое решение (например, +1 или -1) для каждого символа с фазовой коррекцией. Умножитель 816 умножает каждый обнаруженный символ на соответствующее жесткое решение и предоставляет произведение для этого обнаруженного символа. Блок 818 вычисляет скользящее среднее произведений от умножителя 816 и предоставляет усредненное произведение. Для каждого периода символа блок 820 нормализует и сопрягает усредненное произведение и предоставляет опорную фазу θ ref(t) для обнаруженного символа для этого периода t символа. Опорная фаза, таким образом, может выводиться путем определения средних значений на интервале обнаруженных символов. Определение средних значений может быть предназначено для объяснения факта, что информация о фазе от известных символов пилот-сигнала в поле SYNC является более надежной, но может не быть актуальной, тогда как информация о фазе для обнаруженных символов может не быть надежной, но является более актуальной.

Возвращаясь к фиг.4, демодулятор 460 выполняет когерентную демодуляцию символов с фазовой коррекцией. Для BPSK демодулятор 460 может предоставлять вещественную часть каждого символа с фазовой коррекцией в качестве демодулированного символа, который является оценкой символа данных, отправленного передающей станцией 110. Для других схем модуляции демодулятор 460 может предоставлять символ модуляции, который наиболее вероятно отправлен для каждого символа с фазовой коррекцией, в качестве демодулированного символа.

Обращенный перемежитель 462 обратно перемежает демодулированные символы способом, дополнительным к перемежению, выполненному перемежителем 256 на фиг.2. Декодер 464 FEC декодирует обратно перемеженные символы способом, дополнительным к кодированию, выполненному кодером 252 FEC на фиг.2, и предоставляет выходные данные. Мультиплексор 470 принимает выходные данные от процессоров 440 и 450 приема DSSS, предоставляет выходные данные от процессора 440 приема DSSS, если принятый PPDU предназначен для 802.11b/g, и предоставляет выходные данные от процессора 450 приема DSSS, если принятый PPDU предназначен для режима расширения диапазона.

Фиг.4 показывает конкретный вариант осуществления процессора 160 приема для 802.11b/g и режима расширения диапазона. Процессор 160 также может реализовываться с помощью иных конструкций, и это находится в пределах объема изобретения. Вообще, обработка процессором 440 приема DSSS является дополнительной к обработке процессором 240 передачи DSSS на передающей станции 110, и обработка процессором 450 приема DSSS является дополнительной к обработке процессором 250 передачи DSSS. Фиг.4 показывает типовые конструкции процессоров 440 и 450 приема DSSS, которые могут включать в себя другие и/или отличные блоки обработки, не показанные на фиг.4.

Фиг.9 показывает процесс 900 для выполнения обнаружения сигнала для первого этапа. Входные выборки кодируются с сужением спектра с помощью кодовой последовательности, чтобы сформировать суженные символы, например, на скорости передачи элементарного сигнала (этап 912). Формируются произведения суженных символов по меньшей мере для двух разных задержек (этап 914). Каждое произведение формируется исходя из суженного символа и комплексного сопряжения другого суженного символа, который находится по меньшей мере одним периодом символа ранее. Например, 1-символьные произведения с задержкой и 2-символьные произведения с задержкой могут формироваться, как показано на фиг.5, с каждым 1-символьным произведением с задержкой, формируемым с двумя суженными символами, которые разделяются одним периодом символа, и каждым 2-символьным произведением с задержкой, формируемым с двумя суженными символами, которые разделяются двумя периодами символа.

Затем выполняется корреляция между произведениями для каждой задержки и известными значениями для той задержки (этап 916). Известные значения могут быть произведениями битов пилот-сигнала, как показано на фиг.5. Расположенные рядом произведения для каждой задержки могут суммироваться перед выполнением корреляции для подсчета разброса задержек в радиоканале, что также показано на фиг.5. Результаты корреляции для всех задержек объединяются (этап 918). Результаты корреляции для 2-символьной задержки могут поворачиваться на множество предполагаемых фаз и объединяться с соответствующими результатами корреляции для 1-символьной задержки, и могут выбираться объединенные результаты корреляции с наибольшей величиной среди множества предполагаемых фаз, как показано на фиг.5. В качестве альтернативы результаты корреляции для разных задержек могут некогерентно объединяться.

Затем на основе объединенных результатов корреляции обнаруживается наличие сигнала/передаваемых данных, например, путем сравнения объединенных результатов корреляции с самонастраивающейся пороговой величиной Zth, которая является функцией принятой энергии (этап 920). Синхронизация сигнала также определяется исходя из объединенных результатов корреляции, например, путем обнаружения всплеска в объединенных результатах корреляции (этап 922).

Фиг.10 показывает процесс 1000 для выполнения обнаружения сигнала с несколькими (например, тремя) этапами с использованием разных типов обработки сигнала. Самонастраивающиеся пороговые величины, используемые для обнаружения сигнала по этапам, выводятся исходя из принятой энергии для интервала символов (этап 1012). Обнаружение сигнала для первого этапа выполняется с использованием корреляции во временной области и первой пороговой величины (этап 1014). Для первого этапа произведения символов могут формироваться по меньшей мере для одной задержки, может выполняться корреляция между произведениями для каждой задержки и известными значениями, и обнаружение может быть объявлено исходя из результатов корреляции по меньшей мере для одной задержки и первой пороговой величины. Обнаружение сигнала для второго этапа выполняется с использованием обработки в частотной области и второй пороговой величины (этап 1016). Для второго этапа могут определяться энергии для множества элементов разрешения по частоте, и обнаружение может быть объявлено исходя из энергий для этих элементов разрешения по частоте и второй пороговой величины. Обнаружение сигнала для третьего этапа выполняется с использованием обработки во временной области и третьей пороговой величины (этап 1018). Может выводиться множество канальных отводов для оценки импульсной характеристики канала, и обнаружение может быть объявлено исходя из канальных отводов и третьей пороговой величины. Наличие сигнала объявляется на основе результатов первого, второго и третьего этапов (этап 1020).

Фиг.11 показывает процесс 1100 для приема передаваемых данных или PPDU. Синхронизация входных выборок регулируется для получения отрегулированных по времени выборок (этап 1112). Регулировка синхронизации может выполняться с помощью многофазного фильтра и/или на основе ухода частоты, определенного во время вхождения в синхронизм по частоте. Уход частоты в отрегулированных по времени выборках удаляется для получения выборок с частотной коррекцией (этап 1114). Выборки с частотной коррекцией обрабатываются с помощью оценки канала (например, используя многоотводный когерентный приемник) для получения обнаруженных символов (этап 1116). Фазы обнаруженных символов корректируются для получения символов с фазовой коррекцией (этап 1118). Для фазовой коррекции может выводиться опорная фаза на основе обнаруженных символов, и фазы обнаруженных символов могут корректирования исходя из опорной фазы. Над символами с фазовой коррекцией выполняется демодуляция для получения демодулированных символов (этап 1120). Демодулированные символы обратно перемежаются (этап 1122), и обратно перемеженные символы декодируются для получения декодированных данных (этап 1124).

Процессы, изображенные и описанные в отношении фиг.9-11, могут быть реализованы как функции, выполняемые процессором 160. Отдельные блоки могут содержать команды, которые выполняются процессором 160.

Описанные здесь методики могут быть реализованы различными средствами. Например, эти методики могут быть реализованы в аппаратных средствах, микропрограммном обеспечении, программном обеспечении либо их сочетании. Для аппаратной реализации блоки обработки, используемые для выполнения обнаружения сигнала, вхождения в синхронизм и демодуляции, могут реализовываться в одной или нескольких специализированных интегральных схемах (ASIC), цифровых процессорах сигналов (DSP), устройствах цифровой обработки сигналов (DSPD), программируемых логических устройствах (PLD), программируемых пользователем вентильных матрицах (FPGA), процессорах, контроллерах, микроконтроллерах, микропроцессорах, электронных устройствах, других электронных блоках, спроектированных для выполнения описанных здесь функций, или их сочетаниях.

Для программной реализации методики могут быть реализованы с помощью модулей (например, процедур, функций и так далее), которые выполняют описанные здесь функции. Программные коды могут храниться в запоминающем устройстве (например, запоминающем устройстве 182 на фиг.1) и исполняться процессором (например, процессором 160 и/или процессором 180). Запоминающее устройство может быть реализовано внутри процессора или может быть внешним по отношению к процессору.

Предшествующее описание раскрытых вариантов осуществления предоставляется, чтобы дать возможность любому специалисту в данной области техники создать или использовать настоящее изобретение. Различные модификации к этим вариантам осуществления будут полностью очевидны специалистам в данной области техники, а общие принципы, определенные в этом документе, могут быть применены к другим вариантам осуществления без отклонения от сущности или объема изобретения. Таким образом, настоящее изобретение не предназначено, чтобы ограничиваться показанными в этом документе вариантами осуществления, а должно соответствовать самому широкому объему, согласующемуся с принципами и новыми признаками, раскрытыми в этом документе.

Изобретение относится к области беспроводной связи и, в частности, к обнаружению и демодуляции сигнала. Техническим результатом является обеспечение сети беспроводной связи и станции, функционирования с расширенным диапазоном покрытия. Указанный технический результат достигается тем, что обнаружение сигналов выполняется в несколько этапов с использованием корреляции во временной области для первого этапа, обработки в частотной области для второго этапа и обработки во временной области для третьего этапа. Для первого этапа формируют произведения символов по меньшей мере для двух разных задержек, выполняют корреляцию между произведениями для каждой задержки и известными значениями и результаты корреляции для всех задержек объединяют и используют для объявления наличия сигнала. Для демодуляции регулируют синхронизацию входных выборок для получения отрегулированных по времени выборок. Уход частоты оценивают и удаляют из отрегулированных по времени выборок для получения выборок с частотной коррекцией, которые обрабатывают с помощью оценки канала для получения обнаруженных символов. Фазы обнаруженных символов корректируют для получения символов с фазовой коррекцией, которые демодулируют, обратно перемежают и декодируют. 8 н. и 32 з.п. ф-лы, 11 ил., 1 табл.

1. Способ выполнения обнаружения сигнала, содержащий этапы, на которых

формируют первую последовательность произведений первого символа с задержкой для последовательности символов, причем каждое произведение первого символа с задержкой получают в результате по меньшей мере операции первого произведения на основе первого и второго символов последовательности символов, которые разделены задержкой первого символа;

формируют вторую последовательность произведений второго символа с задержкой для последовательности символов, причем каждое произведение второго символа с задержкой получают в результате по меньшей мере операции второго произведения на основе первого и третьего символов последовательности символов, которые разделены задержкой второго символа;

выполняют корреляцию между первой последовательностью и первыми известными значениями для получения результатов первой корреляции;

выполняют корреляцию между второй последовательностью и вторыми известными значениями для получения результатов второй корреляции; и

обнаруживают наличие сигнала на основе результатов первой и второй корреляций.

2. Способ по п.1, в котором операции первого и второго произведений содержат умножение первого символа на комплексные сопряжения второго и третьего символов соответственно.

3. Способ по п.1, в котором задержки первого и второго символов различаются более чем на один период символа.

4. Способ по п.1, в котором обнаружение наличия сигнала на основе результатов первой и второй корреляций содержит этапы, на которых выполняют фазовый поворот результатов второй корреляции; объединяют результаты второй корреляции с фазовым поворотом с результатами первой корреляции; и обнаруживают наличие сигнала на основе объединенных результатов корреляций.

5. Способ по п.1, в котором обнаружение наличия сигнала на основе результатов первой и второй корреляций содержит этапы, на которых объединяют результаты первой и второй корреляций; и сравнивают объединенные результаты корреляций с пороговой величиной, выводимой на основе вычисленной принятой энергии по меньшей мере двух символов.

6. Способ выполнения обнаружения сигнала, содержащий этапы, на которых формируют множество первых последовательностей произведений первого символа с задержкой для множества последовательностей символов, причем каждое произведение первого символа с задержкой для каждой первой последовательности получают в результате операции первого произведения на основе первого и второго символов из одной из множества последовательностей символов, которые разделены задержкой первого символа;

формируют множество вторых последовательностей произведений второго символа с задержкой для множества последовательностей символов, причем каждое произведение второго символа с задержкой для каждой второй последовательности получают в результате операции второго произведения на основе первого и третьего символов из одной из множества последовательностей символов, которые разделены задержкой второго символа;

объединяют множество первых последовательностей;

выполняют корреляцию между объединенным множеством первых последовательностей и первыми известными значениями для получения результатов первой корреляции;

объединяют множество вторых последовательностей;

выполняют корреляцию между объединенным множеством вторых последовательностей и вторыми известными значениями для получения результатов второй корреляции; и обнаруживают наличие сигнала на основе результатов первой и второй корреляций.

7. Способ по п.6, в котором операции первого и второго произведений содержат умножение первого символа на комплексные сопряжения второго и третьего символов соответственно.

8. Способ по п.6, в котором задержки первого и второго символов различаются более чем на один период символа.

9. Способ по п.6, в котором обнаружение наличия сигнала на основе результатов первой и второй корреляций содержит этапы, на которых выполняют фазовый поворот результатов второй корреляции; объединяют результаты второй корреляции с фазовым поворотом с результатами первой корреляции; и обнаруживают наличие сигнала на основе объединенных результатов корреляции.

10. Способ по п.6, в котором обнаружение наличия сигнала на основе результатов первой и второй корреляций содержит этапы, на которых объединяют результаты первой и второй корреляций; и сравнивают объединенные результаты корреляций с пороговой величиной, выводимой на основе вычисленной принятой энергии по меньшей мере двух символов.

11. Устройство для выполнения обнаружения сигнала, содержащее логику для формирования первой последовательности произведений первого символа с задержкой для последовательности символов, причем каждое произведение первого символа с задержкой получается в результате по меньшей мере операции первого произведения на основе первого и второго символов последовательности символов, которые разделены задержкой первого символа;