Изобретения относятся к области радиотехники, в частности к способу и устройству частотно-временной синхронизации системы связи.

В системах связи, в том числе с подвижными объектами, каналы распространения сигнала между приемником и передатчиком данных являются многолучевыми и нестационарными. Эффективность систем связи во многом определяется способностью алгоритмов частотно-временной синхронизации обеспечить в многолучевых нестационарных каналах необходимую точность оценки временного положения сигнала и частотного рассогласования между частотой входного сигнала и частотой опорного генератора.

Для начальной частотно-временной синхронизации обычно используют специальный сигнал - преамбулу, который предшествует информационному сообщению. Преамбула и информационное сообщение могут представлять собой сигнал с кодовым расширением спектра (CDM - Code - Division Multiplex) или OFDM (Orthogonal Frequency Division Multiplexing) сигнал.

Для формирования сигнала с кодовым расширением спектра используют псевдослучайные последовательности (ПСП). CDM сигнал состоит из последовательности кодовых символов длиной несколько чипов. Чип ПСП - это длительность одного элементарного временного интервала ПСП.

OFDM сигнал представляет собой последовательность OFDM символов. Каждый такой символ состоит из двух частей - префикса и многочастотного информационного символа. Многочастотный информационный символ представляет собой сумму модулированных гармоник. Под префиксом понимают некоторую последовательность отсчетов сигнала, которая непосредственно предшествует каждому многочастотному информационному символу и представляет собой часть этого символа. Как правило, длительность префикса меньше длительности информационного символа. Наличие префикса при обработке сигнала позволяет уменьшить или полностью устранить межсимвольную интерференцию (IEEE Std 802.11а - 1999, Прокис Дж., Цифровая связь. Перевод с английского. М.: Радио и связь, 2000, с.593.).

Известен способ частотной и временной синхронизации, описанный в работе Tufvesson F., Faulkne M., Hoeher P., Edfors О., OFDM Time and Frequency Synchronization by Spread Spectrum Pilot Technique // 8th IEEE Communication Theory Mini Conference in conjunction to ICC’99, june 1999, p.115-119. В данной статье предложен способ частотной и временной синхронизации для OFDM систем, который базируется на использовании непрерывной кодовой последовательности. Кодовая последовательность добавляется к OFDM информационному сигналу или используется отдельно как сигнал преамбулы. Этот способ временной и частотной синхронизации заключается в следующем.

Входной сигнал обрабатывают в нескольких фильтрах, согласованных с различными частями известной кодовой последовательности. Выходные сигналы согласованных фильтров используют для формирования комплексной решающей функции. Каждое слагаемое решающей функции представляет собой сумму по парных произведений откликов согласованных фильтров на соответствующие им соседние комплексно-сопряженные отклики согласованных фильтров.

Оценку временной задержки (положения) входного сигнала определяют по положению максимума квадрата модуля решающей функции. Оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала определяют по значению аргумента решающей функции в точке, соответствующей оценке временной задержки.

Описанный способ предполагает одноэтапную процедуру частотно-временной синхронизации. Вследствие этого при больших величинах возможного частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала при реализации способа необходимо использовать фильтры, согласованные с более короткими частями известной кодовой последовательности. Это приводит к ухудшению точности оценки временной задержки и частотной расстройки и является главным недостатком данного способа синхронизации.

Известен способ частотно-временной синхронизации, описанный в статье Schmidi Т.М., Сох D.С., Robust Frequency and Timing Synchronization for OFDM // IEEE Tran. on corn, v.45, №12, Dec.1997, p.1613-1621.

В упомянутой статье предложен способ синхронизации параметров сигнала в OFDM (Orthogonal Frequency Division Multiplexing) системах, который основан на приеме преамбулы, состоящей из двух OFDM символов. В процессе синхронизации на первом этапе по первому символу определяют временное положение сигнала, а также осуществляют грубую оценку частного рассогласования с точностью до n·π·T, n=1,2..., Т - длительность OFDM символа. Окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала осуществляют на втором этапе с использованием второго OFDM символа.

Первый OFDM символ состоит из двух идентичных частей, отличающихся при приеме фазовым сдвигом. Сначала формируют комплексную решающую функцию первого этапа как произведения выборок первой части символа на соответствующие комплексно сопряженные выборки второй части символа. Оценку временной задержки входного сигнала определяют по положению максимума квадрата модуля решающей функции первого этапа. Грубую оценку частотного сдвига между несущей входного сигнала и частотой опорного сигнала вычисляют по значению аргумента решающей функции первого этапа в точке, соответствующей оценке временной задержки.

Для определения окончательной оценки частотного рассогласования формируют решающую функцию второго этапа для всевозможный значений n, используя оба OFDM символа. Оценку параметра n определяют по положению максимума решающей функции второго этапа.

Недостаткам описанного способа является невысокая точность оценки временного положения сигнала вследствие достаточно широкой плоской вершины решающей функции первого этапа, ширина которой равна длительности префикса OFDM символа. Кроме того, недостатком является неполное использование ресурса преамбулы, а именно отказ от использования второго OFDM символа при оценке временного положения сигнала. Перечисленные недостатки приводят к низкой помехоустойчивости частотно-временной синхронизации системы связи.

Наиболее близким к заявляемому решению является способ частотно-временной синхронизации системы связи и алгоритм его реализации, приведенные в книге Nee R. Prasad R., OFDM for Wireless Multimedia Communication, London: “Artech House”, 2000, chapter 4. Synchronization. 4.6. Synchronization using Special Training Symbols, стр.86-88; chapter 10. Applications of OFDM. 10.5.4 Training, стр.246-247.

Этот способ частотно-временной синхронизации системы связи заключается в следующем:

на передающей стороне формируют цифровой видеосигнал, состоящий из двух частей: первая часть представляет собой 10 коротких многочастотных символов, вторая часть представляет собой 2 длинных многочастотных символа и префикс, состоящий из части длинного символа; фильтруют сформированный цифровой видеосигнал, выполняют его цифроаналоговое преобразование, осуществляют перенос сигнала на несущую частоту, усиливают и передают его по каналу связи;

на приемной стороне входной сигнал фильтруют, усиливают, переносят на видеочастоту, осуществляют его аналого-цифровое преобразование и децимацию, формируя входной цифровой комплексный сигнал на видеочастоте; частотно-временную синхронизацию осуществляют в два этапа: на первом этапе определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего осуществляют согласованную с одним коротким многочастотным символом фильтрацию сформированного входного цифрового комплексного сигнала, формируя комплексные отклики первого этапа; вычисляют квадраты модулей комплексных откликов первого этапа, формируя решающую функцию первого этапа; определяют временные положения локальных максимумов решающей функции первого этапа, превышающих заданный порог первого этапа H1; запоминают комплексные отклики первого этапа, соответствующие локальным максимумам решающей функции первого этапа; формируют предварительную оценку частотного сдвига по усредненной разности фаз комплексных откликов первого этапа, соответствующих локальным максимумам решающей функции первого этапа; на втором этапе осуществляют оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей входного сигнала и частотой опорного сигнала, для чего корректируют фазу входного цифрового комплексного сигнала на интервале работы второго этапа с учетом предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала; осуществляют согласованную с одним длинным многочастотным символом фильтрацию скорректированного входного цифрового комплексного сигнала, формируя комплексные отклики второго этапа; вычисляют квадраты модулей комплексных откликов второго этапа, формируя решающую функцию второго этапа; сравнивают значения решающей функции второго этапа с заданным порогом второго этапа H2, при непревышении порога полагают преамбулу необнаруженной; при превышении порога второго этапа Н2 полагают преамбулу обнаруженной, тогда определяют оценку временного положения преамбулы по временному положению первого превышения порога второго этапа Н2; определяют временные положения локальных максимумов решающей функции второго этапа, превышающих заданный порог второго этапа Н2; определяют дополнительную оценку частотного сдвига по разности фаз двух комплексных откликов второго этапа, соответствующих локальным максимумам решающей функции второго этапа; определяют окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как сумму предварительной и дополнительной оценки частотного сдвига.

Оценку временного положения преамбулы, а именно начала преамбулы определяют равной разности временного положения первого превышения порога второго этапа Н2 и суммы длительностей первой части преамбулы и префикса.

Дополнительную оценку частотного сдвига определяют, например, как отношение разности фаз смежных комплексных откликов второго этапа к длительности длинного многочастотного символа.

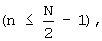

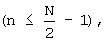

Заметим, что в упомянутом источнике информации структурная схема устройства частотно-временной синхронизации системы связи не приведена. Однако из описания алгоритма можно представить устройство, которое реализует способ-прототип. Устройство-прототип на передающей стороне выполнено на фиг.1, устройство-прототип на приемной стороне выполнено на фиг.2.

Устройство-прототип на передающей стороне (фиг.1) содержит тактовый генератор 1, демультиплексор 2, первый счетчик 3, формирующий число коротких многочастотных символов, второй счетчик 4, формирующий короткий многочастотный символ, первое постоянное запоминающее устройство 5, третий счетчик 6, формирующий длинный многочастотный символ, четвертый счетчик 7, формирующий число длинных многочастотных символов, второе постоянное запоминающее устройство 8, сумматор 9, блок формирования данных 10, передающий тракт 11, при этом вход тактового генератора 1 является входом устройства, выход тактового генератора 1 соединен с первым входом демультиплексора 2, второй вход которого соединен с выходом первого счетчика 3, первый выход демультиплексора 2 соединен со входом второго счетчика 4, выход которого соединен со входами первого счетчика 3 и первого постоянного запоминающего устройства 5, выход первого постоянного запоминающего устройства 5 соединен с первым входом сумматора 9, второй выход демультиплексора 2 соединен со входом третьего счетчика 6, выход которого соединен со входами второго постоянного запоминающего устройства 8 и четвертого счетчика 7, выход которого соединен с третьим входом демультиплексора 2 и входом блока формирования данных 10, выход которого соединен с третьим входом сумматора 9, второй вход которого соединен с выходом второго постоянного запоминающего устройства 8, выход сумматора 9 соединен со входом передающего тракта 11, выход которого является выходом устройства.

Устройство-прототип на приемной стороне (фиг.2) содержит приемный тракт 12, первый 13 и второй 14 согласованные фильтры, осуществляющие на первом этапе согласованную с одним коротким многочастотным символом фильтрацию сформированного входного цифрового комплексного сигнала и формирующие комплексные отклики первого этапа, первый 15 и второй 16 перемножители, первый сумматор 17, комплексный перемножитель 18, блок формирования гармоники 19, блок расчета частотного сдвига 20, первый блок сравнения с порогом 21, блок управления 22, тактовый генератор 23, третий 24 и четвертый 25 согласованные фильтры, осуществляющие на втором этапе согласованную с одним длинным многочастотным символом фильтрацию скорректированного входного цифрового комплексного сигнала и формирующие комплексные отклики второго этапа, третий 26 и четвертый 27 перемножители, второй сумматор 28, второй блок сравнения с порогом 29, блок расчета дополнительного частотного сдвига 30 и третий сумматор 31, при этом вход приемного тракта 12 является входом устройства, первый выход приемного тракта 12 соединен со входом первого согласованного фильтра 13 и первым входом комплексного перемножителя 18, второй выход приемного тракта 12 соединен со входом второго согласованного фильтра 14 и вторым входом комплексного перемножителя 18, выход первого согласованного фильтра 13 соединен с первым и вторым входами первого перемножителя 15 и вторым входом блока расчета частотного сдвига 20, выход второго согласованного фильтра 14 соединен с первым и вторым входами второго перемножителя 16 и третьим входом блока расчета частотного сдвига 20, выходы первого 15 и второго 16 перемножителей соединены соответственно с первым и вторым входами первого сумматора 17, выход которого соединен с первым входом первого блока сравнения с порогом 21, второй вход которого объединен с четвертым входом блока расчета частотного сдвига 20 и соединен с первым выходом блока управления 22, выход первого блока сравнения с порогом 21 соединен с первым входом блока расчета частотного сдвига 20 и со вторым входом блока управления 22, пятый выход которого соединен с пятым входом блока расчета частотного сдвига 20, выход блока расчета частотного сдвига 20 соединен с первым входом блока формирования гармоники 19 и первым входом третьего сумматора 31, второй вход блока формирования гармоники 19 объединен с третьим входом блока управления 22 и соединен с выходом тактового генератора 23, первый и второй выходы блока формирования гармоники 18 соединены соответственно с третьим и четвертым входами комплексного перемножителя 18, первый и второй выходы которого соединены соответственно со входами третьего 24 и четвертого 25 согласованных фильтров, выход третьего согласованного фильтра 24 соединен с первым и вторым входами третьего перемножителя 26 и первым входом блока расчета дополнительного частотного сдвига 30, выход четвертого согласованного фильтра 25 соединен с первым и вторым входами четвертого перемножителя 27 и вторым входом блока расчета дополнительного частотного сдвига 30, выходы третьего 26 и четвертого 27 перемножителей соединены соответственно с первым и вторым входами второго сумматора 28, выход которого соединен с первым входом второго блока сравнения с порогом 29, второй вход которого соединен со вторым выходом блока управления 22 и пятым входом блока расчета дополнительного частотного сдвига 30, выход второго блока сравнения с порогом 29 соединен с третьим входом блока расчета дополнительного частотного сдвига 30 и первым входом блока управления 22, третий выход которого соединен с четвертым входом блока расчета дополнительного частотного сдвига 30, четвертый выход блока управления является первым выходом устройства, выход блока расчета дополнительного частотного сдвига 30 соединен со вторым входом третьего сумматора 31, выход третьего сумматора 31 является вторым выходом устройства.

Устройство частотно-временной синхронизации системы связи (на передающей стороне, фиг.1) работает следующим образом.

Тактовый генератор 1, демультиплексор 2, первый счетчик 3, формирующий число коротких многочастотных символов, второй счетчик 4, формирующий короткий многочастотный символ, третий счетчик 6, формирующий длинный многочастотный символ, четвертый счетчик 7, формирующий число длинных многочастотных символов, первое постоянное запоминающее устройство 5, в котором записан короткий многочастотный символ, второе постоянное запоминающее устройство 8, в котором записан длинный многочастотный символ, и сумматор 9 описанного устройства передачи используют для формирования цифрового видеосигнала преамбулы, а блок формирования данных 10 используют для формирования информационного сигнала системы связи. Временная структура сигнала преамбулы определена заранее.

Сформированный сигнал преамбулы и сигнал данных поступают через передающий тракт 11 в канал связи.

При формировании и передаче сигнала преамбулы и информационного сигнала осуществляют временное разделение. Информационный сигнал начинает поступать в передающий тракт по сигналу окончания процедуры формирования сигнала преамбулы.

Процедуру формирования сигнала преамбулы выполняют следующим образом. Тактовый генератор 1 по команде управления начала или повтора передачи сигнала преамбулы, поступающего на его вход, формирует тактовые импульсы. С выхода тактового генератора 1 тактовые импульсы поступают на первый вход демультиплексора 2, на второй управляемый вход которого с выхода первого счетчика 3 поступает сигнал коммутации. На третий управляемый вход демультиплексора 2 и на управляемый вход блока формирования данных 10 с выхода четвертого счетчика 7 поступает сигнал коммутации окончания преамбулы.

Исходное состояние сигналов коммутации устанавливают таким образом, что первоначально тактовые импульсы с первого выхода демультиплексора 2 поступают на вход второго счетчика 4. Этот счетчик программируют таким образом, что на его выходах формируется сигнал, соответствующий адресам текущих элементов короткого многочастотного символа, а сигнал на старшем разряде, равный, например, логической единице, индицирует окончание считывания очередного короткого многочастотного символа.

По сигналам адресов, поступающим с выхода второго счетчика 4 на вход первого постоянного запоминающего устройства 5, выполняют циклическое считывание текущих элементов короткого символа, которые поступают с выхода первого постоянного запоминающего устройства 5 на первый вход сумматора 9 и далее с его выхода поступают на вход передающего тракта 11. По сигналу окончания считывания очередного короткого многочастотного символа, который поступает на вход первого счетчика 3 с выхода второго счетчика 4, накапливают число циклов считывания и формируют на выходе первого счетчика 3 сигнал управления, равный, например, логической единице, если число циклов равно заданному числу N=10 коротких многочастотных символов в сигнале преамбулы.

При этом в течение временного интервала формирования заданного числа коротких многочастотных символов с выхода второго постоянного запоминающего устройства 8 на второй вход сумматора 9 и с блока формирования данных 10 на третий вход сумматора 9 считывают сигналы, равные нулю.

По сформированному сигналу управления, который поступает с выхода первого счетчика 3 на второй вход демультиплексора 2, осуществляют коммутацию демультиплексора 2, и тактовые импульсы начинают поступать только со второго выхода демультиплексора 2 на вход третьего счетчика 6.

Третий счетчик 6 программируют таким образом, что на его выходах формируют сигнал, соответствующий адресам текущих элементов длинного многочастотного символа, а сигнал на старшем разряде, равный, например, логической единице, индицирует окончание считывания очередного длинного символа. Исходно третий счетчик 6 устанавливают таким образом, чтобы выходной сигнал соответствовал началу префикса.

По сигналам адресов, поступающим с выхода третьего счетчика 6 на вход второго постоянного запоминающего устройства 8, выполняют циклическое считывание текущих элементов длинного многочастотного символа, которые поступают на второй вход сумматора 9. По сигналу окончания считывания очередного длинного символа, который поступает на вход четвертого счетчика 7 с выхода третьего счетчика 6, накапливают число циклов считывания и формируют на выходе четвертого счетчика 7 сигнал управления, равный, например, логической единице, если число циклов равно трем - префиксу и двум длинным многочастотным символам в сигнале преамбулы.

При этом в течение временного интервала формирования заданного числа длинных многочастотных символов, поступающих с выхода первого постоянного запоминающего устройства 5 на первый вход сумматора 9 и с выхода блока формирования данных 10 на третий вход сумматора 9, считывают сигналы, равные нулю.

По сигналу окончания формирования заданного числа длинных многочастотных символов, который поступает в выхода четвертого счетчика 7 на третий вход демультиплексора 2 и на управляемый вход блока формирования данных 10, осуществляют коммутацию таким образом, что с выхода первого постоянного запоминающего устройства 5 на первый вход сумматора 9 и с выхода второго постоянного запоминающего устройства 8 на второй вход сумматора 9, считывают сигналы, равные нулю, а с выхода блока формирования данных 10 на третий вход сумматора 9 считывают информационный сигнал.

С выхода сумматора 9 сформированный цифровой видеосигнал поступает в передающий тракт 11. В передающем тракте 11 сигнал преамбулы и информационный сигнал преобразуют, выполняя стандартную последовательность операций (фильтрацию, цифроаналоговое преобразование, модуляцию, перенос на несущую частоту, усиление и т.д.), и осуществляют передачу полученного сигнала (сообщения) в канал связи.

Устройство частотно-временной синхронизации системы связи (на приемной стороне, фиг.2) работает следующим образом.

На приемной стороне в приемном тракте 12 входной сигнал предварительно фильтруют, усиливают, переносят на видеочастоту, осуществляют его аналого-цифровое преобразование, децимацию и т.д. В результате чего формируют входной цифровой комплексный сигнал на видеочастоте. Для частотно-временной синхронизации, которая состоит из двух этапов, используют сигнал преамбулы. При этом на первом этапе определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала. На втором этапе осуществляют оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала.

На первом этапе синфазная и квадратурная составляющие входного цифрового комплексного сигнала с первого и второго выходов приемного тракта 12 поступают соответственно на входы первого 13 и второго 14 согласованных фильтров и на первый и второй входы комплексного перемножителя 18.

В первом 13 и втором 14 согласованных фильтрах на первом этапе осуществляют согласованную с одним коротким многочастотным символом фильтрацию соответственно синфазной и квадратурной компонент входного цифрового комплексного сигнала и формируют отклики для синфазной и квадратурной составляющих входного цифрового комплексного сигнала, которые поступают соответственно на первые и вторые входы первого 15 и второго 16 перемножителей и на второй и третий входы блока расчета частотного сдвига 20. В первом 15 и втором 16 перемножителях вычисляют квадраты откликов для синфазной и квадратурной составляющих входного цифрового комплексного сигнала первого этапа, которые поступают на первый и второй входы первого сумматора 17. В первом сумматоре 17 путем суммирования соответствующих квадратов откликов синфазной и квадратурной составляющих входного цифрового комплексного сигнала вычисляют квадраты модулей комплексных откликов первого этапа, формируя решающую функцию первого этапа. Отклики первого этапа поступают с выхода первого сумматора 17 на первый вход первого блока сравнения с порогом 21.

В первом блоке сравнения с порогом 21 последовательно сравнивают результаты суммирования с выхода первого сумматора 17 с порогом первого этапа H1. Результаты сравнения с выхода первого блока сравнения с порогом 21 поступают на первый вход блока расчета частотного сдвига 20 и на второй вход блока управления 22.

На второй вход первого блока сравнения с порогом 21 и на четвертый вход блока расчета частотного сдвига 20 с первого выхода блока управления 22 поступает сигнал управления, соответствующий окончанию временной области превышения значениями решающей функции первого этапа порога H1. По этому сигналу в первом блоке сравнения с порогом 21 осуществляют установку первоначального (исходного) значения порога первого этапа и в блоке расчета частотного сдвига 20 запоминают синфазные и квадратурные составляющие комплексных откликов первого этапа, соответствующие локальному максимуму решающей функции первого этапа (поступившие на второй и третий входы блока 20 с первого 13 и второго 14 согласованных фильтров).

В блоке расчета частотного сдвига 20 по сигналу превышения порога первого этапа и по управляющему сигналу окончания временной области превышения значениями решающей функции первого этапа порога H1 определяют временные положения, соответствующие локальным максимумам решающей функции первого этапа.

По сигналу окончания приема первой части преамбулы, который поступает с пятого выхода блока управления 22 на пятый вход блока расчета частотного сдвига 20, в блоке 20 по синфазным и квадратурным составляющим комплексных откликов первого этапа, соответствующим локальным максимумам решающей функции первого этапа, определяют предварительную оценку частотного сдвига. Предварительную оценку частотного сдвига формируют, например, как отношение усредненной разности фаз комплексных откликов первого этапа, соответствующих локальным максимумам, к длительности короткого многочастотного символа. Усредненную разность фаз формируют, например, следующим образом. Для временных позиций локальных максимумов решающей функции первого этапа формируют сумму произведений пар текущих комплексных откликов и предыдущих комплексно-сопряженных откликов. Значение аргумента полученного комплексного числа равно усредненной разности фаз. При этом отношение усредненной разности фаз к длительности короткого многочастотного символа равно предварительной оценке частотного сдвига.

Оценка предварительного частотного сдвига поступает с выхода блока расчета частотного сдвига 20 на первый вход блока формирования гармоники 19 и на первый вход третьего сумматора 31 и соответствует значению "грубой" оценки частотной расстройки. На второй вход блока формирования гармоники 19 и на третий вход блока управления 22 с выхода тактового генератора 23 поступает сигнал тактовой частоты.

В блоке формирования гармоники 19 по предварительной оценке частотного сдвига и сигналу с тактового генератора 23 формируют комплексный множитель единичной амплитуды, фаза которого равна произведению предварительной оценки частотного сдвига на временное положение текущих отсчетов, что соответствует стандартному экспоненциальному представлению комплексного множителя. С другой стороны комплексный множитель может быть эквивалентно сформирован в виде синфазной и квадратурной компоненты. В этом случае синфазная часть комплексного множителя равна косинусу, а мнимая часть - синусу аргумента, который равен произведению предварительной оценки частотного сдвига на временное положение текущих отсчетов. Данное представление комплексного множителя легко реализуется в функциональном преобразователе на базе устройства памяти, в котором записаны значения соответствующих отсчетов функций синуса и косинуса.

Сформированные квадратурные составляющие комплексного множителя с первого и второго выходов блока формирования гармоники 19 поступают соответственно на третий и четвертый входы комплексного перемножителя 18.

В комплексном перемножителе 18 корректируют фазу входного цифрового комплексного сигнала для второго этапа синхронизации с учетом предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, полученной на первом этапе. Для этого в комплексном перемножителе 18 осуществляют известную операцию умножения отсчетов входного цифрового комплексного сигнала на комплексный множитель.

Синфазная и квадратурная составляющие скорректированного входного цифрового комплексного сигнала с первого и второго выходов комплексного перемножителя 18 поступают соответственно на входы третьего 24 и четвертого 25 согласованных фильтров.

В третьем 24 и четвертом 25 согласованных фильтрах для синфазной и квадратурной составляющих входного скорректированного цифрового комплексного сигнала осуществляют фильтрацию, согласованную с одним длинным многочастотным символом, и формируют соответственно синфазные и квадратурные отклики второго этапа. Сформированные синфазные и квадратурные составляющие откликов второго этапа с выходов третьего 24 и четвертого 25 согласованных фильтров поступают соответственно на первый и второй входы третьего 26 (синфазного) и четвертого 27 (квадратурного) перемножителей и на первый и второй входы блока расчета дополнительного частотного сдвига 30. В третьем 26 и четвертом 27 перемножителях формируют соответственно квадраты синфазной и квадратурной составляющих откликов второго этапа, которые поступают на первый и второй входы второго сумматора 28, где путем их суммирования вычисляют квадраты модулей комплексных откликов второго этапа, получая решающую функцию второго этапа. Вычисленные квадраты модулей комплексных откликов второго этапа с выхода второго сумматора 28 поступают на первый вход второго блока сравнения с порогом 29.

Во втором блоке сравнения с порогом 29 сравнивают значения квадратов модулей комплексных откликов второго этапа с порогом второго этапа Н2. Результат сравнения с выхода второго блока сравнения с порогом 29 поступает на первый вход блока управления 22 и на третий вход блока расчета дополнительного частотного сдвига 30.

При непревышении порога Н2 полагают преамбулу необнаруженной и продолжают процедуру частотно-временной синхронизации.

При превышении порога Н2 полагают преамбулу обнаруженной. При этом по сигналам превышения порога в блоке управления 22 определяют оценку временного положения преамбулы, как временное положение первого превышения порога второго этапа Н2. Полученная оценка с четвертого выхода блока управления 22 поступает на первый выход устройства.

Окончательную оценку временного положения преамбулы определяют равной разности временного положения первого превышения порога второго этапа Н2 и суммы длительностей первой части преамбулы и префикса.

Со второго выхода блока управления 22 на второй вход второго блока сравнения с порогом 29 и на пятый вход блока расчета дополнительного частотного сдвига 30 поступает сигнал окончания приема второй части преамбулы, равный, например, логической единице.

В блоке расчета дополнительного частотного сдвига 30 по сигналу превышения порога и по управляющему сигналу окончания временной области превышения значениями решающей функции порога второго этапа, поступающим на его четвертый вход с третьего выхода блока управления 22 определяют временные положения, соответствующие локальным максимумам решающей функции второго этапа.

В блоке расчета дополнительного частотного сдвига 30 по сигналу окончания приема второй части преамбулы синфазные и квадратурные составляющие комплексных откликов второго этапа, соответствующие локальным максимумам решающей функции второго этапа, используют для определения дополнительного частотного сдвига.

Оценка выполняется, например, следующим образом. Формируют разность фаз двух комплексных откликов второго этапа, соответствующих локальным максимумам, как произведение комплексно сопряженного отклика на последующий комплексный отклик. В результате аргумент полученного комплексного числа соответствует оценке дополнительного фазового сдвига. Дополнительную оценку частотного сдвига определяют, например, как отношение оценки дополнительного фазового сдвига к длительности длинного многочастотного символа. Дополнительная оценка частотного сдвига с выхода блока 30 поступает на второй вход третьего сумматора 31. В третьем сумматоре 31 определяют окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как сумму предварительной и дополнительной оценок частотного сдвига. Полученная окончательная оценка с выхода третьего сумматора 31 поступает на второй выход устройства.

К недостаткам способа прототипа и устройства следует отнести отказ от предварительной оценки временного положения сигнала и, как следствие, от использования некогерентной обработки на первом этапе. Указанный недостаток обуславливает недостаточно высокую помехоустойчивость оценки временного положения и частотного рассогласования, особенно в условиях многолучевого распространения сигнала. Наличие префикса во второй части преамбулы может привести к возникновению аномальной ошибки при оценке временного положения на втором этапе.

Задача, которую решают предлагаемые изобретения, - это повышение помехоустойчивости частотно-временной синхронизации системы связи.

Эта задача решается тем, что в способе частотно-временной синхронизации системы связи, заключающемся в том, что

на передающей стороне:

формируют цифровой видеосигнал, состоящий из двух частей,

фильтруют сформированный цифровой видеосигнал, выполняют его цифроаналоговое преобразование, осуществляют перенос сигнала на несущую частоту, усиливают и передают его по каналу связи,

на приемной стороне:

входной сигнал фильтруют, усиливают, переносят на видеочастоту, осуществляют его аналого-цифровое преобразование и децимацию, формируя входной цифровой комплексный сигнал на видеочастоте,

частотно-временную синхронизацию выполняют в два этапа:

на первом этапе определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего

- осуществляют фильтрацию сформированного входного цифрового комплексного сигнала, формируя комплексные отклики первого этапа,

- вычисляют квадраты модулей комплексных откликов первого этапа,

- осуществляют сравнение с заданным порогом первого этапа,

- определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала,

на втором этапе осуществляют оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего

- корректируют фазу входного цифрового комплексного сигнала на интервале работы второго этапа с учетом предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала,

- осуществляют согласованную фильтрацию скорректированного входного цифрового комплексного сигнала, формируя комплексные отклики второго этапа,

- вычисляют квадраты модулей комплексных откликов второго этапа,

- осуществляют сравнение с заданным порогом второго этапа, при непревышении порога полагают преамбулу необнаруженной,

- при превышении порога второго этапа полагают преамбулу обнаруженной, тогда определяют окончательную оценку временного положения преамбулы по временному положению первого превышения порога второго этапа,

- определяют временное положение, соответствующее максимальному значению квадрата модуля комплексного отклика второго этапа,

- определяют дополнительную оценку частотного сдвига по разности фаз комплексных откликов второго этапа,

определяют окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как сумму предварительной и дополнительной оценки частотного сдвига,

согласно изобретению:

на передающей стороне:

цифровой видеосигнал, состоящий из двух частей, формируют таким образом, чтобы части цифрового видеосигнала были разделены паузой заданной длительности, при этом первая часть представляет собой N коротких кодовых последовательностей, а вторая часть - М длинных кодовых последовательностей,

на приемной стороне:

при выполнении первого этапа частотно-временной синхронизации определяют априорный интервал временного положения преамбулы для второго этапа,

для определения предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала на первом этапе:

- осуществляют фильтрацию входного сформированного цифрового комплексного сигнала, согласованную с одной короткой кодовой последовательностью,

- вычисляют суммы N квадратов модулей комплексных откликов первого этапа, взятых с интервалом, равным длительности короткой кодовой последовательности,

- с заданным порогом первого этапа сравнивают полученные суммы N квадратов модулей комплексных откликов первого этапа, при превышении порога:

- временное положение начала преамбулы, соответствующее полученной сумме, полагают текущим временным положением преамбулы,

- формируют текущую оценку частотного сдвига по усредненной разности фаз смежных комплексных откликов первого этапа с n-го по (N-n+1)-й, соответствующих слагаемым суммирования N квадратов модулей комплексных откликов первого этапа, где n - целое число,

- порог первого этапа устанавливают равным результату суммирования;

определяют начало априорного интервала временного положения второй части преамбулы по временному положению преамбулы, соответствующему первому превышению порога первого этапа,

определяют окончание априорного интервала временного положения второй части преамбулы по текущему временному положению преамбулы,

предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала определяют к моменту начала второго этапа как текущую оценку частотного сдвига,

к моменту начала априорного интервала временного положения второй части преамбулы порог первого этапа полагают равным первоначальному значению, а текущее временное положение преамбулы считают неопределенным,

на втором этапе:

осуществляют фильтрацию скорректированного входного сформированного цифрового комплексного сигнала, согласованную с одной длинной кодовой последовательностью,

квадраты модулей комплексных откликов второго этапа сравнивают с заданным порогом второго этапа на априорном интервале временного положения второй части преамбулы,

дополнительную оценку частотного сдвига определяют по усредненной разности фаз М комплексных откликов второго этапа: комплексного отклика второго этапа, соответствующего максимальному значению квадрата модуля, и откликов второго этапа, отстоящих от этого отклика на целое число длительности интервала длинной кодовой последовательности от 1 до (М-1).

Текущую оценку частотного сдвига формируют, например, как отношение усредненной разности фаз комплексных откликов первого этапа к длительности короткой кодовой последовательности.

Начало априорного интервала временного положения второй части преамбулы определяют, например, равным сумме временного положения преамбулы, соответствующего первому превышению порога первого этапа, длительности (N-2)-x коротких кодовых последовательностей и длительности паузы.

Окончание априорного интервала временного положения второй части преамбулы определяют, например, равным сумме текущего временного положения преамбулы, длительности (N+3)-x коротких кодовых последовательностей и длительности паузы.

Фазу входного цифрового комплексного сигнала на интервале работы второго этапа корректируют, умножая отсчеты входного цифрового комплексного сигнала на комплексный множитель единичной амплитуды, фаза которого равна произведению предварительной оценки частотного сдвига на временные положения отсчетов.

Дополнительную оценку частотного сдвига определяют, например, как отношение усредненной разности фаз комплексных откликов второго этапа к длительности длинной кодовой последовательности.

Окончательную оценку временного положения преамбулы, а именно начала преамбулы, определяют равной разности временного положения первого превышения порога второго этапа и суммы длительностей первой части преамбулы и паузы.

Поставленная задача решается также тем, что в устройстве частотно-временной синхронизации системы связи, содержащем

на передающей стороне: тактовый генератор, демультиплексор, первый счетчик, второй счетчик, первое постоянное запоминающее устройство, третий счетчик, четвертый счетчик, второе постоянное запоминающее устройство, сумматор, блок формирования данных, передающий тракт, при этом вход тактового генератора является входом устройства, выход тактового генератора соединен с первым входом демультиплексора, который является входом сигнала тактовых импульсов, второй вход демультиплексора, который является управляемый входом, соединен с выходом первого счетчика, первый выход демультиплексора соединен со входом второго счетчика, выход которого соединен со входами первого счетчика и первого постоянного запоминающего устройства, выход первого постоянного запоминающего устройства соединен с первым входом сумматора, второй выход демультиплексора соединен со входом третьего счетчика, выход которого соединен со входами второго постоянного запоминающего устройства и четвертого счетчика, выход которого соединен с третьим входом демультиплексора, который является управляемым входом, и входом блока формирования данных, выход которого соединен с третьим входом сумматора, второй вход которого соединен с выходом второго постоянного запоминающего устройства, выход сумматора соединен со входом передающего тракта, выход которого является выходом устройства,

на приемной стороне:

приемный тракт, формирующий на выходах входной цифровой комплексный сигнал на видеочастоте, первый и второй согласованные фильтры, осуществляющие фильтрацию соответственно синфазной и квадратурной компоненты сформированного входного цифрового комплексного сигнала и формирующие комплексные отклики первого этапа, первый и второй перемножители, первый сумматор, комплексный перемножитель, блок формирования гармоники, блок расчета частотного сдвига, первый блок сравнения с порогом, блок управления, тактовый генератор, формирующий на выходе сигнал тактовых импульсов, третий и четвертый согласованные фильтры, осуществляющие фильтрацию скорректированного входного цифрового комплексного сигнала и формирующие комплексные отклики второго этапа, третий и четвертый перемножители, второй сумматор, второй блок сравнения с порогом, блок расчета дополнительного частотного сдвига и третий сумматор, при этом вход приемного тракта является входом устройства, первый выход приемного тракта соединен со входом первого согласованного фильтра и первым входом комплексного перемножителя, второй выход приемного тракта соединен со входом второго согласованного фильтра и вторым входом комплексного перемножителя, выходы первого и второго перемножителей соединены соответственно с первым и вторым входами первого сумматора, выход которого соединен с первым входом первого блока сравнения с порогом, второй вход которого соединен с первым выходом блока управления, выход первого блока сравнения с порогом соединен с первым входом блока расчета частотного сдвига, выход которого соединен с первым входом блока формирования гармоники и первым входом третьего сумматора, второй вход блока формирования гармоники соединен с выходом тактового генератора, первый и второй выходы блока формирования гармоники соединены соответственно с третьим и четвертым входами комплексного перемножителя, первый и второй выходы которого соединены соответственно со входами третьего и четвертого согласованных фильтров, выход третьего согласованного фильтра соединен с первым и вторым входами третьего перемножителя и первым входом блока расчета дополнительного частотного сдвига, выход четвертого согласованного фильтра соединен с первым и вторым входами четвертого перемножителя и вторым входом блока расчета дополнительного частотного сдвига, выходы третьего и четвертого перемножителей соединены соответственно с первым и вторым входами второго сумматора, выход которого соединен с первым входом второго блока сравнения с порогом, второй вход которого соединен со вторым выходом блока управления, формирующего на этом выходе сигнал окончания второго этапа, выход второго блока сравнения с порогом соединен с третьим входом блока расчета дополнительного частотного сдвига и первым входом блока управления, третий выход которого соединен с четвертым входом блока расчета дополнительного частотного сдвига, четвертый выход блока управления является первым выходом устройства и выходом сигнала окончательной оценки временного положения преамбулы, первый выход блока расчета дополнительного частотного сдвига, формирующего на первом выходе дополнительную оценку частотного сдвига, соединен со вторым входом третьего сумматора, формирующего на выходе сигнал окончательной оценки частотного сдвига, выход третьего сумматора является вторым выходом устройства,

согласно изобретению

на передающей стороне:

первый счетчик выполнен таким образом, что позволяет осуществлять подсчет в сигнале преамбулы числа коротких кодовых последовательностей, формируя на выходе сигнал управления тактовыми импульсами при заданном числе N циклов считывания,

второй счетчик выполнен таким образом, что позволяет осуществлять подсчет в сигнале короткой кодовой последовательности преамбулы числа тактовых импульсов, формируя на выходе сигнал, соответствующий адресам текущих элементов короткой кодовой последовательности, третий счетчик выполнен таким образом, что позволяет осуществлять подсчет в сигнале длинной кодовой последовательности преамбулы числа тактовых импульсов, формируя на выходе сигнал, соответствующий адресам текущих элементов длинной кодовой последовательности, четвертый счетчик выполнен таким образом, что позволяет осуществлять подсчет в сигнале преамбулы числа длинных кодовых последовательностей, формируя на выходе сигнал управления тактовыми импульсами при заданном числе М циклов считывания и сигнал окончания преамбулы, первое постоянное запоминающее устройство выполнено таким образом, что позволяет хранить отсчеты короткой кодовой последовательности, второе постоянное запоминающее устройство выполнено таким образом, что позволяет хранить отсчеты длинной кодовой последовательности, введен счетчик паузы, осуществляющий подсчет на интервале паузы преамбулы числа тактовых импульсов, формируя на выходе сигнал окончания паузы, вход счетчика паузы соединен с третьим выходом демультиплексора, а выход - с четвертым входом демультиплексора, который является управляемым входом,

на приемной стороне введены:

первая и вторая линии задержки, N-1 первых и N-1 вторых перемножителей, блок определения границ априорного интервала, формирующий на первом выходе сигнал начала априорного интервала временного положения второй части преамбулы, а на втором выходе - сигнал окончания априорного интервала временного положения второй части преамбулы, при этом вход первой линии задержки соединен с выходом первого согласованного фильтра, вход второй линии задержки соединен с выходом второго согласованного фильтра, причем первый и второй согласованные фильтры согласованы с короткой кодовой последовательностью, N выходов первой линии задержки соединены с соответствующими им N вторыми входами блока расчета частотного сдвига и с первыми и вторыми входами соответствующих им N первых перемножителей, N выходов второй линии задержки соединены с соответствующими им N третьими входами блока расчета частотного сдвига и с первыми и вторыми входами соответствующих им N вторых перемножителей, выходы N-1 первых перемножителей соединены с N-1 дополнительными первыми входами первого сумматора, выходы N-1 вторых перемножителей соединены с N-1 дополнительными вторыми входами первого сумматора, выход тактового генератора соединен с пятым входом блока расчета дополнительного частотного сдвига и первым входом блока определения границ априорного интервала, второй вход которого соединен с выходом первого блока сравнения с порогом, первый выход блока определения границ априорного интервала соединен со вторым входом блока управления и третьим входом первого блока сравнения с порогом, второй выход блока определения границ априорного интервала соединен с третьим входом блока управления, формирующего на первом выходе сигнал управления, определяющий момент окончания или повторного запуска выполнения первого этапа, на третьем выходе - сигнал превышения порога второго этапа, на пятом выходе - сигнал окончания априорного интервала второй части преамбулы, пятый выход блока управления соединен с шестым входом блока расчета дополнительного частотного сдвига, на шестом выходе - сигнал идентификации априорного интервала второй части преамбулы, шестой выход блока управления соединен с третьим входом второго блока сравнения с порогом, четвертый вход блока управления соединен со вторым выходом блока расчета дополнительного частотного сдвига.

Заявляемые способ частотно-временной синхронизации системы связи и устройство для его осуществления имеют существенные отличия от наиболее близких аналогов, обнаруженных при поиске из известного уровня техники.

Эти отличия заключаются в следующем: оценку временного положения сигнала преамбулы осуществляют в два этапа, причем на первом этапе формируют решающую функцию с широким полезным откликом, что увеличивает вероятность захвата (успешной грубой оценки временного положения), на втором этапе формируют решающую функцию с узким полезным откликом, что позволяет получить точную оценку временного положения сигнала преамбулы. Оценку частотного сдвига формируют также в два этапа, причем качество этой оценки - высокое, поскольку базируется на качественной оценке временного положения.

Фактически в предлагаемом изобретении осуществлена двухэтапная совместная оценка временного положения и частотного сдвига сигнала преамбулы, причем в силу выбранного вида сигнала преамбулы достигнута высокая точность оцениваемых параметров.

Перечисленные признаки заявляемого способа и устройства для его осуществления как на передающей стороне, так и на приемной стороне имеют отличия от наиболее близких аналогов, выявленных при поиске из известного уровня техники, следовательно, заявляемые решения удовлетворяют условию патентоспособности изобретения “новизна”.

Анализ уровня техники на соответствие заявленных решений условию патентоспособности изобретения “изобретательский уровень” показал, что известные технические решения не позволяют обеспечить требуемый уровень помехоустойчивости для систем связи. А заявляемые способ и устройство за счет повышения качества частотно-временной синхронизации повышают помехоустойчивость системы связи, поэтому можно сделать вывод, что заявляемые технические решения отвечают условию патентоспособности “изобретательский уровень”.

Все признаки заявляемого устройства частотно-временной синхронизации системы связи позволяют полностью реализовать признаки заявляемого способа, т.к. заявляемые изобретения взаимосвязаны настолько, что образуют единый изобретательский замысел.

Изобретения поясняются примерами выполнения и чертежами:

на фиг.1 выполнена структурная схема устройства-прототипа на передающей стороне,

на фиг.2 - структурная схема устройства-прототипа на приемной стороне;

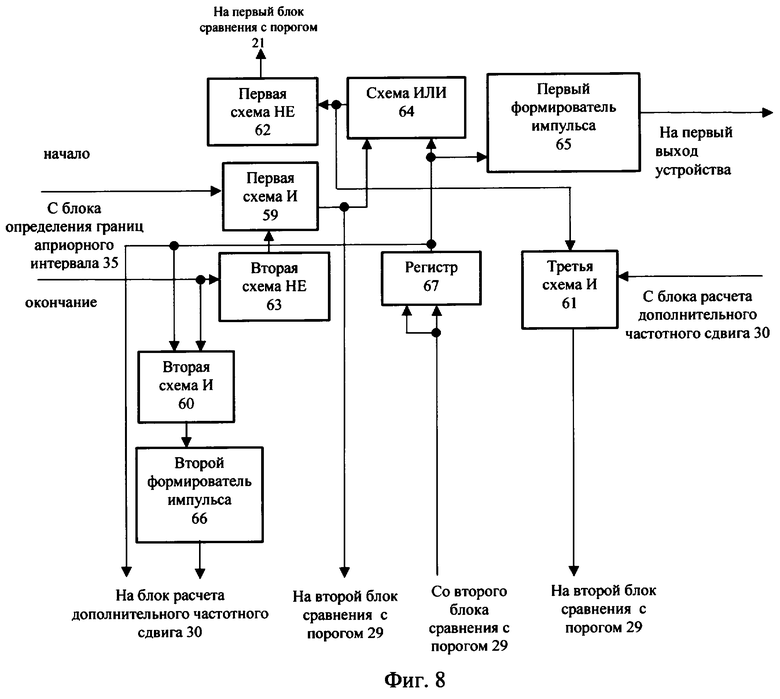

на фиг.3 - структурная схема заявляемого устройства на передающей стороне;

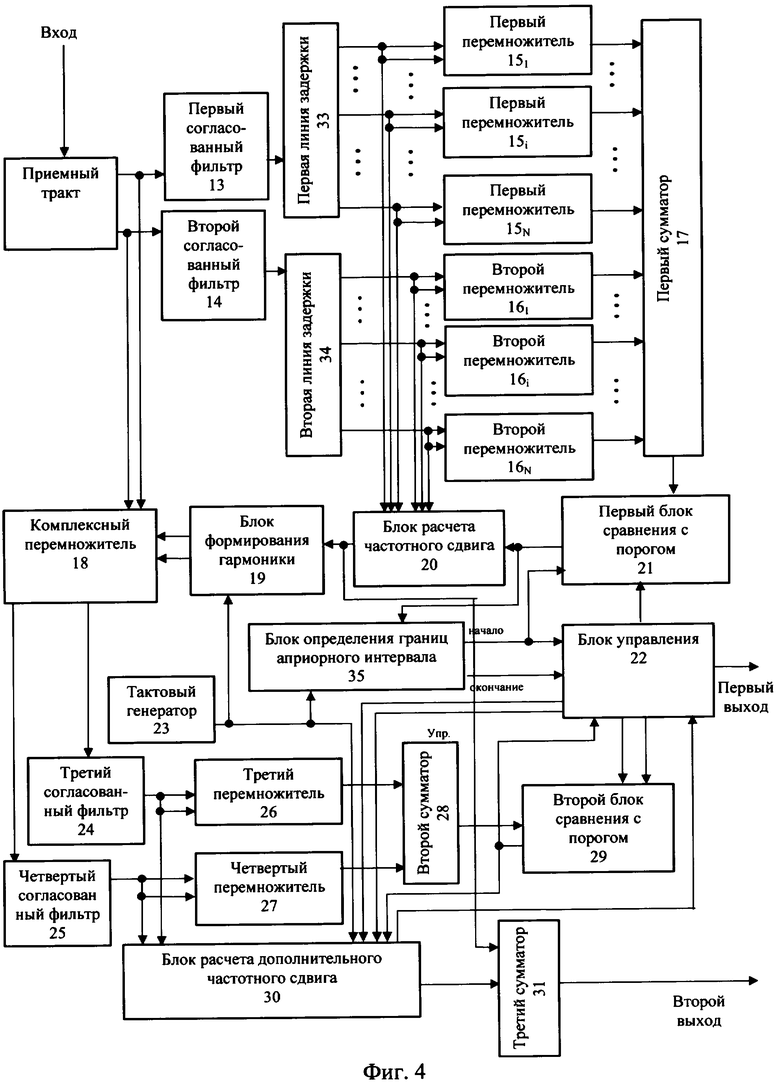

на фиг.4 - структурная схема заявляемого устройства на приемной стороне;

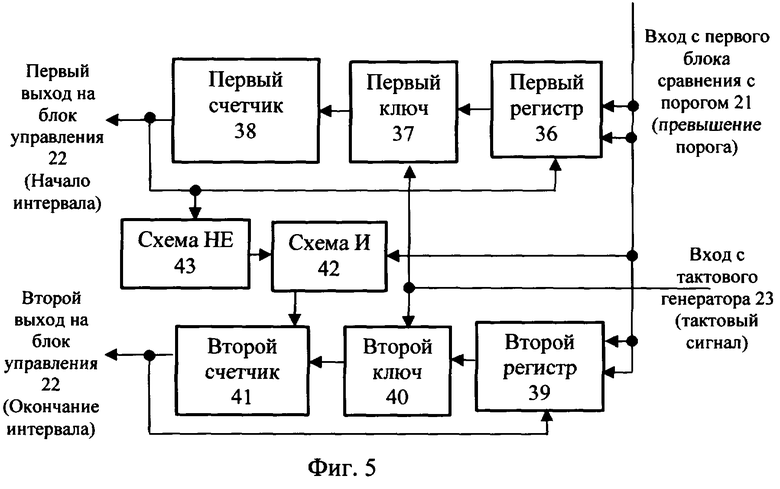

на фиг.5 - структурная схема блока определения границ априорного интервала 35, приведена как пример выполнения;

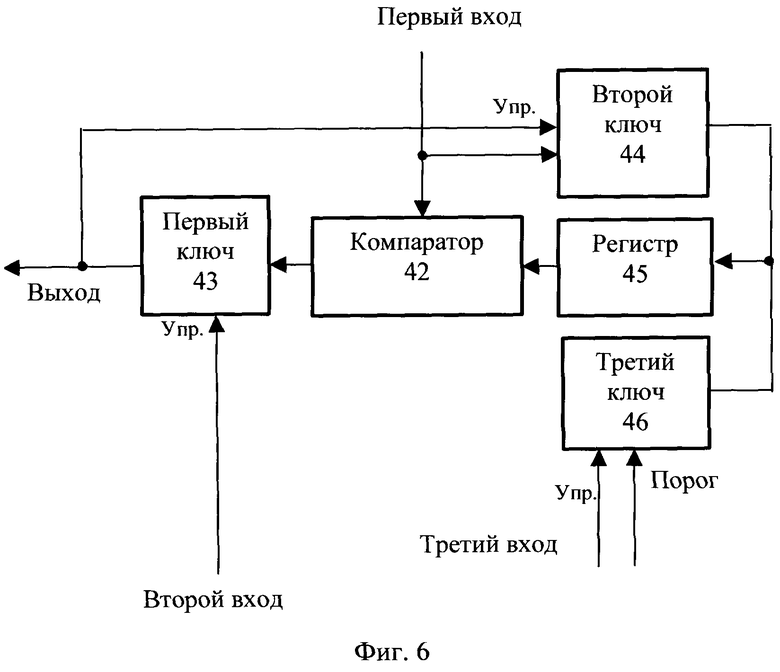

на фиг.6 - структурная схема блока сравнения с порогом 21 и 29, приведена как пример выполнения;

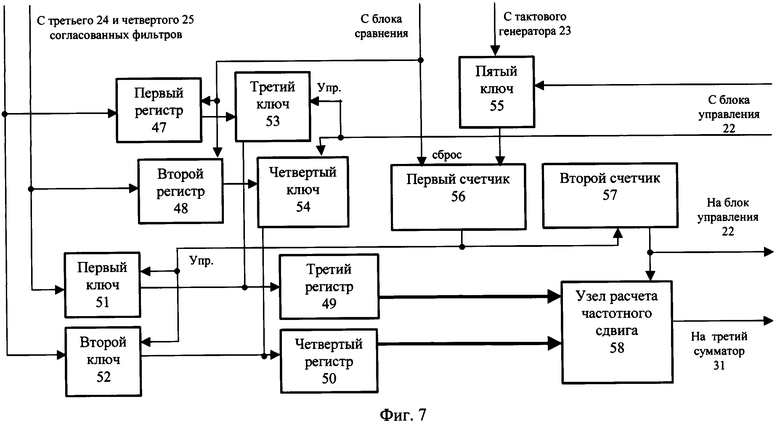

на фиг.7 - структурная схема блока расчета дополнительного частотного сдвига 30, приведена как пример выполнения;

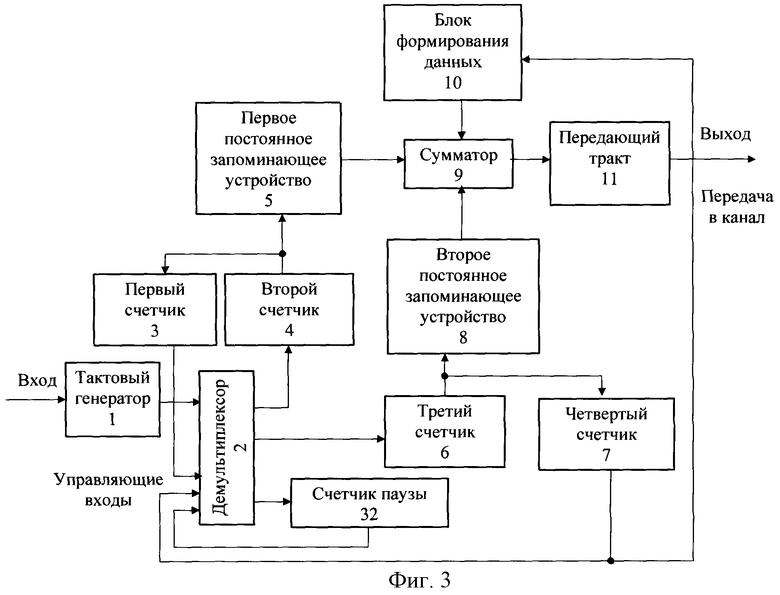

на фиг.8 - блок управления 22, показан как пример выполнения.

Заявляемое устройство частотно-временной синхронизации системы связи содержит на передающей стороне (фиг.3) тактовый генератор 1, демультиплексор 2, первый счетчик 3, второй счетчик 4, первое постоянное запоминающее устройство 5, третий счетчик 6, четвертый счетчик 7, второе постоянное запоминающее устройство 8, сумматор 9, блок формирования данных 10, передающий тракт 11, при этом вход тактового генератора 1 является входом устройства, выход тактового генератора 1 соединен с первым входом демультиплексора 2, второй вход которого соединен с выходом первого счетчика 3, первый выход демультиплексора 2 соединен со входом второго счетчика 4, выход которого соединен со входами первого счетчика 3 и первого постоянного запоминающего устройства 5, выход первого постоянного запоминающего устройства 5 соединен с первым входом сумматора 9, второй выход демультиплексора 2 соединен со входом третьего счетчика 6, выход которого соединен со входами второго постоянного запоминающего устройства 8 и четвертого счетчика 7, выход которого соединен с третьим входом демультиплексора 2 и входом блока формирования данных 10, выход которого соединен с третьим входом сумматора 9, второй вход которого соединен с выходом второго постоянного запоминающего устройства 8, выход сумматора 9 соединен со входом передающего тракта 11, выход которого является выходом устройства, согласно изобретению дополнительно содержит счетчик паузы 32, осуществляющий накопление тактовых импульсов заданной длительности, формирующий на выходе сигнал управления окончанием формирования паузы, вход счетчика паузы соединен с третьим выходом демультиплексора, а выход - с четвертым входом демультиплексора; на приемной стороне: приемный тракт 12, формирующий на выходах входной цифровой комплексный сигнал на видеочастоте, первый 13 и второй 14 согласованные фильтры, осуществляющие фильтрацию соответственно синфазной и квадратурной компоненты сформированного входного цифрового комплексного сигнала и формирующие комплексные отклики первого этапа, первый 151 и второй 161 перемножители, первый сумматор 17, комплексный перемножитель 18, блок формирования гармоники 19, блок расчета частотного сдвига 20, первый блок сравнения с порогом 21, блок управления 22, тактовый генератор 23, формирующий на выходе сигнал тактовых импульсов, третий 24 и четвертый 25 согласованные фильтры, осуществляющие фильтрацию скорректированного входного цифрового комплексного сигнала и формирующие комплексные отклики второго этапа, третий 26 и четвертый 27 перемножители, второй сумматор 28, второй блок сравнения с порогом 29, блок расчета дополнительного частотного сдвига 30 и третий сумматор 31, при этом вход приемного тракта 12 является входом устройства, первый выход приемного тракта 12 соединен со входом первого согласованного фильтра 13 и первым входом комплексного перемножителя 18, второй выход приемного тракта 12 соединен со входом второго согласованного фильтра 14 и вторым входом комплексного перемножителя 18, выходы первого 151 и второго 161 перемножителей соединены соответственно с первым и вторым входами первого сумматора 17, выход которого соединен с первым входом первого блока сравнения с порогом 21, второй вход которого соединен с первым выходом блока управления 22, выход первого блока сравнения с порогом 21 соединен с первым входом блока расчета частотного сдвига 20, выход которого соединен с первым входом блока формирования гармоники 19 и первым входом третьего сумматора 31, второй вход блока формирования гармоники 19 соединен с выходом тактового генератора 23, первый и второй выходы блока формирования гармоники 19 соединены соответственно с третьим и четвертым входами комплексного перемножителя 18, первый и второй выходы которого соединены соответственно со входами третьего 24 и четвертого 25 согласованных фильтров, выход третьего согласованного фильтра 24 соединен с первым и вторым входами третьего перемножителя 26 и первым входом блока расчета дополнительного частотного сдвига 30, выход четвертого согласованного фильтра 25 соединен с первым и вторым входами четвертого перемножителя 27 и вторым входом блока расчета дополнительного частотного сдвига 30, выходы третьего 26 и четвертого 27 перемножителей соединены соответственно с первым и вторым входами второго сумматора 28, выход которого соединен с первым входом второго блока сравнения с порогом 29, второй вход которого соединен со вторым выходом блока управления 22, формирующего на этом выходе сигнал окончания второго этапа, выход второго блока сравнения с порогом 29 соединен с третьим входом блока расчета дополнительного частотного сдвига 30 и первым входом блока управления 22, третий выход которого соединен с четвертым входом блока расчета дополнительного частотного сдвига 30, четвертый выход блока управления 22 является первым выходом устройства и выходом сигнала окончательной оценки временного положения преамбулы, первый выход блока расчета дополнительного частотного сдвига 30, формирующего на первом выходе дополнительную оценку частотного сдвига, соединен со вторым входом третьего сумматора 31, формирующего на выходе сигнал окончательной оценки частотного сдвига, выход третьего сумматора является вторым выходом устройства, согласно изобретению на приемной стороне введены: первая 33 и вторая 34 линии задержки, N-1 первых 15N-1 и N-1 вторых 16N-1 перемножителей, блок определения границ априорного интервала 35, формирующий на первом выходе сигнал начала априорного интервала временного положения второй части преамбулы, а на втором выходе - сигнал окончания априорного интервала временного положения второй части преамбулы, при этом вход первой линии задержки 33 соединен с выходом первого согласованного фильтра 13, вход второй линии задержки 34 соединен с выходом второго согласованного фильтра 14, при этом первый 13 и второй 14 согласованные фильтры согласованы с короткой кодовой последовательностью, N выходов первой линии задержки 15 соединены с соответствующими им N вторыми входами блока расчета частотного сдвига 20 и с первыми и вторыми входами N первых перемножителей 15, N выходов второй линии задержки 34 соединены с N третьими входами блока расчета частотного сдвига 20 и с первыми и вторыми входами N вторых перемножителей 16, выходы N-1 первых перемножителей 15 соединены с N-1 дополнительными первыми входами первого сумматора 17, выходы N-1 вторых перемножителей соединены с (N-1) дополнительными вторыми входами первого сумматора 17, выход тактового генератора 23 соединен с пятым входом блока расчета дополнительного частотного сдвига 30 и первым входом блока определения границ априорного интервала 35, второй вход которого соединен с выходом первого блока сравнения с порогом 21, первый выход блока определения границ априорного интервала 35 соединен со вторым входом блока управления 22 и третьим входом первого блока сравнения с порогом 21, второй выход блока определения границ априорного интервала 35 соединен с третьим входом блока управления 22, формирующего на первом выходе сигнал управления, определяющий момент окончания или повторного запуска выполнения первого этапа, на третьем выходе - сигнал превышения порога второго этапа, на пятом выходе - сигнал окончания априорного интервала второй части преамбулы, пятый выход блока управления 22 соединен с шестым входом блока расчета дополнительного частотного сдвига 30, на шестом выходе - сигнал идентификации априорного интервала второй части преамбулы, шестой выход блока управления 22 соединен с третьим входом второго блока сравнения с порогом 29, четвертый вход блока управления 22 соединен со вторым выходом блока расчета дополнительного частотного сдвига 30.

Блок определения границ априорного интервала 35 (фиг.5) содержит последовательно соединенные первый регистр 36, первый ключ 37 и первый счетчик 38, образующих первое плечо, последовательно соединенные второй регистр 39, второй ключ 40 и второй счетчик 41, образующих второе плечо, схему И 42 и схему НЕ 43, при этом первый и второй входы первого 36 и второго 39 регистров и первый вход схемы И объединены, образуя второй вход блока определения границ априорного интервала 35, вторые входы первого 37 и второго 40 ключей объединены, образуя первый вход блока 35, выход первого счетчика 38 является первым выходом блока 35 и соединен со входом схемы НЕ 43 и третьим входом первого регистра 36, выход второго счетчика 41 является вторым выходом блока 35 и соединен с третьим входом второго регистра 39, второй вход второго счетчика 41 соединен с выходом схемы И, вход которой соединен с выходом схемы НЕ 43.

Первый 21 и второй 29 блоки сравнения с порогом выполнены эквивалентно, пример их выполнения показан на фиг.6. Блок сравнения с порогом содержит компаратор 42, первый ключ 43, второй ключ 44, регистр 45 и третий ключ 46, при этом первые входы компаратора 42 и второго ключа 44 объединены, образуя первый вход блока сравнения с порогом, который является сигнальным входом, второй вход компаратора 42 соединен с выходом регистра 45, выход компаратора 42 соединен с первым входом первого ключа 43, второй вход первого ключа 43 является управляемым вторым входом блока сравнения с порогом, выход первого ключа 43 является выходом блока сравнения с порогом и соединен со вторым входом второго ключа 44, выход которого соединен со входом регистра 45 и первым входом третьего ключа 46, второй вход которого является третьим входом блока сравнения с порогом и является управляемым входом, третий вход третьего ключа 46 является входом сигнала первоначального значения порога (соответственно первого или второго этапа) и формируется внутри блока.

Блок расчета дополнительного частотного сдвига 30 показан как пример выполнения (фиг.7) и содержит: первый 47, второй 48, третий 49 и четвертый 50 регистры, первый 51, второй 52, третий 53, четвертый 54 и пятый 55 ключи, первый 56 и второй 57 счетчики и узел расчета частотного сдвига 58, при этом первые входы первого регистра 47 и второго ключа 52 объединены, образуя первый вход блока 30, первые входы второго регистра 48 и первого ключа 51 объединены, образуя второй вход блока 30, вторые входы первого регистра 47, второго регистра 48 и первый вход первого счетчика 56 объединены, образуя третий вход блока 30, выходы первого 47 и второго 48 регистров соединены соответственно с первыми входами третьего 53 и четвертого 54 ключей, вторые входы которых объединены, образуя четвертый вход блока 30, первый и второй входы пятого ключа 55 являются соответственно пятыми и шестыми входами блока 30, выход пятого ключа 55 соединен со вторым входом первого счетчика 56, выход первого счетчика 56 соединен со входом второго счетчика 57 и вторыми входами первого 51 и второго 52 ключей, выходы первого 51 и третьего 53 ключей соединены со входом третьего регистра 49, выходы второго 52 и четвертого 54 ключей соединены со входом четвертого регистра 50, выходы третьего 49 и четвертого 50 регистров соединены соответственно с первым и вторым входами узла расчета частотного сдвига 58, выход которого является первым выходом блока 30, третий вход узла расчета частотного сдвига 58 соединен с выходом второго счетчика 57, выход которого является вторым выходом блока 30.

Блок управления 22 (фиг.8) приведен как пример выполнения и содержит: первую 59, вторую 60 и третью 61 схемы И, первую 62 и вторую 63 схемы НЕ, схему ИЛИ 64, первый 65 и второй 66 формирователи импульсов и регистр 67, при этом первый вход первой схемы И 59 является вторым входом блока управления 22, первый вход второй схемы И и вход второй схемы НЕ объединены, образуя третий вход блока 22, выход второй схемы НЕ соединен со вторым входом первой схемы И, выход которой является шестым выходом блока управления 22 и соединен с первым входом схемы ИЛИ 64, второй вход которой объединен со входом первого формирователя импульса 65 и вторым входом второй схемы И 60 и соединен с выходом регистра 67, выход которого является третьим выходом блока управления 22, первый и второй входы регистра 67 объединены, образуя первый вход блока управления 22, выход схемы ИЛИ 64 соединен со входом первой схемы НЕ 62 и первым входом третьей схемы И 61, выход первой схемы НЕ является первым выходом блока управления 22, выход первого формирователя импульса 65 является четвертым выходом блока управления 22, второй вход третьей схемы И 61 является четвертым входом блока 22, а выход ее - вторым выходом блока 22, выход второй схемы И 60 соединен со входом второго формирователя импульса 66, выход которого является пятым выходом блока управления 22.

Осуществляют заявляемый способ частотно-временной синхронизации системы связи следующим образом:

на передающей стороне:

- формируют цифровой видеосигнал, состоящий из двух частей, разделенных паузой заданной длительности,

первая часть представляет собой N коротких кодовых

последовательностей,

вторая часть представляет собой М длинных кодовых

последовательностей;

- фильтруют сформированный цифровой видеосигнал, выполняют его цифроаналоговое преобразование, осуществляют перенос сигнала на несущую частоту, усиливают и передают его по каналу связи;

на приемной стороне входной сигнал фильтруют, усиливают, переносят на видеочастоту, осуществляют его аналого-цифровое преобразование и децимацию, формируя входной цифровой комплексный сигнал на видеочастоте;

- частотно-временную синхронизацию выполняют в два этапа, при этом на первом этапе определяют априорный интервал временного положения преамбулы для второго этапа и предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего

осуществляют согласованную с одной короткой кодовой последовательностью фильтрацию сформированного входного цифрового комплексного сигнала, формируя комплексные отклики первого этапа,

вычисляют квадраты модулей комплексных откликов первого этапа,

вычисляют суммы N квадратов модулей комплексных откликов первого этапа, взятых с интервалом, равным длительности короткой кодовой последовательности,

сравнивают полученные суммы с заданным порогом первого этапа, при превышении порога:

временное положение начала преамбулы, соответствующее полученной сумме, полагают текущим временным положением преамбулы,

формируют текущую оценку частотного сдвига по усредненной разности фаз смежных комплексных откликов первого этапа с n-го по (N-n+1)-й, соответствующих слагаемым суммирования, где n - целое число,

порог первого этапа устанавливают равным полученной сумме;

определяют начало априорного интервала временного положения второй части преамбулы по временному положению преамбулы, соответствующему первому превышению порога первого этапа;

определяют окончание априорного интервала временного положения второй части преамбулы по текущему временному положению преамбулы;

к моменту начала второго этапа определяют предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как текущую оценку частотного сдвига;

к моменту начала априорного интервала временного положения второй части преамбулы порог первого этапа полагают равным первоначальному значению, а текущее временное положение преамбулы считают неопределенным;

- на втором этапе осуществляют оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала, для чего

корректируют фазу входного цифрового комплексного сигнала на интервале работы второго этапа с учетом предварительной оценки частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала,

осуществляют согласованную с одной длинной кодовой последовательностью фильтрацию скорректированного входного цифрового комплексного сигнала, формируя комплексные отклики второго этапа,

вычисляют квадраты модулей комплексных откликов второго этапа,

сравнивают квадраты модулей комплексных откликов второго этапа с заданным порогом второго этапа на априорном интервале временного положения второй части преамбулы, при непревышении порога полагают преамбулу необнаруженной,

при превышении порога второго этапа полагают преамбулу обнаруженной, тогда

определяют окончательную оценку временного положения преамбулы по временному положению первого превышения порога второго этапа,

на априорном интервале временного положения второй части преамбулы определяют временное положение, соответствующее максимальному значению квадрата модуля комплексного отклика второго этапа длинной кодовой последовательности,

определяют дополнительную оценку частотного сдвига по усредненной разности фаз М комплексных откликов второго этапа:

комплексного отклика второго этапа, соответствующего максимальному значению квадрата модуля, и откликов второго этапа, отстоящих от этого отклика на целое число длительности интервала длинной кодовой последовательности от 1 до (М-1),

определяют окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала как сумму предварительной и дополнительной оценки частотного сдвига.

Текущую оценку частотного сдвига формируют, например, как отношение усредненной разности фаз комплексных откликов первого этапа к длительности короткой кодовой последовательности.

Начало априорного интервала временного положения второй части преамбулы определяют, например, равным сумме временного положения преамбулы, соответствующего первому превышению порога первого этапа, длительности (N-2)-x коротких кодовых последовательностей и длительности паузы.

Окончание априорного интервала временного положения второй части преамбулы определяют, например, равным сумме текущего временного положения преамбулы, длительности (N+3)-x коротких кодовых последовательностей и длительности паузы.

Фазу входного цифрового комплексного сигнала на интервале работы второго этапа корректируют, умножая отсчеты входного цифрового комплексного сигнала на комплексный множитель единичной амплитуды, фаза которого равна произведению предварительной оценки частотного сдвига на временные положения отсчетов.

Дополнительную оценку частотного сдвига определяют, например, как отношение усредненной разности фаз комплексных откликов второго этапа к длительности длинной кодовой последовательности.

Окончательную оценку временного положения преамбулы, а именно начала преамбулы, определяют равной разности временного положения первого превышения порога второго этапа и суммы длительностей первой части преамбулы и паузы.

Заявляемый способ реализуют на устройстве частотно-временной синхронизации системы связи, структурная схема которого выполнена на фиг.3 и 4.

Рассмотрим реализацию заявляемого способа на передающей стороне, используя для этого фиг.3.

Тактовый генератор 1, демультиплексор 2, первый счетчик 3, второй счетчик 4, третий счетчик 6, четвертый счетчик 7, счетчик паузы 32 и сумматор 9 используют для формирования цифрового видеосигнала преамбулы, а блок формирования данных 10 используют для формирования информационного сигнала системы связи. Временная структура сигнала преамбулы заранее определена.

В заявляемом устройстве на передающей стороне в качестве первого 3, второго 4, третьего 6, четвертого 7 счетчиков и счетчика паузы 32 используют стандартные программируемые счетчики, например серии 564 ИЕ10 и др. В качестве первого 5 и второго 8 постоянных запоминающих устройств используют известные постоянные запоминающие устройства с необходимым объемом памяти.

Сформированный сигнал преамбулы и информационный сигнал поступают через передающий тракт 11 в канал связи.

При формировании сигнала преамбулы и информационного сигнала осуществляют их временное разделение. Информационный сигнал поступает в передающий тракт после сигнала окончания процедуры формирования сигнала преамбулы.

Процедуру формирования сигнала преамбулы выполняют следующим образом.

Тактовый генератор 1 по команде управления начала или повтора передачи сигнала преамбулы, поступающей на его вход, формирует тактовые импульсы, параметры которых определяются длительностью чипа кодовых последовательностей (ПСП). С выхода тактового генератора 1 тактовые импульсы поступают на первый вход демультиплексора 2, на второй и четвертый управляемые входы которого соответственно с выхода первого счетчика 3 и с выхода счетчика паузы 32 поступают сигналы управления (коммутации).

На третий управляемый вход демультиплексора 2 и на управляемый вход блока формирования данных 10 с выхода четвертого счетчика 7 поступает сигнал коммутации - окончания преамбулы.

Исходное состояние сигналов управления (коммутации) устанавливают таким образом, что первоначально тактовые импульсы только с первого выхода демультиплексора 2 поступают на вход второго счетчика 4. Второй счетчик 4 программируют таким образом, чтобы он на выходе сформировал сигнал, соответствующий адресам текущих элементов короткой кодовой последовательности, а сигнал на старшем разряде, равный, например, логической единице, индицирует окончание считывания очередной короткой кодовой последовательности.

По сигналу адресов текущих элементов короткой кодовой последовательности, поступающему с выхода второго счетчика 4 на вход первого постоянного запоминающего устройства 5, в блоке 5 осуществляют циклическое считывание текущих элементов короткой кодовой последовательности, которые поступают с выхода первого постоянного запоминающего устройства 5 на первый вход сумматора 9 и далее с его выхода поступают на вход передающего тракта 11. По сигналу окончания считывания очередной короткой кодовой последовательности, который поступает на вход первого счетчика 3, осуществляют подсчет (накопление) числа циклов считывания и формируют на выходе первого счетчика 3 сигнал управления, равный, например, логической единице, если число циклов равно заданному числу N коротких кодовых последовательностей в сигнале преамбулы.

При этом в течение временного интервала формирования заданного числа коротких кодовых последовательностей с выхода второго постоянного запоминающего устройства 8 на второй вход сумматора 9 и с выхода блока формирования данных 10 на третий вход сумматора 9 считывают сигналы, равные нулю.

По сформированному сигналу управления с выхода первого счетчика 3 осуществляют коммутацию демультиплексора 2, и тактовые импульсы с его третьего выхода поступают на вход счетчика паузы 32. В счетчике паузы 32 осуществляют подсчет (накопление) тактовых импульсов и программируют его таким образом, чтобы появление в его старшем разряде сигнала, равного, например, логической единице, соответствовало окончанию формирования паузы заданной длительности.

При этом в течение интервала паузы с выхода первого постоянного запоминающего устройства 5 на первый вход сумматора 9, с выхода второго постоянного запоминающего устройства 8 на второй вход сумматора 9 и с блока формирования данных 10 на третий вход сумматора 9 и на вход передающего тракта 11 считывают сигналы, равные нулю.

По сигналу окончания формирования паузы заданной длительности, который поступает с выхода счетчика паузы 32 на четвертый вход демультиплексора 2, осуществляют его коммутацию, и тактовые импульсы поступают только со второго выхода демультиплексора 2 на вход третьего счетчика 6.

Третий счетчик 6 программируют таким образом, что на его выходах формируют сигнал, соответствующий адресам текущих элементов длинной кодовой последовательности, а сигнал на старшем разряде, равный, например, логической единице, индицирует окончание считывания очередной длинной кодовой последовательности.

По сигналам адресов, поступающим с выхода третьего счетчика 6 на вход второго постоянного запоминающего устройства 8, осуществляют циклическое считывание текущих элементов длинной кодовой последовательности, которые поступают на второй вход сумматора 9. По сигналу окончания считывания очередной длинной кодовой последовательности, который поступает на вход четвертого счетчика 7, осуществляют подсчет (накопление) числа циклов считывания и формируют на выходе этого счетчика сигнал управления, равный, например, логической единице, если число циклов равно заданному числу М длинных кодовых последовательностей в сигнале преамбулы.

При этом в течение временного интервала формирования заданного числа длинных кодовых последовательностей с выхода первого постоянного запоминающего устройства 5 на первый вход сумматора 9 и с блока формирования данных 10 на третий вход сумматора 9 считывают сигналы, равные нулю.

По сигналу окончания формирования заданного числа длинных кодовых последовательностей, который поступает с выхода четвертого счетчика 7 числа длинных кодовых последовательностей на третий вход демультиплексора 2 и на управляемый вход блока формирования данных 10, осуществляют коммутацию таким образом, что с выхода первого постоянного запоминающего устройства 5 на первый вход сумматора 9 и с выхода второго постоянного запоминающего устройства 8 на второй вход сумматора 9 считывают сигналы, равные нулю, а с выхода блока формирования данных 10 на третий вход сумматора 9 считывают информационный сигнал.

С выхода сумматора 9 сформированный цифровой видеосигнал поступает в передающий тракт 11. В передающем тракте 11 сигнал преамбулы и информационный сигнал преобразуют, выполняя стандартную последовательность операций (фильтрацию, цифроаналоговое преобразование, модуляцию, перенос на несущую частоту, усиление и т.д.), и осуществляют передачу полученного сигнала (сообщения) в канал связи.

Сигнал преамбулы используют для частотно-временной синхронизации, которая состоит из двух этапов. При этом на первом этапе определяют априорный интервал временного положения второй части преамбулы и предварительную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала. На втором этапе осуществляют оценку временного положения преамбулы и окончательную оценку частотного сдвига между несущей частотой входного сигнала и частотой опорного сигнала.

Рассмотрим реализацию заявляемого способа на приемной стороне, используя для этого фиг.4, на которой показана структурная схема заявляемого устройства на приемной стороне.

На приемной стороне в приемном тракте 12 входной сигнал, который поступает на его вход, предварительно фильтруют, усиливают, переносят на видеочастоту, осуществляют его аналого-цифровое преобразование, децимацию и т.д. В результате чего формируют входной цифровой комплексный сигнал на видеочастоте.

Синфазная и квадратурная составляющие входного цифрового сигнала с первого и второго выходов приемного тракта 12 поступают соответственно на входы первого 13 и второго 14 согласованных фильтров и на первый и второй входы комплексного перемножителя 18.

В первом согласованном фильтре 13 осуществляют согласованную с одной короткой кодовой последовательностью фильтрацию синфазной компоненты входного сигнала. Во втором согласованном фильтре 14 осуществляют согласованную с одной короткой кодовой последовательностью фильтрацию квадратурной компоненты входного сигнала.

На выходах первого 13 и второго 14 согласованных фильтров формируют корреляционные отклики соответственно для синфазной и квадратурной составляющих входного цифрового комплексного сигнала, которые поступают на входы первой 33 и второй 34 линий задержки соответственно для синфазной и квадратурной составляющих сигнала.

В первой 33 и второй 34 линиях задержки запоминают (записывают) отклики соответственно для синфазной и квадратурной составляющих с дискретом, например, в один чип на интервале длительности N коротких кодовых последовательностей. Каждая линия задержки соответственно для синфазной и квадратурной составляющих имеет N выходов.