Изобретение относится к области регистрации цифровой информации и может использоваться для увеличения объема регистрации цифровой информации на любой носитель.

Прототипом принято устройство сжатия и восстановления цифровых данных [1], содержащее кодер и декодер. Кодер включает последовательно соединенные регистр, схему сравнения, счетчик импульсов, дешифратор и блок ключей, блок элементов задержек и блок регистрации, декодер включает последовательно соединенные первый регистр, первый блок ключей и второй регистр, второй блок ключей, вычитающий счетчик импульсов и дешифратор и первый и второй ключи. На вход кодера поступают 8-разрядные коды видеосигналов с АЦП в параллельном виде с частотой дискретизации 27 МГц, выполняется сравнение по величине каждого предыдущего и последующего кодов, выявляется их равенство или неравенство, счетчик подсчитывает число кодов, равных по величине и идущих последовательно друг за другом: максимальное число кодов, равных по величине, подряд подсчитывается до 255 /11111111/. Коды, равные по величине, кроме первого, исключаются из потока кодов, за их счет и идет сжатие потока данных. Коэффициент сжатия от 1 до 255. Сжатая информация записывается с кодера на твердотельный носитель. Восстановление сжатой информации на 100% выполняется декодером. Недостатком прототипа является недостаточная степень сжатия, до 255.

Цель изобретения - повышение степени сжатия цифровых данных.

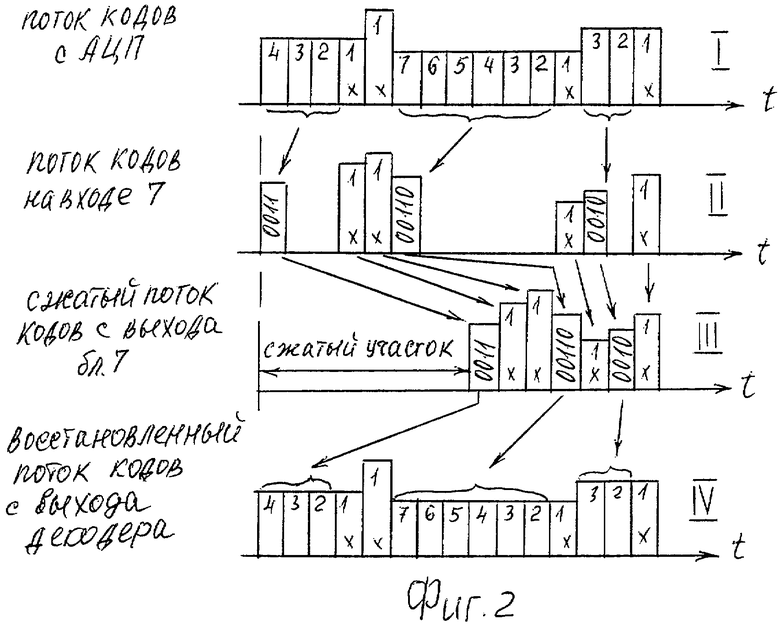

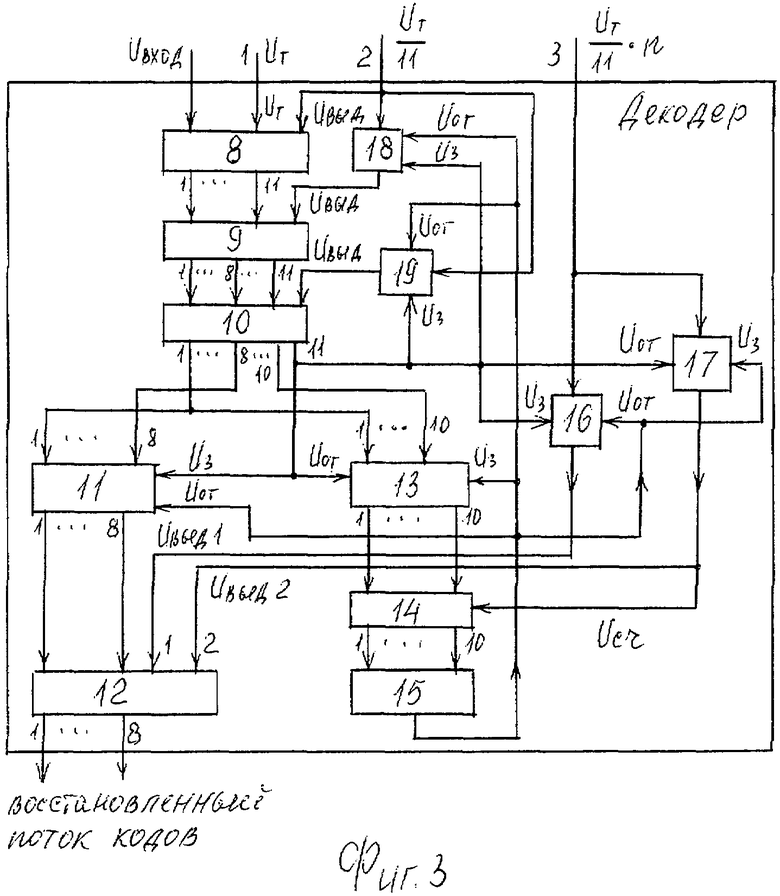

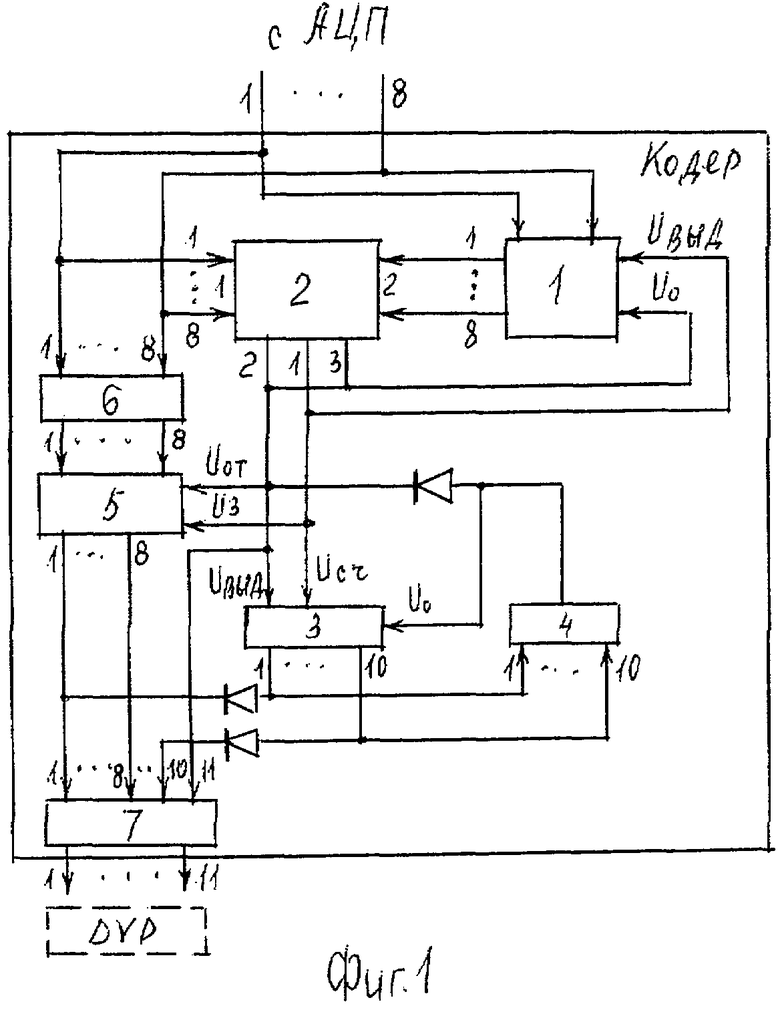

Техническим результатом является увеличение степени сжатия в 4 раза: с 255 по 1023. В заявляемом устройстве используется способ [1], заключающийся в последовательном сравнении каждого предыдущего и последующего кодов по величине, подсчете числа кодов, равных по величине и следующих друг за другом, получении двоичного кода этого числа с введением его в поток вслед за первым кодом своей последовательности и исключением из нее подсчитанных кодов, при воспроизведении - выявление в сжатом потоке кодов кода числа равных кодов и выдача первого кода по числу изъятых кодов при сжатии. Сущность изобретения в том, что в кодере, содержащем регистр, схему сравнения, счетчик импульсов, дешифратор и блок ключей, блок элементов задержек и блок регистрации, счетчик импульсов и дешифратор выполнены 10-разрядными, блок регистрации выполнен 11-разрядным, а в декодер вводятся накопитель кодов соответствующей емкости, третий 11-разрядный регистр, третий и четвертый ключи, а первый регистр выполняется 11-разрядным, вычитающий счетчик и дешифратор выполняются 10-разрядными. В кодере в темпе следования потока кодов в параллельном виде производится подсчет числа идущих друг за другом кодов, равных по величине, формируется 10-разрядный код этого числа, в 11-й разряд которого вводится признак кода числа равных кодов, и этот 11-разрядный код вводится в поток вслед за первым кодом этой последовательности. Максимальное число кодов, равных по величине, составляет 1023, код 1111111111. На чертежах: кодер на фиг.1, диаграммы процесса сжатия и восстановления потока на фиг.2, декодер на фиг.3. Кодер включает /фиг.1/ последовательно соединенные 8-разрядный регистр 1, схему 2 сравнения /компаратор/, 10-разрядный счетчик 3 импульсов, дешифратор 4 и блок 5 ключей из восьми ключей, блок 6 элементов из восьми элементов и блок 7 регистрации, являющийся буферным накопителем 11-разрядных кодов. Декодер включает /фиг.3/ последовательно соединенные первый 11-разрядный регистр 8, введенный накопитель 9 кодов, соответствующей емкости 11-разрядных кодов, введенный третий 11-разрядный регистр 10, первый блок 11 ключей из восьми ключей и второй 8-разрядный регистр 12, последовательно соединенные второй блок 13 ключей из десяти ключей, 10-разрядный вычитающий счетчик 14 импульсов и дешифратор 15, включает первый 16, второй 17 ключи и введенные третий 18 и четвертый 19 ключи. На вход кодера /фиг.1/ поступают 8-разрядные коды в параллельном виде с АЦП /или другого источника цифровых данных/. Первый-восьмой разряды кода поступают на первый-восьмой входы регистра 1, на первый-восьмой входы схемы 2 сравнения и на первый-восьмой входы блока 6 элементов задержек. Исходное состояние ключей в блоке 5 открытое. Импульсы кода в блоке 6 элементов задержек задерживаются на время срабатывания схемы 2 сравнения и поступают через открытые ключи блока 5 на первый-восьмой входы разрядов в блоке 7 регистрации. Схема 2 сравнения производит сравнение по величине каждого предыдущего и последующего кодов, выявляя их равенство или неравенство. В качестве схемы 2 сравнения приняты две микросхемы 530СП1 с временем срабатывания 18 нс [2, c.279]. При неравенстве кодов А больше В схема сравнения выдает сигнал на выходе 2 фиг.1 [2, с.272, рис.2.190, выход 5], а при А меньше В выдает сигнал с выхода 3 /в микросхеме выход 7/, при равенстве кодов А=В выдает сигнал с выхода 1 /в микросхеме выход 6/. При равенстве кодов сигнал с выхода 1 схемы сравнения 2 закрывает Uз ключи в блоке 5, поступает счетным импульсом на счетный вход счетчика 3 импульсов и на первый управляющий Uвыд вход регистра 1. Счетчик 3 ведет счет импульсов, пока в потоке идут коды, равные по величине. При неравенстве кодов со схемы 2 сравнения идет сигнал с выхода 2 или 3, которые объединены, сигналы с этих выходов используются в качестве управляющих сигналов. При следовании равных по величине кодов счетчик 3 импульсов /микросхема К531ИЕ 17П с временем срабатывания 12 нс [2, с.156]/ производит счет числа равных по величине кодов. Счетчик 3 импульсов 10-разрядный, максимальный код в нем 1111111111 /1023/. При сравнении в схеме 2 неравных кодов появляется сигнал с выхода 2 или 3, который обнуляет Uо регистр 1, выдает из счетчика 3 подсчитанный на этот момент код на входы первого-десятого разрядов блока 7 регистрации и заполняет своим импульсом 11-й разряд в блоке 7 регистрации, являющийся признаком числа кодов, равных по величине, со счетчика 3. Параллельно код со счетчика 3 импульсов поступает в дешифратор 4, выходной сигнал с которого поступает на управляющий Uо вход счетчика 3, обнуляя его, и через диод открывает ключи Uот в блоке 5 ключей. Подсчитываемые счетчиком 3 коды на вход блока 7 не поступают, закрыты ключи в блоке 5, а исключаются из потока: за их счет идет сжатие потока /фиг.2/. За первым кодом последовательности равных кодов следует код со счетчика 3 импульсов на входы первого-десятого разрядов блока 7 регистрации и сигнал с второго /третьего/ выхода схемы 2 сравнения на вход одиннадцатого разряда блока 7. При следовании подряд равных кодов более 1023 дешифратор 4 при коде 1111111111 выдает импульс, открывающий Uот ключи в блоке 5, выдает код из счетчика 3 на входы первого-десятого разрядов блока 7 и импульс в 11-й разряд блока 7 регистрации. На входе блока 7 регистрации поток кодов имеет вид диаграммы II фиг.2. Блок 7 регистрации производит регистрацию потока кодов на твердотельный носитель [3, с.326, 328], в который поток заносится байт за байтом и принимает вид диаграммы III на фиг.2. С носителя сжатый поток кодов может переписываться на диск DVD, загружаться на жесткий диск персонального компьютера /ПК/ или на твердотельный носитель [5, с.13 (400 Гбайт), с.69]. Кодер может быть включен в состав ПК /ноутбук/ и иметь свой выход. Пропускная способность определяется временем срабатывания схемы 2 сравнения 18 нс плюс счетчика 3 импульсов 12 нс, в сумме 30 нс, и обеспечивает следование потока кодов в параллельном виде до 30 Мбайт/с. Для восстановления сжатой информации коды в последовательном виде поступают на информационный вход декодера /фиг.3/, на вход первого регистра 8. Информационный код занимает с первого по восьмой разряды регистра 8, а при поступлении кода числа равных кодов заполняются с первого по одиннадцатый разряды регистра 8. Коды принимают параллельный вид, в котором они дальше и используются. На первый управляющий вход Uт регистра 8 поступают тактовые импульсы Uт. С первого регистра 8 код в параллельном виде выдается сигналом Uвыд частотой  в накопитель 9 кодов, емкость которого соответствует предназначению устройства, в котором используется декодер. Из накопителя 9 кодов коды в параллельном виде выдаются сигналом Uвыд с ключа 18 с частотой

в накопитель 9 кодов, емкость которого соответствует предназначению устройства, в котором используется декодер. Из накопителя 9 кодов коды в параллельном виде выдаются сигналом Uвыд с ключа 18 с частотой  . При закрытом ключе 18 накопитель 9 сосредотачивает коды в себе. Исходное состояние ключей в блоке 11 открытое, в блоке 13 закрытое, ключей 16, 18, 19 открытое, ключа 17 закрытое. Пока в регистр 10 поступают коды без сигнала опознания в 11-м разряде кода, они поступают через открытые ключи блока 11 в регистр 12, с него выдаются сигналом Uвыд1 с ключа 16 на выход декодера с частотой

. При закрытом ключе 18 накопитель 9 сосредотачивает коды в себе. Исходное состояние ключей в блоке 11 открытое, в блоке 13 закрытое, ключей 16, 18, 19 открытое, ключа 17 закрытое. Пока в регистр 10 поступают коды без сигнала опознания в 11-м разряде кода, они поступают через открытые ключи блока 11 в регистр 12, с него выдаются сигналом Uвыд1 с ключа 16 на выход декодера с частотой  , где к - коэффициент сжатия информации. Сигнал Uвыд1 при выдаче кода обнуляет разряды регистра 12. При поступлении в регистр 10 кода с сигналом опознания в 11-м разряде сигнал с этого разряда закрывает Uз ключи в блоке 11, открывает ключи в блоке 13, закрывает ключ 16, ключи 18, 19 и открывает ключ 17. Код с регистра 10 поступает через открытые ключи блока 13 в вычитающий счетчик 14 импульсов, а поступление кодов в регистр 10 прекращается: накопитель 9 кодов производит накопление кодов, так как в него продолжают поступать коды с регистра 8. На счетный вход вычитающего счетчика 14 импульсов поступают импульсы с управляющего входа 3 /фиг.3/ с частотой

, где к - коэффициент сжатия информации. Сигнал Uвыд1 при выдаче кода обнуляет разряды регистра 12. При поступлении в регистр 10 кода с сигналом опознания в 11-м разряде сигнал с этого разряда закрывает Uз ключи в блоке 11, открывает ключи в блоке 13, закрывает ключ 16, ключи 18, 19 и открывает ключ 17. Код с регистра 10 поступает через открытые ключи блока 13 в вычитающий счетчик 14 импульсов, а поступление кодов в регистр 10 прекращается: накопитель 9 кодов производит накопление кодов, так как в него продолжают поступать коды с регистра 8. На счетный вход вычитающего счетчика 14 импульсов поступают импульсы с управляющего входа 3 /фиг.3/ с частотой  с ключа 17, с которого они поступают сигналом Uвыд2 на второй управляющий вход регистра 12 и выдают из него код, но при этом не обнуляют разряды регистра 12, поэтому пока идет работа счетчика 14 на вычитание, из регистра 12 выдается один и тот же код: эти коды были изъяты при сжатии потока кодов в кодере. С выхода регистра 12 идет восстановленный на 100% поток 8-разрядных кодов с частотой дискретизации

с ключа 17, с которого они поступают сигналом Uвыд2 на второй управляющий вход регистра 12 и выдают из него код, но при этом не обнуляют разряды регистра 12, поэтому пока идет работа счетчика 14 на вычитание, из регистра 12 выдается один и тот же код: эти коды были изъяты при сжатии потока кодов в кодере. С выхода регистра 12 идет восстановленный на 100% поток 8-разрядных кодов с частотой дискретизации  . С окончанием вычитания в вычитающем счетчике 14 в дешифратор 15 поступает код из нулей, который дешифрируется, с выхода дешифратора 15 сигнал синхронно закрывает ключи в блоке 13, закрывает ключ 17, открывает ключи в блоке 11 и ключи 16, 18, 19. С накопителя 9 кодов опять выдаются коды в регистр 10, с него через ключи блока 11 - в регистр 12 и с него сигналом Uвыд1 - на выход. С приходом следующего кода числа равных кодов в регистр 10 процесс повторяется. Восстановленный поток кодов - на фиг.2, диаграмма IV. Пропускная способность декодера задается временем срабатывания 10,5 нс вычитающего счетчика 14 /микросхема 100ИЕ137 [2, с.428]/ плюс время срабатывания 6 нс дешифратора 15 /микросхема 100ИД161 [2, c.433]/ и составляет до 50 Мбайт/с. Декодер включается в состав аппаратуры, в которую включен и заявляемый кодер, или отдельно в видеопроигрыватели на входе и в ПК и ноутбуки, на которых информация записывалась с использованием предлагаемого здесь кодера.

. С окончанием вычитания в вычитающем счетчике 14 в дешифратор 15 поступает код из нулей, который дешифрируется, с выхода дешифратора 15 сигнал синхронно закрывает ключи в блоке 13, закрывает ключ 17, открывает ключи в блоке 11 и ключи 16, 18, 19. С накопителя 9 кодов опять выдаются коды в регистр 10, с него через ключи блока 11 - в регистр 12 и с него сигналом Uвыд1 - на выход. С приходом следующего кода числа равных кодов в регистр 10 процесс повторяется. Восстановленный поток кодов - на фиг.2, диаграмма IV. Пропускная способность декодера задается временем срабатывания 10,5 нс вычитающего счетчика 14 /микросхема 100ИЕ137 [2, с.428]/ плюс время срабатывания 6 нс дешифратора 15 /микросхема 100ИД161 [2, c.433]/ и составляет до 50 Мбайт/с. Декодер включается в состав аппаратуры, в которую включен и заявляемый кодер, или отдельно в видеопроигрыватели на входе и в ПК и ноутбуки, на которых информация записывалась с использованием предлагаемого здесь кодера.

Работа устройства

Для сжатия цифровых данных коды с АЦП в параллельном виде поступают в кодер /фиг.1/ на первый-восьмой разряды регистра 1, первые входы схемы 2 сравнения и на входы блока 6 элементов задержек. При следовании кодов, неравных по величине, они через открытые ключи блока 5 проходят на регистрацию в блок 7 регистрации. При следовании в потоке кодов, равных по величине, первый код этой последовательности через открытые ключи блока 5 проходит в блок 7 регистрации, а начиная со второго кода, равные коды подсчитываются счетчиком 3 импульсов, в котором формируется двоичный код числа кодов, равных по величине, и который вместо изъятых кодов регистрируется вслед за первым кодом в блоке 7 регистрации. При появлении в потоке кода, отличного по величине, процесс повторяется. Поток кодов, поступающий на вход блока 7 регистрации, на фиг.2 диаграмма II, поток кодов в блоке 7 на диаграмме III и является сжатым потоком цифровых данных. Для восстановления сжатого потока кодов коды с соответствующего носителя, на который они были переписаны, в последовательном виде поступают на информационный вход регистра 8 декодера /фиг.3/, где принимают параллельный вид и поступают в накопитель 9 кодов, с которого выдаются сигналами Uвыд с ключа 18 и поступают в третий регистр 10, с которого выдаются сигналами с ключа 19 в параллельном виде на входы блоков 11, 13 ключей. В исходном состоянии ключи блока 11 открыты, поэтому код через открытые ключи блока 11 поступает во второй регистр 12 на первый-восьмой разряды, а с него выдается сигналом Uвыд1 с ключа 16 на воспроизведение, а регистр 12 обнуляется. При наличии сигнала в одиннадцатом разряде кода код с регистра 8 выдается в накопитель 9 кодов, с него в третий регистр 10, с 11-го разряда которого импульс закрывает ключи в блоке 11 и открывает ключи в блоке 13, он же закрывает ключи 19, 18, 16 и открывает ключ 17. Из накопителя 9 кодов коды не выдаются, он ведет накопление поступающих в него кодов, а код с регистра 10 поступает через открытые ключи блока 13 в вычитающий счетчик 14, на счетный вход которого с ключа 17 поступают импульсы, по которым вычитающий счетчик ведет вычитание, параллельно импульсы с ключа 17 поступают сигналами Uвыд2 на второй управляющий вход регистра 12 и выдают из его первого-восьмого разрядов один и тот же код, не обнуляя разряды регистра 12. Выдача кода идет столько раз, пока вычитающий счетчик 14 не закончит вычитание и не обнулится. С окончанием процесса вычитания дешифратор 15 выдает сигнал, который закрывает ключи в блоке 13, открывает ключи в блоке 11, закрывает ключ 17 и открывает ключи 16, 18, 19. Далее процессы повторяются. Восстановленный поток кодов - на фиг.2, диаграмма IV. Заявляемое устройство выполняет сжатие видео, звуковой и измерительной информации и может использоваться в составе ПК, ноутбука при записи цифровой информации на жесткие диски, на диски DVD, в видеопроигрывателях и в цифровой аппаратуре при выполнении круглосуточных измерений.

Использованные источники

1. Патент РФ №2270528 С1, кл. H04N 1/417, Бюл. №5 от 20.02.06, прототип.

2. Цифровые интегральные микросхемы, справочник. Минск, 1991, с.156, 272, 279, 428, 433.

3. В.И.Мураховский. Устройство компьютера. М., 2003, с.326, 328.

4. Гук М.Ю. Аппаратные средства IBM PC. Энциклопедия. СПб.: Питер, 2006, с.519, 522.

5. Журнал: Персональный компьютер сегодня /PC MAGAZINE/, №11, /209/ ноябрь 2008, с.13, третья колонка внизу, с.69.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЕРСОНАЛЬНЫЙ КОМПЬЮТЕР | 2009 |

|

RU2402806C1 |

| ПЕРСОНАЛЬНЫЙ КОМПЬЮТЕР | 2009 |

|

RU2421771C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2010 |

|

RU2420025C1 |

| ВИДЕОКАМЕРА | 2007 |

|

RU2359425C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2011 |

|

RU2462828C1 |

| ДВУХКАНАЛЬНАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 2009 |

|

RU2413387C1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ НА ОПТИЧЕСКОМ ДИСКЕ | 2006 |

|

RU2316060C1 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2007 |

|

RU2358411C1 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2008 |

|

RU2368097C1 |

| ВИДЕОКАМЕРА | 2007 |

|

RU2358412C1 |

Изобретение относится к области регистрации цифровой информации, в частности к устройствам сжатия и восстановления цифровых данных для записи на любой носитель. Техническим результатом является увеличение степени сжатия цифровых данных. Указанный технический результат достигается тем, что в кодере счетчик импульсов и дешифратор выполняются десятиразрядными, блок регистрации выполняется одиннадцатиразрядным и в декодер вводятся накопитель кодов соответствующей емкости, третий одиннадцатиразрядный регистр, третий и четвертый ключи, первый регистр выполняется одиннадцатиразрядным, вычитающий счетчик импульсов и дешифратор выполняются десятиразрядными. 3 ил.

Устройство сжатия и восстановления цифровых данных, содержащее кодер и декодер, кодер включает последовательно соединенные регистр, схему сравнения, счетчик импульсов, дешифратор и блок ключей, блок элементов задержек и блок регистрации, входы которого подключены к первому-восьмому выходам блока ключей, а выходы блока регистрации являются выходами кодера, первый-восьмой входы регистра, первые входы схемы сравнения и первый-восьмой входы блока элементов задержек поразрядно объединены и являются первым-восьмым входами кодера, первый выход схемы сравнения подключен к счетному входу счетчика импульсов, к первому Uвыд управляющему входу регистра и к второму управляющему U3 входу блока ключей, второй и третий выходы схемы сравнения объединены и подключены к второму управляющему U0 входу регистра, к первому управляющему Uвыд входу счетчика импульсов и к первому управляющему Uот входу блока ключей, выходы счетчика импульсов подключены к входам дешифратора и через соответствующее число диодов подключены к входам соответствующих разрядов блока регистрации, выход дешифратора подключен к второму управляющему U0 входу счетчика импульсов и через диод подключен к первому управляющему Uот входу блока ключей, декодер включает первый регистр, информационный вход которого является входом декодера, первый блок ключей из восьми ключей, первый и второй ключи и второй регистр, входы первого-восьмого разрядов которого подключены к первому-восьмому выходам первого блока ключей, а первый-восьмой выходы второго регистра являются выходами декодера, последовательно соединенные второй блок ключей, вычитающий счетчик импульсов и дешифратор, выход которого подключен к первому управляющему Uот входу первого блока ключей и второму управляющему U3 входу второго блока ключей, к первому управляющему входу Uот первого ключа, к второму управляющему U3 входу второго ключа, первым управляющим Uт входом декодера является тактовый Uт вход первого регистра, второй управляющий вход которого Uвыд является вторым управляющим входом декодера, выход первого ключа подключен к первому управляющему Uвыд1 входу второго регистра, выход второго ключа подключен к второму управляющему Uвыд2 входу второго регистра и к счетному входу вычитающего счетчика импульсов, второй управляющий U3 вход первого ключа и первый управляющий Uот вход второго ключа объединены и подключены к выходу дешифратора, к которому подключены первый управляющий Uот вход первого блока ключей и второй управляющий U3 вход второго блока ключей, отличающееся тем, что в кодере счетчик импульсов и дешифратор выполнены десятиразрядными, блок регистрации выполнен одиннадцатиразрядным, входы с первого по десятый которого подключены через диоды к выходам первого-десятого разрядов счетчика импульсов, а вход одиннадцатого разряда подключен к объединенным второму-третьему выходам схемы сравнения, и к второму управляющему Uвыд входу счетчика импульсов, в декодер введены накопитель кодов соответствующей емкости одиннадцатиразрядных кодов, третий одиннадцатиразрядный регистр, третий и четвертый ключи, первый регистр выполнен одиннадцатиразрядным, вычитающий счетчик импульсов и дешифратор выполнены десятиразрядными, входы первого-одиннадцатого разрядов накопителя кодов подключены соответственно к выходам первого-одиннадцатого разрядов первого регистра, входы первого-одиннадцатого разрядов третьего регистра подключены соответственно к первому-одиннадцатому выходам накопителя кодов, второй блок ключей содержит десять ключей, первый-десятый входы которого подключены соответственно к выходам первого-десятого разрядов третьего регистра, выход одиннадцатого разряда которого подключен параллельно к вторым управляющим U3 входам первого, третьего, четвертого ключей, к первому управляющему Uот входу второго ключа, к второму управляющему U3 входу первого блока ключей и к первому управляющему Uот входу второго блока ключей, сигнальные входы третьего, четвертого ключей и второй управляющий вход Uвыд первого регистра объединены и являются вторым управляющим входом декодера, выход третьего ключа подключен к управляющему Uвыд входу накопителя кодов, выход четвертого ключа подключен к управляющему Uвыд входу третьего регистра, сигнальные входы первого и второго ключей объединены и являются третьим управляющим входом декодера, первые Uот управляющие входы третьего и четвертого ключей объединены и подключены к выходу дешифратора.

| СПОСОБ СЖАТИЯ И ВОССТАНОВЛЕНИЯ ЦИФРОВЫХ ДАННЫХ И УСТРОЙСТВО ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2270528C1 |

| СПОСОБ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИЗОБРАЖЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2093968C1 |

| US 4542413 А, 17.09.1985 | |||

| WO 9620557 А1, 04.07.1996 | |||

| Универсальный шарнир | 1976 |

|

SU588411A2 |

Авторы

Даты

2011-05-27—Публикация

2010-02-19—Подача