Предлагаемое изобретение относится к вычислительной технике и может быть использовано при проектировании систем управления исследовательскими процессами, в частности, при разработке автоматизированного комплекса, предназначенного для определения физико-механических свойств материалов методом кинетического индентирования.

Известно устройство для управления выводом данных в старт-стопном режиме [1]. Известно также устройство для управления выводом данных в старт-стопном режиме, представляющее собой наиболее близкое техническое решение к заявленному предполагаемому изобретению [2].

Недостатком этого устройства является наличие на его выходе данных только в кодах цифровой формы.

Целью предлагаемого изобретения является получение на выходе устройства данных в аналоговой форме.

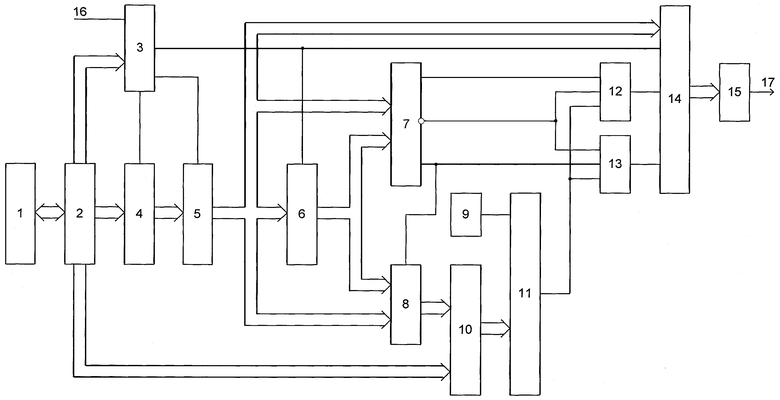

Поставленная цель достигается тем, что в систему управления выводом данных, содержащую первый блок 3 сопряжения, второй блок 2 сопряжения, регистр 5 и блок 4 памяти, причем первый вход регистра 5 подключен к первый выходу первого блока 3 сопряжения, а второй вход - к выходу блока 4 памяти, вход первого блока 3 сопряжения и первый выход второго блока 2 сопряжения связаны между собой, дополнительно подключены ЭВМ 1, дополнительный регистр 6, а также подключены схема 7 сравнения кодов, вычитатель 8 кодов, генератор 9 опорной частоты, преобразователь 10 кодов, управляемый делитель 11 частоты. Также дополнительно введены первый и второй логические элементы 3И 12 и 13, соответственно, реверсивный счетчик 14, цифро-аналоговый преобразователь (ЦАП) 15, входная шина 16 и выходная шина 17. Двунаправленный вход-выход ЭВМ 1 соединен с двунаправленным входом-выходом второго блока 2 сопряжения. Второй выход второго блока 2 сопряжения подключен к первому входу блока 4 памяти, второй вход блока 4 памяти соединен с вторым выходом первого блока 3 сопряжения. Третий выход первого блока 3 сопряжения объединен с первым входом дополнительного регистра 6 и четвертым входом реверсивного счетчика 14. Вторые входы дополнительного регистра 6, схемы 7 сравнения кодов, вычитателя 8 кодов и реверсивного счетчика 14 объединены между собой и подключены к выходу регистра 5. Первые входы вычитателя 8 кодов и схемы 7 сравнения кодов объединены между собой и соединены с выходом дополнительного регистра 6. Выход вычитателя 8 кодов объединен с первым входом преобразователя 10 кодов, выход которого подключен к второму входу управляемого делителя 11 частоты, первый вход управляемого делителя 11 частоты соединен с выходом генератора 9 опорной частоты. Выход управляемого делителя 11 частоты подключен к третьему входу первого логического элемента 12 3И, а также к третьему входу второго логического элемента 13 3И. Первый выход схемы 7 сравнения кодов соединен с первым входом первого логического элемента 12 3И, второй выход схемы 7 сравнения кодов соединен с объединенными между собой вторыми входами первого логического элемента 12 3И и второго логического элемента 13 3И. Третий выход схемы 7 сравнения кодов подключен к первому входу второго логического элемента 13 3И, а также к третьему входу вычитателя 8. Выход второго логического элемента 13 3И соединен с третьим входом реверсивного счетчика 14. Первый вход реверсивного счетчика 14 объединен с выходом первого логического элемента 12 3И. Третий выход первого блока 3 сопряжения подключен к четвертому входу реверсивного счетчика 14, а выход реверсивного счетчика 14 объединен с входом ЦАП 15, выход которого соединен с выходной шиной 17. Второй вход преобразователя 10 кодов подключен к третьему выходу второго блока 2 сопряжения. Второй вход первого блока 3 сопряжения объединен с входной шиной 16, а выход ЦАП 15 соединен с выходной шиной 17.

Рассмотрим работу системы управления выводом данных на ее конкретном применении в автоматизированном комплексе, предназначенном для определения физико-механических свойств материалов методом кинетического индентирования.

В качестве ЭВМ 1 применена персональная ЭВМ, совместимая с IBM PC и имеющая слот расширения PCI. Аппаратные средства блока 2 сопряжения обеспечивают обмен данными с ЭВМ 1 по протоколу обмена PCI через двунаправленный вход-выход. По шине, связывающей двунаправленные входы-выходы ЭВМ 1 и блока 2 сопряжения, передаются коды адреса, данных и команд, а также сигналы управления.

При включении автоматизированного комплекса и, соответственно, аппаратных средств системы, входящей в состав этого комплекса, на шине PCI будет сформирован сигнал RESET, который установит электронные и механические элементы системы в состояние готовности к работе.

В начале цикла индентирования управляющая этим циклом программа, запущенная в ЭВМ 1, устанавливает через третий выход блока 2 сопряжения на втором входе преобразователя 10 кодов код периода меток времени, а также через второй выход записывает в блок 4 памяти массив кодов данных. Этот массив кодов данных представляет собой цифровые коды на коды данных, определяющие алгоритм выполнения цикла индентирования. После завершения записи массива кодов данных в блок 4 памяти ЭВМ 1 по команде управляющей программы через второй блок 2 сопряжения сформирует на первом входе первого блока 3 сопряжения сигнал, который воспринимается блоком 3 сопряжения как сигнал начала собственно цикла индентирования. С приходом с входной шины 16 на второй вход первого блока 3 сопряжения сигнала метки времени первый блок 3 сопряжения формирует на своем третьем выходе сигнал, который записывает код с выхода регистра 5 в дополнительный регистр 6 и в реверсивный счетчик 14. Далее по окончанию этого сигнала первый блок 3 сопряжения сформирует на своем втором выходе сигнал чтения кода данных из блока 4 памяти. Через время, необходимое для чтения кода данных из блока 4 памяти, первый блок 3 сопряжения сформирует на своем первом выходе сигнал, который запишет прочитанный из блока 4 памяти код данных в регистр 5. Схема 7 сравнения кодов в зависимости от величины выходного кода данных регистра 5 (код А) и величины выходного кода данных дополнительного регистра 6 (код В) формирует один из трех возможных сигналов. Если величина кода А больше величины кода В - на первом выходе схемы 7 сравнения кодов будет сформирован разрешающий работу первого логического элемента 12 3И сигнал. Если величина кода А меньше величины кода В - на третьем выходе схемы 7 сравнения кодов будет сформирован разрешающий работу второго логического элемента 13 3И сигнал. Если величина кода А равна величине кода В - на втором выходе схемы 7 сравнения кодов будет сформирован запрещающий работу первого логического элемента 12 3И, а также второго логического элемента 13 3И сигнал. При неравенстве величин кода А и кода В на втором выходе схемы 7 сравнения кодов будет сформирован разрешающий работу первого логического элемента 12 3И и второго логического элемента 13 3И сигнал. Вычитатель 8 формирует на своем выходе модуль разности величин кода А и кода В. Для этого вычитатель 8 при отсутствии сигнала на своем третьем входе суммирует "единицу" с величиной кода А и инверсным значением величины кода В, а при наличии сигнала на своем третьем входе суммирует величину кода А с инверсным значением величины кода В и последующим инвертированием полученного результата. Преобразователь 10 кодов представляет собой как один из вариантов исполнения в данном комплексе постоянное запоминающее устройство (ПЗУ), на адресные входы которого поданы код величины модуля разности с выхода вычитателя 8, а также код величины периода метки времени с третьего выхода второго блока 2 сопряжения и установлен режим чтения. В это ПЗУ предварительно записаны коды, при чтении которых и подаче их на второй вход управляемого делителя 11 частоты, последний формирует на своем выходе последовательность импульсов, численно равную величине кода модуля разности и не зависимую от величины кода периода меток времени. Первая пришедшая после команды начала собственно индентирования на второй вход первого блока 3 сопряжения метка времени инициирует запись "нулевого" кода с выхода регистра 5 (сигнал RESET устанавливает на выходе регистра 5 "нулевой код") в реверсивный счетчик 14 и дополнительный регистр 6, после чего на выходе регистра 5 и, соответственно, на вторых входах вычитателя 8, дополнительного регистра 6, схемы 7 сравнения кодов, а также на втором входе реверсивного счетчика 14 будет установлен цифровой код аналоговой величины силы воздействия индентора на поверхность исследуемого материала до прихода очередной метки времени. Допустим, величина этого выходного кода равна 137, а период метки времени составляет 6 мс, (диапазон меток времени в конкретном применении установлен от 1 до 256 мс с шагом в 1 мс), тогда схема 7 сравнения кодов на своем первом выходе сформирует сигнал, разрешающий работу первого логического элемента 12 3И, а на выходе вычитателя 8 и, соответственно, на втором входе управляемого делителя 11 частоты будет установлен код, величина которого равна 137. При таком коде на своем втором входе управляемый делитель 11 частоты будет формировать на выходе последовательность импульсов с периодом следования, равным 43,79 мкс. Период следования импульсов с выхода генератора 9 опорной частоты должен быть равным 319,67 нс. Импульсы с выхода управляемого делителя 11 частоты, пройдя через первый логический элемент 12 3И на первый (суммирующий) вход реверсивного счетчика 14 за период метки времени, т.е. за 6 мс, увеличат величину выходного кода с "нулевого" значения до 137. Таким образом, вышеупомянутое изменение выходного кода реверсивного счетчика 14 за период метки времени будет выполнено не "скачкообразно", а за 137 тактов минимального изменения. Выходное напряжение ЦАП 15, который преобразует величину входного кода, также изменится не "скачкообразно", а за 137 тактов увеличения на единицу своего младшего значащего разряда в каждом такте. Выход ЦАП 15 соединен с входом генератора силы (преобразователь напряжение-сила), (на чертеже не показан), поэтому изменение величины силы будет аналогично вышеописанному. Если в процессе индентирования величина кода А будет меньше величины кода В, импульсы с выхода управляемого делителя 11 частоты через второй логический элемент 13 поступят на третий (вычитающий) вход реверсивного счетчика 14 и уменьшат величину его выходного кода на величину кода модуля разности текущей метки времени. Процесс вычитания аналогичен вышеописанному процессу суммирования. Если в процессе индентирования код А будет равен коду В, сигнал с второго выхода схемы 7 сравнения кодов запретит работу первого логического элемента 12 3И и второго логического элемента 13 3И, при этом величина выходного кода реверсивного счетчика не изменится.

Таким образом, введение в систему дополнительных компонентов с их взаимосвязями обеспечивает получение на выходе системы данных в аналоговой форме.

Источники информации

[1] Патент Великобритании, G4A, №1264096, 1972.

[2] Авторское свидетельство СССР, кл. G06F 3/04, №583423, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2013 |

|

RU2549513C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2010 |

|

RU2445675C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВВОДОМ-ВЫВОДОМ ДАННЫХ | 2010 |

|

RU2427881C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2010 |

|

RU2445673C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2012 |

|

RU2522025C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ С ДИНАМИЧЕСКОЙ БАЛАНСИРОВКОЙ "НУЛЯ" | 2012 |

|

RU2503990C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2013 |

|

RU2547620C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ В ЦИФРОВОЙ КОД | 2005 |

|

RU2298193C1 |

| ПРЕОБРАЗОВАТЕЛЬ ВЕЛИЧИНЫ СИЛЫ ВОЗДЕЙСТВИЯ В НАПРЯЖЕНИЕ | 2005 |

|

RU2304283C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2012 |

|

RU2551807C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в расширении области применения за счет получения на выходе системы данных в аналоговой форме. Указанный технический результат достигается тем, что система управления выводом данных содержит первый и второй блоки сопряжения, регистр, блок памяти, ЭВМ и дополнительный регистр. Также содержит схему сравнения кодов, вычитатель кодов, генератор опорной частоты, преобразователь кодов, цифро-аналоговый преобразователь, управляемый делитель частоты, первый и второй логические элементы ЗИ, реверсивный счетчик, входную и выходную шины. 1 ил.

Система управления выводом данных, содержащая первый блок сопряжения, второй блок сопряжения, регистр и блок памяти, причем первый вход регистра подключен к первому выходу первого блока сопряжения, а второй вход - к выходу блока памяти, первый вход первого блока сопряжения и первый выход второго блока сопряжения связаны между собой, отличающаяся тем, что в нее дополнительно подключены ЭВМ, дополнительный регистр, схема сравнения кодов, вычитатель кодов, генератор опорной частоты, преобразователь кодов, управляемый делитель частоты, первый и второй логические элементы 3И, реверсивный счетчик, цифроаналоговый преобразователь, входная и выходная шины, причем двунаправленный вход-выход ЭВМ соединен с двунаправленным входом-выходом второго блока сопряжения, второй выход второго блока сопряжения подключен к первому входу блока памяти, второй вход блока памяти соединен с вторым выходом первого блока сопряжения, третий выход первого блока сопряжения объединен с первым входом дополнительного регистра и четвертым входом реверсивного счетчика, вторые входы дополнительного регистра, схемы сравнения кодов, вычитателя кодов и реверсивного счетчика объединены между собой и подключены к выходу регистра, первые входы вычитателя кодов и схемы сравнения кодов объединены между собой и соединены с выходом дополнительного регистра, выход вычитателя кодов объединен с первым входом преобразователя кодов, выход которого подключен к второму входу управляемого делителя частоты, первый вход управляемого делителя частоты соединен с выходом генератора опорной частоты, выход управляемого делителя частоты подключен к третьему входу первого логического элемента 3И, а также к третьему входу второго логического элемента 3И, первый выход схемы сравнения кодов соединен с первым входом первого логического элемента 3И, второй выход схемы сравнения кодов соединен с объединенными между собой вторыми входами первого логического элемента 3И и второго логического элемента 3И, третий выход схемы сравнения кодов подключен к первому входу второго логического элемента 3И, а также к третьему входу вычитателя кодов, выход второго логического элемента 3И соединен с третьим входом реверсивного счетчика, первый вход реверсивного счетчика объединен с выходом первого логического элемента 3И, выход реверсивного счетчика объединен с входом цифроаналогового преобразователя, второй вход преобразователя кодов подключен к третьему выходу второго блока сопряжения, второй вход первого блока сопряжения объединен с входной шиной, выход цифроаналогового преобразователя соединен с выходной шиной.

| Устройство для управления выводом данных в старт-стопном режиме | 1976 |

|

SU583423A1 |

| Дисперсионный анализатор спектра | 1985 |

|

SU1264096A1 |

| Устройство для управления выводом данных в старт-стопном режиме | 1985 |

|

SU1275455A2 |

| Устройство управления вводом-выводом | 1990 |

|

SU1839254A1 |

Авторы

Даты

2011-06-10—Публикация

2010-03-26—Подача