Предлагаемое изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании систем управления исследовательскими процессами, в частности при разработке автоматизированного комплекса, предназначенного для определения физико-механических свойств материалов методом кинетического индентирования.

Известно устройство для управления выводом данных [1]. Известно также устройство управления выводом данных, представляющее собой наиболее близкое техническое решение к заявленному предлагаемому изобретению [2].

Недостатком этих устройств является не высокая точность, обусловленная дестабилизирующими факторами.

Целью предлагаемого изобретения является повышение точности.

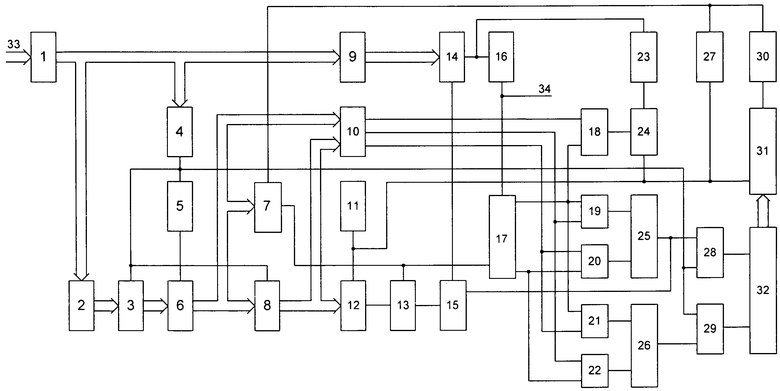

Технический результат достигается тем, что в устройство управления выводом данных, содержащее блок 1 связи, регистр 2 памяти данных, блок 3 памяти, цифровой управляемый генератор 4, элемент 5 задержки, первый и второй регистры 6 и 8, соответственно, первый и второй цифро-аналоговые преобразователи 7 и 12, соответственно, блок цифровых ключей 9, схему 10 сравнения кодов, источник 11 опорного напряжения, аналоговый вычитатель 13, блок 14 времязадающих резисторов, первый и второй аналоговые ключи 15 и 24, соответственно, интегратор 16, компаратор 17, логический элемент 18 2И, первый, второй и третий логические элементы 19, 20 и 25, соответственно, 2И-НЕ, резистор 23, а также входную и выходную 33 и 34, соответственно, шины, причем выход блока 1 связи связан с объединенными между собой входами блока 9 цифровых ключей, регистра 2 памяти данных и цифрового управляемого генератора 4, выход которого подключен к соединенным между собой входу элемента 5 задержки, первому входу второго регистра 8 и дополнительному входу блока 3 памяти, вход блока 3 памяти связан с выходом регистра 2 памяти данных, а выход - с первым входом первого регистра 6, выход которого подключен к объединенным между собой вторым входам первого цифро-аналогового преобразователя 7, второго регистра 8 и схемы 10 сравнения кодов. Выход элемента 5 задержки соединен с вторым входом первого регистра 6, выход второго регистра 8 подключен к объединенным между собой первому входу схемы 10 сравнения кодов и второму входу второго цифро-аналогового преобразователя 12, выходом связанного с вторым входом аналогового вычитателя 13, выход источника 11 опорного напряжения связан с первым входом второго цифро-аналогового преобразователя 12, а также с аналоговым входом второго аналогового ключа 22, выход которого подключен к входу резистора 21, а цифровой вход - к выходу логического элемента 18 2И, первый выход схемы 10 сравнения кодов связан с первым входом логического элемента 18 2И, второй выход - с первым входом первого логического элемента 19 2И-НЕ, третий выход - с первым входом второго логического элемента 20 2И-НЕ, выход аналогового вычитателя 13 подключен к аналоговому входу первого аналогового ключа 15, выход которого соединен с первым входом блока 14 времязадающих резисторов, а цифровой вход - с выходом третьего логического элемента 25 2И-НЕ, первый вход которого связан с выходом второго логического элемента 20 2И-НЕ, а второй вход - с выходом первого логического элемента 19 2И-НЕ, прямой выход компаратора 17 подключен к объединенным между собой вторым входам логического элемента 18 2И и первого логического элемента 19 2И-НЕ, а инверсный выход - к второму входу второго логического элемента 20 2И-НЕ, выход первого цифро-аналогового преобразователя 7 связан с соединенными между собой первыми входами аналогового вычитателя 13 и компаратора 17, выход блока 9 цифровых ключей соединен с вторым входом блока 14 времязадающих резисторов, выход которого объединен с выходом резистора 23 и связан с входом интегратора 16, выход интегратора 16 подключен к второму входу компаратора 17 и соединен с выходной шиной 34, вход блока 1 связи соединен с входной шиной 33, дополнительно введены первый, второй, третий, четвертый и пятый дополнительные логические элементы 21, 22, 26, 28, 29, соответственно, 2И-НЕ. В устройство также введены двоичный реверсивный счетчик 32, дополнительный цифро-аналоговый преобразователь 31, первый и второй дополнительные резисторы 27 и 30, соответственно, причем выход источника 11 опорного напряжения дополнительно подключен к объединенным между собой входу первого дополнительного резистора 27 и первому входу дополнительного цифро-аналогового преобразователя 31, второй вход которого соединен с выходом двоичного реверсивного счетчика 32, а выход - с входом второго дополнительного резистора 30. Первый вход первого цифро-аналогового преобразователя 7 связан с объединенными между собой первым и вторым дополнительными резисторами 27 и 30, соответственно. Выход цифрового управляемого генератора 4 дополнительно подключен к соединенным между собой первым входам дополнительных четвертого и пятого логических элементов 28 и 29, соответственно, 2И-НЕ. Второй выход схемы 10 сравнения кодов дополнительно связан с первым входом второго дополнительного логического элемента 22 2И-НЕ, выход которого подключен к второму входу третьего дополнительного логического элемента 26 2И-НЕ. Третий выход схемы 10 сравнения кодов дополнительно объединен с первым входом первого дополнительного логического элемента 21 2И-НЕ, выходом подключенного к второму входу третьего дополнительного логического элемента 26 2И-НЕ. Прямой выход компаратора 17 дополнительно соединен с вторым входом первого дополнительного логического элемента 21 2И-НЕ, а инверсный выход - также дополнительно связан с вторым входом второго дополнительного логического элемента 22 2И-НЕ. Выход четвертого дополнительного логического элемента 28 2И-НЕ объединен с первым входом двоичного реверсивного счетчика 32, второй вход которого подключен к выходу пятого дополнительного логического элемента 29 2И-НЕ. Выход третьего логического элемента 25 2И-НЕ дополнительно соединен с вторым входом четвертого дополнительного логического элемента 28 2И-НЕ. Выход третьего дополнительного логического элемента 26 2И-НЕ объединен с вторым входом пятого дополнительного логического элемента 29 2И-НЕ.

Рассмотрим работу устройства управления выводом данных на его конкретном применении в составе автоматизированного комплекса, предназначенного для определения физико-механических свойств материалов методом кинетического индентирования.

Блок 1 связи шиной 24 соединен с управляющей ЭВМ (на Фиг. не показана). По шине 24, связывающей ЭВМ и блок 1 связи, передаются коды адреса, данных и команд, а также сигналы управления.

В начале цикла индентирования управляющая этим циклом программа, функционирующая в ЭВМ, записывает через блок 1 связи в цифровой управляемый генератор 4 и блок 9 цифровых ключей код периода меток времени, а также через регистр 2 памяти данных в блок 3 памяти массив кодов данных, представляющих собой цифровые коды величины силы воздействия индентора на исследуемый материал по каждой метке времени в процессе цикла индентирования. После завершения записи массива кодов данных в блок 3 памяти из ЭВМ по команде управляющей программы в блок 1 связи поступит код начала собственно цикла индентирования. С приходом этого кода блок 1 связи выдает на вход цифрового управляемого генератора 4 сигнал, разрешающий этому генератору формировать на своем выходе последовательность импульсов как метки времени с периодом следования, определяемого величиной предварительно записанного кода. Первый импульс на выходе цифрового управляемого генератора 4 инициирует формирование на выходе блока 3 памяти первого слова кода величины силы. Одновременно с этим выходной код первого регистра 6 (код A) записывается в второй регистр 8. Далее через время, определяемое величиной времени задержки элемента 5 задержки, выходной код блока 3 памяти записывается в первый регистр 6. На первый вход схемы 10 сравнения кодов, а также на второй вход второго цифро-аналогового преобразователя 12, с выхода второго регистра 8 поступит код (код B). Величина аналогового сигнала на выходе второго цифро-аналогового преобразователя 12 определяется как C=Uион∗B/2n, где Uион - величина выходного напряжения источника 11 опорного напряжения; B - величина кода B; n - число разрядов второго цифро-аналогового преобразователя 12. В данный момент времени величина этого аналогового сигнала равна "нулю". На вторые входы второго регистра 8, первого цифро-аналогового преобразователя 7 и схемы 10 сравнения кодов с выхода первого регистра 6 поступит код A, по величине, например, больше "нуля", в результате чего на втором выходе схемы 10 сравнения кодов и, соответственно, на первом входе первого логического элемента 19 2И-НЕ будет сформирована логическая единица, а на выходе первого цифро-аналогового преобразователя 7 будет сформирован аналоговый сигнал, величина которого будет равна D=Uион∗A/2n, где Uион - величина выходного напряжения источника 11 опорного напряжения; A - величина кода A и n - число разрядов первого цифро-аналогового преобразователя 7. Этот аналоговый сигнал поступит на первый вход аналогового вычитателя 13, а также на первый вход компаратора 17, в результате чего на выходе аналогового вычитателя 13 и, соответственно, на аналоговом входе первого аналогового ключа 15 будет сформирован разностный сигнал, по величине равный разности аналоговых сигналов D и C, т.е. D-C, а так как величина логического сигнала на втором входе компаратора 17 в начальный момент равна "нулю, то на прямом выходе компаратора 17 и, соответственно, на втором входе первого логического элемента 19 2И-НЕ будет установлена логическая "единица". Наличие на первом и втором входах первого логического элемента 19 2И-НЕ логических "единиц" приведет к формированию логической "единицы" на выходе третьего логического элемента 25 2И-НЕ и, соответственно, на цифровом входе первого аналогового ключа 15. Это, в свою очередь, обеспечит прохождение аналогового сигнала D-C положительной полярности с выхода аналогового вычитателя 13 через первый аналоговый ключ 15 на первый вход блока 14 времязадающих резисторов. В зависимости от величины кода периода следования меток времени, поступившего на вход блока 9 цифровых ключей из ЭВМ через блок 1 связи, в блоке 14 времязадающих резисторов устанавливается такая величина времязадающего резистора, при которой формирующийся на выходе интегратора 16 и, соответственно, на втором входе компаратора 17 линейно увеличивающийся аналоговый сигнал к приходу очередной метки времени достигнет величины аналогового сигнала на выходе первого цифро-аналогового преобразователя 7. Как только величина аналогового сигнала на втором входе компаратора 17 достигнет величины аналогового сигнала на его первом входе, на прямом выходе этого компаратора и, соответственно, на втором входе первого логического элемента 19 2И-НЕ будет сформирован логический "ноль", что приведет к установке логического "нуля" на выходе третьего логического элемента 25 2И-НЕ и, соответственно, на цифровом входе первого аналогового ключа 15. Если при последующих метках времени величина кодов A будут больше величины кодов B, процесс формирования на выходе интегратора 16 будет аналогичен вышеописанному. В случае, когда величина кода A будет меньше величины кода B, на выходе аналогового вычитателя 13 будет сформирован сигнал D-C отрицательной полярности, а на третьем выходе схемы 10 сравнения кодов и, соответственно, на первом входе второго логического элемента 20 2И-НЕ будет установлена логическая "единица". Так как в данный момент времени величина аналогового сигнала на первом входе компаратора 17 будет меньше величины аналогового сигнала на его втором входе, то на инверсном выходе компаратора 17 и, соответственно, на втором входе второго логического элемента 20 2И-НЕ будет сформирована логическая "единица". Наличие логических единиц на первом и втором входах второго логического элемента 20 2И-НЕ приведет к формированию на выходе третьего логического элемента 25 2И-НЕ и, соответственно, на цифровом входе первого аналогового ключа 15 логической "единицы", а это, в свою очередь, обеспечит прохождение аналогового сигнала D-C отрицательной полярности с выхода аналогового вычитателя 13 через первый аналоговый ключ 15 на первый вход блока 14 времязадающих резисторов. На выходе интегратора 16 и, соответственно, на выходной шине 34 и втором входе компаратора 17 будет формироваться линейно уменьшающейся аналоговый сигнал и, как только его величина станет меньше величины аналогового сигнала на первом входе компаратора 17, на инверсном выходе этого компаратора и, соответственно, на втором входе второго логического элемента 20 будет сформирован логический "ноль". Это, в свою очередь, приведет к формированию логического "нуля" на выходе третьего логического элемента 25 2И-НЕ и, соответственно, на цифровом входе первого аналогового ключа 15, что запретит прохождение аналогового сигнала D-C с выхода аналогового вычитателя 13 через этот ключ на первый вход блока 14 времязадающих резисторов и остановит процесс формирования аналогового сигнала на выходе интегратора 16. В случае равенства кода A и кода B, на первом выходе схемы 10 сравнения кодов и, соответственно, на первом входе логического элемента 18 2И будет сформирована логическая "единица". В процессе индентирования применяется режим удержания постоянной величины силы на время от нескольких секунд до нескольких часов, т.е. величина аналогового сигнала на выходе интегратора 16 в течение этого времени должна быть неизменной. Конденсатор, входящий в состав интегратора 16, из-за утечки накопленного заряда, имеет свойство саморазряда, т.е. величина аналогового сигнала на выходе этого интегратора будет уменьшаться - что недопустимо. Уменьшение величины аналогового сигнала на выходе интегратора 16 и, соответственно, на втором входе компаратора 17, вызванное саморазрядом вышеупомянутого конденсатора, приведет к формированию логической "единицы" на прямом выходе этого компаратора и, соответственно, на втором входе логического элемента 18 2И. Наличие логических единиц на первом и втором входах логического элемента 18 2И приведет к формированию логической единицы на выходе этого элемента и, соответственно, на цифровом входе второго аналогового ключа 24, а это, в свою очередь, обеспечит прохождение выходного напряжения источника 11 опорного напряжения через второй аналоговый ключ 24 и далее через резистор 23 на вход интегратора 16. Выходное напряжение источника 11 опорного напряжения имеет положительную полярность, поэтому величина выходного аналогового сигнала интегратора 16 начнет увеличиваться. При достижении на выходе интегратора 16 и, соответственно, на втором входе компаратора 17 величины аналогового сигнала, превышающей величину аналогового сигнала на первом входе этого компаратора, на прямом выходе того же компаратора и, соответственно, на втором входе логического элемента 18 2И будет сформирован логический "ноль". Установка логического "нуля" на втором входе логического элемента 18 2И приведет к формированию на выходе этого логического элемента и, соответственно, на цифровом входе второго аналогового ключа 24 логического "нуля", а это, в свою очередь, запретит прохождение выходного напряжения источника 11 опорного напряжения через второй аналоговый ключ 24 и далее через резистор 23 на вход интегратора 16. После этого величина аналогового сигнала на выходе интегратора 16 снова начнет уменьшаться из-за саморазряда вышеупомянутого конденсатора. Далее алгоритм поддержания величины аналогового сигнала при равенстве кода A и кода B на неизменном уровне на выходе интегратора 16 и, соответственно, на выходной шине 34 аналогичен вышеописанному. Со временем в процессе эксплуатации устройства пассивные и активные компоненты подвержены воздействию дестабилизирующих факторов таких, например, как временная деградация, температурный дрейф и другие. Допустим, что в результате этих воздействий в момент появления на первых входах четвертого и пятого дополнительных логических элементов 28 и 29, соответственно, 2И-НЕ импульса на втором входе четвертого дополнительного логического элемента 28 будет установлена логическая "единица" (работа компаратора 17, первого, второго и третьего логических элементов 19, 20, 23, соответственно, 2И-НЕ описана выше) на выходе четвертого дополнительного логического элемента 28 2И-НЕ и, соответственно, на первом входе двоичного реверсивного счетчика 32 будет сформирован сигнал. В результате величина выходного кода этого счетчика будет увеличена на единицу и, соответственно, величина аналогового сигнала на выходе дополнительного цифро-аналогового преобразователя 31 и первом входе первого цифро-аналогового преобразователя 7 будет также увеличена. В случае, когда на втором выходе схемы 10 сравнения кодов будет сформирована логическая "единица", а величина аналогового сигнала на первом входе компаратора 17 меньше величины аналогового сигнала на втором входе этого же компаратора или же когда на третьем выходе схемы 10 сравнения кодов будет сформирована логическая "единица", а величина аналогового сигнала на первом входе компаратора 17 больше величины аналогового сигнала на втором входе этого же компаратора, первым, вторым и третьим дополнительными логическими элементами 21, 22 и 26, соответственно, 2И-НЕ будет сформирована на втором входе пятого дополнительного логического элемента 29 2И-НЕ логическая "единица". С приходом импульса на первый вход пятого дополнительного логического элемента 29 2И-НЕ на выходе этого элемента и, соответственно, на втором входе двоичного реверсивного счетчика 32 будет сформирован сигнал, который уменьшит величину выходного кода этого счетчика и, соответственно, величину аналогового сигнала на первом входе первого цифро-аналогового преобразователя 7.

Таким образом, совокупность элементов устройства с их взаимосвязями обеспечивает в автоматическом режиме по каждой метке времени на всем протяжении цикла индентирования линейное изменение сигнала на выходной шине 34 при дестабилизирующих факторах.

Источники информации

[1] Авторское свидетельство СССР, кл. G06F 3/04, №586452, 1976 г.

[2] Патент РФ №2445673, кл. G06F 3/00, 2010 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2010 |

|

RU2445673C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2012 |

|

RU2522025C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2010 |

|

RU2420788C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ С ДИНАМИЧЕСКОЙ БАЛАНСИРОВКОЙ "НУЛЯ" | 2012 |

|

RU2503990C1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2010 |

|

RU2445675C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2012 |

|

RU2551807C2 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2013 |

|

RU2547620C1 |

| ПРЕОБРАЗОВАТЕЛЬ МЕХАНИЧЕСКИХ ВЕЛИЧИН В НАПРЯЖЕНИЕ С АВТОМАТИЧЕСКОЙ БАЛАНСИРОВКОЙ "НУЛЯ" | 2005 |

|

RU2304284C2 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ В ЦИФРОВОЙ КОД | 2005 |

|

RU2298193C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2024 |

|

RU2822126C1 |

Изобретение относится к устройству управления выводом данных. Технический результат заключается в повышении точности обработки данных. Устройство управления выводом данных содержит блок связи, регистр памяти данных, блок памяти, цифровой управляемый генератор, элемент задержки, первый и второй регистры, первый и второй цифроаналоговые преобразователи, блок цифровых ключей, схему сравнения кодов, источник опорного напряжения, аналоговый вычитатель, блок времязадающих резисторов, первый и второй аналоговые ключи, интегратор, компаратор, логический элемент 2И, первый, второй и третий логические элементы 2И-НЕ, резистор, входную и выходную шины, а также первый, второй, третий, четвертый и пятый дополнительные логические элементы 2И-НЕ, двоичный реверсивный счетчик, дополнительный цифроаналоговый преобразователь, первый и второй дополнительные резисторы. 1 ил.

Устройство управления выводом данных, содержащее блок связи, регистр памяти данных, блок памяти, цифровой управляемый генератор, элемент задержки, первый и второй регистры, первый и второй цифроаналоговые преобразователи, блок цифровых ключей, схему сравнения кодов, источник опорного напряжения, аналоговый вычитатель, блок времязадающих резисторов, первый и второй аналоговые ключи, интегратор, компаратор, логический элемент 2И, первый, второй и третий логические элементы 2И-НЕ, резистор, а также входную и выходную шины, причем выход блока связи связан с объединенными между собой входами блока цифровых ключей, регистра памяти данных и цифрового управляемого генератора, выход которого подключен к соединенным между собой входу элемента задержки, первому входу второго регистра и дополнительному входу блока памяти, вход блока памяти связан с выходом регистра памяти данных, а выход - с первым входом первого регистра, выход которого подключен к объединенным между собой вторым входам первого цифроаналогового преобразователя, второго регистра и схемы сравнения кодов, выход элемента задержки соединен с вторым входом первого регистра, выход второго регистра подключен к объединенным между собой первому входу схемы сравнения кодов и второму входу второго цифроаналогового преобразователя, выходом связанного с вторым входом аналогового вычитателя, выход источника опорного напряжения связан с первым входом второго цифроаналогового преобразователя, а также с аналоговым входом второго аналогового ключа, выход которого подключен к входу резистора, а цифровой вход - к выходу логического элемента 2И, первый выход схемы сравнения кодов связан с первым входом логического элемента 2И, второй выход - с первым входом первого логического элемента 2И-НЕ, третий выход - с первым входом второго логического элемента 2И-НЕ, выход аналогового вычитателя подключен к аналоговому входу первого аналогового ключа, выход которого соединен с первым входом блока времязадающих резисторов, а цифровой вход - с выходом третьего логического элемента 2И-НЕ, первый вход которого связан с выходом второго логического элемента 2И-НЕ, а второй вход - с выходом первого логического элемента 2И-НЕ, прямой выход компаратора подключен к объединенным между собой вторым входам логического элемента 2И и первого логического элемента 2И-НЕ, а инверсный выход - к второму входу второго логического элемента 2И-НЕ, выход первого цифроаналогового преобразователя связан с соединенными между собой первыми входами аналогового вычитателя и компаратора, выход блока цифровых ключей соединен с вторым входом блока времязадающих резисторов, выход которого объединен с выходом резистора и связан с входом интегратора, выход интегратора подключен к второму входу компаратора и соединен с выходной шиной, вход блока связи соединен с входной шиной, отличающееся тем, что в него дополнительно введены первый, второй, третий, четвертый и пятый дополнительные логические элементы 2И-НЕ, двоичный реверсивный счетчик, дополнительный цифроаналоговый преобразователь, первый и второй дополнительные резисторы, причем выход источника опорного напряжения дополнительно подключен к объединенным между собой входу первого дополнительного резистора и первому входу дополнительного цифроаналогового преобразователя, второй вход которого соединен с выходом двоичного реверсивного счетчика, а выход - с входом второго дополнительного резистора, первый вход первого цифроаналогового преобразователя связан с объединенными между собой первым и вторым дополнительными резисторами, выход цифрового управляемого генератора дополнительно подключен к соединенным между собой первым входам дополнительных четвертого и пятого логических элементов 2И-НЕ, второй выход схемы сравнения кодов дополнительно связан с первым входом второго дополнительного логического элемента 2И-НЕ, выход которого подключен ко второму входу третьего дополнительного логического элемента 2И-НЕ, третий выход схемы сравнения кодов дополнительно объединен с первым входом первого дополнительного логического элемента 2И-НЕ, выходом подключенного к второму входу третьего дополнительного логического элемента 2И-НЕ, прямой выход компаратора дополнительно соединен с вторым входом первого дополнительного логического элемента 2И-НЕ, а инверсный выход - также дополнительно связан с вторым входом второго дополнительного логического элемента 2И-НЕ, выход четвертого дополнительного логического элемента 2И-НЕ объединен с первым входом двоичного реверсивного счетчика, второй вход которого подключен к выходу пятого дополнительного логического элемента 2И-НЕ, выход третьего логического элемента 2И-НЕ дополнительно соединен со вторым входом четвертого дополнительного логического элемента 2И-НЕ, выход третьего дополнительного логического элемента 2И-НЕ объединен с вторым входом пятого дополнительного логического элемента 2И-НЕ.

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫВОДОМ ДАННЫХ | 2010 |

|

RU2445673C1 |

| СТЕКЛО | 2006 |

|

RU2306268C1 |

| US 6202198 B1, 13.03.2001 | |||

| US 6498524 B1, 24.12.2002 | |||

Авторы

Даты

2015-04-27—Публикация

2013-12-30—Подача