Изобретение относится к вычислительном технике и предназначено для организации управления работой внешних устройств персональной ЭВМ.

Известно устройство для сопряжения ЭВМ с абонентом, например с интерфейсом типа общая шина, в состав которого входят два блока канальных приемников, дешифратор адреса, блок канальных приемопередатчиков, блок шифрации управляющих сигналов, генератор синхроимпульсов, блок прерывания, блок преобразования параллельного кода в последовательный и обратно, регистр адреса вектора прерывания, регистр режима, преобразователь напряжения, буферный регистр, коммутатор режима и мультиплексор данных (авт.св. СССР № 1334154, кл. G 06 F 13/24, 30.08.87). Однако в данном устройстве обмен ведется только в старт-стопном режиме.

Известно также устройство для сопряжения ЭВМ с внешним устройством, содержащее блок приемопередающих усилителей, дешифратор управляющих сигналов, дешифратор адреса, регистр внутренней адресации, регистр состояния, регистр данных вывода, регистр данных ввода и вывода, усилитель сигнала данных, узел прерывания, коммутатор, шифратор адреса вектора прерывания и элемент задержки (авт.св. Me СССР N; 1312591, кл. G 06 F 13/24, 23.05.87). Это устройство обеспечивает передачу данных только в синхронном режиме.

Наиболее близким по технической сущности к изобретению является устройство для сопряжения ЭВМ с внешним устройством, в состав которого входят узел приемников, узел передатчика, узел приемопередатчиков, регистр состояния, счетчик адреса, узел управления, буферная память, мультиплексор данных, мультиплексор управляющих сигналов, делитель, шинный формирователь (авт.св. СССР № 1401470, кл. G 06 F 13/00, 18.12.86). Однако данное устройство обеспечивает обмен только в старт-стопном режиме.

Целью изобретения является расширение функциональных возможностей за счет совмещения синхронной и асинхронной логики.

Цель достигается тем, что в устройство управления вводом-выводом, содержащее блок приемопередатчиков, блок приемников управляющих сигналов, передатчик ответного сигнала, регистр адреса, дешифратор адреса, дешифратор записи- чтения, три элемента И-НЕ. два элемента НЕ, триггер, причем первые входы-выходы блока приемопередатчиков, входы блока

приемников управляющих сигналов и выход передатчика соединены с адресными и управляющими шинами ЭВМ, вторые входы- выходы блока приемопередатчиков через

внутреннюю шину соединены с информационными входами регистра адреса и группой входов дешифратора адреса, первый и второй выходы блока приемников управляющих сигналов соединены с первым и вторым

входами первого элемента И, введены четыре элемента И-НЕ, элемент И, два элемента НЕ, передатчик сигнала задержки цикла, при этом управляющий вход дешифратора адреса соединен с третьим выходом блока

приемников управляющих сигналов, выход

дешифратора адреса соединен с входом данных регистра адреса, синхровход которого соединен с первым выходом блока приемников управляющих сигналов, а вход

0 сброса - с его четвертым выходом, первая группа разрядных выходов регистра адреса соединена с группой информационных входов дешифратора записи-чтения, первый синхровход которого соединен с выходом

5 второго элемента И-НЕ, входы которого соединены с выходом первого элемента НЕ и пятым выходом блока приемников управляющих сигналов, выход третьего элемента И-НЕ соединен с управляющим входом бло0 ка приемопередатчиков и вторым синхров- ходом дешифратора записи-чтения, выходы которого являются выходами устройства и соединены с входами четвертого элемента И, выход которого соединен с входом сбро5 са триггера, выход первого элемента И соединен с входом первого элемента НЕ и через элемент задержки с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента

0 НЕ и через передатчик ответного сигнала с соответствующей шиной ЭВМ, первый и второй входы третьего элемента И-НЕ соединены соответственно с выходами первого и второго элементов НЕ, вход которого сое5 динен с пятым выходом блока приемников управляющих сигналов, входы элемента И являются входами состояния устройства, а его выход соединен с 1-входом триггера, синхровход которого является синхровхо0 дом устройства, выходы триггера и четвертого элемента И-НЕ соединены с входами шестого элемента И-НЕ, выход которого и выход пятого элемента И-НЕ соединены с входом седьмого элемента И-НЕ, выход ко5 торого через передатчик сигнала задержки цикла соединен с соответствующей шиной ЭВМ.

При анализе известных технических решений не обнаружено решений с признака- ми. сходными с. отличительными

признаками заявленного решения, что дает основание считать предлагаемое техническое решение соответствующим критериям Существенные отличия и Новизна. Этот вывод подтверждается тем, что создается недостижимый ранее положительный эффект, заключающийся в расширении функциональных возможностей устройства и обусловленный новыми признаками по сравнению с использованием известных технических решений.

Благодаря введению четырех элементов И-НЕ, элемента И, двух элементов НЕ и передатчика сигнала задержки цикла с соответствующими связями заявляемое техническое решение приобретает новые свойства, получение которых не обеспечивает прототип и другие технические решения, а именно создается возможность расширить функциональные возможности устройства за счет совмещения синхронной и асинхронной логики.

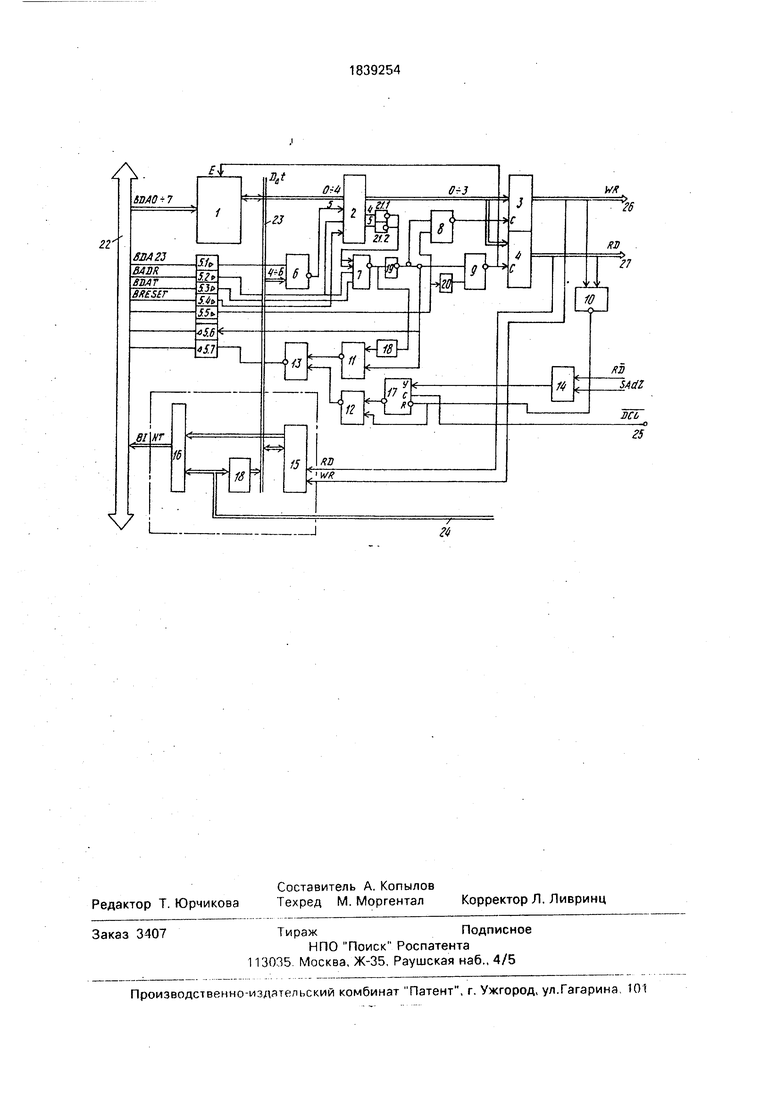

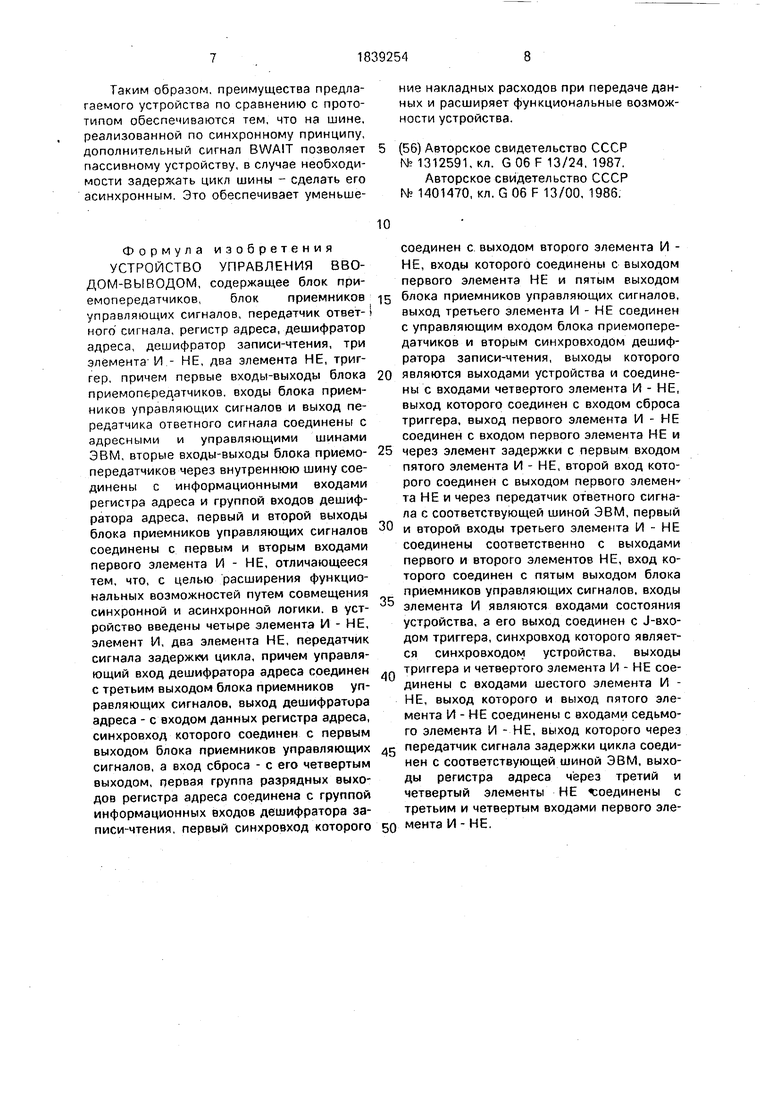

Схема предлагаемого устройства приведена на чертеже.

Устройство для управления вводом-выводом содержит блок 1 приемопередатчиков, регистр 2 адреса, дешифратор 3 записи, дешифратор 4 чтения, блок приемников 5,1-5.5 управляющих сигналов и передатчиков 5.6-5.7, дешифратор б адреса, элементы И-НЕ 7-13, элемент И 14, регистр 15 маски, группу 16 элементов И, триггер 17, элемент 18 задержки, элементы НЕ 19, 20, 21.1. 21.2, шину 22 ЭВМ, внутреннюю шину 23 данных, вход 24 запросов прерывания, синхровход 25, выходы записи 26 и чтения 27. Первые входы-выходы блока 1, входы приемников 5.1-5.5 управляющих сигналов и выходы передатчиков 5.6, 5.7 соединены с адресными и управляющими шинами 22 ЭВМ, вторые входы блока 1 через внутреннюю шину 23 соединены с информационными входами регистра 2 адреса и группой входов дешифратора 6 адреса. Первый и второй выводы блока приемников 5.1-5.5 управляющих сигналов соединены с первым и вторым входами элементами И-НЕ 7, управляющий вход дешифратора 6 адреса соединен с третьим выходом блока приемников 5.1-5.5 управляющих сигналов, выход дешифратора 6 соединен с входом данных регистра 2, синхровход которого соединен с первым выходом блока приемников 5.1- 5.5 управляющих сигналов, а вход сброса - с его четвертым выходом. Первая группа разрядных выходов регистра 2 соединена с группой информационных входов дешифраторов 3, 4, первый синхровход которых соединен с выходом элемента И-НЕ8, входы которого соединены с выходом элемента

НЕ 19 и пятым входом блока приемников 5.1-5.5 управляющих сигналов. Выход третьего элемента И-НЕ 9 соединен с управляющим входом блока 1 и вторым синх- ровходом дешифраторов 3, 4, выходы которых являются выходами 26, 27 устройства и соединены с входами элемента И 10, выход которого соединен с входом сброса триггера 17. Выход элемента И-НЕ 7 соеди0 нен с входом элемента НЕ 19 и через элемент 18 задержки с первым входом элемента И-НЕ 11, второй вход которого соединен с выходом элемента НЕ 19 и через передатчик 5.6 ответного сигнала с соответ5 ствующей шиной ЭВМ. Первый и второй входы элемента И-НЕ 7 соединены соответственно с выходами элементов НЕ 21.1, 21.2. Входы элемента И 14 являются входами состояния устройства, а его выход соеди0 нен с 1-входом триггера 17, синхровход которого является синхровходом устройства. Выходы триггера 17 соединены с входами элемента И-НЕ 12, выход которого и выход элемента И-НЕ 11 соединены с вхо5 дами элемента И-НЕ 13, выход которого через передатчик 5.7 сигнала задержки цикла соединен с соответствующей шиной ЭВМ.

Работает устройство следующим образом.

0 Устройство обеспечивает управление локальной шиной контроллера ввода-вывода персональной ЭВМ. Адрес обращения из процессора или другого активного устройства по шине 22 поступает на вход блока 1

5 приемопередатчиков. Функции синхронизации при передаче адреса выполняют сигналы управления BADR, BDAT и BACR, BWA1T, которые принимаются соответственно приемниками 5.2 и 5.3 и выдаются

0 передатчиком 5.6 и 5.7,

Сигнал BADR присутствует во всех циклах шины. Его формирует активное устройство после выставления адреса на шинах BDA. Снятие этого сигнала информирует

5 пассивное устройство об окончании цикла, и устройство освобождает шину. Сигнал BACK формируется пассивным устройством для уведомления активного устройства, что оно дешифровало свой адрес. Снимается

0 этот сигнал по окончании цикла. Цикл записи определяется сигналом BWR, поступающим на вход приемника 5.5.

Сигналы запросов прерываний поступают по входу 24 на вход группы 16 элементов

5 И, где они маскируются выходными сигналами регистра 15. Сигнал BWA1T может быть выставлен в регистре 2 пассивным устройством не позднее 100 не после приема сигнала, тогда цикл шины удлиняется на время удержания этого сигнала.

Таким образом, преимущества предлагаемого устройства по сравнению с прототипом обеспечиваются тем, что на шине, реализованной по синхронному принципу, дополнительный сигнал BWAIT позволяет пассивному устройству, в случае необходимости задержать цикл шины - сделать его асинхронным. Это обеспечивает уменьшеФормула изобретения УСТРОЙСТВО УПРАВЛЕНИЯ ВВОДОМ-ВЫВОДОМ, содержащее блок приемопередатчиков, блок приемников управляющих сигналов, передатчик ответ- ного сигнала, регистр адреса, дешифратор адреса, дешифратор записи-чтения, три элемента-И - НЕ, два элемента НЕ, триггер, причем первые входы-выходы блока приемопередатчиков, входы блока приемников управляющих сигналов и выход передатчика ответного сигнала соединены с адресными и управляющими шинами ЭВМ, вторые входы-выходы блока приемопередатчиков через внутреннюю шину соединены с информационными входами регистра адреса и группой входов дешифратора адреса, первый и второй выходы блока приемников управляющих сигналов соединены с первым и вторым входами первого элемента И - НЕ, отличающееся тем, что, с целью расширения функциональных возможностей путем совмещения синхронной и асинхронной логики, в устройство введены четыре элемента И - НЕ, элемент И, два элемента НЕ, передатчик сигнала задержка цикла, причем управляющий вход дешифратора адреса соединен с третьим выходом блока приемников управляющих сигналов, выход дешифратора адреса - с входом данных регистра адреса, синхровход которого соединен с первым выходом блока приемников управляющих сигналов, а вход сброса - с его четвертым выходом, первая группа разрядных выходов регистра адреса соединена с группой информационных входов дешифратора записи-чтения, первый синхровход которого

ние накладных расходов при передаче данных и расширяет функциональные возможности устройства.

(56) Авторское свидетельство СССР № 1312591, кл. G Об F 13/24,1987. Авторское свидетельство СССР № 1401470, кл. G 06 F 13/00, 1986.

соединен с выходом второго элемента И - НЕ, входы которого соединены с выходом первого элемента НЕ и пятым выходом

блока приемников управляющих сигналов, выход третьего элемента И - НЕ соединен с управляющим входом блока приемопередатчиков и вторым синхровходом дешифратора записи-чтения, выходы которого

являются выходами устройства и соединены с входами четвертого элемента И - НЕ, выход которого соединен с входом сброса триггера, выход первого элемента И - НЕ соединен с входом первого элемента НЕ и

через элемент задержки с первым входом пятого элемента И - НЕ, второй вход которого соединен с выходом первого элемен та НЕ и через передатчик ответного сигнала с соответствующей шиной ЭВМ, первый

и второй входы третьего элемента И - НЕ соединены соответственно с выходами первого и второго элементов НЕ, вход которого соединен с пятым выходом блока приемников управляющих сигналов, входы

элемента И являются входами состояния устройства, а его выход соединен с J-exo- дом триггера, синхровход которого является синхровходом устройства, выходы триггера и четвертого элемента И - НЕ соединены с входами шестого элемента И - НЕ, выход которого и выход пятого элемента И - НЕ соединены с входами седьмого элемента И - НЕ, выход которого через

передатчик сигнала задержки цикла соединен с соответствующей шиной ЭВМ, выходы регистра адреса через третий и четвертый элементы НЕ соединены с третьим и четвертым входами первого элемента И - НЕ.

ш

S

SAdZ

DCL

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1434448A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство сопряжения для контроля блоков памяти | 1987 |

|

SU1481864A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1989 |

|

SU1624467A2 |

Устройство управления вводом-выводом относится к вычислительной технике и предназначено для организации управления работой внешних устройств в персональной ЭВМ. Цель изобретения - расширение функциональных возможностей ЭВМ. Устройство содержит блок приемопередатчиков, блок приемников управляющих сигналов и передатчиков ответного сигнала регистр адреса, дешифратор адреса, дешифраторы записи/чтения элементы И - НЕ, триггер, элементы И, НЕ, задержки. 1 ил.

№

V

25

4

Авторы

Даты

1993-12-30—Публикация

1990-05-31—Подача