Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ) с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры).

В современной радиоэлектронной аппаратуре находят применение операционные усилители с существенными различными параметрами. Особое место занимают ОУ с простейшей архитектурой, содержащие небольшое число элементов. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предлагаемое изобретение относится к данному типу устройств.

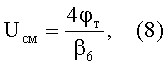

Наиболее близкой по технической сущности к заявляемому ДУ является классическая схема, изображенная на фиг.1 (см. Интегральные микросхемы. Операционные усилители и компараторы. Справочник. - Издательский Дом «Додэка-XXI», 2001, с.269), на основе которой реализованы как отечественные (140УД8, 574УД1, 140УД30), так и зарубежные (TL081) микросхемы. Данная схема стала основой построения большого числа аналоговых устройств, например [1-8].

Существенный недостаток известного ДУ (фиг.1) состоит в том, что он имеет повышенное значение напряжения смещения нуля Uсм.

Основная цель предлагаемого изобретения состоит в уменьшении Uсм.

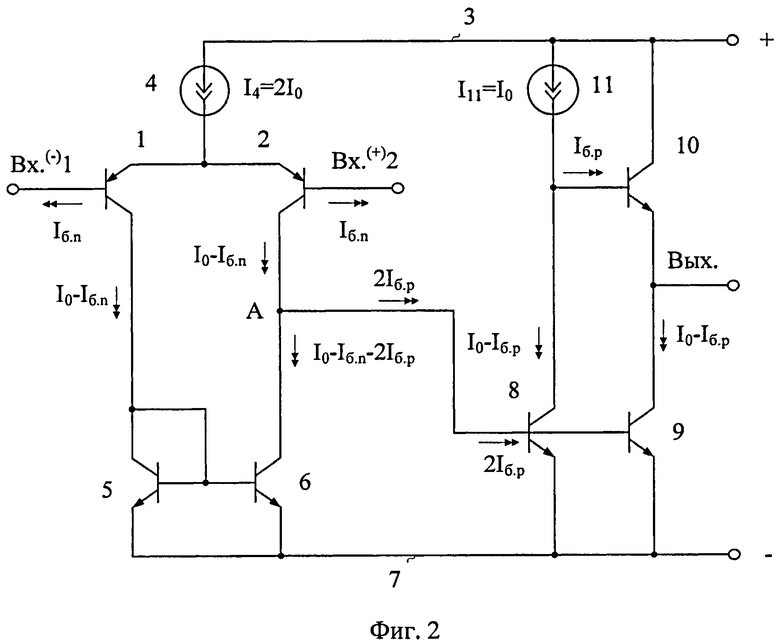

Поставленная цель достигается тем, что в дифференциальном усилителе (фиг.1), содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны друг с другом и подключены к первому 3 источнику питания через первый 4 токостабилизирующий двухполюсник, коллектор первого 1 входного транзистора соединен с коллектором и базой первого 5 вспомогательного транзистора и базой второго 6 вспомогательного транзистора, эмиттеры первого 5 и второго 6 вспомогательных транзисторов связаны со вторым 7 источником питания, коллектор второго 2 входного транзистора соединен с коллектором второго 6 вспомогательного транзистора, первый 8 и второй 9 выходные транзисторы - с объединенными базами, эмиттеры которых соединены со вторым 7 источником питания, коллектор первого 8 выходного транзистора связан с базой третьего 10 выходного транзистора и через второй 11 токостабилизирующий двухполюсник соединен с первым 3 источником питания, коллектор второго 9 выходного транзистора связан с выходом устройства и эмиттером третьего 10 выходного транзистора, коллектор которого соединен с первым 3 источником питания, предусмотрены новые связи - базы первого 8 и второго 9 выходных транзисторов соединены с коллектором второго 6 вспомогательного транзистора.

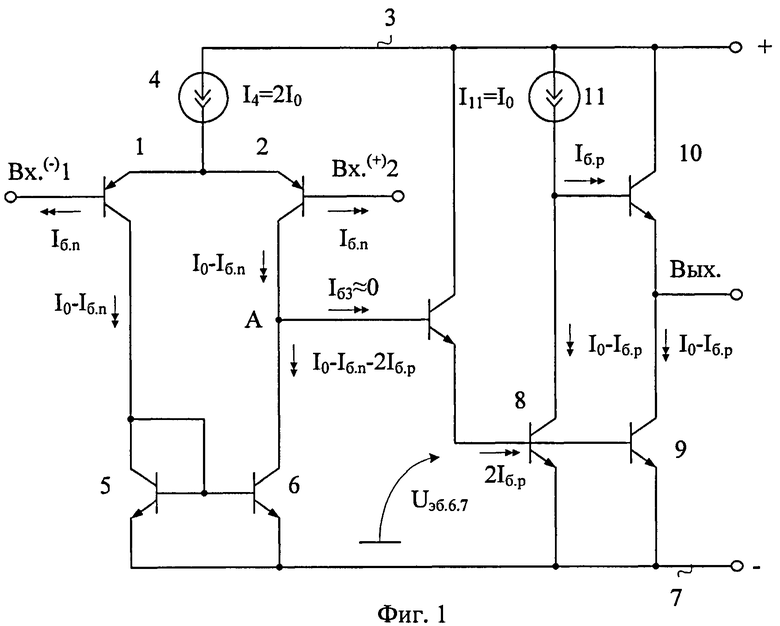

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения. На фиг.3 представлена схема ДУ в соответствии с п.2 формулы изобретения.

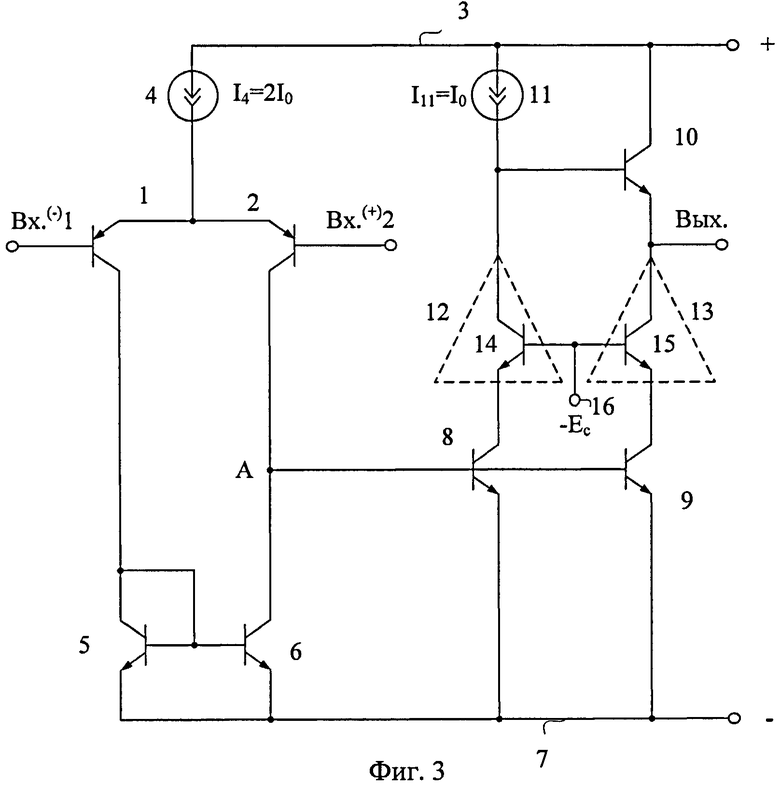

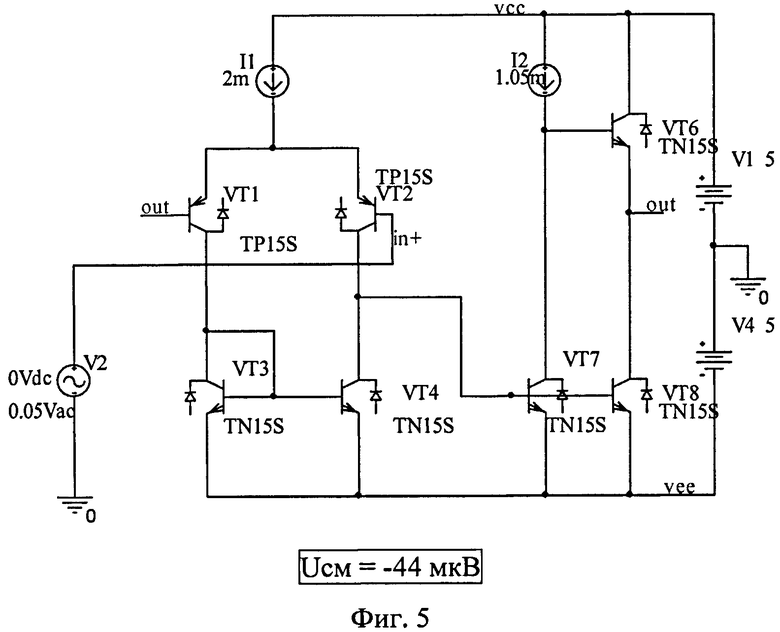

На фиг.4 показана схема ДУ-прототипа фиг.1 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.5 - схема заявляемого ДУ фиг.2.

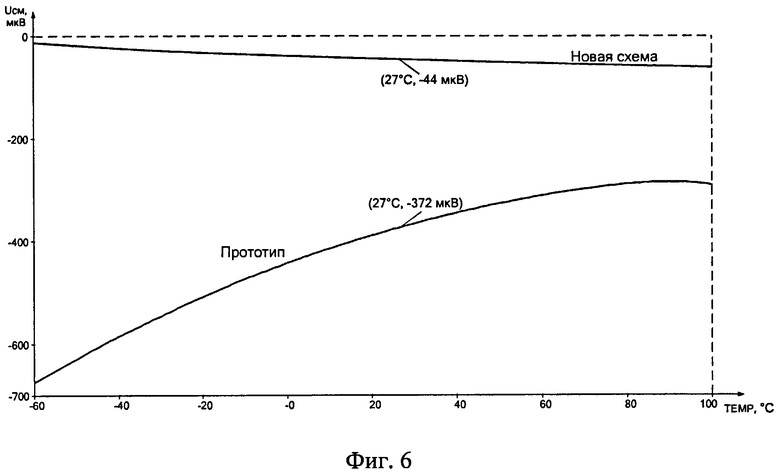

На фиг.6 представлены графики температурной зависимости Uсм сравниваемых схем, фиг.4 и 5.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны друг с другом и подключены к первому 3 источнику питания через первый 4 токостабилизирующий двухполюсник, коллектор первого 1 входного транзистора соединен с коллектором и базой первого 5 вспомогательного транзистора и базой второго 6 вспомогательного транзистора, эмиттеры первого 5 и второго 6 вспомогательных транзисторов связаны со вторым 7 источником питания, коллектор второго 2 входного транзистора соединен с коллектором второго 6 вспомогательного транзистора, первый 8 и второй 9 выходные транзисторы с объединенными базами, эмиттеры которых соединены со вторым 7 источником питания, коллектор первого 8 выходного транзистора связан с базой третьего 10 выходного транзистора и через второй 11 токостабилизирующий двухполюсник соединен с первым 3 источником питания, коллектор второго 9 выходного транзистора связан с выходом устройства и эмиттером третьего 10 выходного транзистора, коллектор которого соединен с первым 3 источником питания. Базы первого 8 и второго 9 выходных транзисторов соединены с коллектором второго 6 вспомогательного транзистора.

На фиг.3, в соответствии с п.2 формулы изобретения, коллектор первого 8 выходного транзистора связан с базой третьего 10 выходного транзистора через первый 12 транзисторный каскад по схеме с общей базой, а коллектор второго 9 выходного транзистора связан с выходом устройства и эмиттером третьего 10 выходного транзистора через второй 13 транзисторный каскад по схеме с общей базой. При этом транзисторные каскады выполнены на основе транзисторов 14 и 15.

Рассмотрим работу схемы, изображенной фиг.2, на постоянном токе.

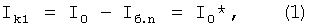

Если принять, что ток общей эмиттерной цепи входного дифференциального каскада 1 на транзисторах 1 и 2 равен 2I0, то токи коллекторов этих транзисторов:

где Iб.n - ток базы входных р-n-р транзисторов 1 и 2, образующих входной дифференциальный каскад.

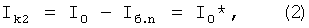

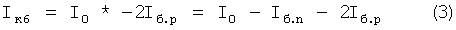

С учетом первого закона Кирхгофа можно найти ток коллектора транзистора 6

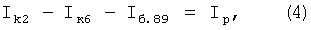

Поэтому сумма токов в узле А

где Iб.89=2Iб.р - суммарный ток базы транзисторов 8 и 9.

Учитывая (1)-(3), из (4) следует, что сумма токов в узле А при его коротком замыкании на эквипотенциальную шину равна нулю, т.е. Iр=0.

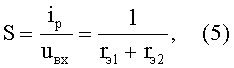

Вследствие воздействия, например, радиации токи Iб,8 и Iб,6 изменяются в несколько раз, но одинаково. В этом случае Iр≈0. Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле А создает Uсм, зависящее от крутизны преобразования входного напряжения uвх ДУ фиг.2 в выходной ток узла А

где rэ1=rэ2 - сопротивления эмиттерных переходов входных

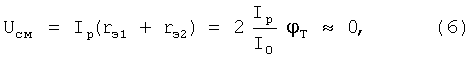

транзисторов дифференциального каскада 1. Поэтому для схем фиг.2

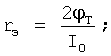

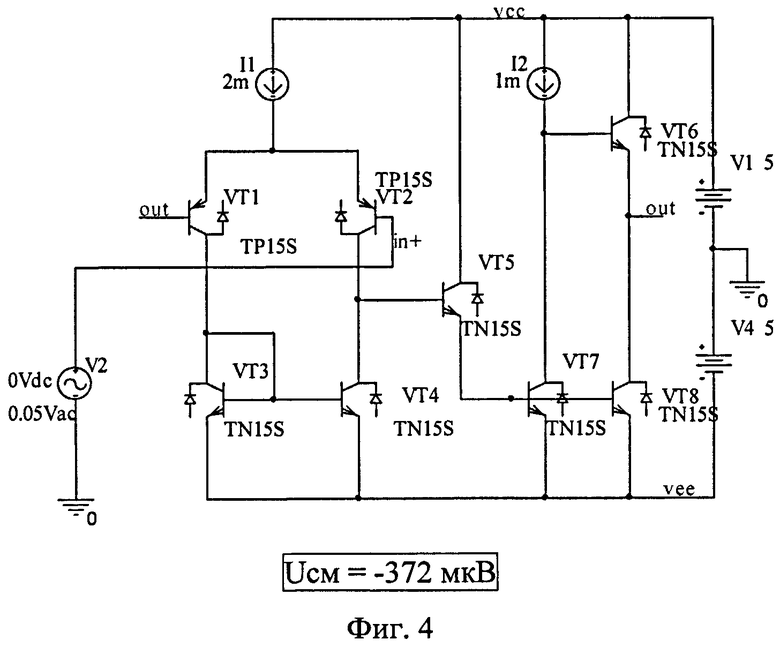

где

φт - температурный потенциал.

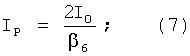

В ДУ-прототипе Iр ≠ 0:

где β6=30÷50 - коэффициент усиления по току базы транзистора 6. Поэтому здесь систематическая составляющая Ucм получается почти на порядок больше (фиг.6, Uсм=-372 мкВ), чем в заявляемой схеме (фиг.6, Uсм=-44 мкВ).

Дальнейшее снижение Uсм обеспечивается в схеме фиг.3, в которой минимизируется влияние напряжения коллектор-база транзисторов 8 и 9 на величину их коэффициента усиления по току базы β. В этой схеме при выборе Eс=1,4 В относительно шины второго 7 источника питания транзисторы 5, 6, 8 и 9 будут работать при одинаковых напряжениях на коллекторе, что обеспечивает равенство β5=β6=β8=β9 и, следовательно, более точную компенсацию токов базы Iб.р транзисторов 6, 8, 9 в узле А.

Таким образом, заявляемое устройство имеет существенное преимущество в сравнении с прототипом.

Источники информации

1. Патент США №4042886.

2. Патент Японии JP 10032437.

3. Патент Японии JP 2005033558.

4. Патент США №4595883, fig.4.

5. Патентная заявка США №2005/0063270А1, fig.2.

6. Патент США №5166638, fig.1.

7. Патент США №5537081, fig.3.

8. Патент США №6114904.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411639C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2412528C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2009 |

|

RU2416154C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2446555C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2010 |

|

RU2421889C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411636C1 |

Изобретение относится к радиотехнике и связи для усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ) с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры). Технический результат: уменьшение Uсм. Дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы (Т), эмиттеры которых связаны друг с другом и подключены к первому (3) источнику питания через первый (4) токостабилизирующий двухполюсник, коллектор первого (1) входного Т соединен с коллектором и базой первого (5) вспомогательного Т и базой второго (6) вспомогательного Т, эмиттеры первого (5) и второго (6) вспомогательных Т связаны со вторым (7) источником питания, коллектор второго (2) входного Т соединен с коллектором второго (6) вспомогательного Т, первый (8) и второй (9) выходные Т с объединенными базами, эмиттеры которых соединены со вторым (7) источником питания, коллектор первого (8) выходного Т связан с базой третьего (10) выходного Т и через второй (11) токостабилизирующий двухполюсник соединен с первым (3) источником питания, коллектор второго (9) выходного Т связан с выходом устройства и эмиттером третьего (10) выходного Т, коллектор которого соединен с первым (3) источником питания. Базы первого (8) и второго (9) выходных Т соединены с коллектором второго (6) вспомогательного Т. 1 з.п. ф-лы, 6 ил.

1. Дифференциальный усилитель с малым напряжением смещения нуля, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых связаны друг с другом и подключены к первому (3) источнику питания через первый (4) токостабилизирующий двухполюсник, коллектор первого (1) входного транзистора соединен с коллектором и базой первого (5) вспомогательного транзистора и базой второго (6) вспомогательного транзистора, эмиттеры первого (5) и второго (6) вспомогательных транзисторов связаны со вторым (7) источником питания, коллектор второго (2) входного транзистора соединен с коллектором второго (6) вспомогательного транзистора, первый (8) и второй (9) выходные транзисторы с объединенными базами, эмиттеры которых соединены со вторым (7) источником питания, коллектор первого (8) выходного транзистора связан с базой третьего (10) выходного транзистора и через второй (11) токостабилизирующий двухполюсник соединен с первым (3) источником питания, коллектор второго (9) выходного транзистора связан с выходом устройства и эмиттером третьего (10) выходного транзистора, коллектор которого соединен с первым (3) источником питания, отличающийся тем, что базы первого (8) и второго (9) выходных транзисторов соединены с коллектором второго (6) вспомогательного транзистора.

2. Дифференциальный усилитель с малым напряжением смещения нуля по п.1, отличающийся тем, что коллектор первого (8) выходного транзистора связан с базой третьего (10) выходного транзистора через первый (12) транзисторный каскад по схеме с общей базой, а коллектор второго (9) выходного транзистора связан с выходом устройства и эмиттером третьего (10) выходного транзистора через второй (13) транзисторный каскад по схеме с общей базой.

| US 5537081 А, 16.07.1996 | |||

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| US 5140281 A, 18.08.1992 | |||

| US 6114904 A, 05.09.2000. | |||

Авторы

Даты

2011-06-10—Публикация

2010-02-24—Подача