Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, ВЧ- и СВЧ-усилителях и т.п.).

В современной микроэлектронике находят применение классические усилители на основе дифференциальных каскадов с двумя токовыми зеркалами. Данная архитектура является основой широкого класса аналоговых интерфейсов современных систем связи и является базовой как для давно существующих, так и для новых, например, SiGe технологий (SG25H2 и др.).

Наиболее близким по технической сущности к заявляемому устройству является дифференциальный усилитель в устройстве по заявке US 2006/0139098 fig.1.

Существенный недостаток известного ДУ, архитектура которого присутствует также во многих других усилительных каскадах [1-12], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еп≤2,0÷2,5 В), его коэффициент усиления по напряжению (Kу) получается небольшим (Kуmax=10÷20). В первую очередь, это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки в выходной цепи токовых зеркал, которые из-за малых Еп не могут выбираться высокоомными.

Основная задача предлагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению Kу при низковольтном питании ДУ.

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными со входами соответствующих первого 4 и второго 5 токовых зеркал, согласованных с первым 6 источником питания, первый 7 двухполюсник нагрузки, первый вывод которого соединен с первым выходом устройства и выходом первого 4 токового зеркала, второй 8 двухполюсник нагрузки, первый вывод которого соединен с выходом второго 5 токового зеркала и вторым выходом устройства, второй источник питания 9, предусмотрены новые элементы и связи - в схему введен первый 10 и второй 11 дополнительные транзисторы, базы которых соединены с источником напряжения смещения потенциалов 12, коллектор первого 10 дополнительного транзистора соединен со входом второго 5 токового зеркала, коллектор второго 11 дополнительного транзистора соединен со входом первого 4 токового зеркала, эмиттер первого 10 дополнительного транзистора связан со вторым выводом первого 7 двухполюсника нагрузки и через первый 13 дополнительный резистор соединен со вторым 9 источником питания, эмиттер второго 11 дополнительного транзистора соединен со вторым выводом второго 8 двухполюсника нагрузки и через второй 14 дополнительный резистор соединен со вторым 9 источником питания.

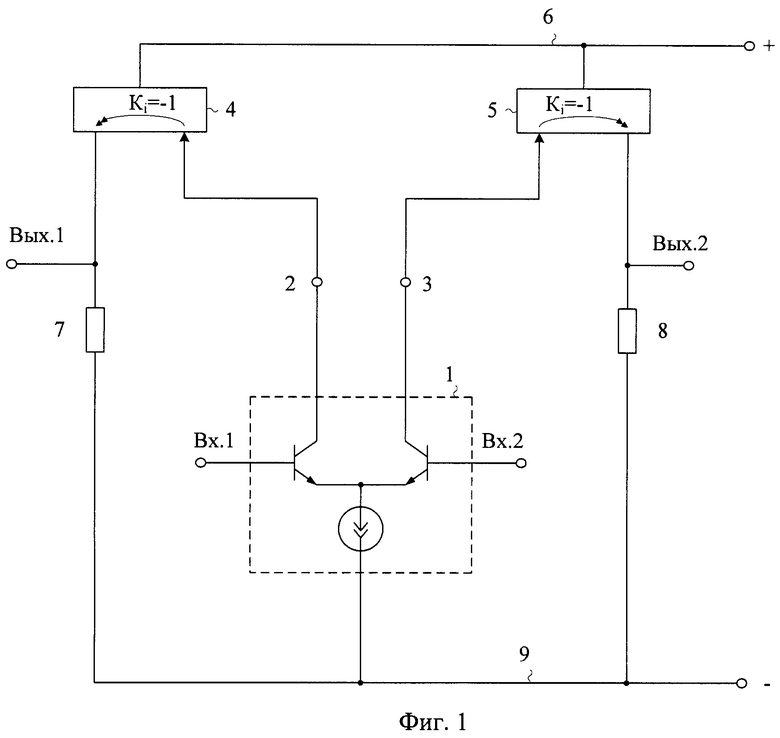

На фиг.1 показана схема ДУ-прототипа.

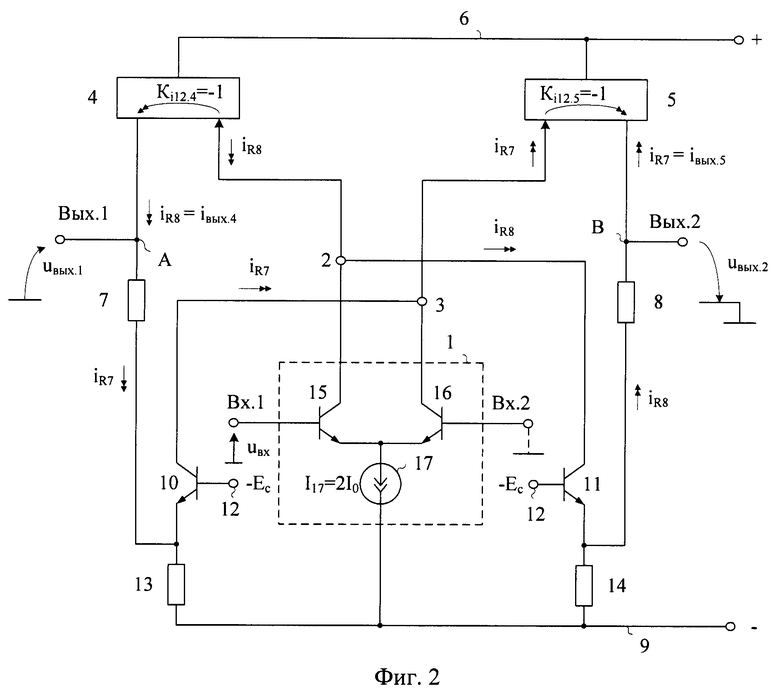

Схема заявляемого устройства, соответствующего формуле изобретения, показана на фиг.2.

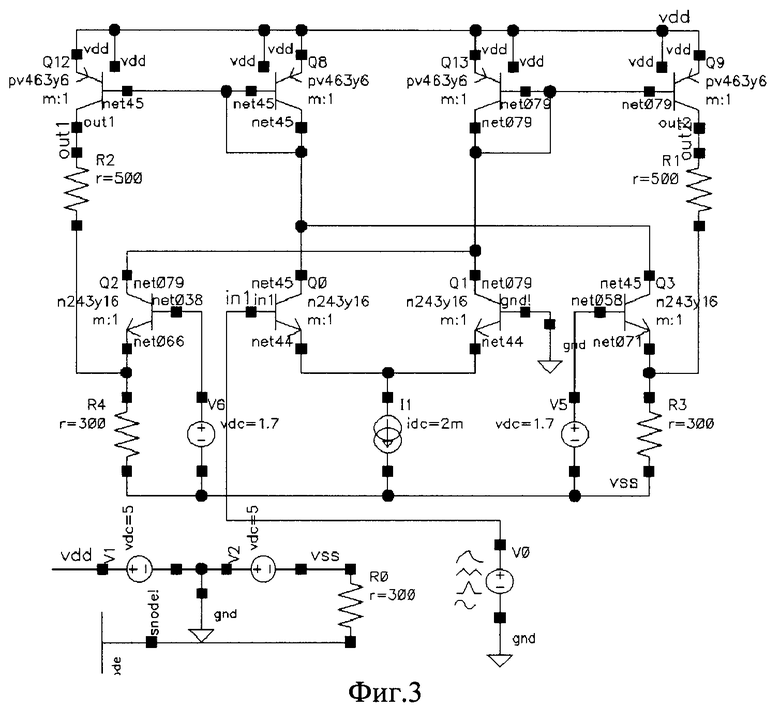

На фиг.3 представлена схема заявляемого ДУ фиг.2 с конкретным выполнением первого 4 и второго 5 токовых зеркал в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW.

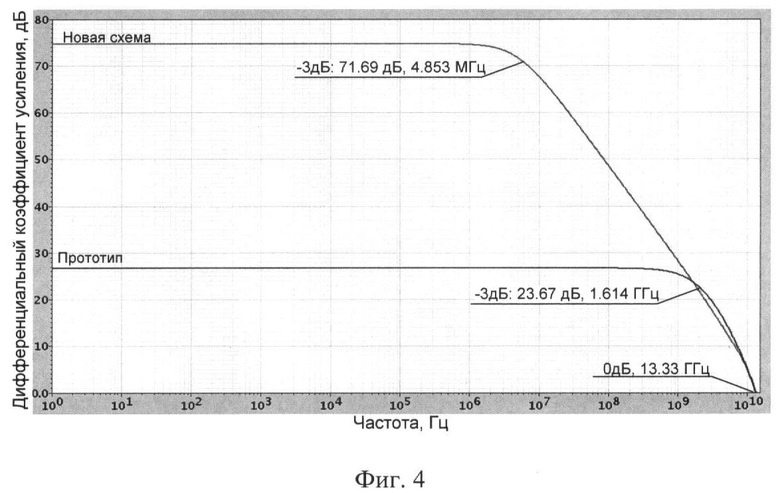

График фиг.4 характеризует частотную зависимость коэффициента усиления по напряжению (Kу) ДУ фиг.3 и. ДУ-прототипа.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными со входами соответствующих первого 4 и второго 5 токовых зеркал, согласованных с первым 6 источником питания, первый 7 двухполюсник нагрузки, первый вывод которого соединен с первым выходом устройства и выходом первого 4 токового зеркала, второй 8 двухполюсник нагрузки, первый вывод которого соединен с выходом второго 5 токового зеркала и вторым выходом устройства, второй источник питания 9. В схему введен первый 10 и второй 11 дополнительные транзисторы, базы которых соединены с источником напряжения смещения потенциалов 12, коллектор первого 10 дополнительного транзистора соединен со входом второго 5 токового зеркала, коллектор второго 11 дополнительного транзистора соединен со входом первого 4 токового зеркала, эмиттер первого 10 дополнительного транзистора связан со вторым выводом первого 7 двухполюсника нагрузки и через первый 13 дополнительный резистор соединен со вторым 9 источником питания, эмиттер второго 11 дополнительного транзистора соединен со вторым выводом второго 8 двухполюсника нагрузки и через второй 14 дополнительный резистор соединен со вторым 9 источником питания.

Статический режим ДУ фиг.2 устанавливается двухполюсником 17, а также резисторами 13, 14 и источником напряжения смещения 12. При необходимости в схему фиг.2 может вводиться общая отрицательная обратная связь по синфазному сигналу.

Рассмотрим работу ДУ фиг.2 при положительном приращении напряжения uвx на первом «Вх.1» входе.

Коэффициент усиления по напряжению ДУ фиг.2 для выхода «Вых.1» определяется, прежде всего, эквивалентным сопротивлением Rэкв.А в цепи выхода Вых.1:

где  - крутизна преобразования входного напряжения uвх ДУ в выходной ток узла «А»;

- крутизна преобразования входного напряжения uвх ДУ в выходной ток узла «А»;

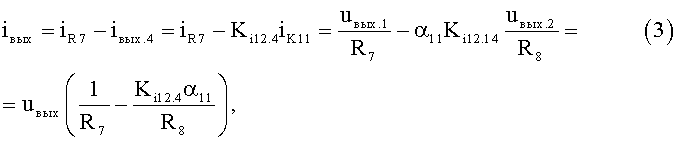

Суммарный ток в цепи выхода Вых.1 с учетом симметрии схемы:

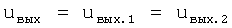

где  - противофазные напряжения на выходах ДУ;

- противофазные напряжения на выходах ДУ;

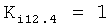

- коэффициент передачи по току первого (4) токового зеркала;

- коэффициент передачи по току первого (4) токового зеркала;

- коэффициент усиления по току эмиттера второго 11 дополнительного транзистора.

- коэффициент усиления по току эмиттера второго 11 дополнительного транзистора.

Таким образом, для ДУ фиг.2:

Из уравнения (4) следует, что при

а также одинаковых

а также одинаковых  , эквивалентное сопротивление в узле «А»

, эквивалентное сопротивление в узле «А»  существенно возрастает и поэтому Ку усилителя фиг.2 увеличивается:

существенно возрастает и поэтому Ку усилителя фиг.2 увеличивается:

Таким образом, в предлагаемой схеме за счет соответствующего выбора резисторов 7 и 8, а также параметра  токовых зеркал 4 и 5 можно получить существенное увеличение коэффициента усиления по напряжению.

токовых зеркал 4 и 5 можно получить существенное увеличение коэффициента усиления по напряжению.

Данные теоретические выводы подтверждаются результатами компьютерного моделирования фиг.4.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

Источники информации

1. Патентная заявка США 2005/0218983 fig.1

2. Патент SU №530425

3. Патент США №6.831.513 fig.4

4. Патентная заявка WO 2002/097974

5. Авт.св. СССР 678641

6. Патент США №6.657.465

7. Патент США №6.882.185 fig.4

8. Патентная заявка США №2003/0132803 fig.4

9. Патент США №4.262.261 fig.10в

10.Патент США №6.538.513

11.Патент США №6.844,781 fig.2

12.Патент Японии JP 53-139453

13.Патент США №4.937.517 fig.2

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419186C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2413356C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2419191C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2010 |

|

RU2432667C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2420864C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444116C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2011 |

|

RU2439783C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2400924C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411640C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2420861C1 |

Изобретение относится к области радиотехники и связи и может быть использовано для усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения: (например, ВЧ- и СВЧ-усилителях и т.п.). Технический результат: повышение предельных значений коэффициента усиления по напряжению Ку при низковольтном питании ДУ. Дифференциальный усилитель содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, связанными со входами соответствующих первого (4) и второго (5) токовых зеркал (ТЗ), согласованных с первым (6) источником питания (ИП), первый (7) двухполюсник нагрузки (ДН), первый вывод которого соединен с первым выходом устройства и выходом первого (4) ТЗ, второй (8) ДН, первый вывод которого соединен с выходом второго (5) ТЗ и вторым выходом устройства, второй ИП (9). В схему введен первый (10) и второй (11) дополнительные транзисторы (Т), базы которых соединены с источником напряжения смещения потенциалов (12), коллектор первого (10) дополнительного Т соединен со входом второго (5) ТЗ, коллектор второго (11) дополнительного Т соединен со входом первого (4) ТЗ, эмиттер первого (10) дополнительного Т связан со вторым, выводом первого (7) ДН и через первый (13) дополнительный резистор соединен со вторым (9) ИП, эмиттер второго (11) дополнительного Т соединен со вторым выводом второго (8) ДН и через второй (14) дополнительный резистор соединен со вторым (9) ИП. 4 ил.

Дифференциальный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, связанными со входами соответствующих первого (4) и второго (5) токовых зеркал, согласованных с первым (6) источником питания, первый (7) двухполюсник нагрузки, первый вывод которого соединен с первым выходом устройства и выходом первого (4) токового зеркала, второй (8) двухполюсник нагрузки, первый вывод которого соединен с выходом второго (5) токового зеркала и вторым выходом устройства, второй источник питания (9), отличающийся тем, что в схему введен первый (10) и второй (11) дополнительные транзисторы, базы которых соединены с источником напряжения смещения потенциалов (12), коллектор первого (10) дополнительного транзистора соединен со входом второго (5) токового зеркала, коллектор второго (11) дополнительного транзистора соединен со входом первого (4) токового зеркала, эмиттер первого (10) дополнительного транзистора связан со вторым выводом первого (7) двухполюсника нагрузки и через первый (13) дополнительный резистор соединен со вторым (9) источником питания, эмиттер второго (11) дополнительного транзистора соединен со вторым выводом второго (8) двухполюсника нагрузки и через второй (14) дополнительный резистор соединен со вторым (9) источником питания.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Дифференциальный усилитель | 1977 |

|

SU678641A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 0 |

|

SU361605A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2011-06-20—Публикация

2010-05-27—Подача