Область, к которой относится изобретение

Варианты осуществления изобретения относятся, в общем, к области обработки информации, а конкретнее к области тактирования в вычислительных системах и микропроцессорах.

Уровень техники

По мере того как все больше функций встраивается в современные микропроцессоры, функциональным блокам в процессоре может потребоваться работать («тактироваться») на разных тактовых частотах, фазах и т.п. С ростом интервалов тактирования в одном и том же процессоре увеличивается сложность во внедрении детерминизма для таких целей, как тестирование. Некоторые методы тестирования могут использовать периодические прерывания для управления системой (ППУС) (PSMI), чтобы пройти по программам, выполняемым на процессоре, и выдать результаты обработки в разных точках в программе.

ППУС представляют собой методологию отладки, посредством которой логический анализатор прослеживает внешнюю шинную активность в кольцевом буфере, тогда как прерывания для управления системой, или ПУС (SMI) генерируются периодически и достаточно часто, чтобы всегда гарантировать, что два последовательных прерывания находятся в буфере логического анализатора. Обработчик ППУС экономит внутреннее состояние процессора для запоминания, позволяя реконструировать значительную часть внутреннего состояния процессора впоследствии на эмуляторе или программной модели процессора, и информация слежения используется для воспроизведения ошибки.

Как правило, ППУС опирается на ресурсы обработки, такие как ресурсы исполнения, синхронизируемые с другими событиями в процессоре, чтобы процессор выдавал детерминистические результаты. Использование методов ППУС становится более трудным, когда число интервалом тактирования возрастает вследствие, например, большего числа функций, встраиваемых в один и тот же процессор.

Сущность изобретения

Технический результат, на достижение которого направлено настоящее изобретение, заключается во внедрении детерминизма в ресурсы исполнения в процессорах, имеющих несколько интервалов тактирования.

Для достижения этого результата предложено устройство для внедрения детерминизма в процессор, имеющий множество интервалов тактирования, содержащее генератор универсальных тактовых импульсов (ГУТИ) для генерирования тактового импульса, общего для множества различных тактовых сигналов, имеющих множество различных частот и фаз; счетчик для подсчета от начального значения до порогового значения на частоте, пропорциональной тактовому импульсу ГУТИ; по меньшей мере, один блок исполнения, подлежащий активации из приостановленного состояния в результате того, что счетчик достиг порогового значения.

В другом варианте осуществления изобретения предложена система для внедрения детерминизма в процессор, содержащая память, включающую в себя программное обеспечение; процессор для выполнения этого программного обеспечения, причем процессор имеет, по меньшей мере, один блок исполнения и множество интервалов тактирования, соответствующих множеству функций; логику для внедрения детерминизма в, по меньшей мере, один блок исполнения по отношению к множеству интервалов тактирования, причем эта логика включает в себя счетчик для счета от начального состояния до порогового состояния со скоростью, соответствующей универсальному тактовому импульсу, а универсальный тактовый импульс синхронизирован с множеством тактовых сигналов от множества интервалов тактирования.

В еще одном варианте осуществления изобретения предложен способ для внедрения детерминизма в процессор, содержащий этапы, на которых инициализируют счетчик в начальное значение; приостанавливают блок исполнения, связанный с этим счетчиком; изменяют значение счетчика со скоростью, пропорциональной частоте сигнала генератора универсальных тактовых импульсов (ГУТИ); активируют блок исполнения после того, как счетчик достигнет порогового значения.

Также предложен машиночитаемый носитель с хранящимся на нем набором команд, который при исполнении компьютером заставляет компьютер выполнять способ, содержащий этапы, на которых исполняют множество команд в блоке исполнения; генерируют сигнал периодических прерываний для управления системой (ППУС) в детерминированной точке множеством команд, причем детерминированная точка является результатом логики детерминизма, приведенной к исполнению в известное состояние по отношению к множеству тактовых сигналов от множества интервалов тактирования, при этом логика детерминизма включает в себя счетчик, чтобы заставить исполнение активироваться из приостановленного состояния, когда счетчик достигнет порогового значения, при этом счетчик должен досчитать до порогового значения со скоростью, пропорциональной универсальному тактовому импульсу, представляющему множество тактовых сигналов от множества интервалов тактирования.

Краткое описание чертежей

Варианты осуществления изобретения иллюстрируются посредством примера, а не путем ограничения, на сопровождающих чертежах, на которых одинаковые ссылочные позиции относятся к аналогичным элементам.

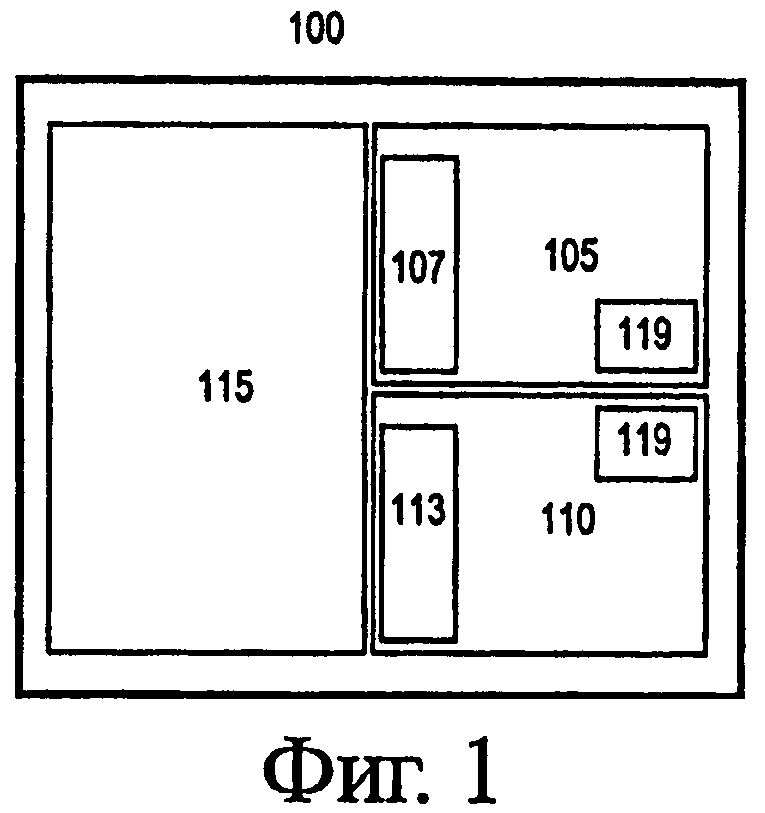

Фиг.1 иллюстрирует блок-схему микропроцессора, в котором можно использовать, по меньшей мере, один вариант осуществления изобретения.

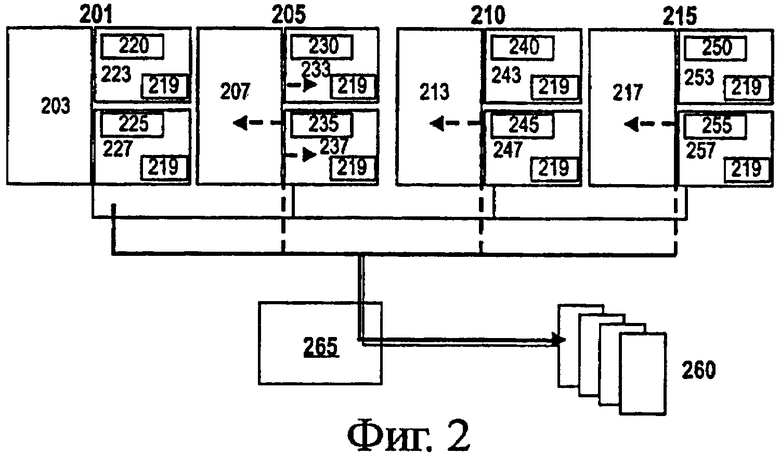

Фиг.2 иллюстрирует блок-схему компьютерной системы с общей шиной, в которой можно использовать, по меньшей мере, один вариант осуществления изобретения.

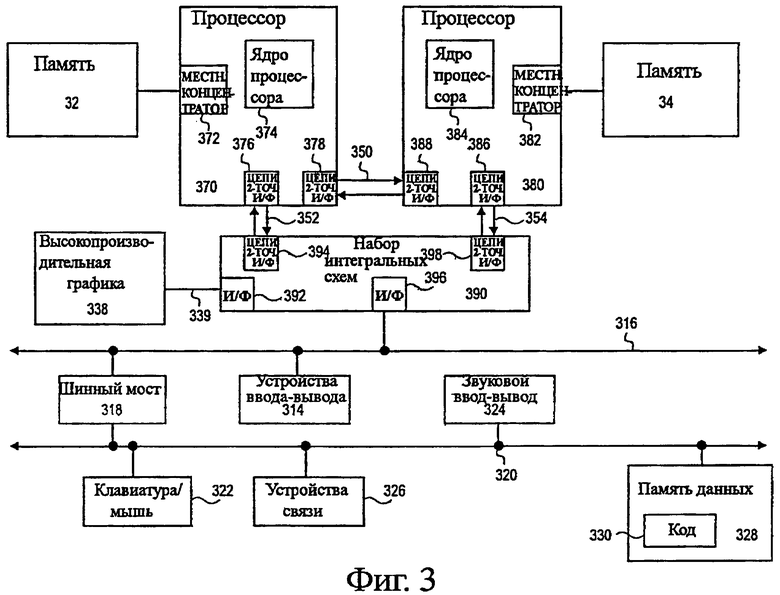

Фиг.3 иллюстрирует блок-схему двухточечной компьютерной системы, в которой можно использовать, по меньшей мере, один вариант осуществления изобретения.

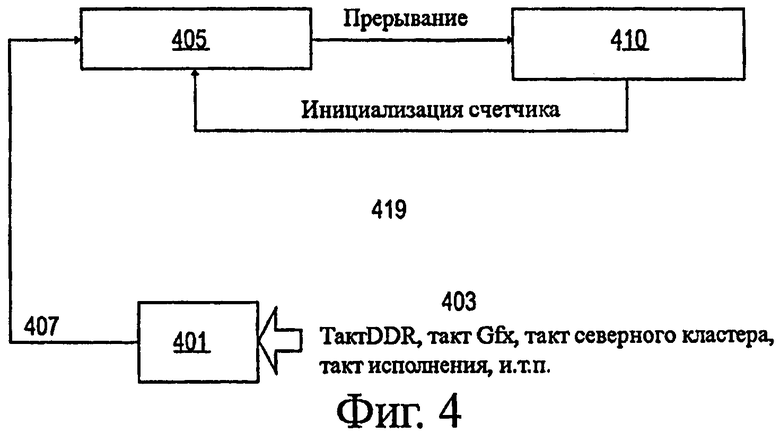

Фиг.4 иллюстрирует блок-схему логики, в которой может быть реализован, по меньшей мере, один вариант осуществления изобретения.

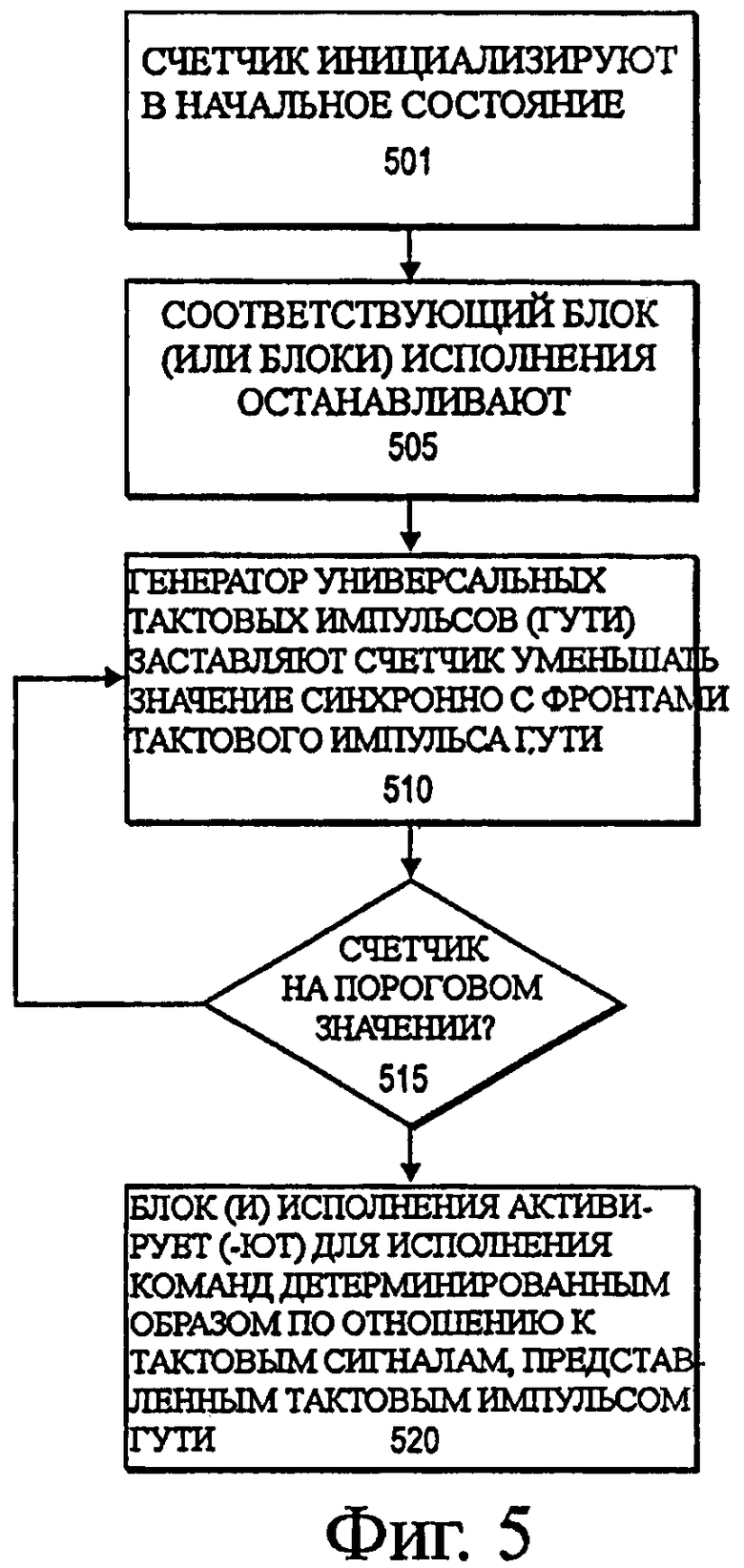

Фиг.5 представляет собой блок-схему операций алгоритма, которые можно использовать для выполнения, по меньшей мере, одного варианта осуществления изобретения.

Подробное описание изобретения

Фиг.1 иллюстрирует микропроцессор, в котором можно использовать, по меньшей мере, один вариант осуществления изобретения. В частности, фиг.1 иллюстрирует микропроцессор 100 с одним или несколькими ядрами 105 и 110, имеющими каждое, по меньшей мере, один периферийный функциональный блок 107 и 113 соответственно. На фиг.1 показан также, по меньшей мере, один периферийный функциональный блок 115, который может выполнять другие операции, не выполняемые функциональными блоками 107 и 113. В одном варианте осуществления функциональные блоки 107, 113 и 115 могут включать в себя такие функции, как графическая обработка, управление памятью и управление периферией, такое как аудио-, видео-, дисковое управление, цифровая обработка сигналов и т.п., в некоторых вариантах осуществления микропроцессор 100 может также включать в себя другую логику, не показанную на фиг.1, такую как управление вводом-выводом. В одном варианте осуществления каждый микропроцессор в многопроцессорной системе или каждое процессорное ядро в многоядерном процессоре может включать в себя или быть иным образом связанным с логикой 119, чтобы обеспечить методы внедрения детерминизма в процессор, имеющий множество интервалов тактирования, в соответствии с, по меньшей мере, одним вариантом осуществления. Эта логика может включать в себя аппаратные схемы для синхронизации одного или нескольких ресурсов исполнения с одним или несколькими часами или событиями в процессоре, согласно одному варианту осуществления. В других вариантах осуществления логика 119 может включать в себя программное обеспечение, чтобы способствовать внедрению детерминизма в ресурсы исполнения в процессорах, имеющих несколько интервалов тактирования. В других вариантах осуществления можно использовать комбинацию аппаратного и программного обеспечения для выполнения описанных здесь методов внедрения детерминизма.

В одном варианте осуществления может быть использована логика внутри или вне интегральной схемы для введения в детерминированное состояние, причем ресурсы исполнения в процессоре имеют множество интервалов тактирования вследствие разнообразных функций в процессоре, чтобы способствовать воплощению, отладке или оптимизации программ, таких как приложения, операционные системы, BIOS, встроенные программы и т.п. Например, в одном варианте осуществления логика 119 включает в себя генератор универсальных тактовых импульсов (ГУТИ) (UCPG) для генерирования общего тактового импульса, сдвинутого от общих тактовых фронтов или событий из нескольких различных тактовых последовательностей с несколькими разными частотами или фазами. В одном варианте осуществления выход ГУТИ используется для изменения состояния счетчика, который при попадании на или выходе за некоторое пороговое значение счета заставляет ресурсы исполнения начинать обработку команд, связанных с подлежащими отладке или оптимизации программами, чтобы способствовать ресурсам исполнения перейти в детерминированное состояние относительно различных тактовых частот в процессоре, как представлено сигналом ГУТИ.

Например, в одном варианте осуществления счетчик инициализируется на начальное значение, а подлежащий синхронизации блок исполнения останавливается. Поскольку фронты сигнала из ГУТИ заставляют счетчик уменьшать (или увеличивать в одном варианте осуществления) значение счета, этот счетчик достигает некоторого порогового значения, такого как нулевое значение, вызывая появление прерывания в блоке исполнения. Блок исполнения затем начинает исполнять команды в детерминированной точке относительно различных тактовых частот в процессоре, который вносит вклад в генерирование сигнала ГУТИ. При исполнении детерминированного состояния относительно различных интервалов тактирования в процессоре обрабатываемый код может отлаживаться или оптимизироваться с помощью таких методов, как ППУС, более надежным образом. В одном варианте осуществления описанные здесь методы могут использоваться в процессоре, имеющем множество процессорных ядер, множество разных функций, таких как графика, управление памятью, управление различными периферийными устройствами (такими как в интегральных процессорах). Описанные здесь методы можно использовать в компьютерных системах, в которых множество функций распределены среди отдельных интегральных схем.

Фиг.2, например, иллюстрирует компьютерную систему с внешней шиной (FSB), в которой можно использовать один вариант осуществления изобретения. Любой процессор 201, 205, 210 или 215 может запрашивать информацию из любой местной сверхоперативной памяти 220, 225, 230, 235, 240, 245, 250, 255 уровня один (L1) внутри одного из ядер 223, 227, 233, 237, 243, 247, 253, 257 процессора или из связанной с ним. Далее, любой процессор 201, 205, 210 или 215 может обращаться к информации из любой из двух совместно используемых сверхоперативных памятей 203,207, 213, 217 уровня два (L2) или из системной памяти 260 через комплект 265 ИС. Один или несколько процессоров на фиг.2 могут включать в себя логику 219 либо могут быть иным образом связаны с нею, чтобы внедрить детерминизм обработки среди множества интервалов тактирования.

В дополнение к компьютерной системе FSB, показанной на фиг.2, иные конфигурации системы можно использовать в сочетании с различными вариантами осуществления изобретения, в том числе одноранговые (Р2Р) коммутационные системы и кольцевые коммутационные системы. Система Р2Р на фиг.3, например, может включать в себя несколько процессоров, из которых только два процессора 370, 380 показаны для примера. Каждый из процессоров 370, 380 может включать в себя местный концентратор 372, 382 контроллера памяти для соединения с памятью 32, 34. Процессоры 370, 280 могут обмениваться данными через двухточечный (PtP) интерфейс 350 с помощью цепей 378, 388 двухточечного интерфейса. Каждый из процессоров 370, 380 может обмениваться данными с набором 390 интегральных схем через отдельные двухточечные интерфейсы 352, 354 с помощью цепей 376, 394, 386, 398 двухточечного интерфейса. Набор 390 интегральных схем может также обмениваться данными с высокопроизводительной графической схемой 338 через интерфейс 339 высокопроизводительной графики. Варианты осуществления изобретения могут располагаться в процессоре с любым числом ядер обработки или в каждом из агентов двухточечной шины по фиг.3. В одном варианте осуществления любое процессорное ядро может включать в себя или может быть иным образом связано с локальной сверхбыстродействующей памятью (не показано). Далее совместно используемая сверхбыстродействующая память (не показано) может быть включена в любой процессор вне обоих процессоров, но при этом все же соединена с этими процессорами через одноранговое соединение, так что информация из локальной сверхбыстродействующей памяти любого из или обоих процессоров может сохраняться в совместно используемой сверхбыстродействующей памяти, если процессор помещен в режим низкого потребления. Один или несколько из процессоров или ядер на фиг.3 могут включать в себя или могут быть иным образом связаны с логикой для внедрения детерминизма исполнения в процессоре или иной интегральной схеме в системе. Эта логика может включать в себя или может быть связана с памятью, такой как один или несколько счетчиков и ГУТИ для переведения ресурсов исполнения в детерминированное состояние, как описано здесь, чтобы помочь отладить или оптимизировать программы с помощью таких методов, как ППУС.

Фиг.4 иллюстрирует логику для выполнения по меньшей мере одного варианта осуществления изобретения. В одном варианте осуществления логика 419 включает в себя ГУТИ 401 для приема нескольких различных тактовых импульсов 403 с несколькими разными (или одной и той же) частотами и (или) фазами и для генерирования общего тактового импульса, частота и фаза которого соответствуют общему состоянию различных тактовых импульсов. Например, в одном варианте осуществления счетчик считает от ненулевого значения вниз до нуля. ГУТИ может реализовать несколько различных методов, чтобы обеспечить генерирование сигнала, который является детерминированным по отношению к нескольким из тактовых сигналов, каждый из которых может находиться не в фазе или иметь отличные частоты. Логика 419 включает в себя также в одном варианте осуществления счетчик 405 для счета от начального значения до порогового значения на частоте, соответствующей выходному сигналу 407 из ГУТИ. Например, в одном варианте осуществления счетчик установлен на ненулевое значение и считает вниз до порогового значения, такого как нулевое значение, тогда как в другом варианте осуществления счетчик инициализирован на некоторое значение, такое как «О», и считает вверх до порогового значения. В одном варианте осуществления счетчик 405 может представлять собой несколько счетчиков, каждый из которых работает совместно или отдельно, чтобы привести один или несколько ресурсов исполнения в детерминированное состояние относительно по меньшей мере двух различных интервалов тактирования.

Когда счетчик достигает порогового значения, это может заставить, по меньшей мере, один блок 410 исполнения прерваться из состояния приостановки и поместить этот, по меньшей мере, один блок исполнения в детерминированное состояние по отношению к тактовому импульсу ГУТИ, благодаря чему блок исполнения приводится в детерминированное состояние относительно тактовых сигналов, представленных тактовым импульсом ГУТИ. С помощью логики 419 методы отладки или оптимизации, такие как ППУС, могут использоваться для помощи программам разработки или отладки, которые выполняются в процессорах, имеющих множество интервалов тактирования.

Фиг.5 иллюстрирует блок-схему операций алгоритма, который можно использовать вместе с, по меньшей мере, одним вариантом осуществления изобретения независимо от конфигурации процессора или системы, в которой этот вариант осуществления используется. В операции 501 счетчик инициализируется в начальное состояние. В одном варианте осуществления начальное состояние представляет значение больше нуля. В операции 505 соответствующий блок (или блоки) исполнения приостанавливается. В операции 510 генератор универсальных тактовых импульсов (ГУТИ) заставляет счетчик уменьшать значение синхронно с фронтами тактового импульса ГУТИ. В другом варианте осуществления импульс ГУТИ заставляет счетчик увеличивать значение. В операции 515, когда счетчик достигает порогового значения, соответствующий(-ие) блок(и) исполнения активирует(-ют) для исполнения команд детерминированным образом по отношению к тактовым сигналам, представленным тактовым импульсом ГУТИ в операции 520. Когда блок(и) исполнения в детерминированном состоянии при синхронизации разных тактовых сигналов в процессоре с тактовым импульсом ГУТИ, методы отладки или оптимизации, такие как ППУС, могут быть использованы для помощи программам отладки или оптимизации, предназначенным для выполнения в процессоре или системе, имеющих множество интервалов тактирования.

Один или несколько объектов, по меньшей мере, одного варианта осуществления могут быть реализованы репрезентативными данными, хранящимися на машиночитаемом носителе, который представляет различную логику в процессоре, которая при ее считывании машиной заставляет логику выполнять описанные здесь методы. Такие представления, известные как «ядра IP», могут сохраняться на вещественном машиночитаемом носителе («ленте») и подаваться разным пользователям или в производственное оборудование для загрузки в технологическое оборудование, которое реально изготавливает логику или процессор.

Таким образом, описаны способ и устройство для управления доступами в микроархитектурную область памяти. Следует понимать, что вышеприведенное описание предназначено для иллюстрации, а не ограничения. Многие другие варианты осуществления станут более понятными специалистам при прочтении и понимании вышеприведенного описания. Объем же изобретения должен поэтому определяться со ссыпкой на приложенную формулу изобретение вместе о объемом эквивалентов, охватываемым такой формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2579140C1 |

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2599971C2 |

| НЕОГРАНИЧЕННАЯ ТРАНЗАКЦИОННАЯ ПАМЯТЬ С ГАРАНТИЯМИ ПРОДВИЖЕНИЯ ПРИ ПЕРЕСЫЛКЕ, ИСПОЛЬЗУЯ АППАРАТНУЮ ГЛОБАЛЬНУЮ БЛОКИРОВКУ | 2014 |

|

RU2597506C2 |

| СХЕМА ОТЛАДКИ, СРАВНИВАЮЩАЯ РЕЖИМ ОБРАБОТКИ НАБОРА КОМАНД ПРОЦЕССОРА | 2007 |

|

RU2429525C2 |

| УСТРОЙСТВО МОНИТОРИНГА ЧАСТИЧНЫХ РАЗРЯДОВ | 2009 |

|

RU2505828C2 |

| МНОГОСКОРОСТНОЙ ПОСЛЕДОВАТЕЛЬНЫЙ ДЕКОДЕР ВИТЕРБИ ДЛЯ ИСПОЛЬЗОВАНИЯ В СИСТЕМЕ МНОГОСТАНЦИОННОГО ДОСТУПА С КОДОВЫМ РАЗДЕЛЕНИЕМ | 1994 |

|

RU2222110C2 |

| СПОСОБ УСТАНОВКИ ПРИЛОЖЕНИЙ, УСТРОЙСТВО-УСТАНОВЩИК И СИСТЕМА, РЕАЛИЗУЮЩИЕ УПОМЯНУТЫЙ СПОСОБ | 2023 |

|

RU2816293C1 |

| УПРАВЛЕНИЕ СИНХРОНИЗАЦИЕЙ ДЛЯ НЕСОГЛАСОВАННОГО ПРИЕМНИКА СИГНАЛА | 2014 |

|

RU2632406C2 |

| УСТРОЙСТВО ДЛЯ КЛАССИФИКАЦИИ НЕЧЕТКИХ СИТУАЦИЙ С РАСШИРЕННЫМ ДИАПАЗОНОМ ДЕЙСТВИЯ | 2014 |

|

RU2579993C1 |

| УСТРОЙСТВА, СИСТЕМЫ И СПОСОБЫ КОНФИГУРИРОВАНИЯ ПРОГРАММИРУЕМОГО ЛОГИЧЕСКОГО КОНТРОЛЛЕРА | 2007 |

|

RU2417391C2 |

Изобретение относится к области обработки информации, а конкретнее к области тактирования в вычислительных системах и микропроцессорах. Техническим результатом является повышение эффективности управления доступами в микроархитектурную область памяти за счет генерирования тактового импульса, общего для множества различных тактовых сигналов, имеющих множество различных частот и фаз. Устройство содержит генератор универсальных тактовых импульсов (ГУТИ) для генерирования тактового импульса, общего для множества различных тактовых сигналов, имеющих множество различных частот и фаз; счетчик для подсчета от начального значения до порогового значения на частоте, пропорциональной тактовому импульсу ГУТИ; по меньшей мере, один блок исполнения, подлежащий активации из приостановленного состояния в результате того, что счетчик достиг порогового значения. 4 н. и 16 з.п. ф-лы, 5 ил.

1. Устройство для внедрения детерминизма в процессор, имеющий множество интервалов тактирования, содержащее: генератор универсальных тактовых импульсов (ТУГИ) для генерирования тактового импульса, общего для множества различных тактовых сигналов, имеющих множество различных частот и фаз; счетчик для подсчета от начального значения до порогового значения на частоте, пропорциональной тактовому импульсу ГУТИ; по меньшей мере, один блок исполнения, подлежащий активации из приостановленного состояния в результате того, что счетчик достиг порогового значения.

2. Устройство по п.1, в котором, по меньшей мере, один блок исполнения должен сбросить счетчик в начальное состояние.

3. Устройство по п.1, в котором начальное значение является ненулевым значением и в котором пороговое значение является нулевым значением.

4. Устройство по п.1, в котором частота тактовых импульсов ГУТИ равна частоте изменения в счете счетчика.

5. Устройство по п.1, в которое дополнительно включены декодер команд, планировщик команд и блок изъятия команд.

6. Система для внедрения детерминизма в процессор, имеющий множество интервалов тактирования, содержащая: память, включающую в себя программное обеспечение; процессор для выполнения этого программного обеспечения, причем процессор имеет, по меньшей мере, один блок исполнения и множество интервалов тактирования, соответствующих множеству функций; логику для внедрения детерминизма в, по меньшей мере, один блок исполнения по отношению к множеству интервалов тактирования, причем эта логика включает в себя счетчик для счета от начального состояния до порогового состояния со скоростью, соответствующей универсальному тактовому импульсу, а универсальный тактовый импульс синхронизирован с множеством тактовых сигналов от множества интервалов тактирования.

7. Система по п.6, содержащая дополнительно логику периодических прерываний для управления системой (ППУС), чтобы помогать в отладке программного обеспечения, причем логика ППУС должна быть синхронизирована с множеством интервалов тактирования согласно логике внедрения детерминизма.

8. Система по п.7, в которой процессор включает в себя центральный процессор, графическое ядро, блок управления памятью и, по меньшей мере, один блок управления периферией.

9. Система по п.8, содержащая дополнительно множество процессоров.

10. Система по п.9, в которой, по меньшей мере, два из множества процессоров имеют множество интервалов тактирования.

11. Способ для внедрения детерминизма в процессор, имеющий множество интервалов тактирования, содержащий этапы, на которых: инициализируют счетчик в начальное значение; приостанавливают блок исполнения, связанный с этим счетчиком; изменяют значение счетчика со скоростью, пропорциональной частоте сигнала генератора универсальных тактовых импульсов (ГУТИ); активируют блок исполнения после того, как счетчик достигнет порогового значения.

12. Способ по п.11, в котором блок исполнения заставляет счетчик перейти на начальное значение.

13. Способ по п.11, в котором сигнал ГУТИ представляет множество тактовых сигналов от множества интервалов тактирования.

14. Способ по п.11, в котором блок исполнения активируют путем генерирования сигнала прерывания после того, как значение счетчика достигнет порогового значения.

15. Способ по п.11, в котором начальное значение счетчика является ненулевым значением, а порогового значение является нулевым значением.

16. Машиночитаемый носитель с хранящимся на нем набором команд, который при исполнении компьютером заставляет компьютер выполнять способ, содержащий этапы, на которых: исполняют множество команд в блоке исполнения; генерируют сигнал периодических прерываний для управления системой (ППУС) в детерминированной точке множеством команд, причем детерминированная точка является результатом логики детерминизма, приведенной к исполнению в известное состояние по отношению к множеству тактовых сигналов от множества интервалов тактирования, при этом логика детерминизма включает в себя счетчик, чтобы заставить исполнение активироваться из приостановленного состояния, когда счетчик достигнет порогового значения, при этом счетчик должен досчитать до порогового значения со скоростью, пропорциональной универсальному тактовому импульсу, представляющему множество тактовых сигналов от множества интервалов тактирования.

17. Машиночитаемый носитель по п.16, в котором начальное значение является значением больше нулевого, а порогового значение является нулем.

18. Машиночитаемый носитель по п.16, в котором начальное значение является нулем, а порогового значение больше нулевого.

19. Машиночитаемый носитель по п.16, в котором блок исполнения связан с процессором интегральной системы.

20. Машиночитаемый носитель по п.19, в котором процессор интегральной системы включает в себя, по меньшей мере, один центральный процессор, графическое ядро, контроллер памяти и, по меньшей мере, один контроллер периферии.

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 6131174 A, 10.10.2000 | |||

| СИНХРОНИЗАЦИЯ РАЗБЛОКИРОВАНИЯ ТАКТОВОГО СИГНАЛА В ЭЛЕКТРОННОМ УСТРОЙСТВЕ | 2003 |

|

RU2281544C2 |

| ТАКТОВЫЙ ГЕНЕРАТОР, В ОСОБЕННОСТИ ДЛЯ USB-ПРИБОРОВ | 2001 |

|

RU2242042C2 |

Авторы

Даты

2011-10-27—Публикация

2009-03-04—Подача