70

Пороз

TJ---Jit-i

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| Декодер сверточного кода | 1984 |

|

SU1319283A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| СПОСОБ НОРМАЛИЗАЦИИ ЗНАЧЕНИЯ МЕТРИКИ КОМПОНЕНТНОГО ДЕКОДЕРА В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2214680C2 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| ДЕКОДЕР ВИТЕРБИ | 1997 |

|

RU2127944C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1725400A1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

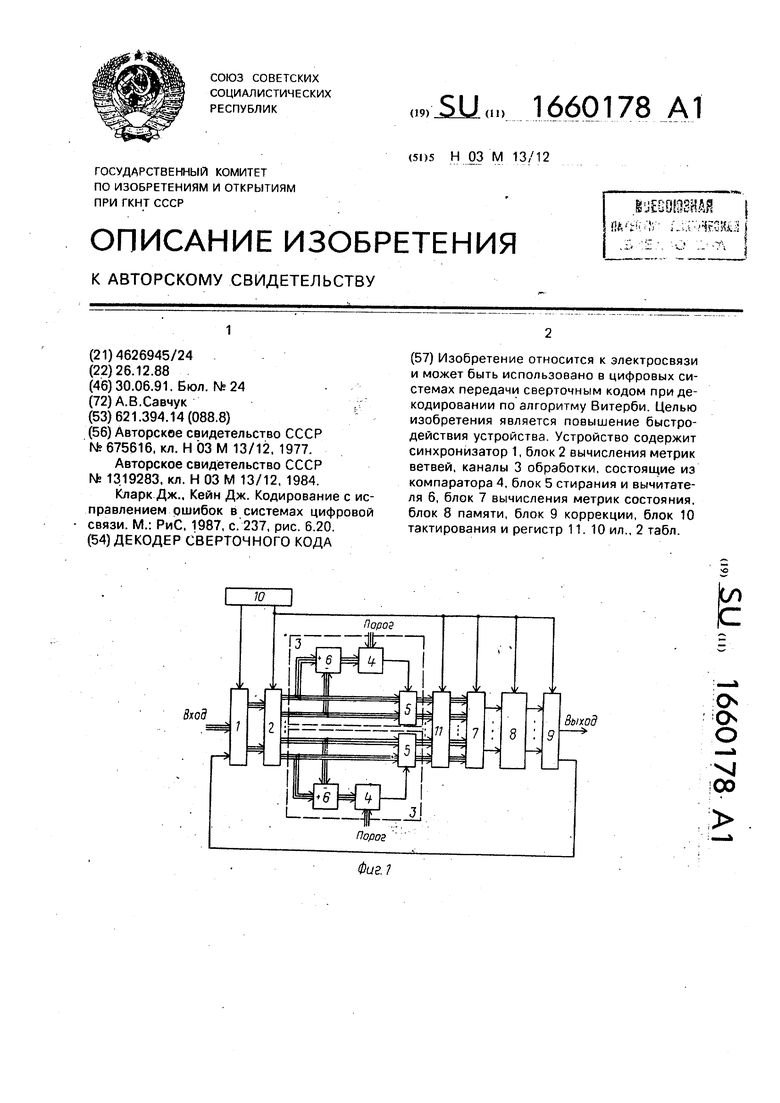

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи сверточным кодом при декодировании по алгоритму Витерби. Целью изобретения является повышение быстродействия устройства. Устройство содержит синхронизатор 1, блок 2 вычисления метрик ветвей, каналы 3 обработки, состоящие из компаратора 4, блока 5 стирания и вычитателя 6, блок 7 вычисления метрик состояния, блок 8 памяти, блок 9 коррекции, блок 10 тактирования и регистр 11. 10 ил.

Выход

о о о

VI 00

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи сверточным кодом при декодировании по алгоритму Витерби.

Целью изобретения является повышение быстродействия устройства.

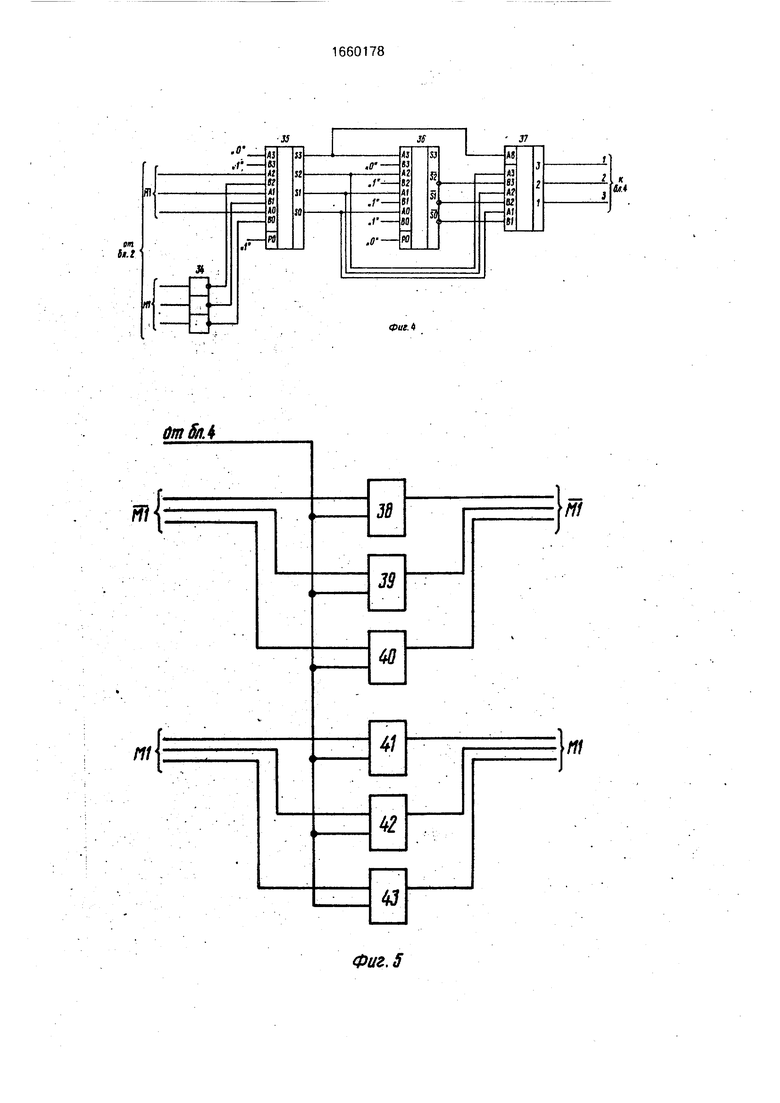

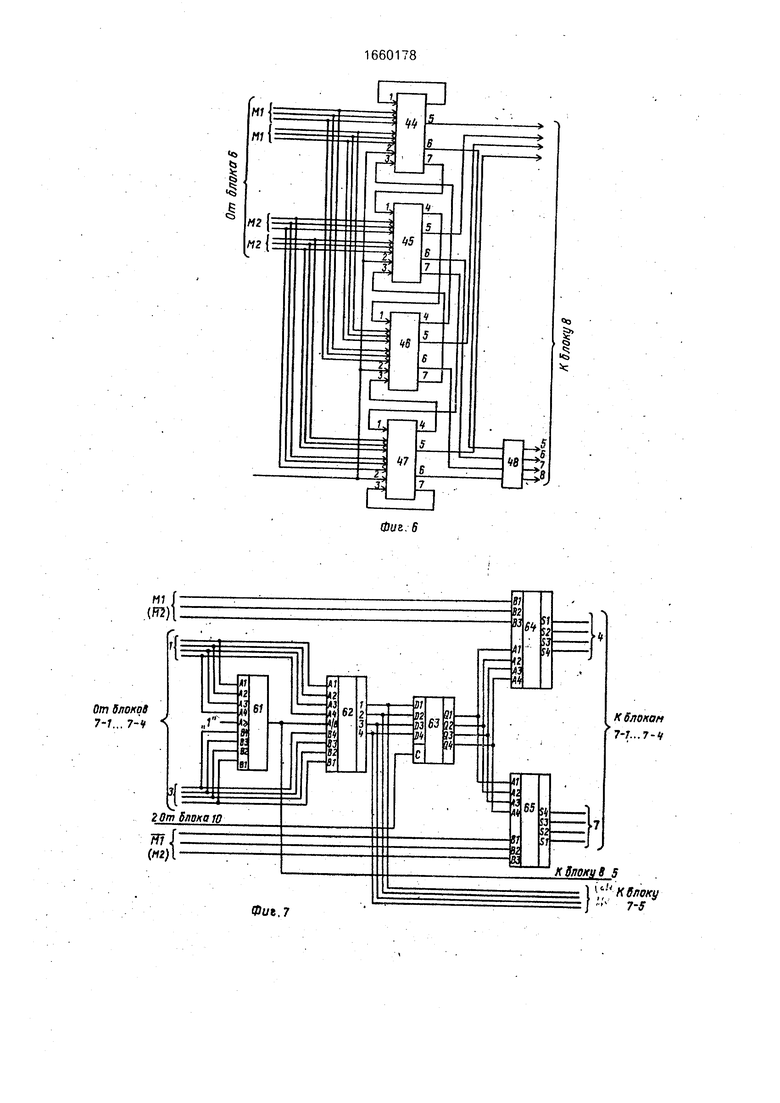

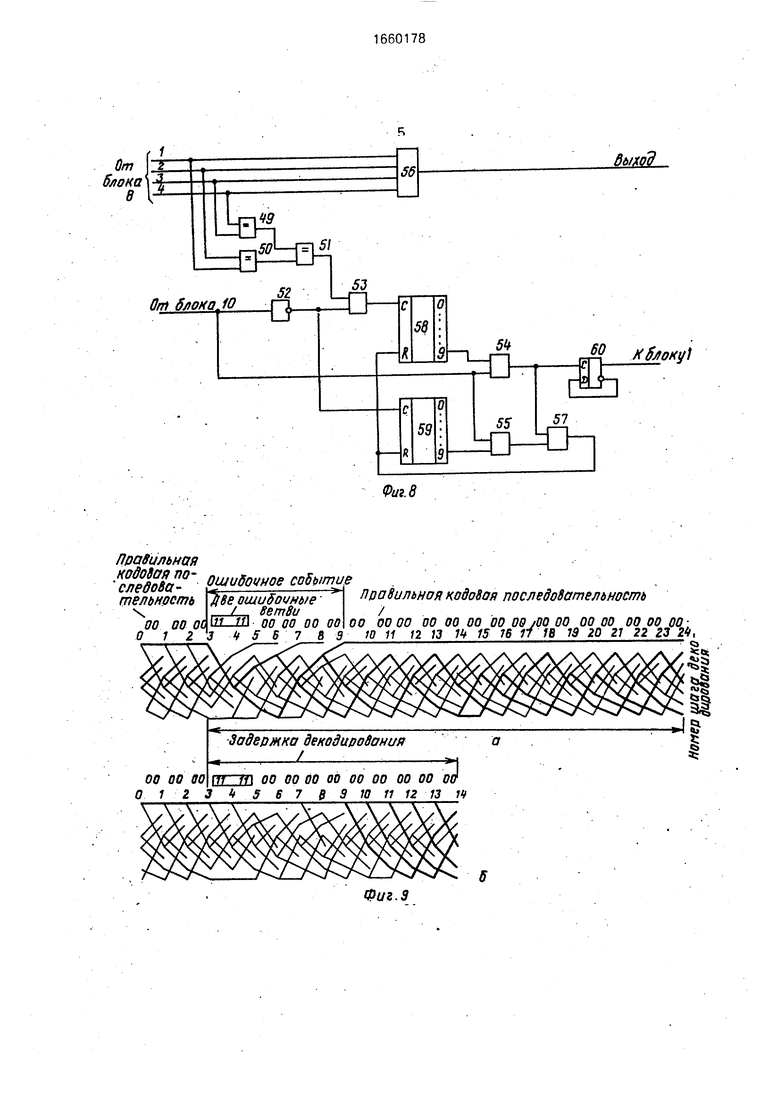

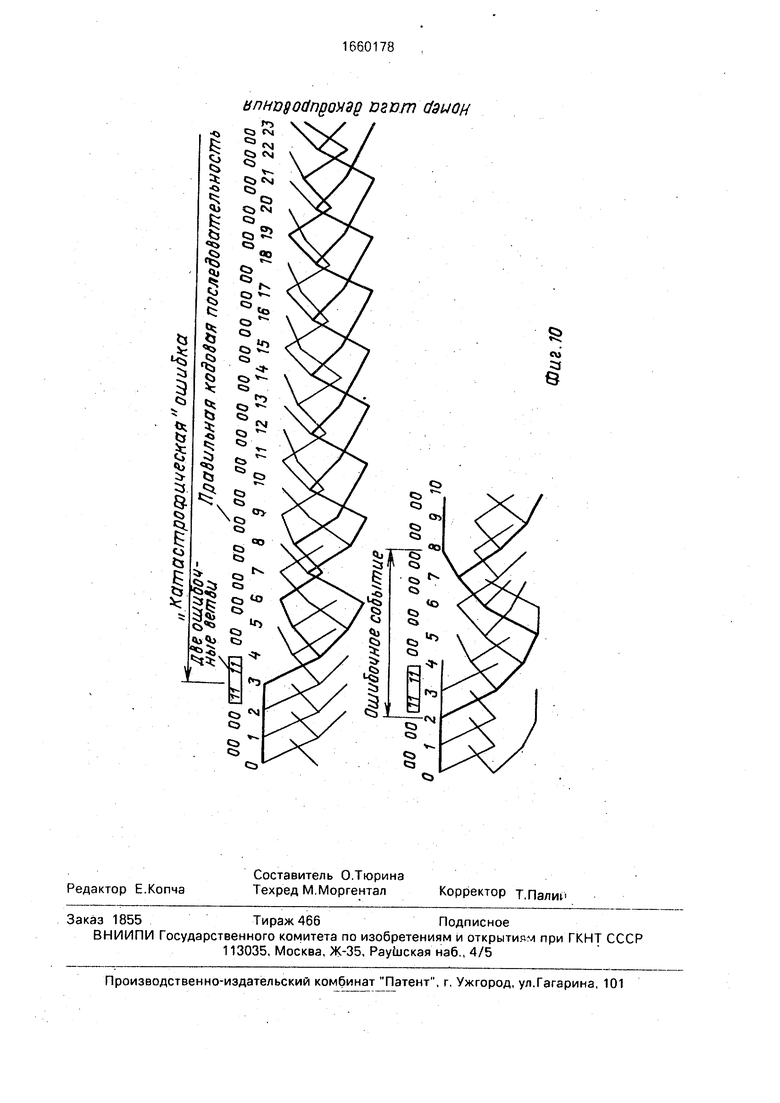

На фиг.1 приведена структурная схема декодера сверточного кода; на фиг. 2 - синхронизатор; на фиг.З - блок вычисления метрик ветвей; на фиг,4 - вычитатель; на фиг.5 - блок сгирания; на фиг.б - блок вычисления Метрики состояния; на фиг.7 - узел сравнения - сложения - выбора; на фиг.8 - блок коррекции (на фиг.2-8 раскрыты отдельные блоки декодера сверточного кода на примере кода со скоростью 1/2 и кодовым ограничением 2); на фиг.9 - графическая иллюстрация процесса декодирования полностью нулевой кодовой последовательности по алгоритму Витерби с помощью известных декодеров (а); то же, но с помощью данного декодера (б); на фиг. 10 - декодирование полностью нулевой последовательности с помощью сокращенного поиска на основе известных принципов (а); то же, но на основе принципа обработки метрик ветвей, предложенных в изобретении (б).

Устройство содержит синхронизатор 1, блок 2 вычисления метрик ветвей, каналы 3 обработки, состоящие из компаратора 4, блока 5 стирания и вычитателя 6, блок 7 вычисления метрик состояния, блок 8 памяти, блок 9 коррекции, блок 10 тактирования и регистр 11.

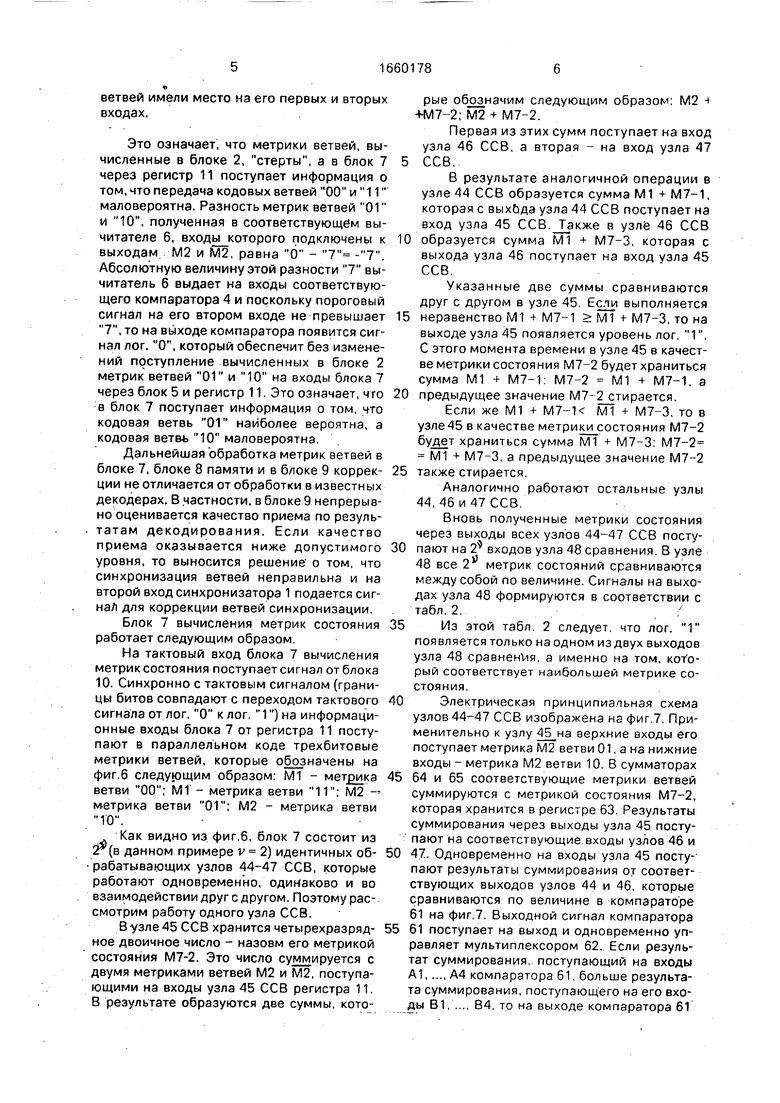

Синхронизатор 1 содержит инвертор 12, ключи 13-24, D-триггеры 25-30.

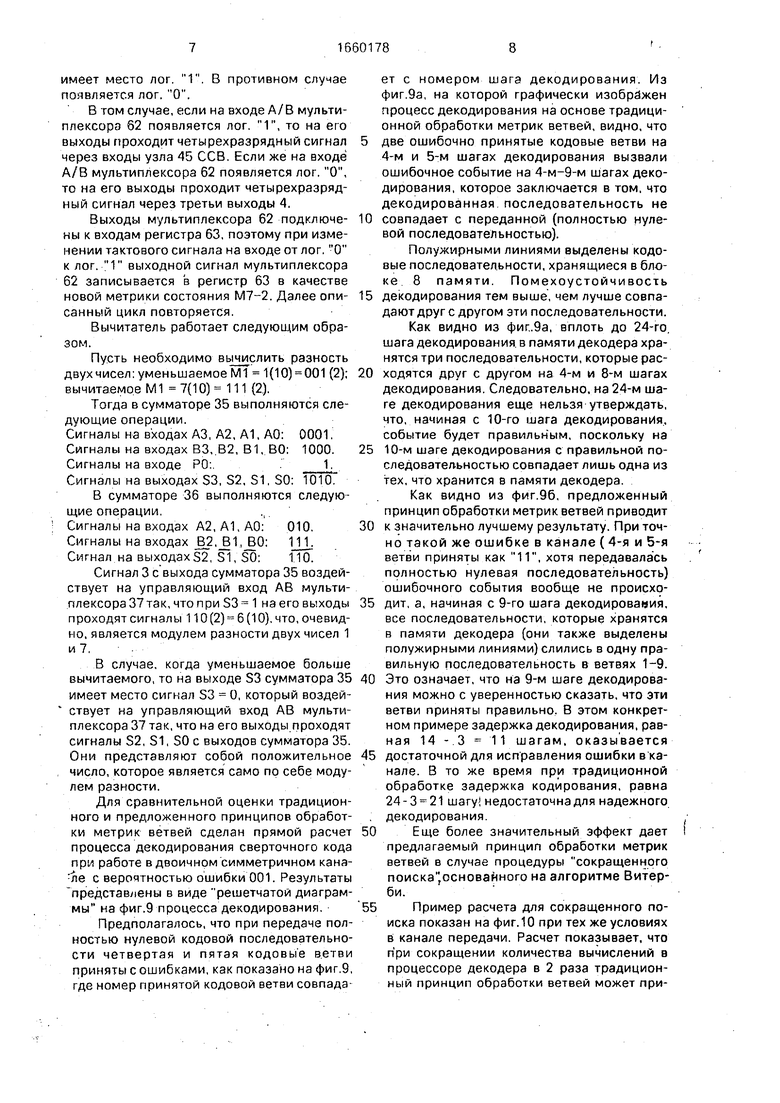

Блок 2 вычисления метрик ветвей содержит регистры 31 и 32 и узел 33 постоянной памяти.

Вычитатель 6 содержит группу 34 инверторов, сумматоры 35 и 36 и мультиплексор 37. .

Блок 5 стирания содержит элементы 38- 43 ИЛИ.

Блок 7 вычисления метрик состояния содержит узлы 44-47 сравнения - сложения - выбора и узел 48 сравнения.

Блок 9 коррекции содержит сумматоры 49-51 по модулю два, инвертор 52, элементы И 53-55, элементы ИЛИ 56 и 57, счетчики 58 и 59 импульсов и D-триггер 60.

Каждый из узлов 44-47 сравнения - сложения - выбора (ССВ) содержит компаратор 61, мультиплексор 62, регистр 63 и сумматоры 64 и 65.

Декодер работает следующим образом. На вход синхронизатора 1 синхронно с тактовым сигналом поступает информационный сигнал, три бита которого представляют собой квантованное значение

одного принятого символа кодовой последовательности. В синхронизаторе f эти квантованные значения группируются попарно - каждая пара трехбитовых сигналов соответствует однйй принятой кодовой ветви.

Так как в непрерывной последовательности трехбитовых сигналов

априори не известны границы кодовых ветвей, то имеются две возможности их групп-и- 15 рования:

Правильная синхронизация ветвей

5

0

5

0

5

0

5

Неправильная синхронизация ветвей

Синхронизатор 1 обесп ечивает правильную синхронизацию ветвей по сигналу, который поступает на его второй вход. Выходные сигналы синхронизатора 1 переписываются в блок 2 вычисления метрик ветвей с тактовой частотой, в два раза меньшей.

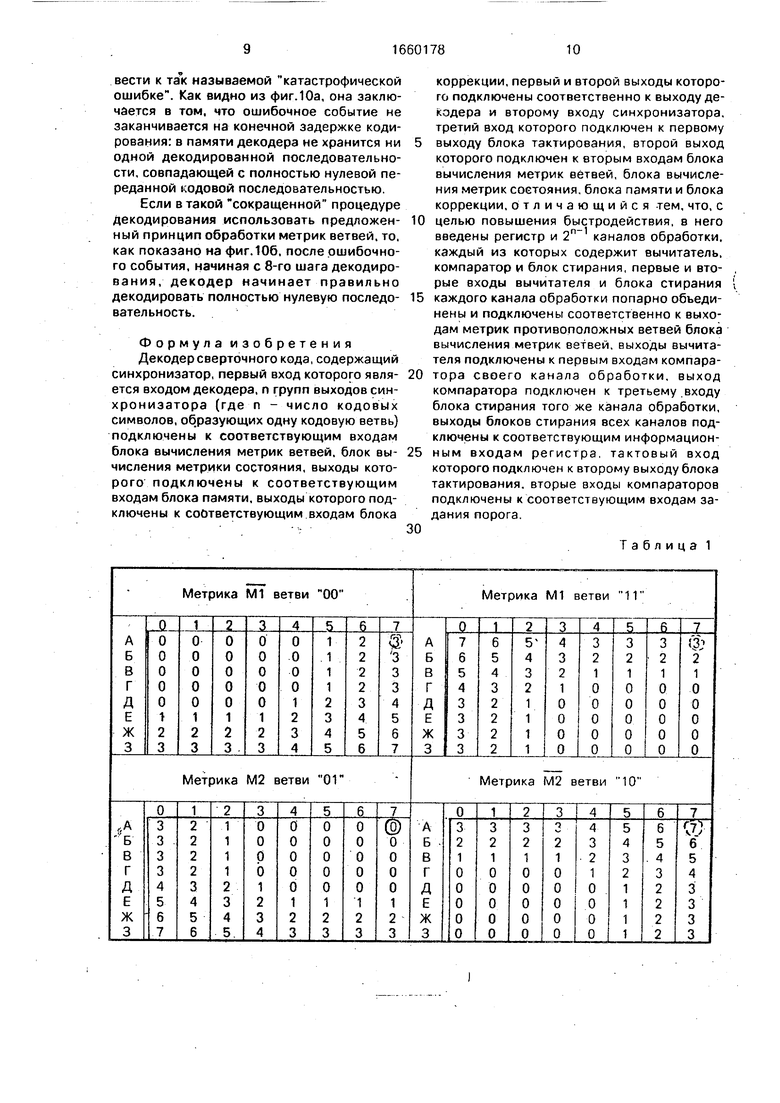

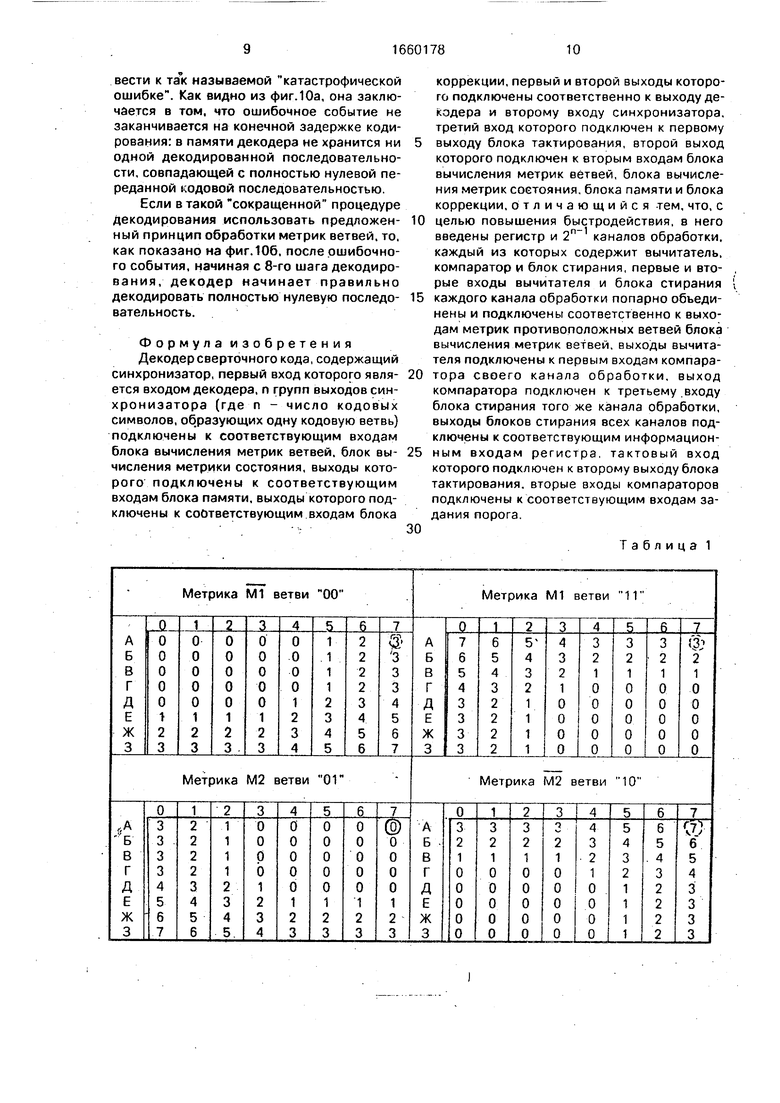

Работу блока 2 поясним с помощью табл 1.

Табл. 1 содержит четыре матрицы, каждая из которых описывает сигналы на одной группе выходов блока 2. В любой позиции матрицы находится десятичный эквивалент трехразрядного двоичного числа, которое появляется на данной группе выходов. Предположим, что принята без ошибок кодовая ветвь 01. Тогда на группе выходов М2 появится метрика ветви 01, которая равна 000 и соответствует позиции А7 в матрице (отмечена в таблице кружком). На группе выходов М2 появится метрика ветви 10, которая равна 111 и соответствует десятичному эквиваленту 7 в той же позиции А7. На группах выходов М1 и М1 противоположных метрик ветви 00 и 11 в тех же позициях А7 появятся равные значения 3, которые являются десятичным эквивалентом числа 011. Когда эти равные значения поступают на входы вычитателя 6. YO на его выходе сигнал будет равен 3 - 3 0. Он подается на первый вход компаратора 4 и, поскольку пороговый сигнал на втором входе компаратора 4 не менее О, то на его выходе появится сигнал лог. 1 и вызовет на обоих-выходах блока 5 сигналы 111 независимо от того, какие значения метрик

ветвей имели место на его первых и вторых входах.

Это означает, что метрики ветвей, вычисленные в блоке 2, стерты, а в блок 7 через регистр 11 поступает информация о том, что передача кодовых ветвей 11 маловероятна. Разность метрик ветвей 01 и 10, полученная в соответствующем вы- читателе 6, входь которого подключены к выходам М2 и М2, равна О - 7 . Абсолютную величину этой разности 7 вы- читатель 6 выдает на входы соответствующего компаратора 4 и поскольку пороговый сигнал на его втором входе не превышает 7, то на выходе компаратора появится сигнал лог. О, который обеспечит без изменений поступление вычисленных в блоке 2 метрик ветвей 01 и 10 на входы блока 7 через блок 5 и регистр 11. Это означает, ч го в блок 7 поступает информация о том, что кодовая ветвь 01 наиболее вероятна, а кодовая ветвь 10 маловероятна.

Дальнейшая обработка метрик ветвей в блоке 7, блоке 8 памяти и в блоке 9 коррекции не отличается от обработки в известных декодерах. В частности, в блоке 9 непрерывно оценивается качество приема по результатам декодирования. Если качество приема оказывается ниже допустимого уровня, то выносится решение о том, что синхронизация ветвей неправильна и на второй вход синхронизатора 1 подается сигнал для коррекции ветвей синхронизации.

Блок 7 вычисления метрик состояния работает следующим образом.

На тактовый вход блока 7 вычисления метрик состояния поступает сигнал от блока 10. Синхронно с тактовым сигналом (границы битов совпадают с переходом тактового сигнала отлог. О к лог. 1) на информационные входы блока 7 от регистра 11 поступают в параллельном коде трехбитовые метрики ветвей, которые обозначены на фиг.6 следующим образом: М1 - метрика ветви М1 - метрика ветви М2 - метрика ветви М2 - метрика ветви 10.

Как видно из фиг.6, блок 7 состоит из 2(в данном примере V 2) идентичных об- рабатывающих узлов 44-47 ССВ, которые работают одновременно, одинаково и во взаимодействии друг с другом. Поэтому рассмотрим работу одного узла ССВ.

В узле 45 ССВ хранится четырехразрядное двоичное число - назовм его метрикой состояния М7-2. Это число суммируется с двумя метриками ветвей М2 и М2, поступающими на входы узла 45 ССВ регистра 11. В результате образуются две суммы, которые обозначим следующим образом: М2 -t -НИ7-2; М2 + М7-2.

Первая из этих сумм поступает на вход узла 46 ССВ, а вторая - на вход узла 47 5 ССВ.

В результате аналогичной операции в узле 44 ССВ образуется сумма М1 + М7-1, которая с выхЬда узла 44 ССВ поступает на вход узла 45 ССВ.Гакже в узле 46 ССВ 10 образуется сумма М1 + М7-3, которая с выхода узла 46 поступает на вход узла 45 ССВ.

Указанные две суммы сравниваются друг с другом в узле 45. Если выполняется 15 неравенство М1 + М7-1 М1 + М7-3, то на выходе узла 45 появляется уровень лог. 1. С этого момента времени в узле 45 в качестве метрики состояния М7-2 будет храниться сумма М1 + М7-1: М7-2 М1 + М7-1, а 0 предыдущее значение М7-2 стирается.

Если же М1 + М7-К М1 + М7-3, то в

узле45 в качестве метрики состояния М7-2

будет храниться сумма М1 + М7-3: М7-2

М1 + М7-3, а предыдущее значение М7-2

5 также стирается.

Аналогично работают остальные узлы 44, 46 и 47 ССВ.

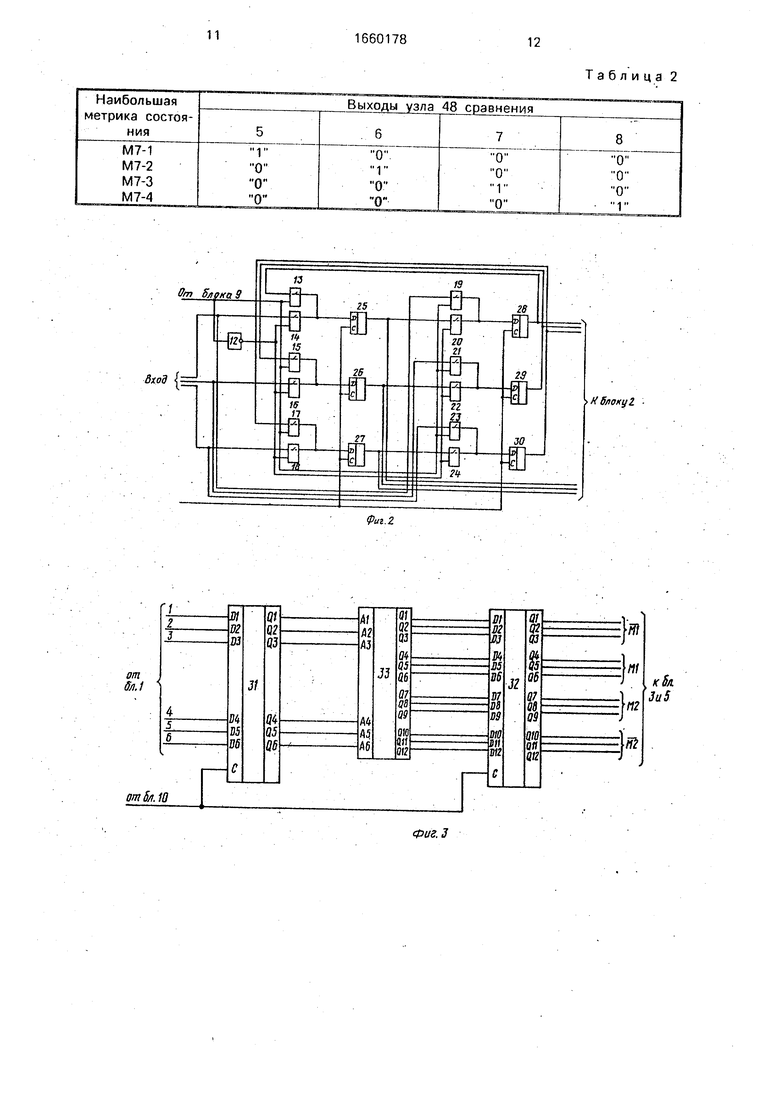

Вновь полученные метрики состояния через выходы всех узлов 44-47 ССВ посту- 0 пают на 2 входов узла 48 сравнения. В узле 48 все 2 метрик состояний сравниваются между собой по величине. Сигналы на выходах узла 48 формируются в соответствии с табл.2./

5Из этой табл. 2 следует, что лог. 1

появляется только на одном из двух выходов узла 48 сравнения, а именно на том, который соответствует наибольшей метрике состояния.

0 Электрическая принципиальная схема узлов 44-47 ССВ изображена на фиг.7. Применительно к узлу 45 на верхние входы его поступает метрика М2 ветви 01, а на нижние входы - метрика М2 ветви 10. В сумматорах 5 64 и 65 соответствующие метрики ветвей суммируются с метрикой состояния М7-2, которая хранится в регистре 63. Результаты суммирования через выходы узла 45 поступают на соответствующие входы узлов 46 и 0 47. Одновременно на входы узла 45 поступают результаты суммирования от соответствующих выходов узлов 44 и 46, которые сравниваются по величине в компараторе 61 на фиг.7. Выходной сигнал компаратора 5 61 поступает на выход и одновременно управляет мультиплексором 62. Если результат суммирования, поступающий на входы А1А4 компаратора 61. больше результата суммирования, поступающего на его входы В1В4. то на выходе компаратора 61

имеет место лог. 1. В противном случае появляется лог. О.

В гом случае, если на входе А/В мультиплексора 62 появляется лог. 1, то на его выходы проходит четырехразрядный сигнал через входы узла 45 ССВ. Если же на входе А/В мультиплексора 62 появляется лог. О, то на его выходы проходит четырехразрядный сигнал через третьи выходы 4.

Выходы мультиплексора 62 подключены к входам регистра 63, поэтому при изменении тактового сигнала на входе от лог. О к лог. 1 выходной сигнал мультиплексора 62 записывается в регистр 63 в качестве новой метрики состояния М7-2. Далее описанный цикл повторяется.

Вычитатель работает следующим образом.

Пусть необходимо вычислить разность двух чисел: уменьшаемое М1 1(10) 001 (2); вычитаемое М1 7(10) 111 (2).

Тогда в сумматоре 35 выполняются следующие операции.

Сигналы на входах A3, А2, А1. АО: 0001. Сигналы на входах ВЗ, В2, В1. ВО: 1000. Сигналы на входе РО.1.

Сигналы на выходах S3, S2, S1. SO: 1010.

В сумматоре 36 выполняются следующие операции.

Сигналы на входах А2,А1,АО: 010, Сигналы на входах JB2,B1,JBO: . Сигнал на выходахS2, S1, SO: 110.

Сигнал 3 с выхода сумматора 35 воздействует на управляющий вход АВ мультиплексора 37 так, что при S3 1 на его выходы проходят сигналы 110 (2) 6 (10), что, очевидно, является модулем разности двух чисел 1 и 7,

В случае, когда уменьшаемое больше вычитаемого, то на выходе S3 сумматора 35 имеет место сигнал S3 0, который воздей- ствует на управляющий вход АВ мультиплексора 37 так, что на его выходы проходят сигналы S2, S1, SO с выходов сумматора 35. Они представляют собой положительное число, которое является само по себе модулем разности.

Для сравнительной оценки традиционного и предложенного принципов обработки метрик ветвей сделан прямой расчет процесса декодирования сверточного кода при работе в двоичном симметричном кана- ле с вероятностью ошибки 001. Результаты представлены в виде решетчатой диаграммы на фиг.9 процесса декодирования.

Предполагалось, что при передаче полностью нулевой кодовой последовательности четвертая и пятая кодовые ветви приняты с ошибками, как показано на фиг.9, где номер принятой кодовой ветви совпада

ет с номером шага декодирования. Из фиг.Эа, на которой графически изображен процесс декодирования на основе традиционной обработки метрик ветвей, видно, что

две ошибочно принятые кодовые ветви на 4-м и 5-м шагах декодирования вызвали ошибочное событие на 4-м-9-м шагах декодирования, которое заключается в том, что декодированная последовательность не

0 совпадает с переданной (полностью нулевой последовательностью).

Полужирными линиями выделены кодовые последовательности, хранящиеся в блоке 8 памяти. Помехоустойчивость

5 декодирования тем выше, чем лучше совпадают друг с другом эти последовательности. Как видно из фиг.Эа, вплоть до 24-го шага декодирования в памяти декодера хранятся три последовательности, которые рас0 ходятся друг с другом на 4-м и 8-м шагах декодирования. Следовательно, на 24-м шаге декодирования еще нельзя утверждать, что, начиная с 10-го шага декодирования, событие будет правильным, поскольку на

5 10-м шаге декодирования с правильной последовательностью совпадает лишь одна из тех, что хранится в памяти декодера.

Как видно из фиг.96, предложенный принцип обработки метрик ветвей приводит

0 к значительно лучшему результату. При точ- но такой же ошибке в канале ( 4-я и 5-я ветви приняты как 11, хотя передавалась полностью нулевая последовательность) ошибочного события вообще не происхо5 дит, а, начиная с 9-го шага декодироваиия, все последовательности, которые хранятся в памяти декодера (они также выделены полужирными линиями) слились в одну правильную последовательность в ветвях 1-9.

0 Это означает, что на 9-м шаге декодирования можно с уверенностью сказать, что эти ветви приняты правильно. В этом конкретном примере задержка декодирования, равная 14-3-11 шагам, оказывается

5 достаточной для исправления ошибки в канале. В то же время при традиционной обработке задержка кодирования, равна 24 - 3 21 шагу недостаточна для надежного декодирования

0 Еще более значительный эффект дает предлагаемый принцип обработки метрик ветвей в случае процедуры сокращенного поиска основайного на алгоритме Витер- би.

5 Пример расчета для сокращенного поиска показан на фиг. 10 при тех же условиях в канале передачи. Расчет показывает, что при сокращении количества вычислений в процессоре декодера в 2 раза традиционный принцип обработки ветвей может привести к так называемой катастрофической ошибке. Как видно из фиг.Юа, она заключается в том, что ошибочное событие не заканчивается на конечной задержке кодирования: в памяти декодера не хранится ни одной декодированной последовательности, совпадающей с полностью нулевой переданной кодовой последовательностью.

Если в такой сокращенной процедуре декодирования использовать предложен- ный принцип обработки метрик ветвей, то. как показано на фиг. 106. после ошибочного события, начиная с 8-го шага декодирования, декодер начинает правильно декодировать полностью нулевую последо- вательность.

Формула изобретения Декодерсверточного кода, содержащий синхронизатор, первый вход которого явля- ется входом декодера, п групп выходов синхронизатора (где п - число кодовых символов, образующих одну кодовую ветвь) подключены к соответствующим входам блока вычисления метрик ветвей, блок вы- числения метрики состояния, выходы которого подключены к соответствующим входам блока памяти, выходы которого подключены к соответствующим входам блока

коррекции, первый и второй выходы которого подключены соответственно к выходу декодера и второму входу синхронизатора, третий вход которого подключен к первому выходу блока тактирования, второй выход которого подключен к вторым входам блока вычисления метрик ветвей, блока вычисления метрик состояния, блока памяти и блока коррекции, отличающийся тем, что, с целью повышения быстродействия, в него введены регистр и 2П каналов обработки, каждый из которых содержит вычитатель, компаратор и блок стирания, первые и вторые входы вычитателя и блока стирания каждого канала обработки попарно объединены и подключены соответственно к выходам метрик противоположных ветвей блока вычисления метрик ветвей, выходы вычитателя подключены к первым входам компаратора своего канала обработки, выход компаратора подключен к третьему входу блока стирания того же канала обработки, выходы блоков стирания всех каналов подключены к соответствующим информационным входам регистра, тактовый вход которого подключен к второму выходу блока тактирования, вторые входы компараторов подключены к соответствующим входам задания порога.

Таблица 1

Таблица 2

К блоку I

. .Гя

а

en

ь.г

.1

бт5п.Ь

т

t

М

3S

37

и

и

а

В1

-А

к

At S

J5

/

41

Фиг. 5

«о

1

I

ж{; (W)l

(

E

I42

Jrr .. 6/

2gm Блокам

m

(m)

Фиг. 7

«Jo

I

62

63

к блоком

7-7...7-Ч

К ВпокуВ 5

К блоку 7-5

:)

От блока В

Правильная

PMtoMQ событие

следоВа- тельность оо оо 04

О 1 2

7}бе ouiuSovfttte . / . ffemft/

Ш ,Ш 00 00 00 00

Правильной кодоЗоя последовательность

/

00 00 00 00 00 00 00 00/00 00 00 00 00 00 00

uj.-ш ци ии ии vu ии ии ии ии ча ии ии ии /w ии ии ии ии оо аи 3 5 В 7 В 9 W 11 12 13 15 76 17 1В 19 20 21 22 23 24,

Задержка декодиробания /

00 00 00

Iff /У1 00 00 00 00 00 00 00 00 (7,

3

О 1 2 3 « 5 б 7 В 9 10 11 12 13 14

дыход

ff К блоку

Правильной кодоЗоя последовательность

/

00 00 00 00 00 00 00 00/00 00 00 00 00 00 00

ии ии ии ии ча ии ии ии /w ии ии ии ии оо аи W 11 12 13 15 76 17 1В 19 20 21 22 23 24

,

3

I

Фиг.З

ипнъдоапдондд osem cfsuon

§

ew

5J

S

| Устройство для декодирования сверточного кода | 1977 |

|

SU675616A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Декодер сверточного кода | 1984 |

|

SU1319283A1 |

| Кларк Дж., Кейн Дж | |||

| Кодирование с исправлением ошибок в системах цифровой связи | |||

| М.: РиС, 1987, с | |||

| Прибор для корчевания пней | 1921 |

|

SU237A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-30—Публикация

1988-12-26—Подача