Настоящее изобретение относится к спутниковой навигационной системе или системе позиционирования, включающей группировку (созвездие) из множества спутников, более точно, к приемнику, применимому в такой спутниковой навигационной системе.

Спутниковые навигационные системы играют все более важную роль в разнообразных областях применения, включая портативные устройства для определения местоположения, бортовые навигационные системы автомобилей и т.д. Основной спутниковой навигационной системой, используемой в настоящее время, является глобальная система позиционирования (GPS, от английского - global positioning system), управляемая министерством обороны США. К 2003 г. объем продаж оборудования GPS в мире составил около 3,5 миллиардов долларов, и ожидается, что он будет устойчиво расти в течение ближайших нескольких лет. Предполагается, что в конце этого десятилетия будет введен в действие европейский аналог спутниковой навигационной системы под названием "Галилео" (Galileo).

Спутниковая навигационная система состоит из группировки спутников, каждый из которых передает на землю один или несколько сигналов. Основной составляющей сигнала спутника является так называемый расширяющий код (кодовая последовательность, применяемая для расширения спектра сигнала), также именуемый кодом позиционирования, синхронизации или определения дальности, который объединяют с навигационной информацией. Затем полученное сочетание используют для модулирования несущей на заданной частоте для передачи на землю. Обычно каждый спутник осуществляет передачу на множестве частот, что помогает компенсировать влияние ионосферы, повысить точность и увеличить объем передаваемых данных.

В некоторых случаях множеством сигналов могут модулировать одну несущую с использованием соответствующей схемы уплотнения. Например, предполагается, что некоторые сигналы системы Galileo будут передаваться по каналу передачи данных, объединенному с пилотным каналом. Пилотный канал содержит только расширяющий код, но не содержит навигационной информации, тогда как канал передачи данных содержит как расширяющий код, так и навигационную информацию.

Расширяющий код сигнала спутника обычно представляет собой заданную последовательность простейших элементов или элементарных посылок кода (далее также именуемых "импульсами") и служит для решения двух основных задач. Во-первых, расширяющий код обеспечивает механизм установления синхронизации и доступа (CDMA, коллективный доступ с кодовым разделением каналов, от английского - code division multiple access), позволяющий приемнику захватить сигнал спутника. За счет этого каждый спутник (и обычно каждый сигнал, передаваемый таким спутником) имеет собственный код синхронизации. При первом включении приемника неизвестно, сигналы каких спутников могут быть приняты, поскольку некоторые спутники, входящие в группировку, находятся ниже горизонта для данного конкретного местоположения в данное конкретное время. Приемник использует коды синхронизации для захвата сигнала, поступающего от первого спутника. После этого может быть осуществлен доступ к навигационной информации, содержащейся в сигнале.

Впоследствии она служит справочной информацией для других спутников группировки и позволяет относительно быстро обнаруживать остальные видимые для приемника спутники.

Во многих спутниках применяется двухстадийный процесс вхождения в синхронизм. На первой стадии приемник осуществляет одновременную корреляцию входного сигнала и набора расширяющих кодов спутников. В частности, приемник осуществляет поиск расширяющего кода любого спутника с поправкой на любую возможную ошибку синхронизации спутника и приемника и на любой возможный доплеровский сдвиг спутника и приемника (который зависит от перемещения спутника в космическом пространстве относительно пользователя). Если установлено, что корреляционное значение превышает заданный порог, осуществляют вторую стадию, предусматривающую более подробный анализ соответствующего сочетания расширяющего кода спутника, ошибки синхронизации и доплеровского сдвига. Этот осуществляемый на второй стадии анализ позволяет проверить и подтвердить или при необходимости отклонить грубое вхождение в синхронизм.

Второй основной задачей расширяющего кода является вычисление расстояния от спутника до приемника, исходя из времени прохождения сигнала от спутника до приемника. После этого методом трилатерации определяют местоположение приемника в трехмерном пространстве при условии, что известны местоположения спутников (указанные в навигационной информации, принимаемой от спутников). Теоретически трилатерация может быть осуществлена с использованием параметров сигналов как минимум трех спутников, если предположить, что известна ошибка синхронизации приемника и спутника. Поскольку на практике эта ошибка синхронизации обычно не известна, не считая специальных приемников, с целью компенсации неизвестной ошибки синхронизации приемника получают параметры сигнала по меньшей мере одного дополнительного спутника. При наличии доступных сигналов дополнительных спутников может быть определено местоположение на основании статистических данных с использованием любого соответствующего алгоритма, такого как алгоритм наименьших квадратов. При этом также может быть получено определенное показание ошибки, связанной с расчетным местоположением.

Важным параметром расширяющего кода является скорость передачи его импульсов, поскольку это, в свою очередь, влияет на точность, с которой может осуществляться определение местоположения. Другим важным параметром расширяющего кода является его общая длина, иными словами, число импульсов расширяющего кода до его повторения. Одной из причин этого является тот факт, что расширяющий код конечной длины способен вызвать неоднозначность при определении местоположения. При большей длине расширяющего кода такая неоднозначность ослабляется, а также обеспечивается лучшее разделение сигналов, поступающих из различных источников, и повышается их устойчивость к помехам. В тоже время при более длинном периоде повторения расширяющего кода может быть задержано вхождение в синхронизм с сигналом, а также требуется наличие у приемника большей способности к обработке данных. Как правило, длина расширяющего кода также влияет на скорость передачи данных, применимую для передачи навигационных данных, поскольку на каждую полную последовательность расширяющего кода обычно приходится только один бит (наименьшую единицу информации) навигационных данных. В связи с этим, чем длиннее период повторения расширяющего кода, тем ниже скорость передачи битов навигационных данных.

Известен способ решения данной задачи, который заключается в использовании иерархического расширяющего кода, включающего первичный и вторичный коды. Если допустить, что первичный код содержит N1 импульсов (элементов), а вторичный код содержит N2 импульсов, первые N1 импульсы всего расширяющего кода соответствуют первичной последовательности исключающее ИЛИ с первым импульсом вторичного кода, следующие N1 импульсы расширяющего кода представляют собой повтор N1 импульсов первичного кода, на это раз исключающее ИЛИ со вторым импульсом вторичного кода и так далее. В результате получаем общий период повторения кода, равный N1×N2, однако, вхождение в синхронизм может осуществляться на основе только первичного кода.

Расширяющие коды GPS реализованы с использованием линейных регистров сдвига с обратными связями (ЛРСОС), в которых выбранные выходные сигналы n-разрядного сдвигового регистра отводят и снова подают на вход. Обратные связи в ЛРСОС можно отобразить в виде многочлена N-го порядка, при этом действие ЛРСОС может быть полностью задано его многочленом и начальной установкой ЛРСОС.

В качестве расширяющих кодов GPS используют золотые коды, которые обладают некоторыми особыми математическими свойствами. Одно из них состоит в том, что они генерируют выходной сигнал псевдослучайного шума (PRN, от английского - pseudo-random noise) с периодом повторения 2N-1, за счет чего относительно компактный ЛРСОС способен генерировать выходной сигнал с большим периодом повторения. Золотые коды также обладают хорошими автокорреляционными свойствами, что способствует вхождению в синхронизм по кодовой комбинации и точности определения местоположения. В частности, автокорреляционная функция имеет четко выраженный пик при нулевом временном сдвиге и относительно небольшой пик при всех остальных (т.е. не нулевых) временных сдвигах. В тоже время важно выбрать набор золотых кодов с хорошими взаимными корреляционными свойствами, при которых взаимная корреляционная функция различных кодов остается относительно слабой. Это важно для установления синхронизации с сигналом, поскольку помогает предотвращать случайное принятие кода синхронизации одного спутника за код синхронизации другого спутника. Дополнительным важным практическим критерием выбора расширяющего кода является наличие равного (или почти равного) числа единиц и нолей, что известно как симметричный код.

Дополнительную информацию о спутниковых навигационных системах можно почерпнуть из книги Misra и Enge под названием "Global Positioning System: Signals, Measurements and Performance", издательство Ganga-Jamuna Press, 2001 г., ISBN 0-9709544-0-9; книги Bradford W. Parkinson и James J. Spilker Jr под названием "Global Positioning System: Theory and Applications", тома 1, 2, ISBN 1-56347-106-Х, публикация Американского института аэронавтики и астронавтики; работы Hollreiser и др. под названием "Galileo User Segment Overview", стр.1914-1928, ION GPS/GNSS 2003, сентябрь 2003 г. Портленд, штат Орегон; и работы Hollreiser и др. под названием "Galileo Test User Segment - First Achievements and Application", GPS World, июль 2005 г.

Несмотря на то, что использование золотых кодов в существующих спутниковых навигационных системах хорошо известно, такие коды имеют ряд недостатков. Например, они доступны только при определенной длине кода (2N-1, при этом в многочлене ЛРСОС могут использоваться не все значения N). Обычно длина кода задана соотношением между скоростью передачи импульсов расширяющего кода и скоростью передачи битов навигационной информации. Если длина кода ограничена длиной доступного золотого кода, это подразумевает ограничение скорости передачи импульсов и скорости передачи битов, что, в свою очередь, влияет на другие параметры, такие как время установления синхронизации и точность определения местоположения. В некоторых случаях ограничение длины кода длиной золотых кодов преодолевают за счет использования усеченных золотых кодов, но это усечение отрицательно сказывается на математических свойствах кодового набора (с точки зрения автокорреляционной функции и т.д.).

Соответственно, в заявках РСТ/ЕР2004/014488 и РСТ/ЕР2005/007235 предложено использовать в качестве спутниковых расширяющих кодов заказные последовательности символов. За счет этого можно создавать расширяющие коды произвольной длины, а также оптимизировать различные свойства, такие как автокорреляция и взаимная корреляция независимо от других ограничений. Такой расширяющий код в дальнейшем именуется в описании кодом "с памятью", поскольку обычно в приемнике хранится вся комбинация элементарных посылок (сигналов) кода. В этом состоит отличие от генерации комбинации элементарных посылок алгоритмическим способом, как в случае золотого кода, в котором для генерации кода алгоритмическим способом в соответствии с его многочленом используют ЛРСОС, а не хранят комбинацию элементарных посылок всего кода. Следует отметить, что, поскольку коды с памятью, как правило, создают из последовательностей (псевдо)случайных чисел, обычно к ним неприменимы методы сжатия данных.

Набор кодов с памятью для приемника может храниться в ПЗУ какого-либо типа, таком как флэш-память. Затем во время начальной загрузки эти коды могут быть загружены в набор микросхем приемника для использования при обнаружении расширяющих кодов во входных сигналах спутников. Если в сам набор микросхем приемника загружают полные коды с памятью, это может привести к очень существенной непроизводительной нагрузке на ячейки памяти в наборе микросхем приемника. В качестве альтернативы коды могут быть загружены во внешнее (по отношению к набору микросхем приемника) ОЗУ, и в этом случае потребуется лишь сравнительно небольшое увеличение общих потребностей в памяти для хранения программ и(или) данных для обычной работы приемника. Тем не менее в этом случае вероятно потребуется специализированный высокоскоростной интерфейс для загрузки в реальном времени кодов из ОЗУ в набор микросхем приемника, а также некоторая дополнительная внутренняя буферизация в самом наборе микросхем приемника.

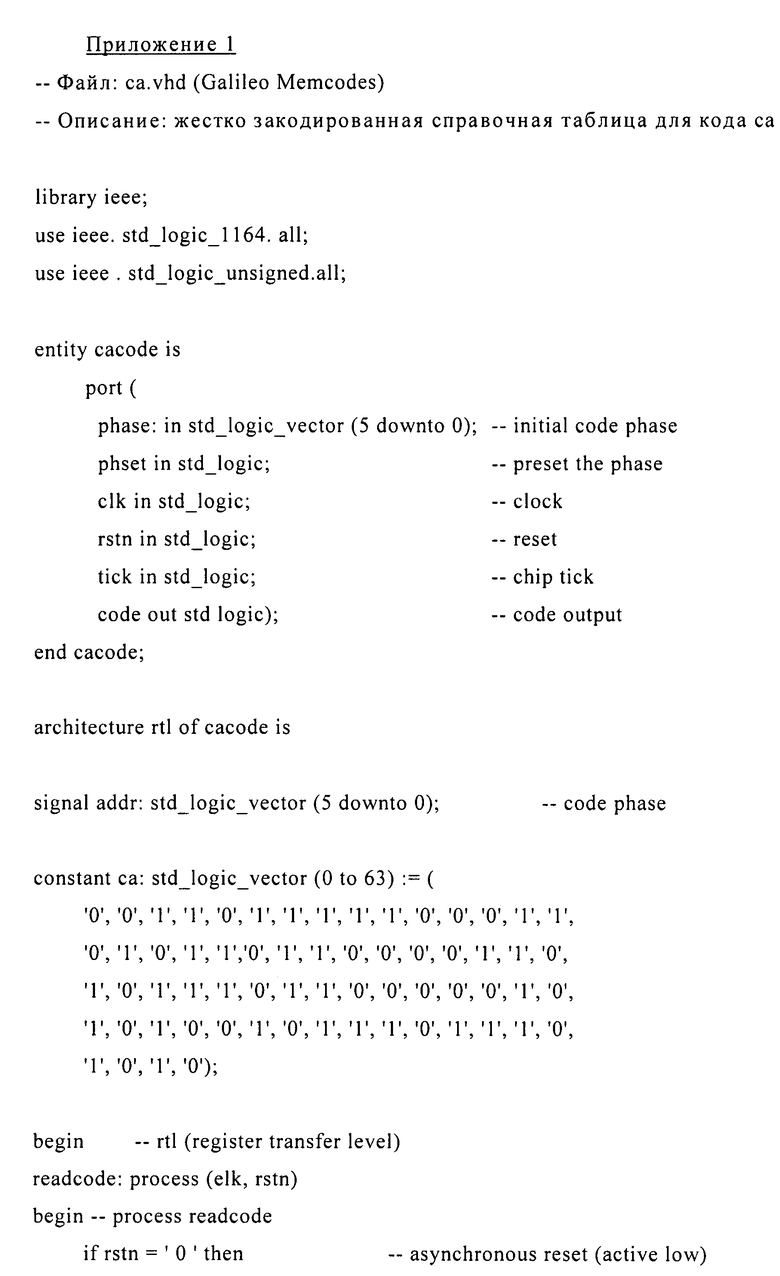

На фиг.1 показана типичная реализация ЛРСОС, который применим, например, в наборе микросхем обычного приемника GPS. В базовое оборудование входит регистр 11 сдвига, имеющий длину N, плюс два дополнительных регистра 12, 13, каждый из которых также имеет длину N. Конструкция регистра сдвига как такового является универсальной за счет того, что отводы обратной связи не реализованы аппаратно. Вместо этого обратной связью между различными стадиями регистра 11 сдвига управляют с помощью полиномиального значения, которое загружают в один из двух дополнительных регистров (полиномиальный регистр 12). Затем, исходя из значения, хранящегося в другом дополнительном регистре (регистре 13 выбора начальной конфигурации) осуществляют начальную установку ЛРСОС. Тем самым путем ввода соответствующих значений в полиномиальный регистр и регистр выбора начальной конфигурации можно привести показанный на фиг.1 ЛРСОС в соответствие с требованиями заказчика.

Показанный на фиг.1 ЛРСОС имеет 3N ячеек памяти (поскольку регистр 11 сдвига, полиномиальный регистр 12 и регистр 13 выбора начальной конфигурации имеют по N ячеек памяти каждый). Как указано выше, в максимальном золотом коде число ячеек памяти в регистре 11 сдвига с обратными связями связано с длиной (L) выходного кода следующей зависимостью: N=2log(L+1). Поскольку в основе золотого кода обычно лежит сочетание выходов двух ЛРСОС, общее число ячеек памяти T(S) для золотого кода можно выразить как T(S)=6*2log(L+1). Кроме того, генератор стандартного кода ЛРСОС имеет определенную комбинаторную логику для обеспечения отводов обратной связи (XOR) в также небольшой конечный автомат/контроллер, объединенный со счетчиком (или компаратор + регистр), для переустановки, перезагрузки и перезапуска в конце последовательности.

В отличие от этого при непосредственной реализации кода с памятью в приемнике для каждого кода, сохраняемого в приемнике, включая соответствующие дешифраторы адресов, может потребоваться память полной емкости. Память может являться статической или динамической в зависимости от выбранной технологии реализации. Наиболее широко распространенные технологии (ASIC, от английского - application-specific integrated circuits, специализированная интегральная схема, FPGA, от английского - Field Programmable Gate Array, программируемая пользователем вентильная матрица) поддерживают статическую память. Кроме того, с целью обеспечить считывание правильной ячейки памяти обычно используют небольшой конечный автомат или контроллер для генерации адреса. Если допустить, что эквивалентное количество логических элементов ячейки статической памяти составляет 1,5 NAND2 (NAND2 соответствует логическому элементу И-НЕ с двумя входами и обычно имеет 6 транзисторов), то при использовании 0,18-µм технологии площадь каждой ячейки памяти составит 18,75 µм2. Если допустить, что конечный автомат/контроллер имеет 200 логических элементов, а код содержит 4096 импульсов (что соответствует сигналу L1 системы Galileo), получаем 6344 логических элементов NAND2 с общей площадью 79300 µм2. В качестве альтернативы, если код содержит 10230 импульсов, как у сигнала Е5 системы Galileo, и исходя из приведенных выше допущений, получаем 15545 логических элементов NAND2 с общей площадью 194312 µм2 (пренебрегая любой экономией за счет регулярности структуры). Это может представлять собой существенную непроизводительную нагрузку на набор микросхем приемника.

Отметим, что в случае кода с памятью T(S)≈L. Иными словами, число ячеек памяти растет прямо пропорционально длине кода, а не пропорционально логарифму кода, как случае реализации на базе ЛРСОС. С связи с этим ясно, что с увеличением длины расширяющего кода для применения кодов с памятью требуется существенно большее число ячеек памяти, чем при обычном подходе с использованием ЛРСОС. Эта проблема усугубляется тем, что в приемнике должен храниться не один расширяющий код, а полный набор расширяющих кодов для всех спутников и всех интересующих сигналов.

Соответственно, в одном из вариантов осуществления изобретения предложен приемник, применимый в спутниковой навигационной системе, включающей группировку из множества спутников, каждый из которых передает сигнал, содержащий расширяющий код. Приемник имеет по меньшей мере одно устройство хранения кодов, которое содержит комбинаторную логику для хранения кода с памятью, представляющего собой фиксированный набор импульсов (простейших элементов или элементарных посылок кода). Хранящийся код с памятью соответствует расширяющему коду, входящему в сигнал, передаваемый спутником. Комбинаторная логика имеет функциональные возможности дешифрирования адресов для извлечения заданной части хранящегося кода с памятью. Причем как в этом варианте осуществления изобретения, так и в раскрытых далее подразумевается, что внутренняя аппаратная конфигурация комбинаторной логики приспособлена для хранения набора данных и не содержит стандартных ячеек памяти, при этом комбинаторная логика для хранения кодов с памятью и обеспечения адресных функций интегрирована на уровне физического компонента без четкого разделения между двумя этими функциями. Приемник также имеет коррелятор для осуществления корреляции входного сигнала и хранящегося кода с памятью, извлеченного из устройства хранения кодов.

Подразумевается, что при обычной реализации ячейки памяти, например в виде триггера или регистра, в ее основу положена последовательная логика, которая поддерживает состояние, зависящее от ранее введенных данных, при этом в устройство загружают данные для хранения в виде входных сигналов. В отличие от этого расширяющий код может считаться сохраненным в комбинаторной логике в силу аппаратной реализованной конфигурации комбинаторной логики.

Также подразумевается, что ЛРСОС, используемый для генерации расширяющего кода в существующем приемнике, содержит последовательную, а не комбинаторную логику, поскольку его выходной сигнал зависит от внутреннего состояния регистров. Кроме того, коды, которые способен генерировать ЛРСОС, ограничены кодами, заданными определенными математическими алгоритмами. По существу, можно скорее считать, что в ЛРСОС хранится математический алгоритм (который может использоваться для генерации кода), а не код как таковой. В отличие от этого комбинаторная логика может использоваться для хранения общего или произвольного расширяющего кода, например кода без каких-либо заданных математических свойств и кода, который генерирован без использования заданного математического алгоритма. Таким образом, комбинаторная логика может использоваться для хранения заказного кода с памятью, который был оптимизирован применительно к конкретной спутниковой навигационной системе (Отметим, что комбинаторная логика не ограничена таким заказным кодом с памятью; она также может использоваться для хранения кодов с памятью, который соответствует золотому коду или какой-либо иной математической последовательности).

Обычно в приемнике хранится отличающийся расширяющий код для каждого сигнала каждого спутника, входящего в группировку навигационных спутников (для обеспечения услуг, поддерживаемых приемником). В их число могут входить расширяющие коды для заменяющих спутников, которые используют в качестве резервных на случай отказа каких-либо спутников в группировке. Существуют различные способы, которыми набор расширяющих кодов можно закрепить за устройством(ами) хранения кодов. Например, в одном из вариантов осуществления для хранения полного набора расширяющих кодов для всех спутников в группировке может использоваться одно устройство хранения кодов. В другом варианте осуществления расширяющий код для каждого сигнала каждого спутника может храниться в отдельном устройстве хранения кодов. Специалисту в данной области техники может быть известно множество других промежуточных способов закрепления кодов с памятью за устройствами хранения кодов.

В одном из вариантов осуществления приемник имеет множество каналов приема, при этом хранящийся код с памятью для спутника может подаваться из устройства(в) хранения кодов в любой из каналов приема с целью корреляции с входным сигналом, принимаемым по этому каналу приема. Так, хотя сами коды с памятью аппаратно реализованы посредством комбинаторной логики, закрепление расширяющих кодов за различными каналами приема может быть гибким. Эта гибкость полезна, поскольку в любое заданное время и в любом заданном местоположении на земле видимым является только определенное подмножество навигационных спутников (остальные могут быть закрыты зданиями или находиться ниже горизонта). Соответственно, за счет гибкого закрепления расширяющих кодов из устройства(в) хранения кодов за различными каналами приема число каналов приема в приемнике может быть меньше общего числа спутников, поскольку в процессе работы система закрепляет за каналами приема расширяющие коды для видимых в данный момент спутников. Кроме того, эта гибкость полезна на случай отказа спутника в группировке, когда его место занимает один из резервных спутников (при условии, что расширяющий код для этого резервного спутника уже хранится в приемнике).

Отметим, что число каналов приема сигнала заданного класса в существующих приемниках также обычно меньше числа спутников в группировке. Это достигается за счет соответствующей настройки каждого ЛРСОС в канале приема на сигнал искомого спутника (с использованием многочлена и регистров начальной установки, показанных на фиг.1). Хотя комбинаторную логику устройства(в) хранения кодов невозможно гибко настроить таким способом в процессе работы, определенная гибкость может быть обеспечена на уровне архитектуры приемника.

В одном из вариантов осуществления устройство хранения кодов способно определять конкретный сегмент одного или нескольких импульсов хранящегося кода с памятью с целью его вывода. Способность выбора определенной части кода с памятью позволяет выводить код с памятью через ограниченное число выходных выводов, а также лучше согласуется со схемами поиска кода с памятью для нормального использования. Устройство хранения кодов может иметь генератор последовательностей, позволяющий устройству последовательно проходить за один раз через один или несколько импульсов кода, созданного комбинаторной логикой, и(или) адресную функцию, позволяющую выбирать для вывода конкретную часть кода с памятью. Отметим, что такой механизм вывода может быть реализован в последовательной логике (например, для прохождения через код), но этот последовательный вывод кода можно считать логически отличающимся от хранения кода с помощью комбинаторной логики (даже если хранение и вывод кода затем объединены на уровне физических компонентов устройства хранения кодов).

Вывод из устройства хранения кодов может осуществляться по одному импульсу за один раз, или каждый вывод может содержать набор из множества импульсов. Отметим, что этот последний вариант отражает дополнительное различие между хранением расширяющего кода в комбинаторной логике и использованием ЛРСОС, поскольку ЛРСОС выводит только по одному импульсу за один раз. В отличие от этого, поскольку в блоке комбинаторной логики хранится вся комбинация элементарных посылок кода, для одновременного вывода в любое заданное время (если это желательно) доступно множество импульсов кода.

Устройство хранения кодов особо применимо для реализации в виде программируемой пользователем вентильной матрицы (FPGA) или специализированной интегральной схемы (ASIC, такой как матрица логических элементов, стандартный элемент), хотя может применяться любая соответствующая полупроводниковая технология (например, полностью заказная технология и т.д.). Поскольку комбинаторная логика обычно совместима с имеющимися схемными решениями FPGA и(или) ASIC, комбинаторная логика может быть спроектирована и реализована с использованием стандартных средств разработки полупроводников. Подразумевается, что применение стандартных технологий, таких как FPGA и ASIC, также способствует реализации комбинаторной логики в увязке с основным набором микросхем приемника (за счет чего отпадает необходимость в высокоскоростном интерфейсе между устройством(-ами) хранения кодов одного устройства и отдельным набором микросхем приемника).

Устройство(а) хранения кодов может(гут) использоваться для хранения множества уровней иерархического кода. Например, устройство хранения кодов может использоваться для хранения первичного кода и(или) вторичного кода. Отметим, что, если в устройстве(ах) хранения кодов хранится как первичный код, так и соответствующий вторичный код, они могут храниться в виде одной длинной последовательности (отображающей окончательный комбинированный код для вывода) или в виде первичного и вторичного кодов по отдельности. Подразумевается, что последняя конфигурация является более компактной, поскольку в этом случае необходимо хранить только N1+N2 импульсов по сравнению с N1×N2 импульсов для хранения полной (комбинированной) кодовой последовательности. В других вариантах осуществления комбинаторная логика может использоваться только для хранения одного уровня иерархического кода, например первичных кодов.

В настоящем изобретении также предложен спутник, применимый в спутниковой навигационной системе, включающей группировку из множества спутников, каждый из которых передает сигнал, содержащий расширяющий код. Спутник имеет по меньшей мере одно устройство хранения кодов, которое содержит комбинаторную логику для хранения кода с памятью, содержащего фиксированный набор импульсов. Код с памятью соответствует расширяющему коду, входящему в сигнал, который передает спутник. Таким образом, подход, применяемый для генерации в приемнике расширяющего кода для корреляции с входным сигналом, также применим для генерации расширяющего кода для передачи спутником.

Кроме того, в настоящем изобретении предложен способ работы приемника, применимого в спутниковой навигационной системе, включающей группировку из множества спутников. Каждый спутник передает сигнал, содержащий расширяющий код. При осуществлении способа создают по меньшей мере одно устройство хранения кодов, которое содержит комбинаторную логику для хранения кода с памятью, содержащего фиксированный набор импульсов. Код с памятью соответствует расширяющему коду, входящему в сигнал, который передает спутник. При осуществлении способа дополнительно осуществляют корреляцию входного сигнала и расширяющего кода, хранящегося в комбинаторной логике.

В настоящем изобретении также предложен способ изготовления приемника, применимого в спутникового навигационной системе, включающей группировку из множества спутников, каждый из которых передает сигнал, содержащий расширяющий код. При осуществлении способа определяют расширяющий код спутника для хранения в приемнике и создают по меньшей мере одно устройство хранения кодов, содержащее комбинаторную логику для хранения фиксированного набора импульсов, соответствующих расширяющему коду спутника.

В одном из вариантов осуществления комбинаторную логику генерируют путем создания спецификации фиксированного набора импульсов на языке описания аппаратных средств. Затем эта спецификация может быть реализована на желаемой платформе с использованием логического синтеза. Отметим, что для определения желаемого выходного кода в спецификации комбинаторной логики, созданной на языке описания аппаратных средств, может использоваться константа. Соответственно, единственным изменением, необходимым для определения отличающегося расширяющего кода, является обновление значения константы.

Далее лишь в порядке примера подробно описаны различные варианты осуществления изобретения со ссылкой на следующие чертежи, на которых:

на фиг.1 показана блок-схема обычного линейного регистра сдвига с обратными связями (ЛРСОС),

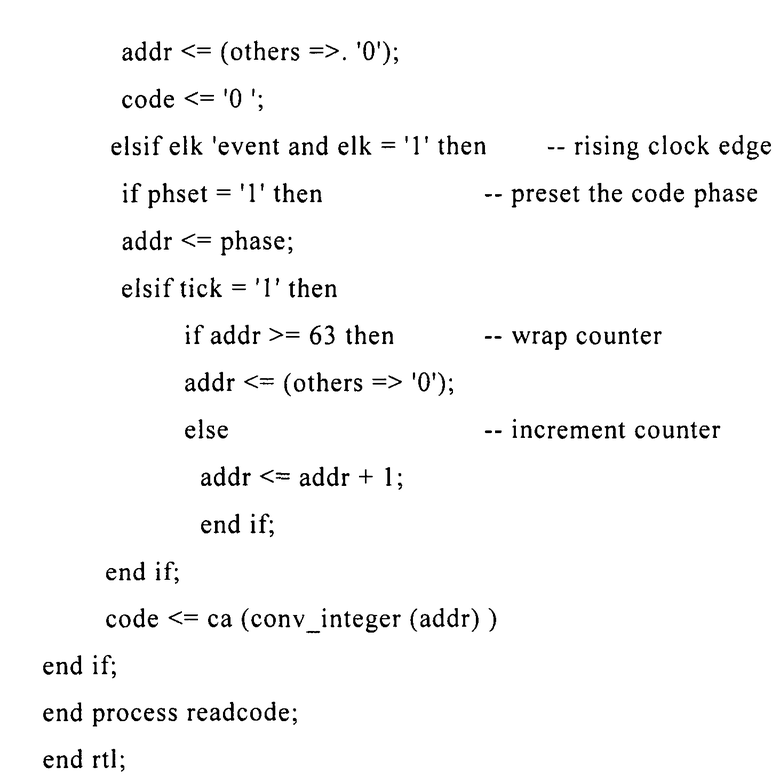

на фиг.2 - блок-схема, иллюстрирующая хранение кода с памятью с использованием комбинаторной логики согласно одному из вариантов осуществления изобретения,

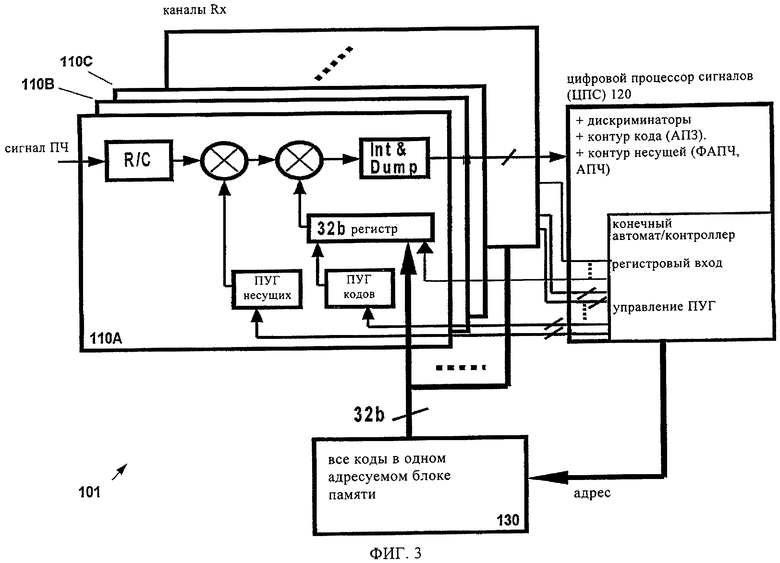

на фиг.3 - блок-схема, иллюстрирующая архитектуру приемника согласно одному из вариантов осуществления изобретения, в котором все коды с памятью хранятся в одном устройстве хранения кодов,

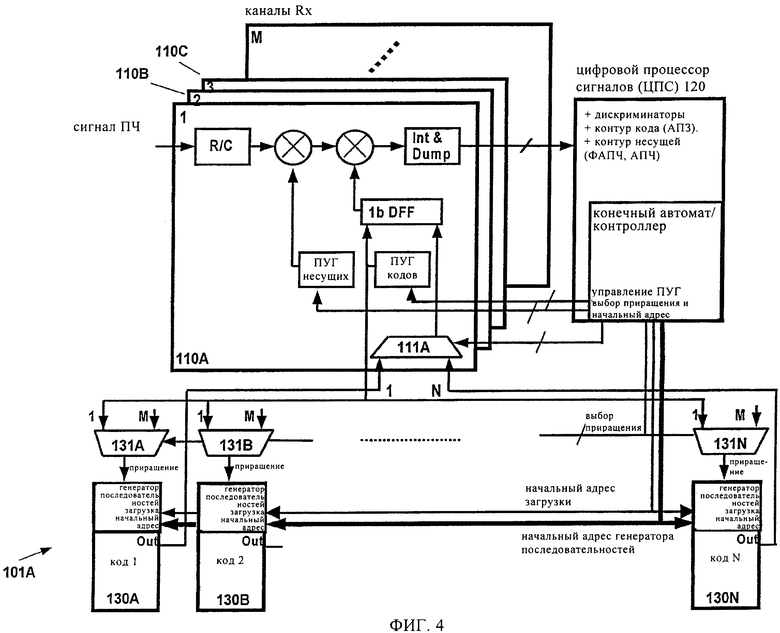

на фиг.4 - блок-схема, иллюстрирующая архитектуру приемника согласно другому варианту осуществления изобретения, в котором каждый код с памятью хранится в отдельном устройстве хранения кодов,

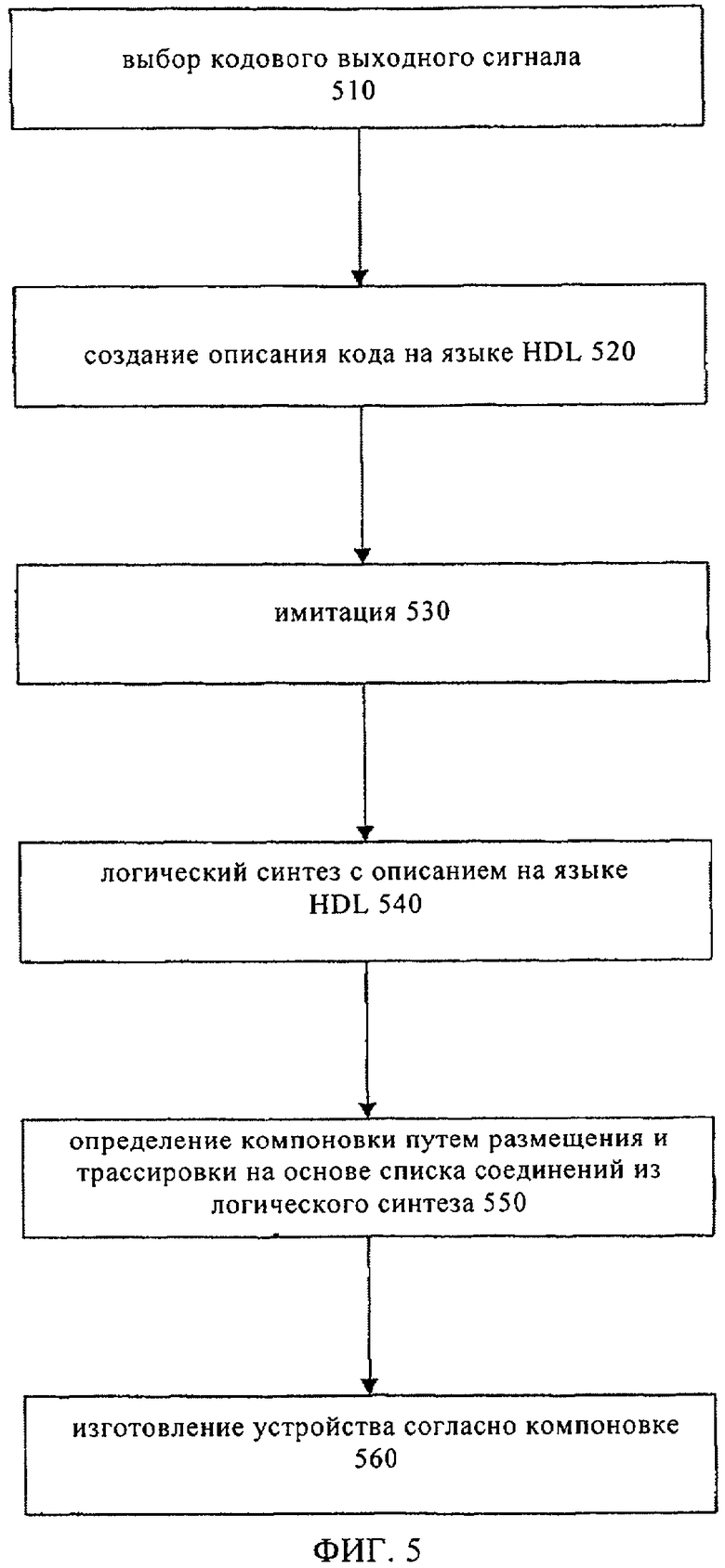

на фиг.5 - блок-схема, иллюстрирующая способ разработки устройства хранения кодов для хранения кодов с памятью согласно одному из вариантов осуществления изобретения и

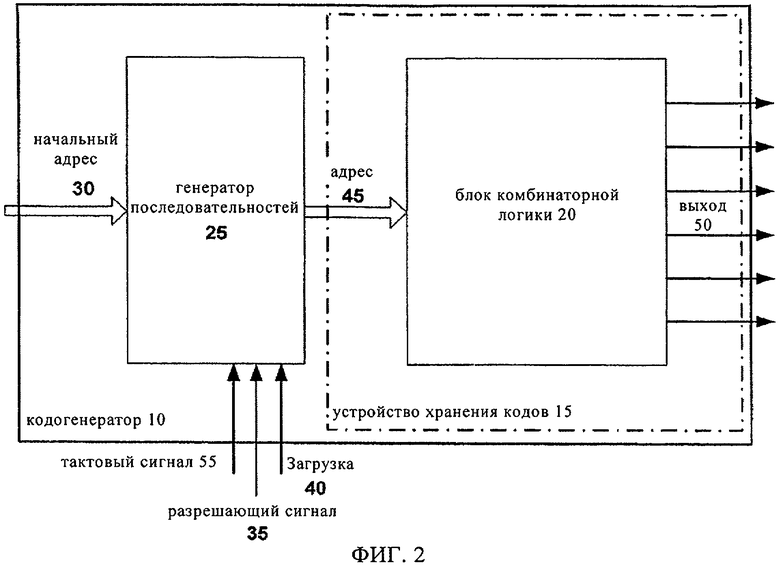

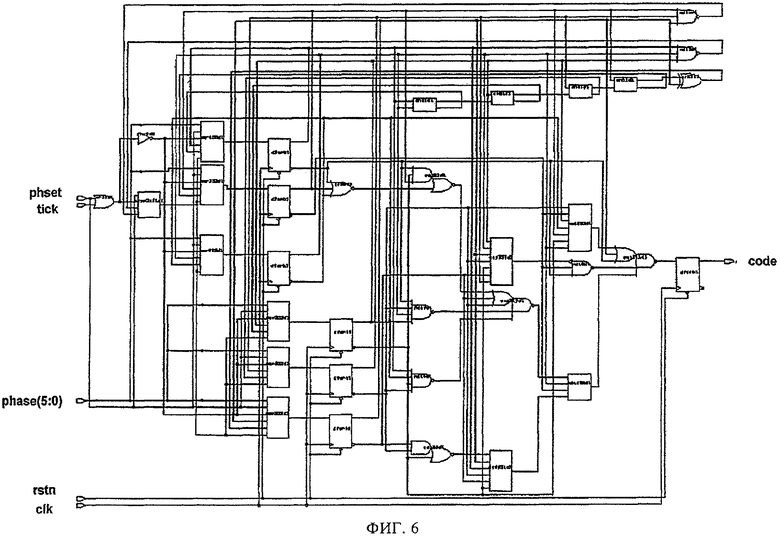

на фиг.6 - пример блок-схемы на основе списка соединений (узлов), созданного проиллюстрированным на фиг.5 способом согласно одному из вариантов осуществления изобретения.

На фиг.2 схематически проиллюстрирован кодогенератор 10 с устройством 15 хранения кодов согласно одному из вариантов осуществления изобретения. Кодогенератор 10 используется для хранения и вывода одного или нескольких кодов с памятью и, следовательно, заменяет такое устройство, как показанный на фиг.1 ЛРСОС в обычном приемнике. С логической точки зрения можно считать, что кодогенератор 10 содержит два основных компонента, а именно устройство 15 хранения кодов и генератор 25 последовательностей. Устройство 15 хранения кодов содержит комбинаторную логику (логическую схему) 20, которую используют для хранения кода с памятью и обеспечения дешифрирования адресов. Генератор 25 последовательностей используют для определения адреса желаемой части кода с памятью для вывода путем загрузки соответствующих начальных адресов и приращения текущих адресов (Отметим, что при физической реализации функциональные возможности этих двух компонентов, по-видимому, будут объединены, как это более подробно пояснено далее, и поэтому между комбинаторной логикой и генератором последовательности не существует четкого разделения, тем не менее с логической или функциональной точки зрения оба компонента могут рассматриваться по отдельности).

В приведенном на фиг.2 примере комбинаторная логика 20 имеет определенное число выходов 50. Выходы 50 определены для заданного адреса в зависимости от конкретной конфигурации логических элементов в комбинаторной логике 20. Во время загрузки 40 в генератор 25 последовательностей адресов загружают начальный адрес 30. Затем адрес из генератора 25 последовательностей адресов в качестве адреса 45 вводят в устройство 15 хранения кодов, и на выходах 50 комбинаторной логики 20 появляется соответствующая часть кода с памятью.

Генератор последовательности адресов осуществляет приращения адреса 45 с каждым импульсом тактового сигнала 55 при условии наличия разрешающего входного сигнала 35. Вследствие этого на выходах 50 комбинаторной логики 20 появляются соответствующие доли или части кода с памятью. В противном случае при отсутствии разрешающего сигнала выбранный адрес 45 и, следовательно, выходы комбинаторной логики 20 остаются постоянными.

Подразумевается, что, поскольку логический блок 20 является комбинаторным, а не последовательным, в нем не хранится информация о состоянии. Следовательно, комбинаторную логику обычно не считают формой запоминающего устройства. Тем не менее конфигурацию логических элементов в комбинаторной логике 20 можно рассматривать как некую форму (аппаратно реализованной) памяти, и поэтому выходы 50 комбинаторной логики 20 соответствуют хранящемуся множеству битов (наименьших единиц информации). Таким образом, комбинаторная логика может считаться одной из форм постоянного запоминающего устройства (ПЗУ), в котором хранится множество битов для каждого адреса 45. Вместе с тем отмечаем, что "содержимое" комбинаторной логики является фиксированным (при условии, что блок комбинаторной логики реализован аппаратно), и не может быть обновлено в отличие от многих стандартных форм ПЗУ, таких как флэш-память, ЭСППЗУ, которые все же поддерживают определенную форму механизма записи. Кроме того, внутренняя конфигурация комбинаторной логики 20 является индивидуальной (заказной) для хранящегося множества битов в отличие от оперативного запоминающего устройства (ОЗУ), которое обычно состоит из стандартных ячеек памяти, в которые затем загружают значения данных. Иными словами, в большинстве обычных запоминающих устройств общая аппаратная структура запоминающего устройства и содержание данных, хранящихся в устройстве, логически разделены (аналогичное разделение также относится к показанной на фиг.1 архитектуре ЛРСОС). Вместе с тем в комбинаторной логике 20 такое разделение отсутствует, поскольку аппаратная структура непосредственно соответствует (т.е. отражает или отображает) фактическому содержанию хранящихся данных (плюс дешифрирование адресов).

Выходы 50 комбинаторной логики 20 могут быть рассчитаны на отображение любого заданного множества битов путем выбора соответствующей конфигурации логических элементов в комбинаторной логике (как это более подробно описано далее). Следовательно, проиллюстрированная на фиг.2 комбинаторная логика применима для хранения последовательности импульсов, соответствующей коду с памятью, и, таким образом, выходы 50 логического блока соответствуют последовательности импульсов кода с памятью (Подразумевается, что при этом задают соответствующее упорядоченное расположение выходов 50 комбинаторной логики 20 для согласования с последовательным характером кода с памятью. Это может быть достигнуто посредством слияния дешифрирования адресов с фактическим содержанием кода с памятью во время логического синтеза, как это более подробно описано далее).

В случае кода с памятью, имеющего длинную последовательность L, содержащую (например) несколько тысяч импульсов, обычно неудобно параллельно выводить все импульсы кода с памятью, поскольку для этого потребовалось бы очень большое число выходных выводов. Кроме того, для работы приемника обычно не требуется выводить сразу весь расширяющий код. Вместо этого комбинаторная логика 20 выводит подмножество одного или нескольких импульсов кода с памятью для каждого выбранного адреса 45.

Например, в зависимости от общей архитектуры приемника:

1. На каждое циклическое изменение адреса 45 может быть предусмотрен один импульс. Затем этот импульс маршрутизируют в единственный коррелятор приемника. В этом случае в комбинаторной логике 20 содержится только один код с памятью.

2. Если в комбинаторной логике 20 содержатся несколько кодов с памятью (например, коды с памятью для нескольких сигналов и(или) нескольких спутников), должен быть предусмотрен коллективный доступ с разделением времени для нескольких корреляторов приемника. При такой реализации комбинаторная логика 20 выводит первую подпоследовательность первого кода с памятью, когда адрес 45 прирастает до определенного значения. Эту подпоследовательность маршрутизируют в соответствующий первый коррелятор приемника. Пока первый коррелятор приемника обрабатывает эту подпоследовательность, комбинаторная логика 20 обеспечивает различные корреляторы приемника другими подпоследовательностями различных кодов с памятью. После того, как обслужены все корреляторы приемника, генератор последовательности возвращается к первому коррелятору приемника и предоставляет ему вторую подпоследовательность первого кода с памятью.

Длина отдельных подпоследовательностей зависит от общего числа корреляторов приемника, обслуживаемых отдельным кодогенератором 10. Число импульсов на подпоследовательность обычно может составлять N=8, 16, 32, 64 или 128. Таким образом, при каждом последующем инициировании тактового сигнала 55 при инициированном разрешающем сигнале 35 генератор 25 последовательностей осуществляет приращение адреса 45, и комбинаторная логика 20 подает очередные N импульсов на выходы 50.

Например, допустим, что в комбинаторной логике 20 хранится только один код с памятью, если L=4096, a N=16, то первый цикл тактового сигнал 55 (при инициированном разрешающем сигнале 35) содержит импульсы 0-15 кода с памятью, хранящиеся в комбинаторной логике 20, следующий цикл тактового сигнала 55 содержит импульсы 16-31 кода с памятью, хранящиеся в комбинаторной логике 20, и так далее, пока не будет выведен весь код с памятью (после чего происходит циклический возврат к импульсу 0). В другом варианте N=1, и в этом случае хранящийся код с памятью выводят из устройства 15 хранения кодов импульс за импульсом.

Подразумевается, что, поскольку генератор 25 последовательностей содержит информацию о состоянии (свое местоположение/адрес в последовательности кодов с памятью), генератор 25 последовательностей использует последовательную логику, а не чистую комбинаторную логику. Например, если L=4096, a N=16, в одном из вариантов осуществления генератор 25 последовательностей может быть реализован в виде восьмиразрядного счетчика.

В проиллюстрированном на фиг.2 варианте осуществления генератор 25 последовательностей также имеет механизм адресации в форме сигнала 30 управления адресами. Этот сигнал 30 управления адресами может использоваться для определения конкретного местоположения в последовательности кодов с памятью для вывода. Так, если продолжить рассмотрение упомянутого примера, в котором L=4096, N=16, a генератором 25 последовательностей является восьмиразрядный счетчик, сигнал 30 управления адресами может быть реализован в виде восьмиразрядной величины для загрузки в счетчик. Иными словами, если разрешающий сигнал 35 приращивает выход генератора 25 последовательностей до местоположения следующего кода, сигнал 30 управления адресами может использоваться для установки генератора 25 последовательностей в любом желаемом (новом) местоположении внутри кода. В другом варианте осуществления сигнал 30 управления адресами заменен простой шиной сброса, которая возвращает отсчет в генераторе 25 последовательностей к нолю. Этот вариант осуществления позволяет переустановить местоположение генератора последовательности, но не позволяет задавать произвольное местоположение генератора последовательности внутри последовательности кодов с памятью.

Существуют различные возможные конфигурации приемника, в котором хранится множество кодов с памятью, таких как различные коды с памятью для различных спутников. В одном из вариантов осуществления для каждого различного кода с памятью предусмотрено отдельное устройство хранения кодов. В качестве альтернативы, для хранения всех кодов с памятью может использоваться одно устройство хранения кодов большой емкости, при этом для выбора как кода, так и местоположения выводимого кода используют механизм 30 адресации. Дополнительно может использоваться множество устройств хранения кодов, в каждом из которых хранятся коды с памятью для некоторых, но не всех спутников или некоторых, но не всех сигналов, например шесть устройств хранения кодов, в каждом из которых хранятся коды с памятью для пяти спутников, или в каждом из которых хранятся все коды с памятью для одного спутника, и т.д. В качестве дополнительной возможности один код с памятью делят среди множества устройств хранения кодов.

Применение комбинаторной логики 20 для хранения кодов с памятью, включая дешифрирование адресов, основано на том, что после определения и объединения кодов обычно их можно считать фиксированными, и следовательно, их не требуется хранить в обычных (обновляемых) запоминающих устройствах. За счет применения комбинаторной логики для хранения или отображения кодов с памятью можно добиться значительного упрощения с точки зрения логических элементов и полупроводниковой технологии, хотя и за счет некоторой потери гибкости. Тем не менее эта гибкость может быть частично компенсирована на уровне архитектуры, как это более подробно описано далее.

На фиг.3 показана блок-схема приемника 101 согласно одному из вариантов осуществления изобретения. В частности, на фиг.3 проиллюстрирован основной диапазон приемника, используемый для обнаружения сигнала и слежения за ним, а другие стандартные элементы (например, антенна, входной каскад ВЧ, блок навигации и т.д.) для ясности опущены. Приемник 101 может быть реализован в виде автономного устройства или может входить в какое-либо более крупное устройство, например мобильный (сотовый) телефон, компьютер, автомобиль или транспортное средство другого типа, больничную койку, самолет или судно, грузовой контейнер и так далее.

Приемник 101 имеет устройство 130 хранения кодов, а также цифровой процессор сигналов (ЦПС) 120 и каналов (Rx) 110A, 110 В, 110С и т.д. приема. Подразумевается, что на всех каналах приема обрабатывают один и тот же входной сигнал, но обработка входного сигнала меняется в каждом канале приема, как это более подробно описано далее. Устройство 130 хранения кодов используют для хранения набора кодов с памятью для группировки спутников. В одном из вариантов осуществления устройство 130 хранения кодов, ЦПС 120 и каналы 110 приема реализованы в одном полупроводниковом устройстве или наборе микросхем, хотя в других вариантах осуществления эти компоненты могут быть распределены среди множества устройств.

Подразумевается, что число кодов, входящих в заданный кодовый набор (и, следовательно, подлежащих хранению в логическом блоке 130), зависит от конкретных требований соответствующей спутниковой навигационной системы. Такие системы обычно рассчитаны на использование примерно 24-30 различных спутников, при этом, как правило, предусмотрен один или несколько дополнительных спутников в качестве потенциального резерва на случай отказа. Каждый спутник также обычно передает множество сигналов. Кроме того, некоторые сигналы спутников системы Galileo содержат пилотную составляющую и составляющую данных (которые могут поступать по одному каналу приема).

Предполагается, что проиллюстрированная на фиг.3 архитектура рассчитана на прием одного сигнала по одному каналу. Канал может быть гибко закреплен за любой несущей и сигнальной составляющей любого спутника, сигнал которого поступает на входной каскад ВЧ. В устройстве 130 хранения кодов хранятся коды, используемые для любой несущей и сигнала в группировке спутников.

В некоторых вариантах осуществления число кодов в кодовом наборе может быть увеличено, чтобы учесть сигналы "псевдоспутников", излучаемые из наземных точек, например вблизи аэропортов. Приемник воспринимает такие сигналы псевдоспутников, как дополнительные спутниковые навигационные сигналы, за счет чего может быть обеспечено более точное и надежное определение местоположения таких точек.

В процессе работы канала 110 приема реальный входной сигнал промежуточной частоты (ПЧ) преобразуют в комплексный модулирующий сигнал. Затем модулирующий сигнал микшируют с выходным сигналом программно-управляемого генератора (N СО, от английского - numerically controlled oscillator) несущих, чтобы удалить из сигнала доплеровский эффект. Затем осуществляют корреляцию входного сигнала с локальным расширяющим кодом, т.е. кодом, хранящимся или генерируемым в приемнике, при этом ее синхронизацией управляет ПУГ кодов. Результаты этой корреляции в заданное время интегрируют и затем направляют в ЦПС 120. В нем дискриминаторы и контурные фильтры с помощью соответствующих ПУГ замыкают контур соответствующей несущей (автоматическая подстройка частоты (АПЧ), фазовая автоподстройки частоты (ФАПЧ)) и контур кода (автоматическая подстройка по задержке (АПЗ)).

Подразумевается, что описанная выше работа приемника 101 обычно соответствует характеристикам существующих приемников спутниковой навигации, таких как используются в GPS. Дополнительная информация о таких приемниках может быть почерпнута из упомянутой книги Misra и Enge (Также подразумевается, что для ясности на фиг.3 опущены некоторые касающиеся приемника 101 подробности, такие как обработка кодов данных и пилотных кодов, которые не имеют непосредственного отношения к пониманию изобретения).

В существующих приемниках локальный расширяющий код генерирует ЛРСОС, такой как показан на фиг.1, который может быть включен в каждый канал 110А, 110В и т.д. приема. В отличие от этого в показанном на фиг.3 приемнике для хранения кодов с памятью используется устройство 130 хранения кодов (такое, как показано на фиг.2). Устройство 130 хранения кодов принимает от ЦПС 120 сигнал адресации, в котором определено, какая часть хранящихся кодов должна быть выведена в соответствующие каналы 110 приема. Этот адрес вывода задан конечным автоматом (КА)/контроллером, входящим в ЦПС 120.

В показанном на фиг.3 варианте осуществления предполагается, что каждый адрес соответствует 32-импульсной порции кода с памятью в блоке 130. Затем эту порцию кода с памятью загружают в регистр внутри соответствующего канала 110 приема для использования при корреляции с входным сигналом. Корреляцию 32-импульсной порции кода с памятью, хранящегося в регистре, осуществляют под управлением ПУГ кодов обычно тем же способом, что и в существующих системах с использованием кодовых ЛРСОС (Можно считать, что существующий приемник аналогичен приемнику согласно варианту осуществления, показанному на фиг.3, но не имеет устройства 130 хранения кодов и вместо буферного регистра в каждом канале приема имеет кодовый ЛРСОС). Отметим, что в других вариантах осуществления для считывания данных из устройства 130 хранения кодов может использоваться отличающаяся длина слова в зависимости от общего числа каналов приема и полосы пропускания, доступной в выходном интерфейсе устройства 130 хранения кодов.

Обычно КА/контроллер ЦПС 120 дает устройству 130 хранения кодов команду последовательно подать 32-импульсный сегмент кода в каждый канал 110 приема. Так, после подачи 32-импульсного сегмента кода в канал приема 110А КА/контроллер последовательно циклически проходит через каждый из остальных каналов приема 110 В, 110С,…110N, чтобы подать в них их собственный соответствующий сегмент кода. Пока устройство 130 хранения кодов подает сегменты кода в другие каналы приема, в канале 110А приема осуществляется корреляция 32-импульсного сегмента кода, буферизованного в его регистре, с входным сигналом (обычно по одному импульсу за один раз). Затем КА/контроллер дает устройству 130 хранения кодов команду вывести следующий 32-импульсный сегмент соответствующего кода с памятью в регистр канала 110А приема, и цикл продолжается. Таким образом, сигнал адресации, подаваемый КА/контроллером в устройство 130 хранения кодов, по существу, опознает как конкретный канал приема, так и местоположение в заданной последовательности кодов с памятью для подачи в такой канал приема.

В большинстве приемников число каналов 110 приема меньше числа спутников в группировке. Этот отражает тот факт, что в любое заданное время видимой является только ограниченная часть спутников (фактический набор спутников над горизонтом в любом заданном местоположении меняется с течением времени по мере движения спутников по своим орбитам).

Как показано на фиг.1, типичная реализация ЛРСОС является универсальной, поскольку позволяет загрузить полиномиальный код для любого желаемого спутника. Благодаря этому ЛРСОС может быть включен в канал приема без привязки канала приема к коду заданного спутника. Вместо этого любой заданный канал приема может быть настроен на прием сигнала от любого заданного спутника из группировки спутников, использующих золотые коды. За счет этого ограниченный набор каналов приема может быть приведен в соответствие с поднабором спутников, видимых приемником в данное время.

В отличие от этого расширяющие коды в устройстве 130 хранения кодов являются фиксированными или аппаратно реализованными в комбинаторной логике. В связи с этим для обеспечения гибкости закрепления каналов приема за различными спутниками приемник 101 способен подавать код с памятью, хранящийся в устройстве 130 хранения кодов, в любой заданный канал 110 приема (указанный ЦПС 120). За счет этого сохраняется способность гибкого закрепления каналов 110 приема за спутниками.

На фиг.4 показана реализация приемника 101А в другом варианте осуществления. Отметим, что многие особенности проиллюстрированного на фиг.4 варианта осуществления совпадают с особенностями варианта осуществления, показанного на фиг.3, поэтому далее в описании сосредоточено внимание на различиях между двумя вариантами осуществления.

В варианте осуществления, показанном на фиг.4, используется не одно устройство хранения кодов, а набор устройств 130А, 130В,…130N хранения кодов. В каждом устройстве 130А, 130В и т.д. хранения кодов хранится расширяющий код для одного сигнала одного спутника. Каждый канал 110 приема имеет мультиплексор 111, который соединен с выходом каждого устройства 130А, 130В и т.д. хранения кодов (Для простоты на фиг.4 показаны только соединения устройств 130А, 130В и т.д. хранения кодов с каналом 110А приема; предусмотрены аналогичные соединения устройств 130А, 130В и т.д. хранения кодов с другими каналами 110В, 110С и так далее приема). Затем выходной сигнал мультиплексора 111 подают в триггер в канале 110 приема, а оттуда кодовый бит загружают для корреляции с входным сигналом существующих приемников.

В мультиплексор 111 из контроллера внутри ЦПС 120 подают управляющий сигнал, который используют для выбора выходного сигнала из различных входных сигналов мультиплексора. Подразумевается, что эта конфигурация позволяет контроллеру ЦПС выбирать код с памятью из любого заданного устройства 130А, 130В т.д. хранения кодов для подачи в любой заданный канал 110А, 110В и т.д. приема. Таким образом, хотя коды с памятью можно считать аппаратно реализованными в различных устройствах 130 хранения кодов, их можно гибко закреплять за набором каналов приема (как в показанном на фиг.3 варианте осуществления). Таким образом, ЦПС 120 в процессе работы управляет мультиплексорами 111 с использованием этого управляющего сигнала таким образом, чтобы каждый канал 110 приема, по существу, имел закрепленное устройство 130 хранения кодов. Число каналов приема может быть меньше числа спутников в группировке.

Следовательно, в данном варианте осуществления число каналов приема также может быть меньше числа устройств 130 хранения кодов, т.е. M<N. Таким образом, гибкая зависимость между каналом 110 приема и устройством 130 хранения кодов позволяет ЦПС закреплять каналы 110 приема за теми устройствами хранения кодов, которые содержат расширяющие коды для видимых в данный момент спутников. Поддержка такого гибкого закрепления также полезна, если один или несколько отказавших спутников должны быть заменены спутниками, которые используют различные коды с памятью (при условии, что в устройстве 130 хранения кодов также доступны заменяющие коды).

Каждое устройство 130А, 130В и т.д. хранения кодов имеет генератор последовательностей, который может быть настроен на заданный загрузочный адрес (как это описано выше со ссылкой на фиг.2). Генератор последовательностей принимает сигнал приращения (разрешения) для пошагового прохождения на один импульс через код с памятью для вывода в мультиплексор 111. В варианте осуществления, показанном на фиг.4, сигнал приращения, подаваемый в устройство 130А, 130В и т.д. хранения кодов, принимают через соответствующий мультиплексор 131А, 131В и т.д. Каждый мультиплексор 131А, 131В и т.д. принимает входной сигнал от ПУГ кодов по каждому из каналов 110А, 110В и т.д. приема. Аналогичный управляющий сигнал, подаваемый в мультиплексор 111, также используют для выбора входного сигнала, который через мультиплексор 131 подают в устройство 130 хранения кодов в качестве сигнала приращения. Соответственно, ПУГ кодов в канале 110 приема способен запрашивать (разрешать) извлечение очередного кодового импульс из устройства 130 хранения кодов, выход которого закреплен за таким каналом приема.

Доступ к расширяющему коду в приемнике 101А осуществляется по одному импульсу за один раз (а не единовременно к 32 импульсам, как в показанном на фиг.3 варианте осуществления), поскольку различные устройства 130А, 130В и т.д. хранения кодов способны осуществлять вывод в соответствующие каналы 110А, 110В и т.д. приема параллельно друг другу. Так, каждый канал приема, по существу, способен по требованию принимать кодовый импульс от закрепленного за ним устройства хранения кодов (В отличие от этого устройство 130 хранения кодов, показанное на фиг.3, обслуживает набор каналов приема последовательно в режиме разделения времени, поэтому при каждом доступе в канал приема поступает достаточно импульсов до очередного периода обслуживания канала приема). Таким образом, эта конфигурация позволяет с помощью ПУГ кодов независимо управлять в каждом канале приема скоростью подачи импульсов в коррелятор. Подразумевается, что показанный на фиг.3 вариант осуществления, в котором все коды с памятью хранятся в одном устройстве хранения кодов, показанный на фиг.4 вариант осуществления, в котором каждый код с памятью хранится в отдельном устройстве хранения кодов, отображают лишь две возможные реализации. Например, в некоторых вариантах осуществления может использоваться множество устройств хранения кодов, в каждом из которых хранится множество (но не все) кодов с памятью, а в других вариантах осуществления каждый код с памятью может быть распределен среди множества устройств хранения кодов.

На фиг.5 показана блок-схема, служащая высокоуровневым представлением изготовления устройства 130 хранения кодов согласно одному из вариантов осуществления изобретения. Осуществление способа начинают с определения желаемого расширяющего кода (шаг 510). Подразумевается, что проиллюстрированный на фиг.5 способ является универсальным, поскольку он применим с использованием произвольной (например, заказной) последовательности импульсов расширяющего кода. В этом состоит отличие, например, от реализации на основе ЛРСОС, которые способны лишь обеспечивать ограниченный набор расширяющих кодов, т.е. те коды, которые могут быть выражены посредством определенных заданных математических алгоритмов.

Устройство хранения желаемого расширяющего кода описывают с использованием языка описания аппаратных средств (HDL, от английского - hardware description language) (шаг 520). Примером HDL является язык описания аппаратных средств на базе сверхбыстродействующих интегральных схем (VHDL, от английского - Very High Speed Integrated Circuits Hardware Description Language), регламентируемый стандартом IEEE 1076. Другим примером HDL является язык Verilog, регламентируемый стандартом IEEE 1995. Языки VHDL и Verilog хорошо известны специалистам в данной области техники и позволяют описывать функцию и структуры интегральных схем.

После того, как на языке HDL разработано и составлено описание схемы генерации желаемого расширяющего кода, может быть осуществлена имитация (на шаге 530), чтобы удостовериться в том, что схема обладает ожидаемыми свойствами. Существует множество промышленно производимых средств осуществления такой имитации. Затем описание на языке HDL может использоваться в качестве данных для ввода в процедуру логического синтеза (шаг 540), в ходе которой преобразуют описание на языке HDL в структурный список соединений компонентов (библиотечных элементов) схемы. Этот список соединений используют в качестве данных для ввода в соответствующие средства размещения и трассировки с целью определения компоновки полупроводникового устройства (шаг 550). Затем в зависимости от выбранной технологии может быть изготовлена специализированная интегральная схема (ASIC) или заказное полупроводниковое устройство (шаг 560) или настроена программируемая пользователем вентильная матрица (FPGA). Также подразумевается, что имеются стандартные промышленные средства для осуществления логического синтеза описанной на языке HDL схемы и затем ее преобразования в фактическую реализацию.

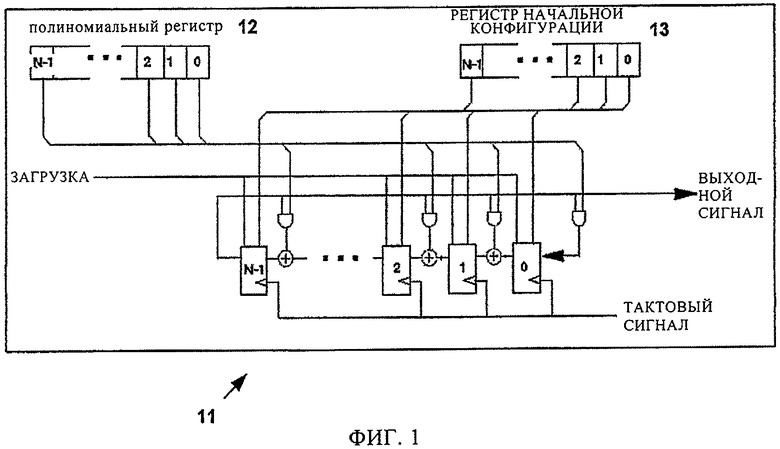

В Приложении 1 приведен пример программы на языке VHDL для использования в устройстве 130 хранения кодов согласно одному из вариантов осуществления изобретения. Устройство хранения кодов (именуемое "cacode") выводит 64-импульсную последовательность, определяемую как константа "са". Подразумевается, что с использованием языка VHDL могут быть реализованы другие кодовые последовательности путем соответствующей адаптации значения константы "са" к желаемой комбинации элементарных посылок.

На языке VHDL описывают пять входных сигналов и один выходной сигнал cacode для осуществления следующих функций:

phase - этот входной сигнал описывает начальный адрес первого выходного импульса и содержит 6 импульсов, соответствующих диапазону адресов 64-импульсной последовательности са,

phset - этот входной сигнал разрешает величину сигнала phase,

clk - входной тактовый сигнал,

tick - этот входной сигнал используют, чтобы указать, когда необходим другой кодовый выходной сигнал (для корреляции с входным сигналом); отметим, что сигнал tick имеет гораздо меньшую частоту, чем сигнал clk,

rstn - этот входной сигнал переустанавливает на ноль адрес и выходной сигнал,

code - этот входной сигнал отображает значение cacode по соответствующему адресу.

В процессе работы заданная схема выводит из последовательности импульсов cacode последовательные значения для каждой величины сигнала tick, при этом для поддержания адреса или текущего местоположения в последовательности импульсов используют переменный адрес (addr). Подразумевается, что адресная составляющая этой схемы является последовательной (а не чисто комбинаторной), поскольку для каждого выводимого кодового импульса поддерживают и приращивают текущий адрес вывода. Тем не менее с функциональной точки зрения можно считать, что схема имеет первый участок для хранения расширяющего кода, включая дешифрирование адреса, и второй участок для генерации адреса и тем самым управления выводом расширяющего кода. С этой точки зрения первый участок для хранения расширяющего кода и дешифрирования адреса является комбинаторным, тогда как второй участок для генерации адреса и управления выводом расширяющего кода является последовательным. Подразумевается, что это различие между комбинаторным и последовательным участками четко проявляется на функциональном уровне, но на уровне физической реализации оба участка обычно объединены (смотри далее).

Специалисту в данной области техники известны различные иные возможные спецификации для устройства хранения кодов. Например, вариант осуществления согласно Приложению 1 можно усовершенствовать таким образом, чтобы сигнал phset считался всегда инициированным, и в этом случае схема будет выводить кодовый импульс, определяемый адресом, который задан сигналом phase. В таком варианте осуществления в самой схеме отсутствует информация о состоянии, но эта информация о текущем местоположении в кодовой последовательности должна поддерживаться извне, например, схемным компонентом, который обеспечивает сигнал phase (и который затем способен соответствующим образом приращивать сигнал phase). Теоретически такая реализация допускает чисто комбинаторное устройство хранения кодов, хотя на практике, вероятно, будет использоваться последовательный компонент.

На фиг.6 приведен пример блок-схемы на основе списка соединений, полученного методом логического синтеза с использованием языка VHDL согласно Приложению 1. Схема имеет пять сигнальных входов, которые сверху вниз обозначены как phset, tick, phase (5:0), rstn и elk, плюс один сигнальный выход, обозначенный как code. Схема содержит в основном комбинаторную логику в форме логических элементов (отметим, что прямоугольники на фиг.6 также соответствуют сочетаниям логических элементов). Показанная на фиг.6 схема также имеет семь триггеров (все они также соединены своим разрешающим входом с сигналом elk и с входом rstn ниже). Шесть из этих семи триггеров используют, по существу, для хранения шести битов адреса. Остающийся триггер используют с целью буферизации единственного импульса кодового выходного сигнала, хотя в других вариантах осуществления это может быть опущено (Относительно большая часть схемы, показанной на фиг.6, приходится на адресные триггеры, поскольку код является коротким, содержит только 64 импульса; в случае более длинных кодов на адресные триггеры приходится меньшая часть схемы). Показанный на фиг.6 список соединений может использоваться в качестве входных данных для размещения и трассировки компонентов, после чего осуществляют операцию изготовления полупроводникового прибора (соответствующую шагам 550 и 560 на фиг.5). Изготовление полупроводникового прибора может быть осуществлено любым применимым способом, таким как литографирование реального устройства, конфигурирование FPGA и т.д.

Подразумевается, что показанная на фиг.6 конкретная блок-схема (включая сочетания логических элементов, обозначенные прямоугольниками на схеме) является характерной для технологии конкретного изготовителя устройства определенного типа согласно требованиям различных библиотек, которые могут быть привлечены в процессе логического синтеза (Для размещения и трассировки схем также могут использоваться библиотеки изготовителя). В частности, как показано на фиг.6, изготовителем является Amtel, компания, занимающаяся изготовлением на заказ полупроводниковых устройств, а компоновка схемы рассчитана на технологию ASIC. При использовании технологии других изготовителей список соединений и компоновка для реализации схемы на языке VHDL, приведенной в Приложении 1, будет отличаться. Соответственно, на фиг.6 лишь в общей схематической форме проиллюстрированы результаты логического синтеза, а его подробная структура не имеет значения для понимания настоящего изобретения.

Применение комбинаторной логики для хранения расширяющих кодов способно обеспечить значительную экономию логических элементов по сравнению со стандартной памятью, реализованной на базе триггеров или ячеек статического ОЗУ или иных подобных обычных архитектур памяти.

На первой и третьей строках Таблицы 1 приведены расчетные данные при "стандартной" реализации памяти (статического ОЗУ) для хранения расширяющего кода для сигналов L1 и Е5а, соответственно, системы Galileo. На второй и четвертой строках Таблицы 1 показана реализация на базе комбинаторной логики с использованием логического синтеза, такого как описан выше со ссылкой на фиг.5 и 6. Как видно из Таблицы 1, применение комбинаторной логики обеспечивает весьма существенную экономию на 80% или более в пересчете на регистры (триггеры), логические элементы и площадь схемы по сравнению со стандартной реализацией памяти.

Отметим, что цифры на второй и четвертой строках Таблицы 1 отражают результаты логического синтеза (при условии реализации на базе ASIC), и поэтому их следует считать чисто потенциальной реализацией, а не просто расчетом. Разумеется, подразумевается, что эти цифры будут незначительно меняться при других потенциальных реализациях, например, с использованием технологии различных изготовителей, FPGA вместо ASIC и так далее. Например, может быть предусмотрена еще более компактная реализация с использованием целиком заказной сверхбольшой интегральной схемы (СБИС). Разумеется, реализация на базе такой заказной СБИС была бы существенно дороже, чем на базе FPGA или ASIC, хотя она может стать рентабельной для рынка приемников массового производства.

На трех последних строках Таблицы 1 приведены 1023-импульсный код СА, используемый в GPS. На шестой и седьмой строках Таблицы 1 показано хранение этого кода в обычной памяти и с использованием комбинаторной логики, соответственно. Также можно увидеть, что использование комбинаторной логики для хранения кодов с памятью обеспечивает существенную экономию логических элементов и площади схемы. На пятой строке Таблицы 1 приведены цифры в случае фактической реализации 1023-импульсного расширяющего кода с использованием ЛРСОС (поскольку кодами GPS являются золотые коды). Отметим, что реализация на базе комбинаторной логики имеет такой же порядок сложности, что и реализация на базе ЛРСОС (для чего необходимо относительно большое число регистров), и в этом конкретном случае она даже еще более компактна. Соответственно, использование комбинаторной логики для хранения расширяющих кодов является потенциально привлекательным даже в случае золотых кодов и других математически генерируемых кодов.

Подразумевается, что при использовании комбинаторной логики для хранения получают коды, которые, по существу, аппаратно реализованы в приемнике. Вместе с тем на практике набор расширяющих кодов для группировки спутников, вероятно, будет оставаться неизменным в течение многих лет (что имеет место в случае с GPS). При этих обстоятельствах обычно важнее иметь возможность гибко закреплять расширяющие коды за различными каналами приема, чем изменять сами расширяющие коды. Первая функция может быть обеспечена в приемниках, имеющих комбинаторную логику для хранения расширяющих кодов, как это описано выше со ссылкой на фиг.3 и 4.

В приемник могут быть введены хранящиеся коды по меньшей мере для двух спутников, обозначенных как резервные (помимо кодов для основной группировки спутников). Затем эти заменяющие спутники вводят в группировку навигационных спутников в случае отказа одного из исходного набора спутников. При условии, что коды, закрепленные за заменяющими спутниками, заранее известны, они также могут быть сохранены в приемнике с использованием комбинаторной логики и введены в действие по обстоятельствам, например, как это описано выше со ссылкой на фиг.3 и 4. В других вариантах осуществления приемник может иметь обычную память, такую как ППЗУ или ОЗУ, в которую затем загружают любые новые спутниковые расширяющие коды (для применения в сочетании с кодами, хранящимися в описанном(ых) устройстве(ах) хранения кодов).

В некоторых вариантах осуществления в приемнике могут хранится расширяющие коды по меньшей мере для двух группировок спутников, например системы Galileo и GPS, с целью обеспечения комбинированной информации о местоположении. Хотя расширяющими кодами GPS являются золотые коды, которые обычно генерируют в приемник с использованием ЛРСОС, вместо этого коды GPS могут хранится в виде полных комбинаций элементарных посылок с использованием комбинаторной логики, если это желательно (в противоположность использованию ЛРСОС, в котором, по существу, хранится алгоритм для генерации комбинации элементарных посылок, а не сама комбинация элементарных посылок). Как следует из Таблицы 1, за счет использования комбинаторной логики для хранения полных кодов GPS можно фактически обеспечить более компактную реализацию, чем на основе ЛРСОС. Соответственно, применение комбинаторной логики для хранения расширяющих кодов совместимо с заказными кодовыми комбинациями, а также с обычными кодовыми комбинациями, полученными из математических алгоритмов, такими как комбинации на базе золотых кодов. Также подразумевается, что комбинаторная логика может использоваться для хранения фрагментов расширяющего кода, представляющих собой первичный код и(или) вторичный код, или для хранения полной последовательности символов, отображающей получаемую комбинацию первичного и вторичного кода.

Комбинаторная логика для хранения расширяющего кода может быть включена не только в приемник, но также в спутник. В этом случае комбинаторную логику используют для хранения расширяющего кода, применимого в сигнале для передачи на землю. Вместе с тем описанный в изобретении подход обычно более эффективен в отношении приемников, чем спутников. Так, поскольку спутникам требуется хранить лишь собственный расширяющий код (а не расширяющие коды для всей группировки), на запоминающие устройства спутников приходится меньшая нагрузка, чем у приемников. Кроме того, каждому спутнику потребовалось бы особое устройство хранения кодов для собственного расширяющего кода. При этом возникают дополнительные сложности с проверкой достоверности и изготовлением программного обеспечения по сравнению с обычной архитектурой памяти, в которой во всех спутниках может использоваться стандартный набор ячеек памяти, в которые затем по обстоятельствам загружают желаемый расширяющий код. Кроме того, поскольку спутники не являются массово производимыми устройствами, на них не распространяются такие же ограничение на издержки, как на приемники.

Следует также отметить, что, хотя описанный в изобретении подход в основном рассчитан на применение в спутниковых навигационных системах, он также может применяться в других навигационных системах или системах связи (спутниковых, наземных или морских), в которых в настоящее время используют ЛРСОС для генерации кодов синхронизации, фильтры, наборы фильтров и тому подобное. Одним из частных примеров является упомянутый выше псевдоспутник, который генерирует сигналы определения местоположения, аналогичные сигналам навигационного спутника, но базируется на земле. Псевдоспутники обычно используют там, где требуется высокая точность, например вблизи аэропортов, чтобы усилить (и эмулировать) сигналы определения местоположения, поступающие от спутников. Соответственно, расширяющие коды для сигналов псевдоспутников могут хранится в приемниках (и(или), возможно, в самих псевдоспутниках) с использованием описанной выше комбинаторной логики.

В заключение необходимо отметить, что, хотя выше описаны разнообразные варианты осуществления, подразумевается, это сделано лишь в порядке примера, и специалист в данной области техники сможет предложить множество изменений и усовершенствований, входящих в объем настоящего изобретения, охарактеризованный приложенной формулой изобретения и ее эквивалентами.

Изобретение относится к области радиотехники, а именно к спутниковой навигации или спутниковому позиционированию, и может быть использовано в спутниковых навигационных системах. Технический результат заключается в обеспечении высокой скорости передачи битов навигационных данных. Для этого приемник в спутниковой навигационной системе, включающей группировку из множества спутников, каждый из которых передает сигнал, содержащий расширяющий код, имеет по меньшей мере одно устройство хранения кодов, которое содержит комбинаторную логику для хранения кода с памятью, содержащего фиксированный набор символов, включая дешифрование адресов, при этом хранящийся код с памятью соответствует расширяющему коду, входящему в сигнал, который передает спутник. Приемник дополнительно имеет коррелятор для осуществления корреляции входного сигнала и хранящегося расширяющего кода из одного устройства хранения кодов. Комбинаторная логика для хранения кодов с памятью и обеспечения адресных функций интегрирована на уровне физического компонента без четкого разделения между двумя этими функциями. 4 н. и 13 з.п. ф-лы, 6 ил.

1. Приемник для использования в спутниковой навигационной системе, включающей группировку из множества спутников, каждый из которых передает сигнал, содержащий расширяющий код, при этом приемник содержит

по меньшей мере одно устройство хранения кодов, имеющее комбинаторную логику для хранения кода с памятью, представляющего собой фиксированный набор импульсов и соответствующего расширяющему коду, включенному в сигнал, передаваемый спутником, причем упомянутая комбинаторная логика имеет функциональные возможности дешифрирования адресов для извлечения заданной части хранящегося кода с памятью, а внутренняя аппаратная конфигурация комбинаторной логики приспособлена для хранения набора данных и не содержит стандартных ячеек памяти, при этом комбинаторная логика для хранения кодов с памятью и обеспечения адресных функций интегрирована на уровне физического компонента без четкого разделения между двумя этими функциями, и

коррелятор для осуществления корреляции входного сигнала и хранящегося кода с памятью, извлеченного из устройства хранения кодов.

2. Приемник по п.1, в котором для каждого спутника в группировке спутников хранится отличающийся код с памятью.

3. Приемник по п.2, в котором в упомянутом по меньшей мере в одном устройстве хранения кодов хранятся коды с памятью для множества спутников, при этом оно способно выводить код с памятью для конкретного спутника.

4. Приемник по п.3, в котором различные коды с памятью для спутников хранятся в одном устройстве хранения кодов.

5. Приемник по п.2, в котором каждый код с памятью для сигнала спутника хранится в отдельном устройстве хранения кодов.

6. Приемник по п.2, имеющий множество каналов приема, а хранящийся код с памятью для спутника может подаваться в любой канал приема для корреляции с входным сигналом на этом канале приема.

7. Приемник по любому предшествующему пункту, в котором упомянутое по меньшей мере одно устройство хранения кодов дополнительно имеет генератор последовательности.

8. Приемник по п.7, в котором упомянутый генератор последовательности способен реагировать на сигнал приращения и выводить очередной поднабор из одного или нескольких импульсов из хранящегося кода с памятью.

9. Приемник по любому из пп.1-6, в котором каждый выходной сигнал по меньшей мере одного устройства хранения кодов содержит поднабор, отображающий множество импульсов упомянутого хранящегося кода с памятью.

10. Приемник по любому из пп.1-6, в котором расширяющие коды для спутников содержат заказные последовательности импульсов.

11. Приемник по любому из пп.1-6, в котором упомянутое по меньшей мере одно устройство хранения кодов выполнено на базе программируемой пользователем вентильной матрицы или на базе специализированной интегральной схемы.

12. Приемник по любому из пп.1-6, в котором упомянутое по меньшей мере одно устройство хранения кодов выполнено на базе того же полупроводникового устройства, что и упомянутый коррелятор.

13. Приемник по любому из пп.1-6, в котором в комбинаторной логике по меньшей мере в одном устройстве хранения кодов хранится множество кодов с памятью, при этом в комбинаторную логику вводят отличающийся входной сигнал для выбора одного из множества различных кодов с памятью для вывода из устройства хранения кодов.

14. Спутник для использования в спутниковой навигационной системе, включающей группировку из множества спутников, в которой каждый спутник передает сигнал, содержащий расширяющий код, и включает по меньшей мере одно устройство хранения кодов, имеющее комбинаторную логику для хранения кода с памятью, содержащего фиксированный набор импульсов и соответствующего расширяющему коду, включенному в сигнал, передаваемый спутником, причем упомянутая комбинаторная логика имеет функциональные возможности дешифрирования адресов для извлечения заданной части хранящегося кода с памятью, а внутренняя аппаратная конфигурация комбинаторной логики приспособлена для хранения набора данных и не содержит стандартных ячеек памяти, при этом комбинаторная логика для хранения кодов с памятью и обеспечения адресных функций интегрирована на уровне физического компонента без четкого разделения между двумя этими функциями.

15. Способ обеспечения работы приемника в спутниковой навигационной системе, включающей группировку из множества спутников, в которой каждый спутник передает сигнал, содержащий расширяющий код, при этом способ включает шаги, на которых:

обеспечивают по меньшей мере одно устройство хранения кодов, включающее комбинаторную логику для хранения кода с памятью, содержащего фиксированный набор импульсов и соответствующего расширяющему коду, входящему в сигнал, который передает спутник, причем упомянутая комбинаторная логика имеет функциональные возможности дешифрирования адресов для извлечения заданной части хранящегося кода с памятью, а внутренняя аппаратная конфигурация комбинаторной логики приспособлена для хранения набора данных и не содержит стандартных ячеек памяти, при этом комбинаторная логика для хранения кодов с памятью и обеспечения адресных функций интегрирована на уровне физического компонента без четкого разделения между двумя этими функциями, и

осуществляют корреляцию входного сигнала и хранящегося кода с памятью, извлеченного по меньшей мере из одного устройства хранения кодов.

16. Способ выполнения приемника для спутниковой навигационной системы, включающей группировку из множества спутников, каждый из которых передает сигнал, содержащий расширяющий код, при осуществлении которого:

определяют расширяющий код спутника для хранения в приемнике,

обеспечивают в приемнике по меньшей мере одно устройство хранения кодов, содержащее комбинаторную логику для хранения кода с памятью, содержащего фиксированный набор импульсов, соответствующих расширяющему коду спутника, при этом упомянутая комбинаторная логика имеет функциональные возможности дешифрирования адресов для извлечения заданной части хранящегося кода с памятью, а внутренняя аппаратная конфигурация комбинаторной логики приспособлена для хранения набора данных и не содержит стандартных ячеек памяти, при этом комбинаторная логика для хранения кодов с памятью и обеспечения адресных функций интегрирована на уровне физического компонента без четкого разделения между двумя этими функциями.

17. Способ по п.16, в котором упомянутое обеспечение по меньшей мере одного устройства хранения кодов включает создание описания фиксированного набора импульсов на языке описания аппаратных средств и реализацию упомянутого описания с использованием логического синтеза.

| US 4642647 A, 10.02.1987 | |||

| US 4876659 A, 24.10.1989 | |||

| RU 98108445 A, 10.05.2000 | |||

| RU 96115941 A, 20.02.1999 | |||

| Ребристый каток | 1922 |

|

SU121A1 |

| A.Koch "Structured Design Implementation - a Strategy for Implementing Regular Datapath on FPGAs", 1996. | |||

Авторы

Даты

2011-12-27—Публикация

2006-03-09—Подача