Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в радиоприемных устройствах, фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Аналоговый смеситель сигналов (АСС) является базовым узлом современных систем приема и обработки сигналов ВЧ- и СВЧ-диапазонов.

Аналоговый смеситель сигналов современных систем связи и телекоммуникаций реализуется, в основном, на базе перемножающей ячейки Гильберта, которая совершенствовалась в более чем 50 патентах ведущих микроэлектронных фирм (см., например, [1-48]). Предлагаемое изобретение относится к данному классу устройств. В этом смысле АСС является базовым функциональным узлом современной микроэлектроники, определяющим качественные показатели многих систем связи.

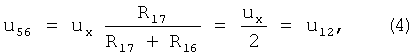

Ближайшим прототипом заявляемого устройства является аналоговый смеситель сигналов фиг.1, рассмотренный в патентной заявке фирмы Sharp US №20060066362, фиг. 15, содержащий первый 1 и второй 2 входные транзисторы, объединенные эмиттеры которых связаны с первым 3 выходом преобразователя «напряжение-ток» 4 канала «Y», третий 5 и четвертый 6 входные транзисторы, объединенные эмиттеры которых соединены со вторым 7 выходом преобразователя «напряжение-ток» канала «Y», согласованного с первой 8 шиной источника питания, причем база третьего 5 входного транзистора соединена с базой второго 2 входного транзистора, первый 9 двухполюсник коллекторной нагрузки, включенный между первым 10 выходом устройства, связанным с коллектором третьего 5 входного транзистора и второй 11 шиной источника питания, второй 12 двухполюсник коллекторной нагрузки, включенный между вторым 13 выходом устройства, связанным с коллектором четвертого 6 выходного транзистора и второй 11 шиной источника питания, источник сигнала канала «X» 14, связанный по переменному току первым выводом с общей шиной 15 источника питания и базой четвертого 6 входного транзистора.

Существенный недостаток известного смесителя состоит в том, что он характеризуется повышенной погрешностью перемножения (смешения) двух сигналов, обусловленной его архитектурой.

Основная задача предлагаемого изобретения состоит в снижении погрешности смешения (перемножения) двух сигналов по каналу «X» и каналу «Y».

Поставленная задача решается тем, что в АСС фиг.1, содержащим 1 и второй 2 входные транзисторы, объединенные эмиттеры которых связаны с первым 3 выходом преобразователя «напряжение-ток» 4 канала «Y», третий 5 и четвертый 6 входные транзисторы, объединенные эмиттеры которых соединены со вторым 7 выходом преобразователя «напряжение-ток» канала «Y», согласованного с первой 8 шиной источника питания, причем база третьего 5 входного транзистора соединена с базой второго 2 входного транзистора, первый 9 двухполюсник коллекторной нагрузки, включенный между первым 10 выходом устройства, связанным с коллектором третьего 5 входного транзистора и второй 11 шиной источника питания, второй 12 двухполюсник коллекторной нагрузки, включенный между вторым 13 выходом устройства, связанным с коллектором четвертого 6 выходного транзистора и второй 11 шиной источника питания, источник сигнала канала «X» 14, связанный по переменному току первым выводом с общей шиной 15 источника питания и базой четвертого 6 входного транзистора, предусмотрены новые элементы и связи - второй вывод источника сигнала канала «X» 14 соединен с базой первого 1 входного транзистора и первым выводом дополнительного резистора 16, второй вывод первого 16 дополнительного резистора соединен с первым выводом второго 17 дополнительного резистора, второй вывод которого подключен по переменному току к общей шине 15 источника питания и базе четвертого 6 входного транзистора, причем коллектор второго 2 входного транзистора соединен с коллектором третьего 5 входного транзистора, коллектор первого 1 входного транзистора связан с коллектором четвертого 6 входного транзистора, а второй вывод первого 16 дополнительного резистора и первый вывод второго 17 дополнительного резистора связаны с объединенными базами второго 2 и третьего 5 входных транзисторов.

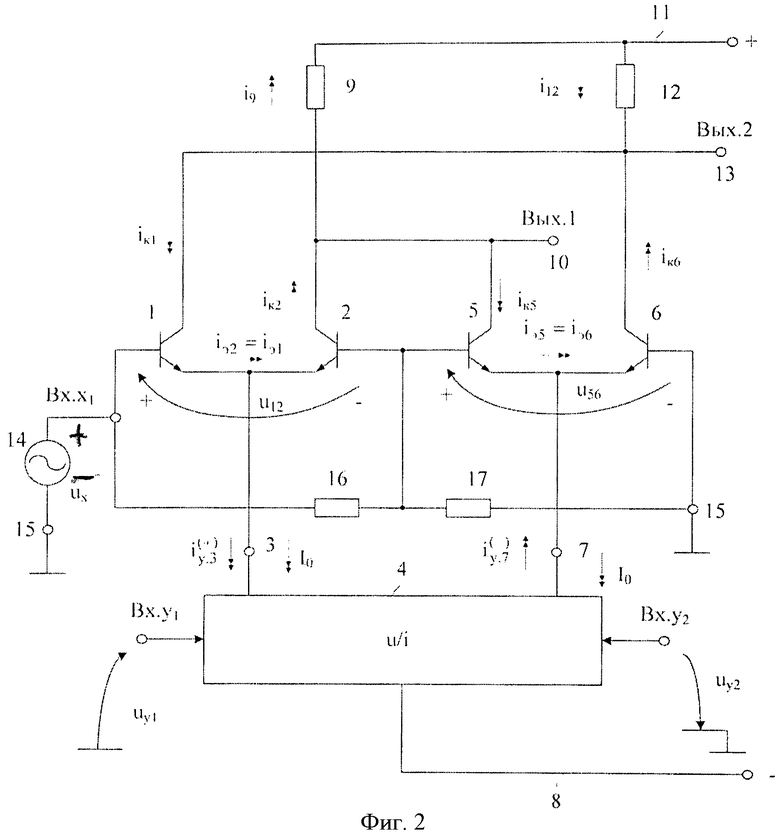

На фиг.1 показана схема АСС-прототипа, а на фиг.2 - схема заявляемого АСС в соответствии с п.1 формулы изобретения.

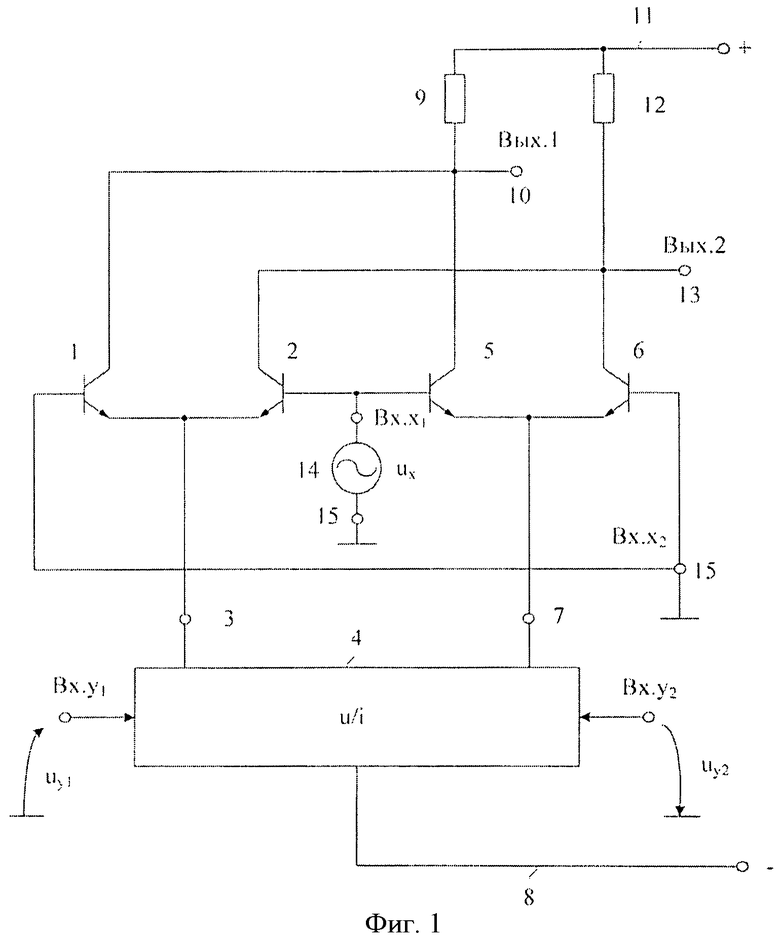

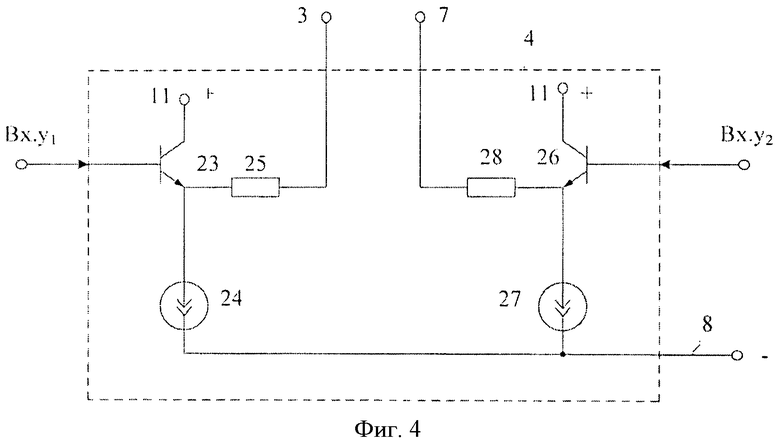

На фиг.3 и фиг.4 показаны типовые варианты построения преобразователя «напряжение-ток» 4 канала «Y».

На фиг.5 представлена схема АСС в соответствии с п.2 формулы изобретения.

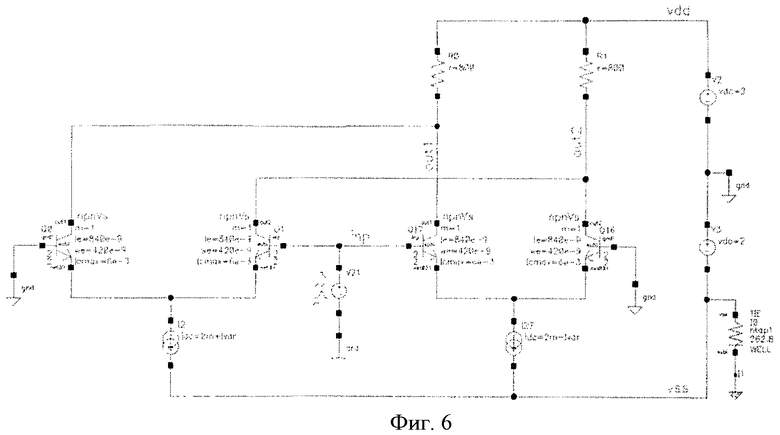

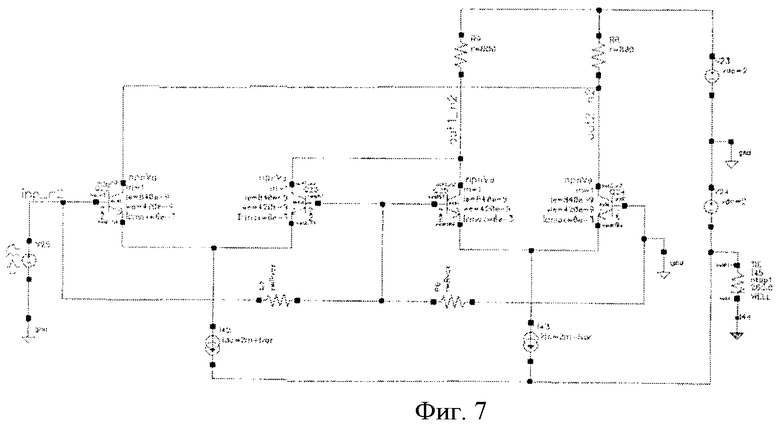

На фиг.6 приведена схема АСС-прототипа фиг.1 в среде компьютерного моделирования Cadence на моделях SiGe интегральных транзисторов, а на фиг.7 - схема АСС фиг.2 в среде компьютерного моделирования Cadence на моделях SiGe интегральных транзисторов.

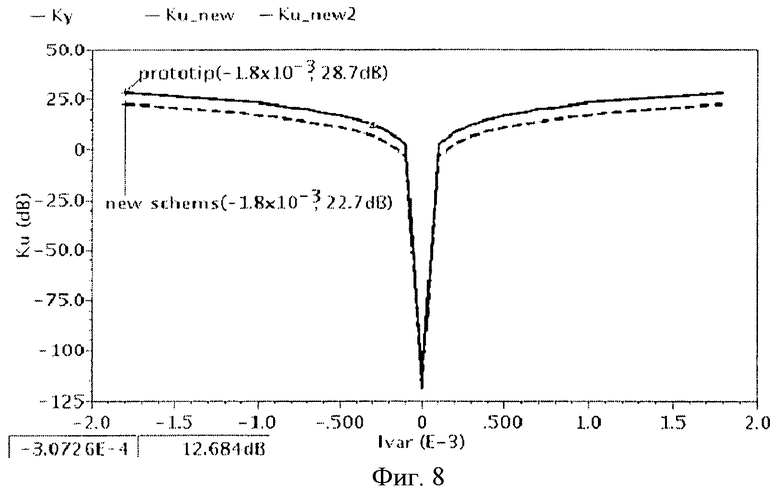

На фиг.8 показана зависимость модуля коэффициента усиления сравниваемых схем фиг.6 и фиг.7 от величины токов управления по выходам 3 и 7 преобразователя «напряжение-ток» канала «Y».

На фиг.9 приведена схема АСС фиг.5, соответствующая п.2 формулы изобретения, в среде компьютерного моделирования Cadence на моделях SiGe интегральных транзисторов.

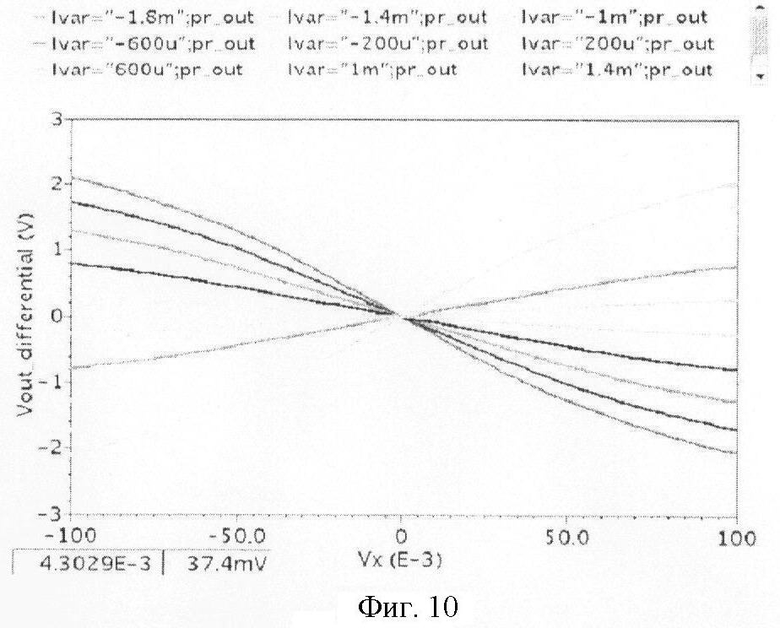

На фиг.10 приведена зависимость выходного дифференциального напряжения АСС-прототипа фиг.6 от напряжения источника сигнала по каналу «X» при разных величинах токов управления по выходам 3 и 7 преобразователя «напряжение-ток» 4 канала «Y».

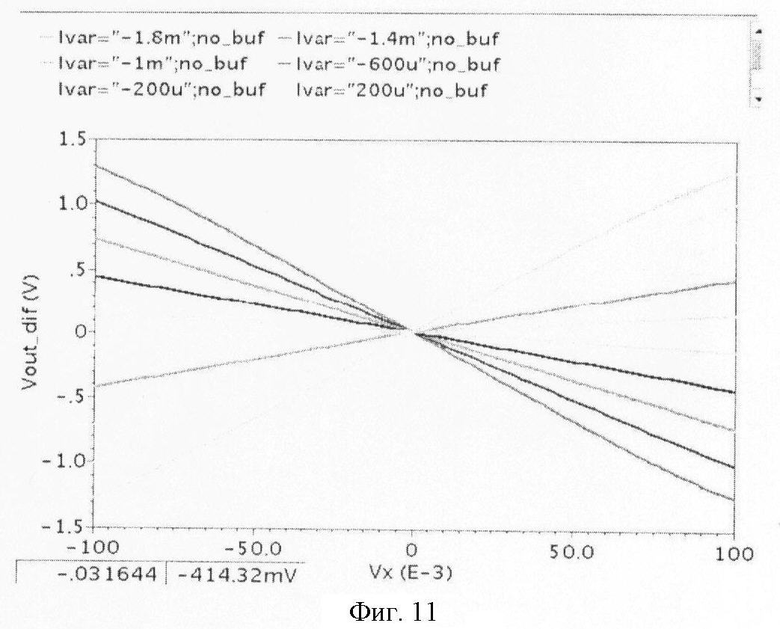

На фиг.11 приведена зависимость выходного дифференциального напряжения заявляемого АСС фиг.7 без дополнительного буферного усилителя 29 от напряжения источника сигнала ux, по каналу «X» при разных величинах токов управления по выходам 3 и 7 преобразователя «напряжение-ток» канала «Y».

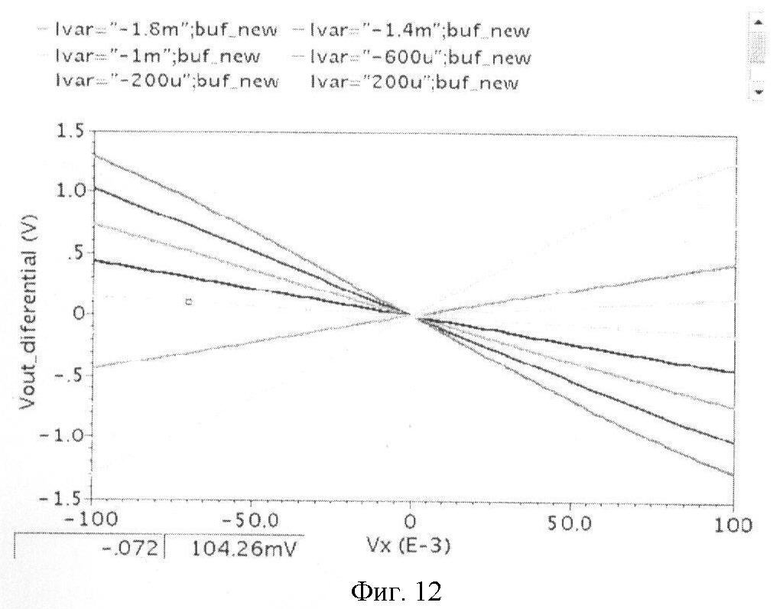

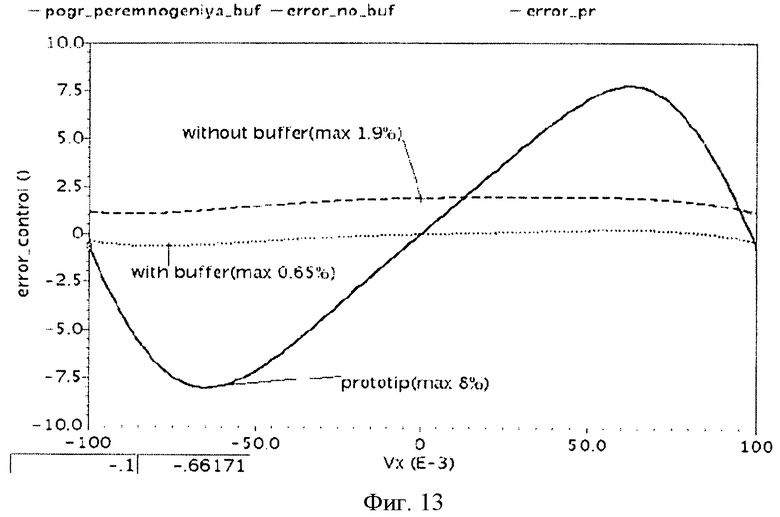

На фиг.12 приведена зависимость выходного дифференциального напряжения заявляемого АСС фиг.5 с дополнительным буферным усилителем 29 от напряжения источника сигнала ux по каналу «X» при разных величинах токов управления по выходам 3 и 7 преобразователя «напряжение-ток» канала «Y». Сравнительный анализ фиг.10, фиг.11, фиг.12 показывает, что заявляемые модификации АСС фиг.7 и фиг.9 отличаются от прототипа фмг.6 большей линейностью характеристик, определяющих его «перемножающие» свойства. Данный вывод подтверждается фиг.13, на которой показаны графики ошибки перемножения трех сравниваемых схем АСС: классического АСС фиг.6 (максимальная погрешность перемножения 8%), заявляемого АСС фиг.7 без буферного усилителя (максимальная погрешность 1,9%) и заявляемого АСС с буферным усилителем фиг.9 (максимальная погрешность 0,65%).

Заявляемый АСС фиг.2 содержит первый 1 и второй 2 входные транзисторы, объединенные эмиттеры которых связаны с первым 3 выходом преобразователя «напряжение-ток» 4 канала «Y», третий 5 и четвертый 6 входные транзисторы, объединенные эмиттеры которых соединены со вторым 7 выходом преобразователя «напряжение-ток» канала «Y», согласованного с первой 8 шиной источника питания, причем база третьего 5 входного транзистора соединена с базой второго 2 входного транзистора, первый 9 двухполюсник коллекторной нагрузки, включенный между первым 10 выходом устройства, связанным с коллектором третьего 5 входного транзистора и второй 11 шиной источника питания, второй 12 двухполюсник коллекторной нагрузки, включенный между вторым 13 выходом устройства, связанным с коллектором четвертого 6 выходного транзистора и второй 11 шиной источника питания, источник сигнала канала «X» 14, связанный по переменному току первым выводом с обшей шиной 15 источника питания и базой четвертого 6 входного транзистора. Второй вывод источника сигнала канала «X» 14 соединен с базой первого 1 входного транзистора и первым выводом дополнительного резистора 16, второй вывод первого 16 дополнительного резистора соединен с первым выводом второго 17 дополнительного резистора, второй вывод которого подключен по переменному току к обшей шине 15 источника питания и базе четвертого 6 входного транзистора, причем коллектор второго 2 входного транзистора соединен с коллектором третьего 5 входного транзистора, коллектор первого 1 входного транзистора связан с коллектором четвертого 6 входного транзистора, а второй вывод первого 16 дополнительного резистора и первый вывод второго 17 дополнительного резистора связаны с объединенными базами второго 2 и третьего 5 входных транзисторов.

На фиг.5, в соответствии с п.2 формулы изобретения, второй вывод первого 16 дополнительного резистора и первый вывод второго 17 дополнительного резистора связаны с объединенными базами второго 2 и третьего 5 входных транзисторов через дополнительный буферный усилитель 29. Функции буферного усилителя 29 могут выполнять классические эмиттерные повторители на n-p-n и p-n-p транзисторах и операционные усилители со 100% отрицательной обратной связью.

Преобразователь «напряжение-ток» 4 (фиг.3) содержит транзисторы 18 и 19, статический режим которых устанавливается двухполюсниками 21, 22, а также резистор обратной связи 20.

В схеме преобразователя фиг.4 используется транзисторы 23 и 26, а также двухполюсники 24, 27 и масштабирующие резисторы 25, 28.

Рассмотрим работу АСС фиг.2.

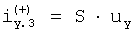

Для реализации функции смешения (перемножения) двух напряжений ux и uy в схеме фиг.2 необходимо с помощью преобразователя «напряжение-ток» 4 обеспечить преобразование напряжения uy=uy1=uy2 в канале «Y» с крутизной S в два противофазно изменяющихся тока выходов 3 и 7  ,

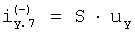

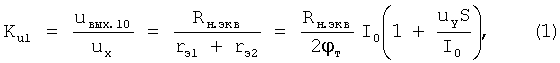

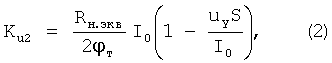

,  и управление этими токами величиной коэффициента усиления по напряжению каскадов на транзисторах 1, 2 и 5, 6. В схеме фиг.2 при увеличении суммарного тока эмиттерной цепи транзисторов 1 и 2 их коэффициент усиления по напряжению увеличивается

и управление этими токами величиной коэффициента усиления по напряжению каскадов на транзисторах 1, 2 и 5, 6. В схеме фиг.2 при увеличении суммарного тока эмиттерной цепи транзисторов 1 и 2 их коэффициент усиления по напряжению увеличивается

а транзисторов 5 и 6 уменьшается

где Rн.экв - эквивалентное сопротивление нагрузки.

Поэтому дифференциальное выходное напряжение АСС пропорционально произведению ux и uy:

Замечательная особенность схемы фиг.2 - подавление передачи сигнала uy на выходы 10 и 13. Действительно, при изменении тока  в эмиттерах транзисторов 1 и 2 их коллекторные токи изменяются пропорционально uy. Однако противофазно изменяются и коллекторные токи транзисторов 5 и 6, что компенсирует соответствующее приращение тока коллектора транзистора 1 (2) и стабилизирует статическое напряжение на двухполюснике 9 (12)

в эмиттерах транзисторов 1 и 2 их коллекторные токи изменяются пропорционально uy. Однако противофазно изменяются и коллекторные токи транзисторов 5 и 6, что компенсирует соответствующее приращение тока коллектора транзистора 1 (2) и стабилизирует статическое напряжение на двухполюснике 9 (12)

Напряжение ux источника сигнала 14 канала «X» делится между дополнительными резисторами 16 и 17:

где R17=R16 - сопротивления резисторов 16 и 17.

В результате, напряжение u12 «подзапирает» транзистор 1 и «приоткрытвает» транзистор 2. Аналогичное влияние на транзисторы 5 и 6 оказывает напряжение u56. Поэтому коллекторные токи транзисторов 1 и 5 увеличиваются под влиянием ux, коллекторные токи транзисторов 2 и 6 - уменьшаются, а направления результирующих токов в двухполюсниках 9 и 12 зависят от численных значений iк2 и iк5 (iк1 и iк6), функционально связанных с токами выходов 3 и 7 преобразователя «напряжение-ток» канала «Y».

Сравнительный анализ фиг.10, фиг.11, фиг.12 позволяет сделать вывод о том, что заявляемые модификации АСС фиг.7 и фиг.9 отличаются от прототипа фиг.6 большей линейностью характеристик, определяющих его «перемножающие» свойства. Действительно, как показывает сравнительное компьютерное моделирование фиг.13, на котором приведены графики ошибки перемножения трех сравниваемых схем АСС - классического АСС фиг.6 (максимальная погрешность перемножения 8%), заявляемого АСС фиг.7 без буферного усилителя (максимальная погрешность 1,9%) и заявляемого АСС с буферным усилителем фиг.9 (максимальная погрешность 0,65%), предлагаемое техническое решение (фиг.9, фиг.8) отличается от прототипа более высокой точностью. При этом погрешность перемножения (смешения) сигналов ux и uy в заявляемом АСС при малых ux (|ux|<100 мВ) не превышает 0,65% (в прототипе - 8%). Для существенного расширения динамического диапазона перемножаемых сигналов ux и uy следует использовать их предварительное логарифмирование.

В СВЧ-смесителях сигналов фиг.2 дополнительные резисторы 16 и 17 могут выполнять функции устройств согласования сигнала 14 ux и АСС с заданным волновым сопротивлением, например 50 Ом.

Таким образом, предлагаемое техническое решение является дальнейшим развитием широко распространенного смесителя Гильберта [1-48] и характеризуется более высокими качественными параметрами.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5.329.189, фиг.2.

2. Патентная заявка США №2008/0074188, фиг.3.

3. Патент США №6.229.395, фиг.2.

4. Патентная заявка США №2006/0232334, фиг.2.

5. Патент США №7.676.212.

6. Патентная заявка США №2006/0170494.

7. Патентная заявка США №2006/0066362, фиг.15.

8. Патент США №7.653.372, фиг.1.

9. Патентная заявка США №2010/0056095.

10. Патент EP 1.480.333, фиг.17.

11. Патент CN 101849353.

12. Патентная заявка США №2010/141325.

13. Патентная заявка США №2008/0180156, фиг.11.

14. Патент США №7.812.775, фиг.20.

15. Патент EP 2235559, фиг.3.

16. Патентная заявка США №2003/0155959.

17. Патент США №5.825.231, фиг.1.

18. Патент СВ 2.318.470, H03F 3/45.

19. Патент ЕР 1.369.992.

20. Патент США №5.874.857.

21. Патент США №6.456.142, фиг.8.

22. Патент США №3.931.583, фиг.9.

23. Патентная заявка США №2007/0139114, фиг.1.

24. Патентная заявка США №2005/0073362, фиг.1.

25. Патент США №5.057.787.

26. Патентная заявка WO 2004/041298.

27. Патент США №5.389.840, фиг.1А.

28. Патент США №5.883.539, фиг.1.

29. Патентная заявка США №2005/0052239.

30. Патент США №5.151.625, фиг.1.

31. Патент США №4.458.211, фиг.5.

32. Патентная заявка США №2005/0030096, фиг.6.

33. Патентная заявка США №2007/0090876.

34. Патент США №6.727.755.

35. Патент США №5.552.734, фиг.13, фиг.16.

36. Патент США №5.767.727.

37. Патент США №5.115.409.

38. Патентная заявка США №2005/0231283, фиг.1.

39. Патент США №5.151.624. фиг.1, фиг.2.

40. Патент США №4.704.738.

41. Патент США №4.480.337.

42. Патент США №6.211.718, фиг.1, фиг.2.

43. Патент США №5.151.624.

44. Патент США №5.329.189.

45. Патент США №5.331.289.

46. Патент GB №2.323.728.

47. Патентная заявка США №2008/0122540, фиг.1.

48. Патент США №4.965.528.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2396595C2 |

| АНАЛОГОВЫЙ СМЕСИТЕЛЬ СИГНАЛОВ | 2012 |

|

RU2504072C1 |

| СМЕСИТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ | 2011 |

|

RU2439777C1 |

| АНАЛОГОВЫЙ СМЕСИТЕЛЬ ДВУХ СИГНАЛОВ | 2011 |

|

RU2458456C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421883C1 |

| АНАЛОГОВЫЙ СМЕСИТЕЛЬ ДВУХ СИГНАЛОВ | 2011 |

|

RU2450352C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2011 |

|

RU2439785C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И АНАЛОГОВЫЙ СМЕСИТЕЛЬ СИГНАЛОВ | 2013 |

|

RU2530259C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419190C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ ДВУХ СИГНАЛОВ | 2008 |

|

RU2389072C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в радиоприемных устройствах, фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Аналоговый смеситель сигналов (АСС) является базовым узлом современных систем приема и обработки сигналов ВЧ- и СВЧ-диапазонов. Технический результат заключается в снижении погрешности смешения (перемножения) двух сигналов по каналу «X» и каналу «Y». Аналоговый смеситель сигналов содержит с первого по четвертый входные транзисторы, первый и второй дополнительные резисторы, преобразователь «напряжение-ток», первый и второй двухполюсники коллекторной нагрузки. 1 з.п. ф-лы, 13 ил.

1. Аналоговый смеситель сигналов, содержащий первый (1) и второй (2) входные транзисторы, объединенные эмиттеры которых связаны с первым (3) выходом преобразователя «напряжение-ток» канала «Y» (4), третий (5) и четвертый (6) входные транзисторы, объединенные эмиттеры которых соединены со вторым (7) выходом преобразователя «напряжение-ток» канала «Y», согласованного с первой (8) шиной источника питания, причем база третьего (5) входного транзистора соединена с базой второго (2) входного транзистора, первый (9) двухполюсник коллекторной нагрузки, включенный между первым (10) выходом устройства, связанным с коллектором третьего (5) входного транзистора, и второй (11) шиной источника питания, второй (12) двухполюсник коллекторной нагрузки, включенный между вторым (13) выходом устройства, связанным с коллектором четвертого (6) выходного транзистора, и второй (11) шиной источника питания, источник сигнала канала «X» (14), связанный по переменному току первым выводом с общей шиной (15) источника питания и базой четвертого (6) входного транзистора, отличающийся тем, что второй вывод источника сигнала канала «X» (14) соединен с базой первого (1) входного транзистора и первым выводом дополнительного резистора (16), второй вывод первого (16) дополнительного резистора соединен с первым выводом второго (17) дополнительного резистора, второй вывод которого подключен по переменному току к общей шине (15) источника питания и базе четвертого (6) входного транзистора, причем коллектор второго (2) входного транзистора соединен с коллектором третьего (5) входного транзистора, коллектор первого (1) входного транзистора связан с коллектором четвертого (6) входного транзистора, а второй вывод первого (16) дополнительного резистора и первый вывод второго (17) дополнительного резистора связаны с объединенными базами второго (2) и третьего (5) входных транзисторов.

2. Аналоговый смеситель сигналов по п.1, отличающийся тем, что второй вывод первого (16) дополнительного резистора и первый вывод второго (17) дополнительного резистора связаны с объединенными базами второго (2) и третьего (5) входных транзисторов через дополнительный буферный усилитель (29).

| US 5587689 A, 24.12.1996 | |||

| US 6122497 A, 19.09.2000 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| СМЕСИТЕЛЬ ЧАСТОТ | 2004 |

|

RU2266610C1 |

Авторы

Даты

2012-01-27—Публикация

2011-02-11—Подача