Область техники

Настоящее изобретение относится к схеме возбуждения емкостной нагрузки, которая возбуждает емкостную нагрузку на основании входного напряжения, и к устройству отображения, включающему в себя схему возбуждения емкостной нагрузки.

Уровень техники

В качестве одного из способов уменьшения размера жидкокристаллического устройства отображения и снижения его энергопотребления известен способ объединенного формирования пиксельных схем и схем возбуждения пиксельных схем на одной и той же подложке. Далее, жидкокристаллическое устройство отображения, сформированное согласно этому способу, будет именоваться “жидкокристаллическим устройством отображения со встроенным драйвером”. В жидкокристаллическом устройстве отображения со встроенным драйвером схемы возбуждения формируются с использованием тонкопленочных транзисторов (далее именуемых TFT), выполненных из низкотемпературного поликремния, CG-кремния (кремния с непрерывной структурой кристаллов) и пр.

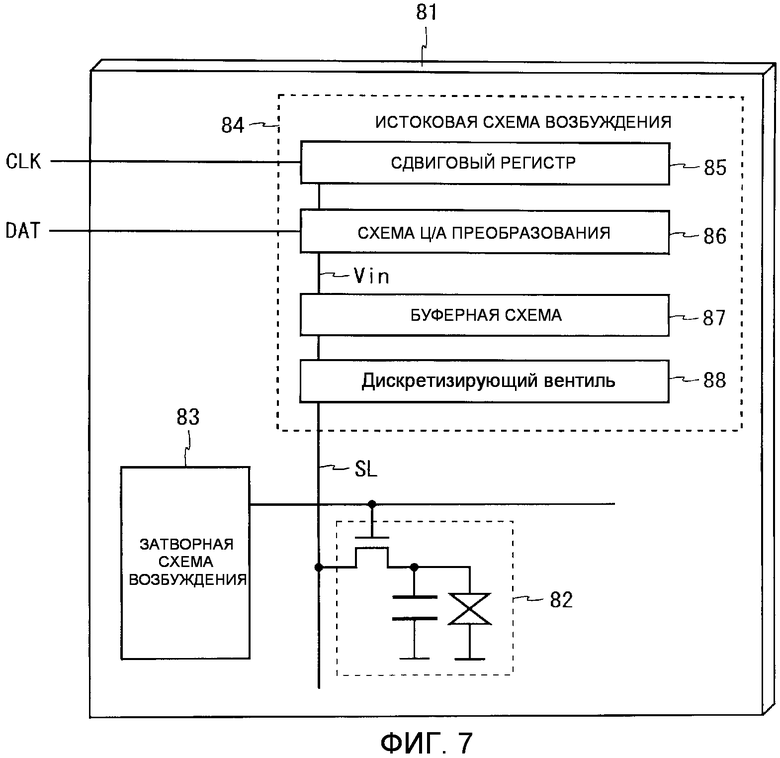

На фиг.7 показана блок-схема, демонстрирующая конфигурацию традиционного жидкокристаллического устройства отображения со встроенным драйвером. Жидкокристаллическое устройство отображения, показанное на фиг.7, включает в себя жидкокристаллическую панель 81, в которой пиксельные схемы 82, затворная схема возбуждения 83 и истоковая схема возбуждения 84 сформированы воедино на стеклянной подложке. Истоковая схема возбуждения 84 включает в себя сдвиговый регистр 85, схему Ц/А преобразования 86, буферную схему 87 и дискретизирующий вентиль 88. Буферная схема 87 возбуждает истоковую линию SL, подключенную к пиксельной схеме 82, на основании аналогового сигнала напряжения Vin, выводимого из схемы Ц/А преобразования 86. Дискретизирующий вентиль 88 производит переключение в зависимости от того, нужно ли подключать буферную схему 87 и истоковую линию SL. Дискретизирующий вентиль 88 предусмотрен для отключения истоковой линии SL от буферной схемы 87 и поддержания постоянного напряжения истоковой линии SL. Кроме того, дискретизирующий вентиль 88 используется для переключения и возбуждения совокупности истоковых линий SL. Переключение и возбуждение совокупности истоковых линий SL позволяет сократить количество истоковых линий SL схем Ц/А преобразования 86 и буферных схем 87.

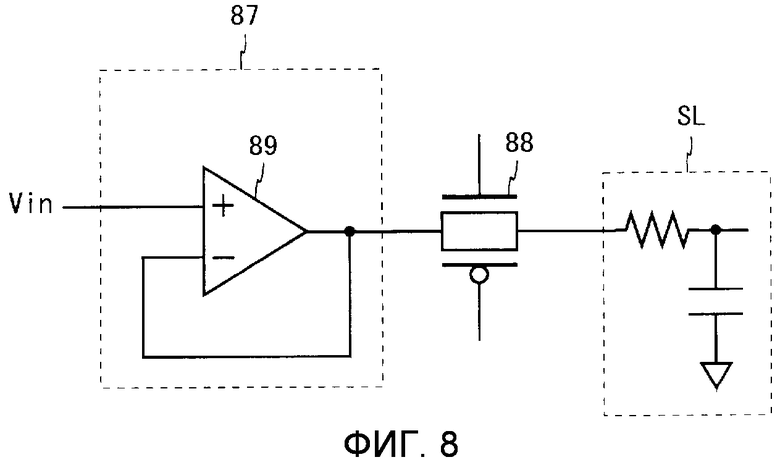

На фиг.8 показана принципиальная схема, демонстрирующая часть последовательных каскадов схемы Ц/А преобразования 86 жидкокристаллического устройства отображения, показанного на фиг.7. В схеме, показанной на фиг.8, буферная схема 87 выполнена с использованием операционного усилителя 89. На входной контакт положительной стороны операционного усилителя 89 подается аналоговый сигнал напряжения Vin, выводимый из схемы Ц/А преобразования 86. Выходной контакт операционного усилителя 89 подключен в рамках обратной связи к его входному контакту отрицательной стороны. Операционный усилитель 89 функционирует как усилитель единичного усиления и осуществляет управление таким образом, что напряжение истоковой линии SL равно аналоговому сигналу напряжения Vin.

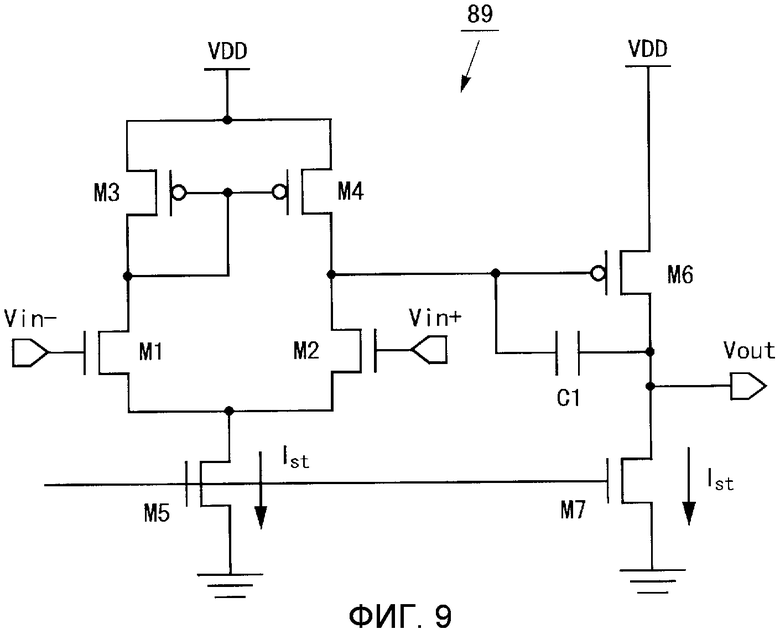

На фиг.9 показана принципиальная схема, демонстрирующая один пример операционного усилителя 89. Операционный усилитель 89, показанный на фиг.9, включает в себя TFT M1-M7 и конденсатор C1 и применяет усиление класса А к дифференциальным входным напряжениям Vin+ и Vin- для генерации выходного напряжения Vout. Осуществление усиления класса А в операционном усилителе 89 позволяет возбуждать истоковую линию SL на основании выходного напряжения Vout с малым искажением.

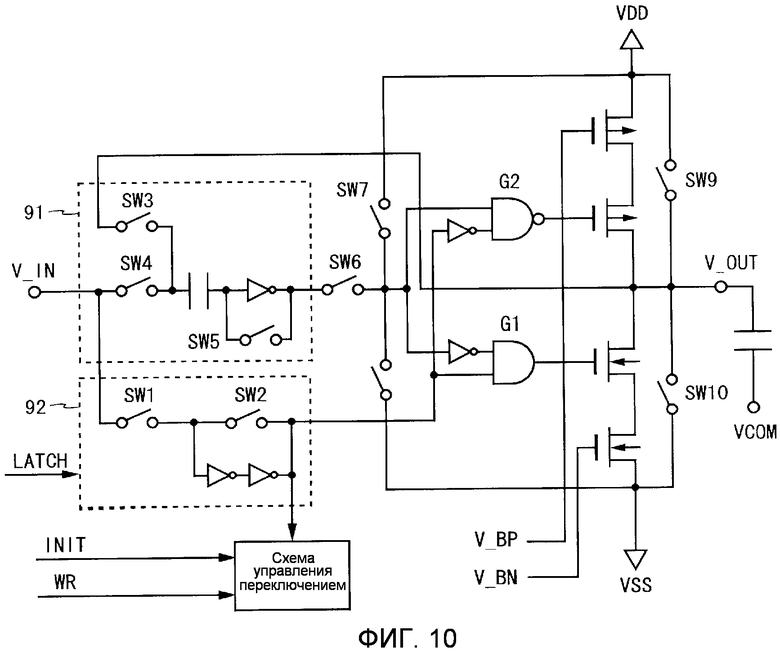

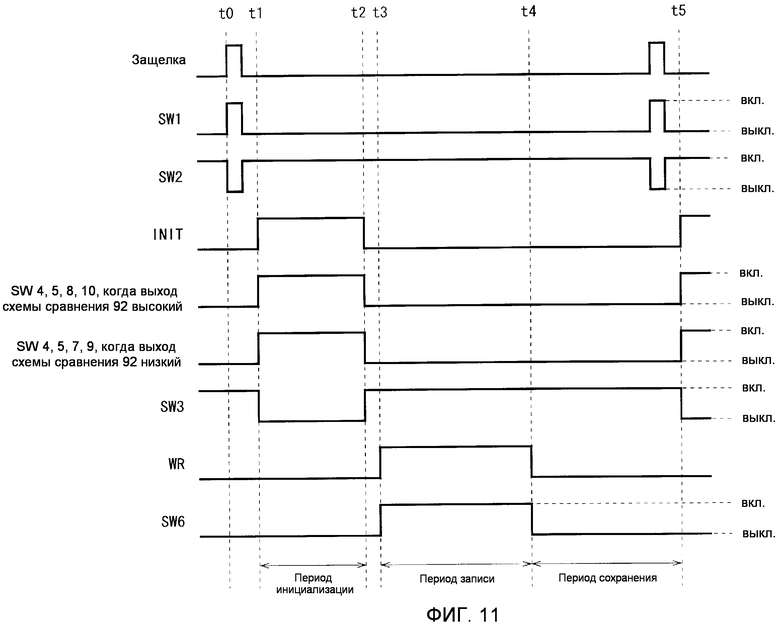

Методы, относящиеся к изобретению, настоящей заявки также описаны в следующих документах. В патентном документе 1 описана схема выходного каскада истоковой схемы возбуждения, показанной на фиг.10. Схема выходного каскада, показанная на фиг.10, осуществляет трехэтапную операцию первоначального установления, записи и сохранения в соответствии с диаграммой хронирования, показанной на фиг.11. Состояния переключателей SW7-SW10 изменяются в соответствии с высоким уровнем или низким уровнем выходного сигнала схемы компаратора 92. В патентных документах 2-4 описаны другие примеры истоковой схемы возбуждения, которая возбуждает истоковую линию на основании входного напряжения.

ПАТЕНТНЫЕ ДОКУМЕНТЫ

[Патентный документ 1] Выложенная патентная заявка Японии №2004-166039

[Патентный документ 2] Выложенная патентная заявка Японии №2001-222261

[Патентный документ 3] Выложенная патентная заявка Японии №2005-338131

[Патентный документ 4] Выложенная патентная заявка Японии №2006-133444

Сущность изобретения

Задачи изобретения

Истоковая схема возбуждения жидкокристаллического устройства отображения со встроенным драйвером имеет проблемы в том, что она имеет большое энергопотребление, подвержена изменению процесса, имеет большую площадь схемы и т.п. Например, в операционном усилителе 89, показанном на фиг.9, для осуществления усиления класса А, ток смещения Ist стабильно течет через TFT M5 и TFT M7. При использовании операционного усилителя, в котором течет установившийся ток, энергопотребление истоковой схемы возбуждения увеличивается. Кроме того, поскольку имеющееся напряжение общего режима в схеме дифференциального усилителя ограничено, рабочее напряжение схемы нужно увеличивать для обеспечения нужной производительности, в то же время удовлетворяя ограничению. Однако при увеличении рабочего напряжения энергопотребление схемы увеличивается. Кроме того, поскольку в дискретизирующем вентиле существуют емкостной компонент и резистивный компонент, электрическая мощность также потребляется в дискретизирующем вентиле. По вышеописанным причинам истоковая схема возбуждения имеет большое энергопотребление, что неблагоприятно.

Кроме того, когда TFT сформированы на стеклянной подложке, изменение (изменение процесса) легко происходит в характеристиках TFT (например, пороговых напряжениях). Изменения пороговых напряжений TFT приводят к изменению производительности операционного усилителя, сформированного с использованием TFT. Кроме того, напряжение смещения, подаваемое на операционный усилитель, будет изменяться. Производительность истоковой схемы возбуждения изменяется по вышеописанным причинам, что приводит к возникновению линейного шума на экране дисплея, что приводит к неблагоприятному снижению качества изображения экрана дисплея.

Во избежание снижения качества изображения экрана дисплея можно предусмотреть схему для компенсации изменения процесса. Однако добавление компенсационной схемы создает проблему в том, что при этом увеличивается площадь схемы истоковой схемы возбуждения. Кроме того, в истоковой схеме возбуждения предусмотрены дискретизирующий вентиль и его схема управления, что также увеличивает площадь схемы.

Таким образом, задачей настоящего изобретения является обеспечение малоразмерной схемы возбуждения емкостной нагрузки с низким энергопотреблением и устойчивой к изменению процесса, что предпочтительно для схемы выходного каскада истоковой схемы возбуждения в устройстве отображения со встроенным драйвером и пр., и устройства отображения, включающего в себя ее.

Решение задач

Согласно первому аспекту настоящего изобретения предусмотрена схема возбуждения емкостной нагрузки, которая возбуждает емкостную нагрузку на основании входного напряжения, включающая в себя: блок сравнения напряжений, который сравнивает входное напряжение, поступающее с входного контакта, и выходное напряжение, выводимое с выходного контакта, для вывода напряжения результата сравнения в соответствии с результатом сравнения; блок управления возбуждением, который выводит напряжение управления зарядом и напряжение управления разрядом, которые установлены на начальных уровнях, соответственно, в течение первого периода, и изменяются в соответствии с напряжением результата сравнения в течение второго периода; и двухтактный выходной блок, включающий в себя зарядную схему, которая заряжает емкостную нагрузку, подключенную к выходному контакту, на основании напряжения управления зарядом, и разрядную схему, которая разряжает емкостную нагрузку на основании напряжения управления разрядом, причем блок управления возбуждением избирательно оперирует зарядной схемой и разрядной схемой таким образом, что выходное напряжение становится равным входному напряжению.

Согласно второму аспекту настоящего изобретения в первом аспекте настоящего изобретения блок сравнения напряжений включает в себя: переключатель выбора входной стороны, который предусмотрен между входным контактом и заранее определенным узлом и переходит в состояние включения в течение первого периода; переключатель выбора выходной стороны, который предусмотрен между выходным контактом и узлом и переходит в состояние включения в течение второго периода; и схему компаратора, вход которой подключен к узлу, причем схема компаратора сравнивает входное напряжение в течение первого периода и выходное напряжение в течение второго периода для вывода напряжения результата сравнения.

Согласно третьему аспекту настоящего изобретения во втором аспекте настоящего изобретения схема компаратора включает в себя: инвертирующую схему; емкостной элемент, предусмотренный между входом инвертирующей схемы и узлом; и переключатель для короткого замыкания, который предусмотрен между входом и выходом инвертирующей схемы и переходит в состояние включения в течение первого периода, причем емкостной элемент поддерживает разность между входным напряжением и напряжением инверсии инвертирующей схемы в течение первого периода, и, в течение второго периода, инвертирующая схема выводит, в качестве напряжения результата сравнения, напряжение в соответствии с напряжением, полученным путем прибавления напряжения инверсии к разности между выходным напряжением и входным напряжением.

Согласно четвертому аспекту настоящего изобретения в первом аспекте настоящего изобретения в течение первого периода блок управления возбуждением устанавливает напряжение управления зарядом и напряжение управления разрядом на уровнях, при которых зарядная схема и разрядная схема не действуют, соответственно, и в течение второго периода, на основании напряжения результата сравнения, блок управления возбуждением устанавливает напряжение управления зарядом на уровне, при котором зарядная схема действует, когда выходное напряжение меньше входного напряжения, и устанавливает напряжение управления разрядом на уровне, при котором разрядная схема действует, когда выходное напряжение больше входного напряжения.

Согласно пятому аспекту настоящего изобретения в четвертом аспекте настоящего изобретения блок управления возбуждением включает в себя: схему усилителя зарядной стороны, которая выводит напряжение управления зарядом на зарядную схему; и схему усилителя разрядной стороны, которая выводит напряжение управления разрядом на разрядную схему.

Согласно шестому аспекту настоящего изобретения в пятом аспекте настоящего изобретения блок управления возбуждением дополнительно включает в себя: емкостной элемент зарядной стороны для обеспечения емкостной связи выхода блока сравнения напряжений и входа схемы усилителя зарядной стороны; емкостной элемент разрядной стороны для обеспечения емкостной связи выхода блока сравнения напряжений и входа схемы усилителя разрядной стороны; переключатель установки зарядной стороны, который переходит в состояние включения в течение первого периода для подачи напряжения отключения на вход схемы усилителя зарядной стороны; и переключатель установки разрядной стороны, который переходит в состояние включения в течение первого периода для подачи напряжения отключения на вход схемы усилителя разрядной стороны.

Согласно седьмому аспекту настоящего изобретения в первом аспекте настоящего изобретения в качестве зарядной схемы двухтактный выходной блок включает в себя переключатель для заряда, который предусмотрен между линией питания высоковольтной стороны и выходным контактом, и управляется с использованием напряжения управления зарядом, и в качестве разрядной схемы, двухтактный выходной блок включает в себя переключатель для разряда, который предусмотрен между линией питания низковольтной стороны и выходным контактом, и управляется с использованием напряжения управления разрядом.

Согласно восьмому аспекту настоящего изобретения в седьмом аспекте настоящего изобретения двухтактный выходной блок дополнительно включает в себя: переключатель для остановки заряда, который предусмотрен между линией питания высоковольтной стороны и выходным контактом последовательно с переключателем для заряда; и переключатель для остановки разряда, который предусмотрен между линией питания низковольтной стороны и выходным контактом последовательно с переключателем для разряда.

Согласно девятому аспекту настоящего изобретения предусмотрено устройство отображения, которое возбуждает сигнальную линию, подключенную к пиксельной схеме, с использованием схемы возбуждения емкостной нагрузки согласно любому из аспектов настоящего изобретения с первого по восьмой.

Преимущества изобретения

Согласно первому аспекту настоящего изобретения, избирательно оперируя зарядной схемой и разрядной схемой, входящими в состав двухтактного выходного блока, на основании результата сравнения входного напряжения и выходного напряжения для осуществления заряда и разряда емкостной нагрузки, выходное напряжение и входное напряжение можно сделать равными. Кроме того, избирательно оперируя зарядной схемой и разрядной схемой, можно препятствовать протеканию установившегося тока в схеме и, таким образом, можно снизить энергопотребление схемы. Кроме того, осуществляя заряд и разряд емкостной нагрузки, только когда выходное напряжение не равно входному напряжению, можно препятствовать расточительному энергопотреблению за счет заряда и разряда емкостной нагрузки. Поскольку в течение второго периода выходное напряжение устанавливается равным входному напряжению, не требуется схема для поддержания выходного напряжения (например, дискретизирующего вентиля), благодаря чему можно уменьшить энергопотребление, область и площадь схемы. Для блока сравнения напряжений, блока управления возбуждением и двухтактного выходного блока можно легко сформировать схемы, устойчивые к изменению процесса. Соответственно, можно сформировать малоразмерную схему возбуждения емкостной нагрузки с низким энергопотреблением и устойчивую к изменению процесса.

Согласно второму аспекту настоящего изобретения предпочтительно благодаря управлению состояниями двух переключателей, напряжение, вводимое в схему компаратора, переключается между в течение первого периода и в течение второго периода, и с использованием схемы компаратора, можно найти напряжение результата сравнения в соответствии с результатом сравнения между входным напряжением в течение первого периода и выходным напряжением в течение второго периода.

Согласно третьему аспекту настоящего изобретения в схеме компаратора, включающей в себя емкостной элемент, инвертирующую схему и переключатель, предпочтительно благодаря управлению состоянием переключателя, инвертирующая схема, в течение второго периода, выводит напряжение в соответствии с напряжением, полученным путем прибавления напряжения инверсии инвертирующей схемы (входного/выходного напряжения, когда вход и выход инвертирующей схемы закорочены) к разности между выходным напряжением и входным напряжением. Когда напряжение, выводимое из инвертирующей схемы, используется в качестве напряжения результата сравнения, напряжение управления зарядом и напряжение управления разрядом не подвергаются влиянию изменения порогового напряжения инвертирующей схемы. Соответственно, выходное напряжение можно сделать равным входному напряжению, не подвергая влиянию изменения порогового напряжения инвертирующей схемы. Следовательно, можно сформировать схему возбуждения емкостной нагрузки, устойчивую к изменению процесса.

Согласно четвертому аспекту настоящего изобретения в течение первого периода зарядная схема и разрядная схема останавливаются, и в течение второго периода зарядная схема действует, когда выходное напряжение меньше входного напряжения, и разрядная схема действует, когда выходное напряжение больше входного напряжения, благодаря чему, не изменяя выходное напряжение в течение первого периода, выходное напряжение можно сделать равным входному напряжению в течение второго периода.

Согласно пятому аспекту настоящего изобретения использование двух схем усилителя позволяет легко сформировать блок управления возбуждением, в котором в течение первого периода напряжение управления зарядом и напряжение управления разрядом установлены на соответствующие начальные уровни, и в течение второго периода напряжение управления зарядом и напряжение управления разрядом изменяются в соответствии с напряжением результата сравнения.

Согласно шестому аспекту настоящего изобретения в течение первого периода два переключателя установки переводятся в состояние включения для подачи напряжения отключения на входы соответствующих схем усилителя, благодаря чему напряжение управления зарядом и напряжение управления разрядом можно установить на соответствующие начальные уровни. В течение второго периода два переключателя установки переводятся в состояние выключения для подачи напряжения результата сравнения на входы соответствующих схем усилителя через емкостные элементы, благодаря чему напряжение управления зарядом и напряжение управления разрядом можно изменять в соответствии с напряжением результата сравнения.

Согласно седьмому аспекту настоящего изобретения переключатели предусмотрены между двумя типами линии питания и выходного контакта, соответственно, и управление ими осуществляется с использованием напряжения управления зарядом и напряжения управления разрядом, что позволяет легко сформировать двухтактный выходной блок, причем двухтактный выходной блок включает в себя зарядную схему, которая заряжает емкостную нагрузку на основании напряжения управления зарядом, и разрядную схему, которая разряжает емкостную нагрузку на основании напряжения управления разрядом. С использованием этого двухтактного выходного блока можно препятствовать протеканию установившегося тока в схеме, таким образом, снижая энергопотребление схемы.

Согласно восьмому аспекту настоящего изобретения переключатели добавлены между двумя типами линии питания и выходного контакта, соответственно, и предпочтительно управлять состояниями добавленных переключателей таким образом, чтобы период, когда осуществляются заряд и разряд емкостной нагрузки, был ограничен, что позволяет предотвратить отказ схемы и снизить энергопотребление.

Согласно девятому аспекту настоящего изобретения при возбуждении сигнальной линии, подключенной к пиксельной схеме, использование малоразмерной схемы возбуждения емкостной нагрузки с низким энергопотреблением и устойчивой к изменению процесса позволяет сформировать малоразмерное устройство отображения с низким энергопотреблением и высоким качеством изображения.

Краткое описание чертежей

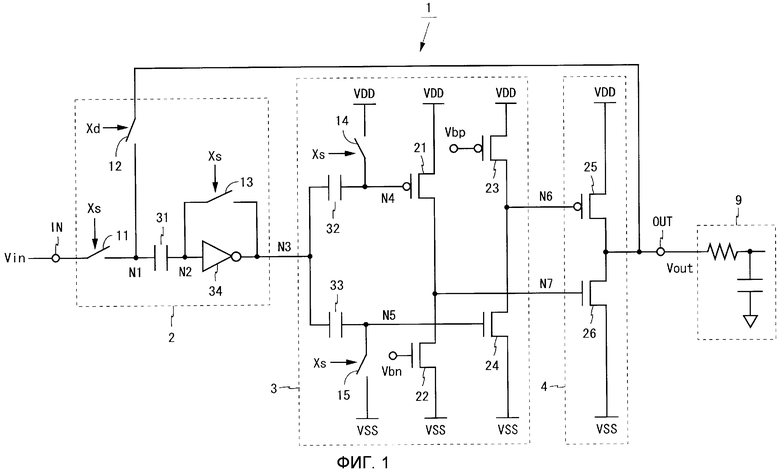

Фиг.1 - принципиальная схема буферной схемы двухтактного типа согласно варианту осуществления настоящего изобретения.

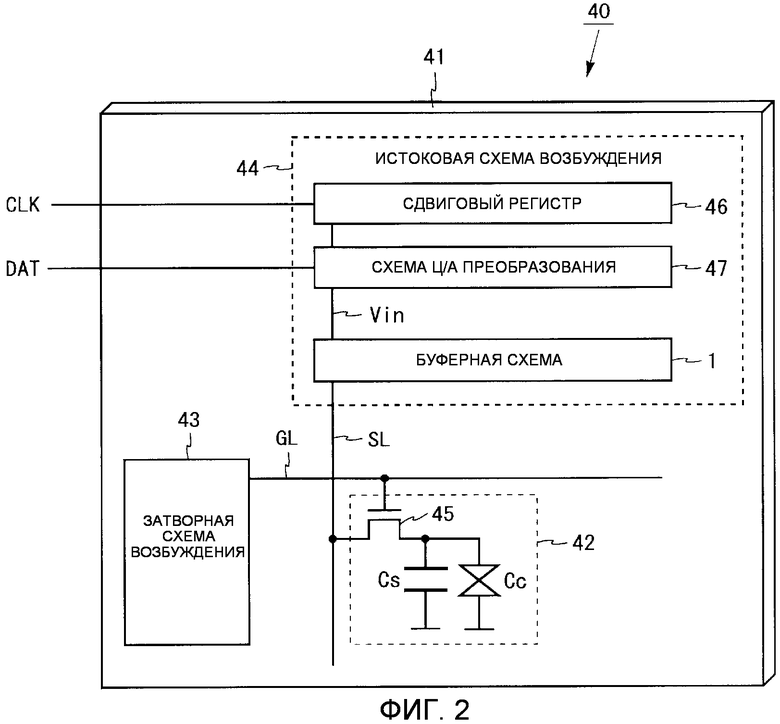

Фиг.2 - блок-схема, демонстрирующая конфигурацию жидкокристаллического устройства отображения со встроенным драйвером, включающего в себя буферную схему, показанную на фиг.1.

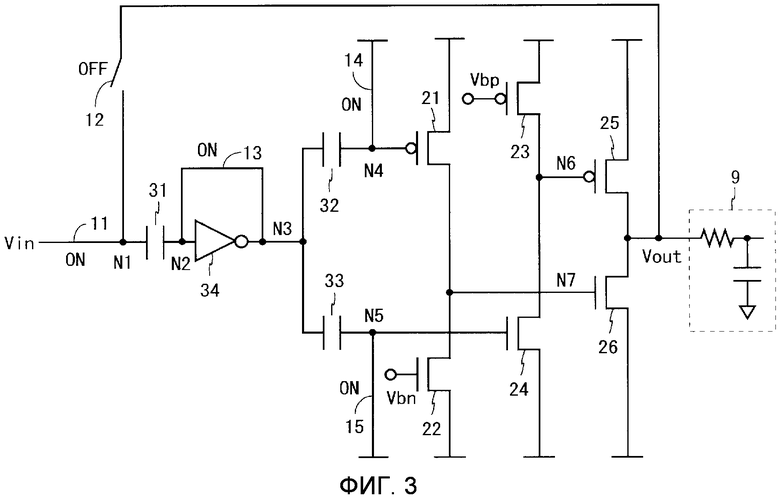

Фиг.3 - схема, демонстрирующая состояние переключателей в течение периода установки буферной схемы, показанной на фиг.1.

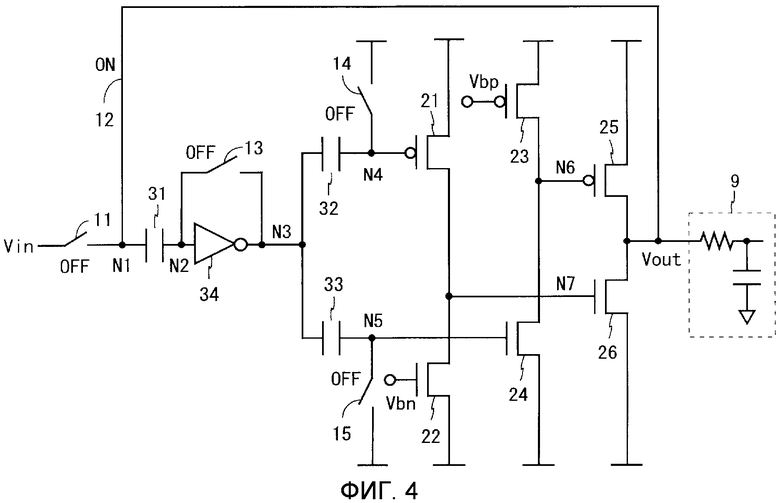

Фиг.4 - схема, демонстрирующая состояние переключателей в течение периода возбуждения буферной схемы, показанной на фиг.1.

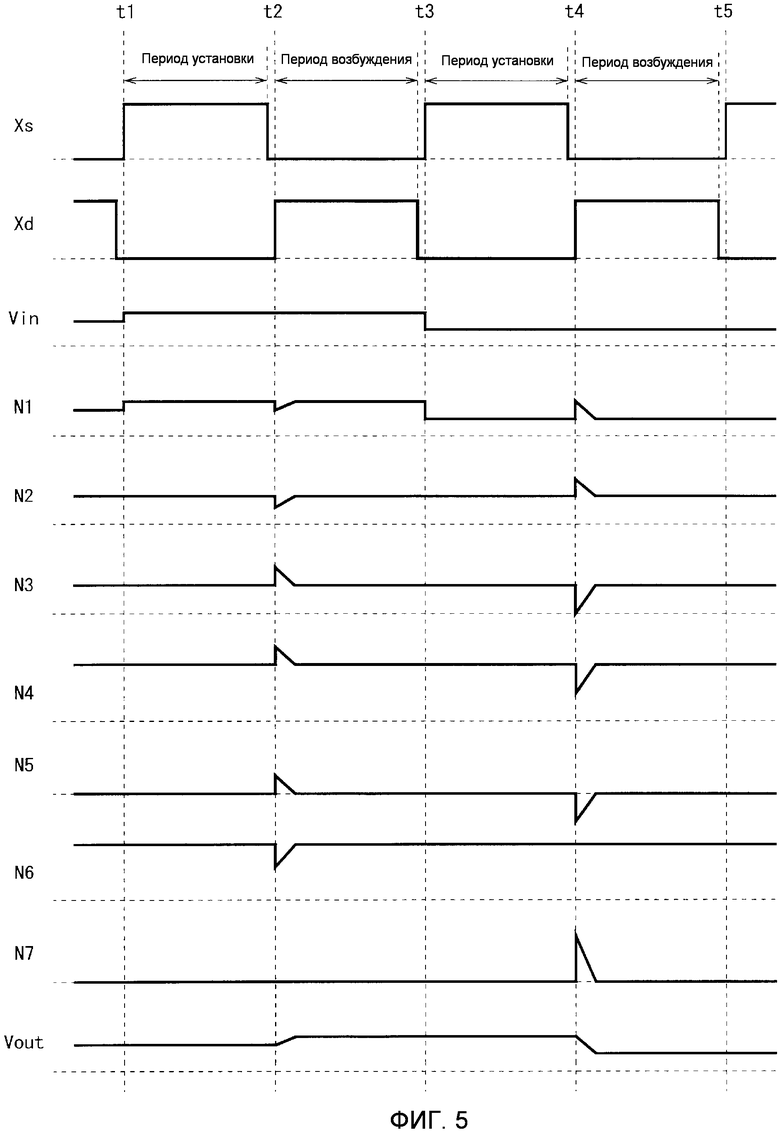

Фиг.5 - диаграмма хронирования буферной схемы, показанной на фиг.1.

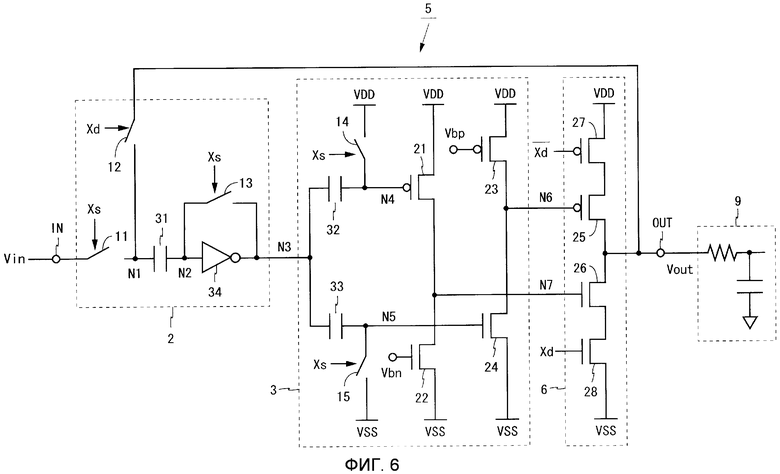

Фиг.6 - принципиальная схема буферной схемы двухтактного типа согласно модификации варианта осуществления настоящего изобретения.

Фиг.7 - блок-схема, демонстрирующая конфигурацию традиционного жидкокристаллического устройства отображения со встроенным драйвером.

Фиг.8 - принципиальная схема, демонстрирующая часть последовательных каскадов схемы Ц/А преобразования жидкокристаллического устройства отображения, показанного на фиг.7.

Фиг.9 - принципиальная схема, демонстрирующая один пример операционного усилителя, входящего в состав схемы, показанной на фиг.8.

Фиг.10 - принципиальная схема, демонстрирующая схему выходного каскада истоковой схемы возбуждения, описанной в документе.

Фиг.11 - диаграмма хронирования схемы выходного каскада, показанной на фиг.10.

Предпочтительные варианты осуществления изобретения

На фиг.1 показана принципиальная схема буферной схемы двухтактного типа согласно варианту осуществления настоящего изобретения. Буферная схема 1, показанная на фиг.1, является одним конкретным примером схемы возбуждения емкостной нагрузки настоящего изобретения и возбуждает емкостную нагрузку 9, подключенную к выходному контакту OUT, на основании напряжения, вводимого из входного контакта IN. Далее, напряжение, вводимое с входного контакта IN, именуется входным напряжением Vin, и напряжение, выводимое с выходного контакта OUT, именуется выходным напряжением Vout.

Буферная схема 1 используется, например, в качестве схемы выходного каскада истоковой схемы возбуждения, которая возбуждает истоковую линию (также именуемую сигнальной линией данных, сигнальной линией видео и пр.) в жидкокристаллическом устройстве отображения со встроенным драйвером (жидкокристаллическом устройстве отображения, в котором пиксельные схемы и их схемы возбуждения сформированы воедино на одной и той же подложке). На фиг.2 показана блок-схема, демонстрирующая конфигурацию жидкокристаллического устройства отображения со встроенным драйвером, включающего в себя буферную схему 1. Жидкокристаллическое устройство отображения 40, показанное на фиг.2, включает в себя жидкокристаллическую панель 41, в которой пиксельные схемы 42, затворная схема возбуждения 43 и истоковая схема возбуждения 44 сформированы воедино на стеклянной подложке. Схемы на стеклянной подложке сформированы с использованием TFT, выполненных из низкотемпературного поликремния, CG-кремния и пр.

В жидкокристаллической панели 41 сформированы совокупность затворных линий GL, параллельных друг другу, и совокупность истоковых линий SL, перпендикулярных затворным линиям GL и параллельных друг другу (на фиг.2 показаны одна затворная линия GL и одна истоковая линия SL). В соответствии с соответствующими пересечениями затворных линий GL и истоковых линий SL сформированы пиксельные схемы 42, каждая из которых включает в себя TFT 45, емкость жидкого кристалла Cc и дополнительную емкость Cs. Каждая пиксельная схема 42 подключена к соответствующей затворной линии GL и истоковой линии SL.

Кроме того, в жидкокристаллической панели 41, в качестве схем возбуждения пиксельных схем 42, сформированы затворная схема возбуждения 43 и истоковая схема возбуждения 44. Затворная схема возбуждения 43 выбирает одну затворную линию из совокупности затворных линий GL. Истоковая схема возбуждения 44 подает на истоковые линии SL напряжения, подлежащие записи в пиксельные схемы 42, подключенные к выбранной затворной линии GL. Истоковая схема возбуждения 44 включает в себя сдвиговый регистр 46, схему Ц/А преобразования 47 и буферную схему 1 согласно настоящему варианту осуществления. Схема Ц/А преобразования 47 преобразует цифровые видеоданные DAT, поступающие извне жидкокристаллического устройства отображения 40, в аналоговый сигнал напряжения Vin. Буферная схема 1 подключена к истоковой линии SL, которая является емкостной нагрузкой, для возбуждения истоковой линии SL на основании аналогового сигнала напряжения Vin, выводимого из схемы Ц/А преобразования 47. Поскольку буфер 1 способен производить переключение в зависимости от того, нужно ли подключать истоковую линию SL, истоковую схему возбуждения 44, включающую в себя буферную схему 1, не требуется снабжать дискретизирующим вентилем.

Ниже, согласно фиг.1, приведено подробное описание буферной схемы 1. Как показано на фиг.1, буферная схема 1 включает в себя блок 2 сравнения напряжений, блок 3 управления возбуждением и двухтактный выходной блок 4. Эти схемы сформированы с использованием переключателей 11-15, TFT 21-26, конденсаторов 31-33 и инвертирующей схемы 34. TFT 21, 23 и 25 являются TFT P-типа и TFT 22, 24 и 26 являются TFT N-типа.

Блок 2 сравнения напряжений включает в себя переключатели 11-13 и конденсатор 31 и инвертирующую схему 34. Переключатель 11 предусмотрен между входным контактом IN и одним электродом конденсатора 31 (электродом на левой стороне на фиг.1. Далее именуемый электродом входной стороны). Переключатель 12 предусмотрен между выходным контактом OUT и электродом входной стороны конденсатора 31. Другой электрод конденсатора 31 подключен ко входу инвертирующей схемы 34. Переключатель 13 предусмотрен между входом и выходом инвертирующей схемы 34. Переключатель 13, конденсатор 31 и инвертирующая схема 34 образуют схему компаратора, которая сравнивает два последовательно вводимые напряжения.

Блок 3 управления возбуждением включает в себя переключатели 14 и 15, TFT 21-24 и конденсаторы 32 и 33. TFT 21 и 22 соединены последовательно и установлены между линией питания высоковольтной стороны и линией питания низковольтной стороны (в дальнейшем первая именуется линией VDD и последняя именуется линией VSS). В частности, стоковые контакты TFT 21 и 22 подключены друг к другу, и истоковые контакты TFT 21 и 22 подключены к линии VDD и линии VSS, соответственно. Заранее определенное напряжение смещения Vbn поступает на затворный контакт TFT 22, и TFT 22 функционирует как транзистор со смещением. Конденсатор 32 предусмотрен между выходом инвертирующей схемы 34 и затворным контактом TFT 21. Переключатель 14 предусмотрен между линией VDD и затворным контактом TFT 21. Таким образом, TFT 21 и 22 образуют схему усилителя (далее именуемую схемой усилителя разрядной стороны), и вход схемы усилителя разрядной стороны подключен посредством емкостной связи к выходу блока 2 сравнения напряжений.

TFT 23 и 24, по аналогии с TFT 21 и 22, соединены последовательно и установлены между линией VDD и линией VSS. Заранее определенное напряжение смещения Vbp поступает на затворный контакт TFT 23, и TFT 23 функционирует как транзистор со смещением. Конденсатор 33 предусмотрен между выходом инвертирующей схемы 34 и затворным контактом TFT 24. Переключатель 15 предусмотрен между линией VSS и затворным контактом TFT 24. Таким образом, TFT 23 и 24 образуют схему усилителя (далее именуемую схемой усилителя зарядной стороны), и вход схемы усилителя зарядной стороны подключен посредством емкостной связи к выходу блока 2 сравнения напряжений.

Двухтактный выходной блок 4 включает в себя TFT 25 и 26. TFT 25 и 26, по аналогии с TFT 21 и 22, соединены последовательно и установлены между линией VDD и линией VSS. Затворный контакт TFT 25 подключен к стоковым контактам TFT 23 и 24, затворный контакт TFT 26 подключен к стоковым контактам TFT 21 и 22. Стоковые контакты TFT 25 и 26 подключены к выходному контакту OUT. Таким образом, TFT 25 предусмотрен между линией VDD и выходным контактом OUT, и TFT 26 предусмотрен между линией VSS и выходным контактом OUT.

В буферной схеме 1 переключатели 11-15 функционируют как переключатель выбора входной стороны, переключатель выбора выходной стороны, переключатель для короткого замыкания, переключатель установки разрядной стороны и переключатель установки зарядной стороны, соответственно. Конденсатор 32 функционирует как емкостной элемент разрядной стороны, и конденсатор 33 функционирует как емкостной элемент зарядной стороны. TFT 25 функционирует как переключатель для заряда, и TFT 26 функционирует как переключатель для разряда. Переключатель для заряда образует зарядную схему, и переключатель для разряда образует разрядную схему.

На переключатели 11 и 13-15 поступает сигнал управления переключением Xs, и на переключатель 12 поступает сигнал управления переключением Xd. Переключатели 11-15 переходят в состояние включения, когда каждый из поступающих сигналов управления переключением находится на высоком уровне, и переходят в состояние выключения, когда каждый из сигналов находится на низком уровне. В дальнейшем, узел, где соединены переключатели 11 и 12 и конденсатор 31, именуется N1, узел, где подключен вход инвертирующей схемы 34, именуется N2, узел, где подключен выход инвертирующей схемы 34, именуется N3, и узлы, где подключены затворные контакты TFT 21, 24, 25 и 26, именуются, соответственно, N4-N7.

Буферная схема 1 осуществляет двухэтапную операцию установки и возбуждения для возбуждения емкостной нагрузки 9. В дальнейшем, период, когда осуществляется операция установки, именуется “периодом установки”, и период, когда осуществляется операция возбуждения, именуется “периодом возбуждения”. В течение периода установки сигнал управления переключением Xs поддерживается на высоком уровне, и сигнал управления переключением Xd поддерживается на низком уровне. Соответственно, в течение периода установки переключатели 11 и 13-15 находятся в состоянии включения, и переключатель 12 находится в состоянии выключения (см. фиг.3). С другой стороны, в течение периода возбуждения сигнал управления переключением Xs поддерживается на низком уровне, и сигнал управления переключением Xd поддерживается на высоком уровне. Соответственно, в течение периода возбуждения переключатели 11 и 13-15 находятся в состоянии выключения, и переключатель 12 находится в состоянии включения (см. фиг.4).

На фиг.5 показана диаграмма хронирования буферной схемы 1. На фиг.5 показаны изменения сигналов управления переключением Xs, Xd, входного напряжения Vin, напряжений на узлах N1-N7 и выходного напряжения Vout. Период, когда сигнал управления переключением Xs находится на высоком уровне, является периодом установки, и период, когда сигнал управления переключением Xd находится на высоком уровне, является периодом возбуждения. Период установки и период возбуждения устанавливаются так, чтобы не перекрывать друг друга. Кроме того, во избежание отказа буферной схемы 1 небольшой запас по времени предусмотрен между периодом установки и периодом возбуждения.

В примере, показанном на фиг.5, входное напряжение Vin растет в момент t1 и падает в момент t3. Буферная схема 1 осуществляет операцию установки для инициализации состояния схемы в течение периода установки, начинающегося в момент времени t1. В течение периода возбуждения, начинающегося в момент времени t2, буферная схема 1 осуществляет операцию возбуждения, в которой емкостная нагрузка 9 заряжается, обеспечивая рост выходного напряжения Vout. В течение периода установки, начинающегося в момент времени t3, буферная схема 1 осуществляет ту же операцию установки, что и в течение периода установки, начинающегося в момент времени t1. В течение периода возбуждения, начинающегося в момент времени t4, буферная схема 1 осуществляет операцию возбуждения, в которой емкостная нагрузка 9 разряжается, обеспечивая спад выходного напряжения Vout. Далее будет подробно описана работа буферной схемы 1 в соответствующие периоды.

Поскольку в течение периода установки, начинающегося в момент времени t1 или в момент времени t3, сигнал управления переключением Xs поддерживается на высоком уровне и сигнал управления переключением Xd поддерживается на низком уровне, переключатели 11 и 13-15 переходят в состояние включения и переключатель 12 переходит в состояние выключения (см. фиг.3). Поскольку переключатель 11 находится в состоянии включения, и переключатель 12 находится в состоянии выключения, входное напряжение Vin поступает на электрод входной стороны конденсатора 31 через переключатель 11, в результате чего напряжение на узле N1 становится равным входному напряжению Vin.

Кроме того, поскольку переключатель 13 находится в состоянии включения, вход и выход инвертирующей схемы 34 короткозамкнуты, и входное напряжение и выходное напряжение инвертирующей схемы 34 становятся равными. Входное/выходное напряжение инвертирующей схемы 34 при короткозамкнутых входе и выходе именуется напряжением инверсии Vm. В течение периода установки напряжения на узлах N2 и N3 становятся равными напряжению инверсии Vm, и напряжение между электродами конденсатора 31 становится равным (Vin-Vm). Конденсатор 31 поддерживает напряжение между электродами в конце периода установки.

Кроме того, поскольку переключатели 14 и 15 находятся в состоянии включения, напряжение источника питания на высоковольтной стороне (далее именуемое VDD) поступает на узел N4 с линии VDD, и напряжение источника питания на низковольтной стороне (далее именуемое VSS) поступает на узел N5 с линии VSS. Таким образом, напряжение между электродами конденсатора 32 становится равным (VDD-Vm), и напряжение между электродами конденсатора 33 становится равным (VSS-Vm). Конденсаторы 32 и 33 поддерживают соответствующие напряжения между электродами в конце периода установки.

TFT 24 переходит в состояние выключения, поскольку на его затворный контакт поступает напряжение VSS. В этот момент времени TFT 23 повышает напряжение на узле N6, чтобы оно превышало пороговое напряжение TFT 25. Кроме того, TFT 21 переходит в состояние выключения, поскольку на его затворный контакт поступает напряжение VDD. В этот момент времени TFT 22 понижает напряжение на узле N7, чтобы оно было меньше порогового напряжения TFT 26. Соответственно, в течение периода установки, поскольку TFT 25 и 26 переходят в состояние выключения, в результате чего выходной сигнал буферной схемы 1 переходит в плавающее состояние, так что выходное напряжение Vout не изменяется.

В течение периода возбуждения, начинающегося в момент времени t2, поскольку сигнал управления переключением Xs поддерживается на низком уровне, и сигнал управления переключением Xd поддерживается на высоком уровне, переключатели 11 и 13-15 переходят в состояние выключения и переключатель 12 переходит в состояние включения (см. фиг.4). Поскольку переключатель 11 находится в состоянии выключения, и переключатель 12 находится в состоянии включения, выходное напряжение Vout поступает на электрод входной стороны конденсатора 31 через переключатель 12, в результате чего напряжение на узле N1 становится равным выходному напряжению Vout. Таким образом, напряжение на узле N1 падает с Vin до Vout в момент времени t2.

Кроме того, в момент времени t2 и далее переключатель 13 находится в состоянии выключения. Напряжение, поддерживаемое на конденсаторе 31, не изменяется до и после момента t2, и, таким образом, когда напряжение на узле N1 падает с Vin до Vout, напряжение на узле N2 падает на ту же величину, достигая значения (Vout-Vin+Vm). Когда напряжение на узле N2 падает, напряжение на узле N3, к которому подключен выход инвертирующей схемы 34, растет. В общем случае, выходное напряжение инвертирующей схемы изменяется в большей степени, чем входное напряжение, когда входное напряжение изменяется вблизи напряжения инверсии Vm. Соответственно, в соответствии с величиной спада (Vout-Vin+Vm) напряжения на узле N2, напряжение на узле N3 растет в большей степени, чем величина спада напряжения на узле N2.

Кроме того, в момент времени t2 и далее, переключатели 14 и 15 находятся в состоянии выключения. Напряжения, поддерживаемые на конденсаторах 32 и 33, не изменяются до и после момента t2, и, таким образом, когда напряжение на узле N3 растет, напряжения на узлах N4 и N5 растут на ту же величину, соответственно. Когда напряжение на узле N5 растет, TFT 24 переходит в состояние включения, напряжение на узле N6 падает, и TFT 25 переходит в состояние включения. С другой стороны, даже когда напряжение на узле N4 растет, TFT 21 и 26 остаются в состоянии выключения. Таким образом, поскольку TFT 25 переходит в состояние включения, и TFT 26 остается в состоянии выключения, емкостная нагрузка 9 подключена к линии VDD через TFT 25. В результате, емкостная нагрузка 9 заряжается, в связи с чем выходное напряжение Vout растет.

Выходное напряжение Vout продолжает расти, пока не становится равным входному напряжению Vin. Когда выходное напряжение Vout становится равным входному напряжению Vin, напряжения на узлах N1-N7 возвращаются к уровням в течение периода установки. Например, напряжения на узлах N2 и N3 становятся равными напряжению инверсии Vm, и напряжения на узлах N4 и N5 становятся равными VDD и VSS, соответственно. Соответственно, когда выходное напряжение Vout становится равным входному напряжению Vin, TFT 24 и 25 возвращаются в состояние выключения, в результате чего выходное напряжение Vout перестает расти.

В течение периода возбуждения, начинающегося в момент времени t4, переключатели 11-15 находятся в том же состоянии, что и в течение периода возбуждения, начинающегося в момент времени t2 (см. фиг.4). Поскольку переключатель 11 находится в состоянии выключения и переключатель 12 находится в состоянии включения, напряжение на узле N1 становится равным выходному напряжению Vout. Таким образом, напряжение на узле N1 растет с Vin до Vout в момент времени t4.

Когда напряжение на узле N1 растет с Vin до Vout, напряжение на узле N2 растет на ту же величину, достигая (Vout-Vin+Vm), и напряжение на узле N3, подключенном к выходу инвертирующей схемы 34, падает. Когда напряжение на узле N3 падает, напряжения на узлах N4 и N5 падают на одну и ту же величину, соответственно. Когда напряжение на узле N4 падает, TFT 21 переходит в состояние включения, напряжение на узле N7 растет, и TFT 26 переходит в состояние включения. С другой стороны, даже когда напряжение на узле N5 падает, TFT 24 остается в состоянии выключения, и TFT 25 также остается в состоянии выключения. Таким образом, поскольку TFT 26 переходит в состояние включения и TFT 25 остается в состоянии выключения, емкостная нагрузка 9 подключается к линии VSS через TFT 26. В результате, емкостная нагрузка 9 разряжается, в связи с чем выходное напряжение Vout падает.

Выходное напряжение Vout продолжает падать, пока не становится равным входному напряжению Vin. Когда выходное напряжение Vout становится равным входному напряжению Vin, напряжения на узлах N1-N7 возвращаются к уровням в течение периода установки. Соответственно, когда выходное напряжение Vout становится равным входному напряжению Vin, TFT 21 и 26 возвращаются в состояние выключения, выходное напряжение Vout прекращает падать.

Здесь, напряжение, выводимое из блока 2 сравнения напряжений на блок 3 управления возбуждением (напряжение на узле N3), именуется “напряжением результата сравнения”, и среди напряжений, выводимых из блока 3 управления возбуждением на двухтактный выходной блок 4, напряжение, подаваемое на затворный контакт TFT 25 (напряжение на узле N6), именуется “напряжением управления зарядом”, и напряжение, подаваемое на затворный контакт TFT 26 (напряжение на узле N7), именуется “напряжением управления разрядом”. В дальнейшем, конфигурация и работа буферной схемы 1 будут описаны с использованием этих терминов.

Блок сравнения напряжений 2 включает в себя схему компаратора, образованную переключателем 13, конденсатором 31 и инвертирующей схемой 34, переключатель 11 в качестве переключателя выбора входной стороны и переключатель 12 в качестве переключателя выбора выходной стороны. В течение периода установки переключатели 11 и 13 находятся в состоянии включения, и конденсатор 31 поддерживает напряжение между электродами (Vin-Vm). В течение периода возбуждения переключатель 12 находится в состоянии включения, и инвертирующая схема 34 выводит напряжение результата сравнения в соответствии с напряжением на узле N2 (Vout-Vin+Vm). Напряжение результата сравнения становится выше, чем напряжение инверсии Vm, когда выходное напряжение Vout меньше входного напряжения Vin, и становится ниже, чем напряжение инверсии Vm, когда выходное напряжение Vout больше входного напряжения Vin. Таким образом, блок 2 сравнения напряжений сравнивает входное напряжение Vin, поступающее с входного контакта IN, и выходное напряжение Vout, выводимое с выходного контакта OUT для вывода напряжения результата сравнения в соответствии с результатом сравнения. Схема компаратора, входящая в состав блока 2 сравнения напряжений, сравнивает входное напряжение Vin в течение периода установки и выходное напряжение Vout в течение периода возбуждения для вывода напряжения результата сравнения.

Блок 3 управления возбуждением включает в себя схему усилителя зарядной стороны, образованную посредством TFT 23 и 24, схему усилителя разрядной стороны, образованную посредством TFT 21 и 22, конденсатор 33 в качестве емкостного элемента зарядной стороны, конденсатор 32 в качестве емкостного элемента разрядной стороны, переключатель 15 в качестве переключателя установки зарядной стороны и переключатель 14 в качестве переключателя установки разрядной стороны. В течение периода установки переключатели 14 и 15 переходят в состояние включения, в результате чего напряжения отключения (напряжения, при которых TFT 21 и 24 переходят в состояние выключения) поступают на две схемы усилителя. В этот момент времени напряжение управления зарядом достаточно велико, чтобы TFT 25 находился в состоянии выключения, и напряжение управления разрядом достаточно низко, чтобы TFT 26 находился в состоянии выключения. В течение периода возбуждения переключатели 14 и 15 находятся в состоянии выключения, благодаря чему входные напряжения двух схем усилителя, напряжение управления зарядом и напряжение управления разрядом изменяются в соответствии с напряжением результата сравнения. Таким образом, блок 3 управления возбуждением выводит напряжение управления зарядом и напряжение управления разрядом, установленные на соответствующие начальные уровни в течение периода установки, и в течение периода возбуждения, изменяются в соответствии с напряжением результата сравнения, выводимым из блока 2 сравнения напряжений.

Двухтактный выходной блок 4 включает в себя в качестве переключателя для заряда TFT 25, который заряжает емкостную нагрузку 9, и включает в себя в качестве переключателя для разряда TFT 26, который разряжает емкостную нагрузку 9. Управление TFT 25 осуществляется с использованием напряжения управления зарядом, и управление TFT 26 осуществляется с использованием напряжения управления разрядом. Кроме того, переключатель для заряда образует зарядную схему, и переключатель для разряда образует разрядную схему. Двухтактный выходной блок 4 включает в себя зарядную схему, которая возбуждает емкостную нагрузку 9 на основании напряжения управления зарядом, и разрядную схему, которая возбуждает емкостную нагрузку 9 на основании напряжения управления разрядом.

Когда выходное напряжение Vout меньше входного напряжения Vin, напряжение результата сравнения становится выше, чем напряжение инверсии Vm, и входные напряжения обеих схем усилителя растут. В этот момент времени TFT 24, входящий в состав схемы усилителя зарядной стороны, переходит в состояние включения, и напряжение управления зарядом падает, в связи с чем TFT 25 переходит в состояние включения. С другой стороны, поскольку TFT 21, входящий в состав схемы усилителя разрядной стороны, остается в состоянии выключения, напряжение управления разрядом не изменяется. Таким образом, в двухтактном выходном блоке 4 разрядная схема не действует, и действует только зарядная схема. Когда зарядная схема действует, емкостная нагрузка 9 заряжается и выходное напряжение Vout растет. Выходное напряжение Vout растет, пока не становится равным входному напряжению Vin.

Когда выходное напряжение Vout больше входного напряжения Vin, напряжение результата сравнения становится ниже, чем напряжение инверсии Vm, и входные напряжения обеих схем усилителя падают. В этот момент времени TFT 21, входящий в состав схемы усилителя разрядной стороны, переходит в состояние включения, и напряжение управления разрядом растет, в связи с чем TFT 26 переходит в состояние включения. С другой стороны, поскольку TFT 24, входящий в состав схемы усилителя зарядной стороны, остается в состоянии выключения, напряжение управления зарядом не изменяется. Таким образом, в двухтактном выходном блоке 4 зарядная схема не действует, и действует только разрядная схема. Когда разрядная схема действует, емкостная нагрузка 9 разряжается и выходное напряжение Vout падает. Выходное напряжение Vout падает, пока не становится равным входному напряжению Vin.

Таким образом, блок 3 управления возбуждением избирательно оперирует зарядной схемой и разрядной схемой, входящими в состав двухтактного выходного блока 4, так что выходное напряжение Vout становится равным входному напряжению Vin. В частности, в течение периода установки блок 3 управления возбуждением устанавливает напряжение управления зарядом и напряжение управления разрядом на уровнях, при которых зарядная схема и разрядная схема не действуют, соответственно, и в течение периода возбуждения, на основании напряжения результата сравнения, устанавливает напряжение управления зарядом на уровне, при котором действует зарядная схема, когда выходное напряжение Vout меньше входного напряжения Vin, и устанавливает напряжение управления разрядом на уровне, при котором действует разрядная схема, когда выходное напряжение Vout больше входного напряжения Vin.

Теперь опишем преимущества буферной схемы 1 согласно настоящему варианту осуществления. Как описано выше, в буферной схеме 1 зарядная схема (TFT 25) и разрядная схема (TFT 26), входящие в состав двухтактного выходного блока 4, избирательно задействуются, на основании результат сравнения входного напряжения Vin и выходного напряжения Vout, и, таким образом, осуществляются заряд и разряд емкостной нагрузки 9. Соответственно, выходное напряжение Vout можно сделать равным входному напряжению Vin.

Кроме того, избирательное использование зарядной схемы и разрядной схемы препятствует протеканию установившегося тока в двухтактном выходном блоке 4. Соответственно, можно снизить энергопотребление в буферной схеме 1. Кроме того, поскольку зарядная схема и разрядная схема не действуют одновременно, можно эффективно осуществлять заряд и разряд, поскольку между источниками питания не течет сквозной ток. Соответственно, по сравнению со схемой усиления класса А (операционным усилителем 89, показанным на фиг.9) можно получить достаточную токовую возбудимость и можно осуществлять заряд и разряд с более высокой скоростью посредством малоразмерных TFT. Кроме того, в буферной схеме 1, только когда выходное напряжение Vout не равно входному напряжению Vin, действует одна из зарядной схемы и разрядной схемы для заряда или разряда емкостной нагрузки 9. Соответственно, можно предотвратить бесполезное энергопотребление за счет заряда и разряда емкостной нагрузки 9. Кроме того, буферная схема 1 может выдавать напряжение VDD и напряжение VSS в качестве выходного напряжения Vout (операция с размахом, равным напряжению питания). Соответственно, можно понизить рабочее напряжение буферной схемы 1, что позволяет снизить энергопотребление.

Кроме того, в течение периода установки выходной сигнал буферной схемы 1 находится в плавающем состоянии, где никакого соединения не установлено, и в течение периода возбуждения он устанавливается равным входному напряжению Vin. Таким образом, когда буферная схема 1 используется для возбуждения истоковой линии SL в жидкокристаллическом устройстве отображения со встроенным драйвером (см. фиг.2), дискретизирующий вентиль для осуществления переключения в зависимости от того, нужно ли подключать истоковую линию SL (дискретизирующий вентиль 88, показанный на фиг.7), не требуется. Соответственно, можно уменьшить площадь схемы, поскольку дискретизирующий вентиль, его схема управления и т.п. не предусмотрены. В случае когда управление периодом, когда буферная схема 1 и истоковая линия SL не соединены (далее именуемым периодом отсутствия соединения), и периодом установки осуществляется независимо, на переключатели 11 и 13 и переключатели 14 и 15 можно подавать разные сигналы управления. Это позволяет возбуждать совокупность истоковых линий SL на основе разнесения по времени. Кроме того, для блока 2 сравнения напряжений, блока 3 управления возбуждением и двухтактного выходного блока 4 можно легко сформировать схемы, устойчивые к изменению процесса, что показано ниже.

Переключатели 11 и 12 подключены к входному контакту схемы компаратора, образованной переключателем 13, конденсатором 31 и инвертирующей схемой 34, другой конец переключателя 11 подключен к входному контакту IN, и другой конец переключателя 12 подключен к выходному контакту OUT, что позволяет легко формировать блок 2 сравнения напряжений. В течение периода установки переключатель 11 поддерживается в состоянии включения, и в течение периода возбуждения переключатель 12 поддерживается в состоянии включения, что позволяет переключать напряжение, вводимое в схему компаратора между в течение периода установки и в течение периода возбуждения. Кроме того, переключатель 13 поддерживается в состоянии включения в течение периода установки и поддерживается в состоянии выключения в течение периода возбуждения, благодаря чему инвертирующая схема 34 выводит напряжение в соответствии с напряжением (Vout-Vin+Vm) в течение периода возбуждения. Когда напряжение, выводимое из инвертирующей схемы 34, поступает на блок 3 управления возбуждением в качестве напряжения результата сравнения, напряжение управления зарядом и напряжение управления разрядом, выводимые из блока 3 управления возбуждением, не подвергаются влиянию изменения порогового напряжения инвертирующей схемы 34. Соответственно, выходное напряжение Vout можно сделать равным входному напряжению Vin, не подвергая влиянию изменения порогового напряжения инвертирующей схемы 34.

TFT 23 и 24 образуют схему усилителя зарядной стороны, TFT 21 и 22 образуют схему усилителя разрядной стороны, входы двух схем усилителя подключены посредством емкостной связи к выходу блока 2 сравнения напряжений, соответственно, и, дополнительно, для входов двух схем усилителя, соответственно предусмотрены переключатели установки, благодаря которым можно легко сформировать блок 3 управления возбуждением. В течение периода установки два переключателя установки переводятся в состояние включения для подачи напряжения отключения на входы схем усилителя, что позволяет устанавливать напряжение управления зарядом и напряжение управления разрядом на начальные уровни, соответственно. В течение периода возбуждения два переключателя установки переводятся в состояние выключения для подачи напряжения результата сравнения через емкостные элементы на входы соответствующих схем усилителя, благодаря чему напряжение управления зарядом и напряжение управления разрядом можно изменять в соответствии с напряжением результата сравнения. Таким образом, установление напряжения управления зарядом и напряжения управления разрядом на начальные уровни в течение периода установки, соответственно, позволяет безопасно переводить двухтактный выходной блок 4 из состояния выключения независимо от изменения пороговых напряжений TFT. Кроме того, в течение периода возбуждения, поскольку состояние двухтактного выходного блока 4 изменяется в одном направлении в соответствии с напряжением результата сравнения, в принципе невозможно, чтобы схема усилителя зарядной стороны и схема усилителя разрядной стороны работали одновременно.

TFT 25 предусмотрен между линией VDD и выходным контактом OUT, TFT 26 предусмотрен между линией VSS и выходным контактом, и затворный контакт TFT 25 подключен к выходу схемы усилителя зарядной стороны (стоковым контактам TFT 23 и 24), затворный контакт TFT 26 подключен к выходу схемы усилителя разрядной стороны (стоковым контактам TFT 21 и 22), что позволяет легко сформировать двухтактный выходной блок 4. Поскольку зарядная схема и разрядная схема, входящие в состав двухтактного выходного блока 4, используются избирательно, двухтактный выходной блок 4 не действует как аналоговая схема, в которой выходное напряжение чувствительно меняется на напряжение смещения, но активирует и деактивирует операцию наподобие цифровой схемы. Таким образом, двухтактный выходной блок 4 имеет схемную конфигурацию, в которой отказ маловероятен даже при изменении процесса.

Как описано выше, преимуществами буферной схемы 1 согласно настоящему варианту осуществления являются ее малый размер, низкое энергопотребление и устойчивость к изменению процесса. Соответственно, при возбуждении истоковой линии в жидкокристаллическом устройстве отображения со встроенным драйвером использование буферной схемы 1 согласно настоящему варианту осуществления обеспечивает малоразмерное жидкокристаллическое устройство отображения с низким энергопотреблением и высоким качеством изображения.

Буферная схема 1 согласно настоящему варианту осуществления имеет следующие преимущества по сравнению со схемой выходного каскада, показанной на фиг.10 (далее именуемой традиционной схемой). Во-первых, в традиционной схеме емкостная нагрузка заряжается и разряжается в течение периода инициализации, и в этот момент времени потребляется излишняя электрическая мощность. Напротив, в буферной схеме 1 период инициализации не предусмотрен, и заряд и разряд емкостной нагрузки осуществляются в течение периода возбуждения только для изменения выходного напряжения до нужного уровня. Соответственно, согласно буферной схеме 1 энергопотребление можно сделать меньшим, чем в традиционной схеме.

Кроме того, в традиционной схеме, если пороговые напряжения инвертирующих схем, входящих в состав схем компаратора 91 и 92, не совпадают с пороговыми напряжениями вентилей И G1 и G2, возникает ошибка смещения в выходном напряжении. С другой стороны, в буферной схеме 1, благодаря использованию вышеописанных блока 2 сравнения напряжений и блока 3 управления возбуждением, можно генерировать напряжение управления зарядом и напряжение управления разрядом, не подверженные влиянию изменения порогового напряжения инвертирующей схемы 34, что позволяет сделать выходное напряжение Vout равным входному напряжению Vin, не подвергая его влиянию изменения процесса. Соответственно, буферная схема 1 оказывается более устойчивой к изменению процесса, чем традиционная схема.

Кроме того, в традиционной схеме площадь схемы оказывается большой, поскольку предусмотрены вентили И G1 и G2 и т.п., и управление усложнено, поскольку состояния переключателей SW7-SW10 изменяются в соответствии с выходным сигналом схемы компаратора 92. С другой стороны, в буферной схеме 1 вентиль И и т.п. не требуются, и на переключатели 11-15 требуется подавать только сигналы управления переключением Xs и Xd с фиксированным шаблоном изменения. Соответственно, согласно буферной схеме 1 площадь схемы можно сделать меньше, чем в традиционной схеме.

Кроме того, в традиционной схеме, поскольку в период записи осуществляется только один из заряда и разряда, в выходном напряжении может возникать ошибка смещения из-за задержки внутри схемы. С другой стороны, в буферной схеме 1 поскольку заряд и разряд переключаются и осуществляются по мере необходимости в течение периода возбуждения, даже если выходное напряжение чрезмерно изменяется из-за задержки внутри схемы (даже если происходит перерегулирование), избыточное изменение выходного напряжения сразу же автоматически корректируется. Соответственно, согласно буферной схеме 1 выходное напряжение можно сделать в точности равным входному напряжению.

Для буферной схемы 1 согласно настоящему варианту осуществления можно сформировать модификацию, описанную ниже. На фиг.6 показана принципиальная схема буферной схемы двухтактного типа согласно модификации варианта осуществления настоящего изобретения. В буферной схеме 5, показанной на фиг.6, двухтактный выходной блок 4 в вышеописанной буферной схеме 1 заменен двухтактным выходным блоком 6. Двухтактный выходной блок 6 получается добавлением в двухтактный выходной блок 4 TFT 27 в качестве переключателя для остановки заряда и TFT N-типа 28 в качестве переключателя для остановки разряда.

В буферной схеме 5 TFT 27 предусмотрен между линией VDD и TFT 25 и TFT 28 предусмотрен между линией VSS и TFT 26. В частности, истоковый контакт TFT 27 подключен к линии VDD и его стоковый контакт подключен к истоковому контакту TFT 25. Истоковый контакт TFT 28 подключен к линии VSS и его стоковый контакт подключен к истоковому контакту TFT 26. Сигнал инверсии сигнала управления переключением Xd поступает на затворный контакт TFT 27, и сигнал управления переключением Xd поступает на затворный контакт TFT 28.

В течение периода возбуждения, поскольку сигнал управления переключением Xd поддерживается на высоком уровне, TFT 27 и 28 переходят в состояние включения, благодаря чему буферная схема 5 действует аналогично буферной схеме 1. С другой стороны, в течение периода установки, поскольку сигнал управления переключением Xd поддерживается на низком уровне, TFT 27 и 28 переходят в состояние выключения. Таким образом, даже когда TFT 25 и 26 переходят в состояние включения, заряд и разряд емкостной нагрузки 9 не осуществляются.

Таким образом, двухтактный выходной блок 6 включает в себя TFT 27, обеспеченный последовательно с TFT 25 между линией VDD и выходным контактом OUT, и TFT 28, обеспеченный последовательно с TFT 26 между линией VSS и выходным контактом OUT, и TFT 27 и 28 поддерживаются в состоянии включения в течение периода возбуждения. Соответственно, согласно буферной схеме 5 период, когда осуществляются заряд и разряд емкостной нагрузки 9, ограничен только периодом возбуждения, что может предотвращать отказ схемы. Кроме того, поскольку периодом отсутствия соединения и периодом установки можно управлять независимо, совокупность истоковых линий SL может возбуждаться на основе разнесения по времени. В частности, переключатель 12 и двухтактный выходной блок 6 предусмотрены для каждой из истоковых линий SL, и другие схемы являются общими для совокупности истоковых линий SL, что позволяет возбуждать множественные истоковые линии SL на основе разнесения по времени при малом размере схемы.

Буферную схему двухтактного типа настоящего изобретения можно использовать в различных вариантах осуществления в качестве схемы возбуждения емкостной нагрузки, которая возбуждает емкостную нагрузку, на основании входного напряжения, помимо схемы выходного каскада истоковой схемы возбуждения жидкокристаллического устройства отображения.

Промышленное применение

Поскольку схема возбуждения емкостной нагрузки настоящего изобретения отличается малым размером, низким энергопотреблением и устойчивостью к изменению процесса, ее можно использовать в различных режимах, в которых емкостная нагрузка возбуждается на основании входного напряжения, в том числе, в схеме выходного каскада истоковой схемы возбуждения жидкокристаллического устройства отображения.

Перечень условных обозначений

1 и 5: БУФЕРНАЯ СХЕМА

2: БЛОК СРАВНЕНИЯ НАПРЯЖЕНИЙ

3: БЛОК УПРАВЛЕНИЯ ВОЗБУЖДЕНИЕМ

4 и 6: ДВУХТАКТНЫЙ ВЫХОДНОЙ БЛОК

9: ЕМКОСТНАЯ НАГРУЗКА

11-15: ПЕРЕКЛЮЧАТЕЛЬ

21-28 и 45: TFT

31-33: КОНДЕНСАТОР

34: ИНВЕРТИРУЮЩАЯ СХЕМА

40: ЖИДКОКРИСТАЛЛИЧЕСКОЕ УСТРОЙСТВО ОТОБРАЖЕНИЯ

41: ЖИДКОКРИСТАЛЛИЧЕСКАЯ ПАНЕЛЬ

42: ПИКСЕЛЬНАЯ СХЕМА

43: ЗАТВОРНАЯ СХЕМА ВОЗБУЖДЕНИЯ

44: ИСТОКОВАЯ СХЕМА ВОЗБУЖДЕНИЯ

46: СДВИГОВЫЙ РЕГИСТР

47: СХЕМА Ц/А ПРЕОБРАЗОВАНИЯ

Изобретение относится к схеме возбуждения емкостной нагрузки, которая возбуждает емкостную нагрузку на основании входного напряжения, и к устройству отображения, включающему в себя схему возбуждения емкостной нагрузки. Техническим результатом является создание малоразмерной схемы возбуждения емкостной нагрузки с низким энергопотреблением и устойчивой к изменению процесса. Схема возбуждения емкостной нагрузки содержит: блок сравнения напряжений; блок управления возбуждением; двухтактный выходной блок, включающий в себя зарядную схему, которая заряжает емкостную нагрузку, подключенную к выходному контакту, на основании напряжения управления зарядом, и разрядную схему, которая разряжает емкостную нагрузку на основании напряжения управления разрядом, причем блок управления возбуждением избирательно оперирует зарядной схемой и разрядной схемой таким образом, что выходное напряжение становится равным входному напряжению; и связи между ними. 2 н. и 7 з.п. ф-лы, 11 ил.

1. Схема возбуждения емкостной нагрузки, которая возбуждает емкостную нагрузку на основании входного напряжения, содержащая

блок сравнения напряжений, который сравнивает входное напряжение, поступающее с входного контакта, и выходное напряжение, выводимое с выходного контакта, для вывода напряжения результата сравнения в соответствии с результатом сравнения,

блок управления возбуждением, который выводит напряжение управления зарядом и напряжение управления разрядом, которые установлены на начальных уровнях, соответственно, в течение первого периода, и изменяются в соответствии с напряжением результата сравнения в течение второго периода, и

двухтактный выходной блок, включающий в себя зарядную схему, которая заряжает емкостную нагрузку, подключенную к выходному контакту, на основании напряжения управления зарядом, и разрядную схему, которая разряжает емкостную нагрузку, на основании напряжения управления разрядом, причем

блок управления возбуждением избирательно оперирует зарядной схемой и разрядной схемой таким образом, что выходное напряжение становится равным входному напряжению.

2. Схема возбуждения емкостной нагрузки по п.1, в которой

блок сравнения напряжений включает в себя

переключатель выбора входной стороны, который предусмотрен между входным контактом и заранее определенным узлом и переходит в состояние включения в течение первого периода,

переключатель выбора выходной стороны, который предусмотрен между выходным контактом и узлом и переходит в состояние включения в течение второго периода, и

схему компаратора, вход которой подключен к узлу, причем схема компаратора сравнивает входное напряжение в течение первого периода и выходное напряжение в течение второго периода для вывода напряжения результата сравнения.

3. Схема возбуждения емкостной нагрузки по п.2, в которой

схема компаратора включает в себя

инвертирующую схему,

емкостной элемент, предусмотренный между входом инвертирующей схемы и узлом, и

переключатель для короткого замыкания, который предусмотрен между входом и выходом инвертирующей схемы и переходит в состояние включения в течение первого периода,

причем емкостной элемент поддерживает разность между входным напряжением и напряжением инверсии инвертирующей схемы в течение первого периода, и в течение второго периода инвертирующая схема выводит, в качестве напряжения результата сравнения, напряжение в соответствии с напряжением, полученным путем прибавления напряжения инверсии к разности между выходным напряжением и входным напряжением.

4. Схема возбуждения емкостной нагрузки по п.1, в которой

в течение первого периода блок управления возбуждением устанавливает напряжение управления зарядом и напряжение управления разрядом на уровнях, при которых зарядная схема и разрядная схема не действуют, соответственно, и в течение второго периода, на основании напряжения результата сравнения, блок управления возбуждением устанавливает напряжение управления зарядом на уровне, при котором зарядная схема действует, когда выходное напряжение меньше входного напряжения, и устанавливает напряжение управления разрядом на уровне, при котором разрядная схема действует, когда выходное напряжение больше входного напряжения.

5. Схема возбуждения емкостной нагрузки по п.4, в которой

блок управления возбуждением включает в себя

схему усилителя зарядной стороны, которая выводит напряжение управления зарядом на зарядную схему, и

схему усилителя разрядной стороны, которая выводит напряжение управления разрядом на разрядную схему.

6. Схема возбуждения емкостной нагрузки по п.5, в которой

блок управления возбуждением дополнительно включает в себя

емкостной элемент зарядной стороны для обеспечения емкостной связи выхода блока сравнения напряжений и входа схемы усилителя зарядной стороны,

емкостной элемент разрядной стороны для обеспечения емкостной связи выхода блока сравнения напряжений и входа схемы усилителя разрядной стороны,

переключатель установки зарядной стороны, который переходит в состояние включения в течение первого периода для подачи напряжения отключения на вход схемы усилителя зарядной стороны, и

переключатель установки разрядной стороны, который переходит в состояние включения в течение первого периода для подачи напряжения отключения на вход схемы усилителя разрядной стороны.

7. Схема возбуждения емкостной нагрузки по п.1, в которой

в качестве зарядной схемы двухтактный выходной блок включает в себя переключатель для заряда, который предусмотрен между линией питания высоковольтной стороны и выходным контактом, и управляется с использованием напряжения управления зарядом, и

в качестве разрядной схемы двухтактный выходной блок включает в себя переключатель для разряда, который предусмотрен между линией питания низковольтной стороны и выходным контактом, и управляется с использованием напряжения управления разрядом.

8. Схема возбуждения емкостной нагрузки по п.7, в которой

двухтактный выходной блок дополнительно включает в себя

переключатель для остановки заряда, который предусмотрен между линией питания высоковольтной стороны и выходным контактом последовательно с переключателем для заряда, и

переключатель для остановки разряда, который предусмотрен между линией питания низковольтной стороны и выходным контактом последовательно с переключателем для разряда.

9. Устройство отображения, которое возбуждает сигнальную линию, подключенную к пиксельной схеме, с использованием схемы возбуждения емкостной нагрузки по любому из пп.1-8.

| RU 2006139827 А, 20.05.2008 | |||

| ГЕНЕРАТОР ЭЛЕКТРОДИНАМИЧЕСКОГО ПОЛЯ | 2001 |

|

RU2268542C2 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

Авторы

Даты

2012-06-27—Публикация

2009-06-02—Подача