Настоящее раскрытие относится к нейронному усилителю с дифференциальным коммутируемым конденсатором, например, для использования в аналоговой искусственной нейронной сети, к аналоговой искусственной нейронной сети с одним или более такими нейронными усилителями и к устройству датчика с такой нейронной сетью.

Нейронная сеть является каскадом нейронных слоев, которые являются взаимосвязанными. Искусственная нейронная сеть (просто называемая нейронной сетью в данном документе) является вычислительной системой, используемой в машинном обучении. Нейронная сеть может быть основана на слоях соединенных узлов, называемых нейронами, которые могут приблизительно моделировать нейроны в биологическом мозге. Основным элементом нейронной сети является одиночный нейрон, который вычисляет взвешенную сумму своих входных данных. Было показано, что любая или почти любая функция может быть реализована через нейронную сеть посредством правильной настройки индивидуальных весов нейронов, также называемой обучением.

Каждый слой может иметь множество нейронов. Нейроны между различными слоями соединяются посредством соединений, которые соответствуют синапсам в биологическом мозге. Нейрон на первом слое может передавать сигнал другому нейрону на другом слое через соединение между этими двумя нейронами. Сигнал, переданный по соединению, может быть действительным числом. Другой нейрон другого слоя может обрабатывать принятый сигал (т.е., действительное число) и затем передавать обработанный сигнал дополнительным нейронам. Выходные данные каждого нейрона могут быть вычислены посредством некоторой нелинейной функции на основе входных данных этого нейрона.

В основном, нейрон выполняет множество операций умножения с накоплением, MAC, по своим входным данным. Следовательно, нейронные сети с большим числом нейронов и высокой взаимосвязанностью должны выполнять огромное число MAC-операций. Поскольку сегодня нейронные сети, главным образом, реализуются в цифре, и поскольку цифровая MAC-операция является дорогостоящей в вычислительном отношении, требуется значительное количество вычислительной мощности. Следовательно, традиционные нейронные сети типично не реализуются на оконечных устройствах с питанием от аккумулятора.

Напротив, традиционные аналоговые нейронные реализации выдают себя за более энергоэффективные, но требуют большого усилия для реализации, которое увеличивается экспоненциально с числом входных данных соответствующего нейрона. Кроме того, точность MAC-операций аналогового нейрона имеет влияние на общую точность и четкость аналоговой нейронной сети, в частности, относительно увеличивающегося числа нейронов и/или числа взаимосвязей между нейронами. Традиционные аналоговые нейроны имеют недостатки в этом отношении.

Целью, которая должна быть достигнута, является предоставление улучшенной концепции для аналоговых нейронных сетей с улучшенной производительностью и/или гибкостью.

Эта цель достигается посредством объекта изобретения по независимым пунктам формулы изобретения. Варианты осуществления и развития улучшенной концепции определяются в зависимых пунктах формулы изобретения.

Улучшенная концепция основывается на представлении, что две основные функции аналогового нейрона должны быть эффективно реализованы, которые имеют различные требования реализации, а именно, взвешивание нескольких входных сигналов и их суммирование. Например, в то время как суммирование сигналов в текущей предметной области может быть легко осуществлено, взвешивание текущих сигналов требует гораздо большего усилия реализации, которое масштабируется вместе с числом весовых коэффициентов.

Улучшенная концепция, следовательно, предлагает аналоговый нейронный усилитель с двумя основными каскадами, каждый из которых может быть реализован эффективно и с высокой точностью. Первый каскад является осуществляющим выборку (дискретизирующим) каскадом с множеством входов для приема множества входных напряжений и с одним или более регулируемыми цифровым образом хранилищами заряда для выборки множества входных напряжений. Например, каждое из регулируемых цифровым образом хранилищ заряда регулируется на основе соответствующего веса для входного напряжения, выборку которого хранилище заряда осуществляет. Предпочтительно, входные напряжения предоставляются как дифференциальные напряжения, так что множество входов являются дифференциальными входами. Второй каскад является суммирующим каскадом для суммирования зарядов, обеспечиваемых в результате из полученного выборкой множества входных напряжений, для того, чтобы формировать сигнал суммирования. В частности, суммирующий каскад подключается ниже по потоку по отношению к осуществляющему выборку каскаду. Например, суммирующий каскад содержит по меньшей мере одну пару хранилищ заряда для хранения суммированных зарядов.

Дополнительные каскады аналогового нейронного усилителя могут содержать каскад буфера и активации, который может применять функцию активации и формировать буферизованное выходное напряжение на дифференциальном выходе, на основе сигнала суммирования, соответственно суммированных зарядов.

Использование технологии переключаемого конденсатора для аналогового нейронного усилителя предоставляет возможность иметь эффективный интерфейс между различными каскадами усилителя, который может быть реализован с разумным усилием и все еще обеспечивает высокоточную работу. Использование подхода с дифференциальным сигналом дополнительно улучшает точность нейронного усилителя, например, уменьшая эффекты инжекции заряда, которые могут быть вредными для точности итогового результата вычисления.

Улучшенная концепция предоставляет реализацию для нейронного усилителя с дифференциальным переключаемым конденсатором, который, например, подходит для использования в аналоговой искусственной нейронной сети. Нейронный усилитель содержит осуществляющий выборку каскад с множеством дифференциальных входов для приема множества входных напряжений и с по меньшей мере одной парой регулируемых цифровым образом хранилищ заряда для выборки множества входных напряжений. Нейронный усилитель дополнительно содержит суммирующий каскад для суммирования зарядов, обеспечиваемых в результате из полученного выборкой множества входных напряжений, для того, чтобы формировать сигнал суммирования. Суммирующий каскад подключается ниже по потоку по отношению к осуществляющему выборку каскаду. Каскад буфера и активации конфигурируется, чтобы применять функцию активации и формировать буферизованное выходное напряжение на дифференциальном выходе, на основе сигнала суммирования. Как упомянуто выше, каждое регулируемое цифровым образом хранилище заряда может быть отрегулировано согласно соответствующему весу, который должен быть реализован для входного напряжения, выборка которого должна быть осуществлена.

Следует понимать, что суммирующий каскад выполняет операцию суммирования в аналоговой области, так что, в частности, преобразование или операция в цифровой области не требуется. Следовательно, сигнал суммирования формируется как аналоговый сигнал.

Существует несколько реализаций относительно взаимодополняющих дифференциальных входов и пар регулируемых цифровым образом хранилищ заряда и их соответствующих межсоединений. Например, в некоторых реализациях число дифференциальных входов соответствует числу пар регулируемых цифровым образом хранилищ заряда. Другими словами, для каждого входа из дифференциальных входов предусматривается конкретная пара регулируемых цифровым образом хранилищ заряда. Это означает, что все дифференциальные входные напряжения могут быть получены выборкой по соответствующей ассоциированной паре хранилищ заряда в одно и то же время, предоставляя возможность более быстрой работы сигнала суммирования и, следовательно, всего нейронного усилителя. Тем не менее, это происходит с таким результатом, что усилие реализации нейронного усилителя повышается с точки зрения площади вследствие большего числа пар хранилищ заряда.

В альтернативной реализации осуществляющий выборку каскад содержит по меньшей мере один мультиплексор для выборочного соединения множества дифференциальных входов с по меньшей мере одной парой регулируемых цифровым образом хранилищ заряда. Соответственно, временное разделение сигналов может применяться для выборки дифференциальных входных напряжений по регулируемым цифровым образом хранилищам заряда, т.е., повторное использование одной и той же пары регулируемых хранилищ заряда для нескольких различных входных напряжений.

Например, число мультиплексоров соответствует числу пар регулируемых цифровым образом хранилищ заряда. Следовательно, например, единственная пара регулируемых цифровым образом хранилищ заряда может быть предусмотрена вместе с единственным мультиплексором, соединяющим все дифференциальные входы с парой хранилищ заряда. Это приведет в результате к уменьшенному усилию для реализации регулируемых цифровым образом хранилищ заряда с разумным усилием для мультиплексора. Кроме того, вследствие временного разделения сигналов, времена обработки могут увеличиваться.

Однако, если число пар регулируемых цифровым образом хранилищ заряда и ассоциированных мультиплексоров увеличивается, время обработки может быть сокращено со слегка возросшим усилием для хранилищ заряда, предоставляя возможность уравновешивания усилия и скорости.

Суммирующий каскад согласно различным реализациям, например, содержит дифференциальный интегрирующий усилитель с парой интегрирующих хранилищ заряда на пути дифференциальной обратной связи интегрирующего усилителя. Например, интегрирующий усилитель реализуется как операционный усилитель с активной межэлектродной проводимостью. Дифференциальный интегрирующий усилитель предоставляет возможность эффективного переноса сохраненных зарядов в осуществляющем выборку каскаде в суммирующий каскад и их интегрирование, т.е., их суммирование, по интегрирующим хранилищам заряда.

Например, в некоторых таких реализациях суммирующий каскад дополнительно содержит пару хранилищ заряда двойной выборки, выборочно подключаемых ниже по потоку от интегрирующего усилителя. В такой реализации нейронный усилитель, например, конфигурируется, чтобы осуществить выборку нулевого входного сигнала по паре хранилищ заряда двойной выборки во время первой фазы двойной выборки, например, устанавливая по меньшей мере одну пару регулируемых цифровым образом хранилищ заряда в нулевое значение, и предоставлять заряды, обеспечиваемые в результате из полученного выборкой нулевого входного сигнала, в каскад буфера и активации вместе с зарядами, сохраненными в паре интегрирующих хранилищ заряда.

Следовательно, например, суммированию нейронных сигналов предшествует суммирование нулевого входного сигнала, которое может быть осуществлено посредством регулирования регулируемых хранилищ заряда, так что они осуществляют выборку не соответствующего входного напряжения, а, например, нулевого напряжения или напряжения синфазного режима. Таким образом, смещение осуществляющего выборку каскада и интегрирующего усилителя может быть извлечено и вычтено во время окончательного переноса заряда в каскад буфера и активации, т.е., реализации схемы коррелированной двойной выборки.

Например, в некоторых других таких реализациях с дифференциальным интегрирующим усилителем, нейронный усилитель дополнительно содержит схему прерывания (chopping) в себе и перед суммирующим каскадом, которая может уменьшать ошибки инжекции заряда, получающиеся в результате остаточных ошибок различных компонентов.

Например, нейронный усилитель дополнительно содержит для каждого из по меньшей мере одного мультиплексоров, первый дифференциальный блок прерывания, подключенный между выходом соответствующего мультиплексора и подсоединенной парой хранилищ заряда. Нейронный усилитель дополнительно содержит второй и третий дифференциальный блок прерывания, при этом второй дифференциальный блок прерывания соединяет первый конец пути обратной связи интегрирующего усилителя с входной стороной интегрирующего усилителя, в то время как третий блок прерывания соединяет второй конец пути обратной связи с выходной стороной интегрирующего усилителя. Предпочтительно второй и третий блок прерывания управляются скоординированным образом. Также первый дифференциальный блок прерывания для каждого из мультиплексоров может управляться скоординированным образом со вторым и третьим блоками прерывания. Например, каждый блок прерывания может переключаться между прямым и перекрестным соединением дифференциальных сигнальных линий. Прерывание может нейтрализовать какие-либо остаточные смещения от всех входных переключателей выборки, предоставляя возможность для почти произвольного числа входов нейронного усилителя.

В некоторых реализациях дифференциальный интегрирующий усилитель суммирующего каскада содержит переключающую схему для выборочной зарядки пары интегрирующих хранилищ заряда с помощью входного напряжения смещения интегрирующего усилителя плюс входное смещение каскада буфера и активации. Например, переключающая схема предоставляет возможность для выборочной зарядки пары интегрирующих хранилищ заряда с помощью первого напряжения смещения на входной стороне интегрирующего усилителя и второго напряжения смещения на входной стороне каскада буфера и активации. Например, такая реализация предоставляет возможность того, что во время суммирования смещение интегрирующего усилителя на выходной стороне интегрирующего усилителя устраняется, и смещение каскада буфера и активации применяется, чтобы компенсировать упомянутое смещение каскада буфера и активации.

Например, первое и второе напряжение смещения получаются выборкой по интегрирующим хранилищам заряда в течение периода времени, в котором суммирование не происходит, и только соответствующие напряжения смещения присутствуют, получающиеся в результате соответствующих настроек переключающей схемы. Во время фактического суммирования зарядов осуществляющего выборку каскада получаемые выборкой напряжения смещения нейтрализуются этими напряжениями смещения, также присутствующими во время такой фазы суммирования.

В некоторых реализациях каскад буфера и активации содержат буферный каскад с дифференциальным емкостным усилителем с дополнительной парой хранилищ заряда и дополнительным путем дифференциальной обратной связи емкостного усилителя. Такая реализация, например, предоставляет возможность легкого переноса зарядов, суммированных и сохраненных в интегрирующих хранилищах заряда, в буферный каскад для того, чтобы предоставлять возможность формирования буферизованного выходного напряжения. Аналогично суммирующему каскаду, также дифференциальный емкостной усилитель буферного каскада может быть реализован как OTA.

В некоторых таких реализациях функция активации каскада буфера и активации может быть реализована посредством ограничения питающего напряжения емкостного усилителя и/или буферного каскада. Например, функция отсечения может быть реализована в этом способе в качестве функции активации, ограничивающая выходное напряжение между положительным и отрицательным питающими напряжениями, соответственно.

В некоторых альтернативных реализациях каскад буфера и активации дополнительно содержит отсекающий каскад, подключенный выше по потоку или ниже по потоку от буферного каскада, и при этом функция активации реализуется посредством отсекающего каскада. Это, например, предоставляет возможность реализации более сложных функций отсечения.

Например, отсекающий каскад подключается ниже по потоку от буферного каскада и конфигурируется, чтобы сравнивать дифференциальное напряжение на выходе буферного каскада с дифференциальным опорным напряжением. Отсекающий каскад может выводить дифференциальное опорное напряжение на дифференциальном выходе, если дифференциальное напряжение на выходе буферного каскада превышает дифференциальное опорное напряжение либо в положительном, либо отрицательном направлении. Аналогично, отсекающий каскад выводит на дифференциальном выходе дифференциальное напряжение на выходе буферного каскада, например, без отсечки.

В различных реализациях нейронного усилителя каждое регулируемое цифровым образом хранилище заряда из по меньшей мере одной пары регулируемых цифровым образом хранилищ заряда может содержать первый и второй зарядный вывод и множество подвергаемых весовой обработке хранилищ заряда, каждое имеет первый конец, соединенный с первым зарядным выводом, и второй конец, соответственно соединенный со вторым зарядным выводом или с выводом синфазного режима, в зависимости от цифрового кода регулировки. Например, цифровой код регулировки соответствует желаемому весовому коэффициенту, который должен быть применен к соответствующему входному напряжению.

Например, множество подвергаемых весовой обработке хранилищ заряда бинарно взвешиваются, так что соседние хранилища заряда различаются по своей емкости на коэффициент, равный двум. В других реализациях все хранилища заряда могут иметь одинаковый вес, соответственно, емкость, таким образом, реализуя, например, линейную схему взвешивания. Кроме того, линейное и бинарное взвешивание могут сочетаться. Предпочтительно, регулируемые хранилища заряда из пары создаются соответствующими друг другу, в частности, создаются номинально идентичными, и управляются обычно, чтобы иметь одинаковую емкость во время выборки.

В различных реализациях нейронный усилитель может дополнительно содержать схему управления для управления функцией переключаемого конденсатора нейронного усилителя и/или для регулировки по меньшей мере одной пары регулируемых цифровым образом хранилищ заряда. Это может включать в себя управление мультиплексорами и/или каскадами прерывателя (chopper), если применимо.

Нейронный усилитель согласно одной из реализаций, упомянутых выше, может быть использован в аналоговой искусственной нейронной сети, например, рекуррентной нейронной сети. Такая нейронная сеть может содержать множество таких нейронных усилителей, при этом дифференциальный выход по меньшей мере одного из нейронных усилителей соединяется с одним из дифференциальных входов того же или другого усилителя из нейронных усилителей. Нейронная сеть может содержать несколько уровней, например, входной уровень, выходной уровень и один или более скрытых уровней, каждый из которых содержит один или более нейронных усилителей, как описано выше. Аналоговая реализация нейронной сети предоставляет возможность эффективной реализации вместе, например, с аналоговыми датчиками вследствие аналогичных процессов изготовления. Потребление мощности снижается по сравнению с традиционными цифровыми нейронными сетями, поскольку, например, аналого-цифровые преобразователи и процессоры нейронной сети не нужны.

Соответственно, улучшенная концепция также предлагает устройство датчика, содержащее один или боле датчиков, например, аналоговых датчиков, и аналоговую искусственную нейронную сеть, как описано ранее, при этом выходные сигналы одного или более датчиков предоставляются, по меньшей мере, для одного из нейронных усилителей.

Обучение нейронной сети может выполняться в режиме онлайн, т.е., во время работы сети, оффлайн, например, посредством моделирования нейронной сети для того, чтобы определять соответствующие весовые коэффициенты, или даже как сочетание оффлайн-обучения с последующей онлайн-калибровкой, например. Другие реализации не исключаются этими примерами.

Улучшенная концепция будет описана более подробно ниже для нескольких вариантов осуществления со ссылкой на чертежи. Идентичные ссылочные номера обозначают сигналы, элементы или компоненты с идентичными функциями. Если сигналы, элементы или компоненты соответствуют друг другу по функции, их описание не будет обязательно повторяться на каждом из последующих чертежей.

На чертежах:

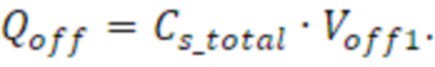

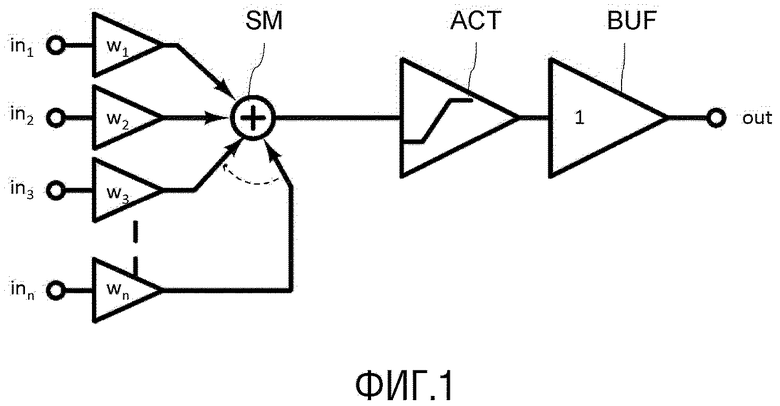

Фиг. 1 показывает примерную реализацию аналогового нейронного усилителя;

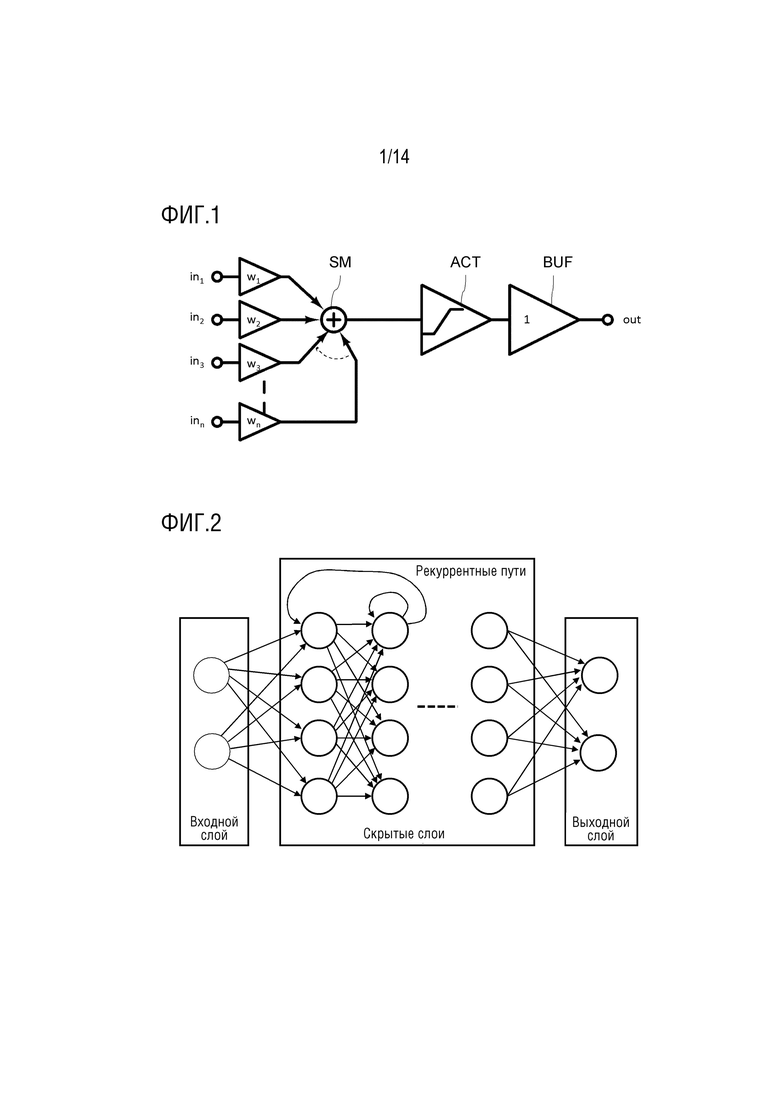

Фиг. 2 показывает примерную реализацию нейронной сети;

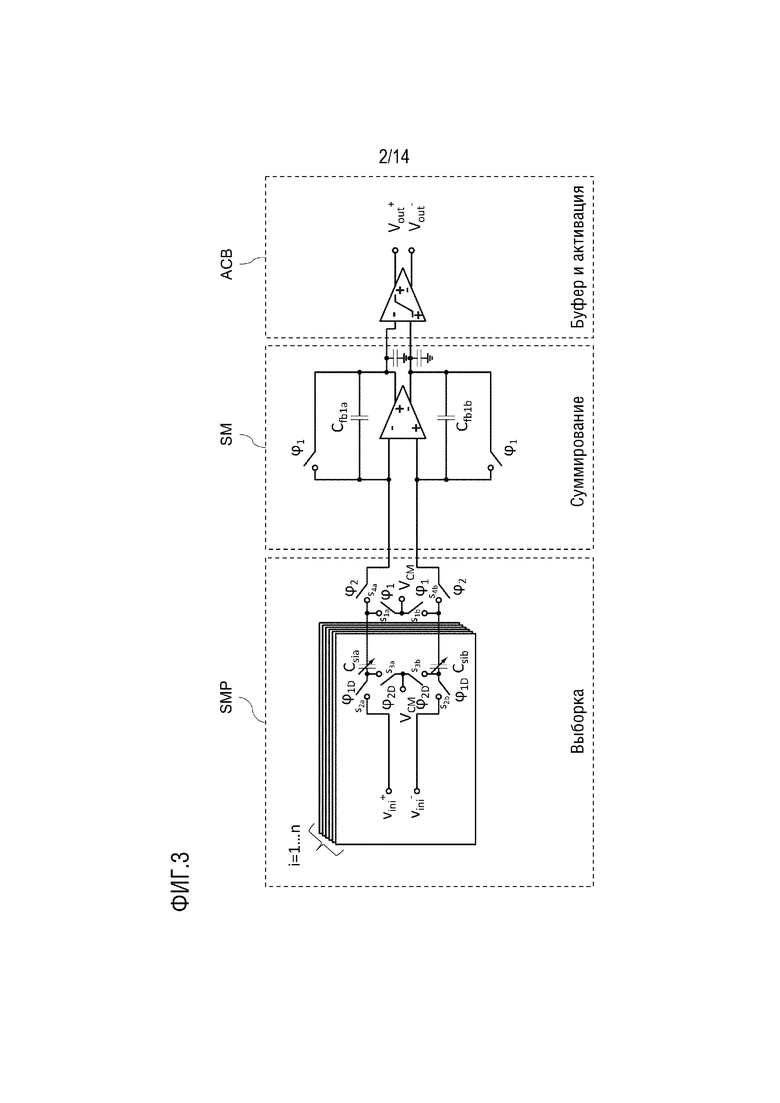

Фиг. 3 показывает примерную реализацию нейронного усилителя согласно улучшенной концепции;

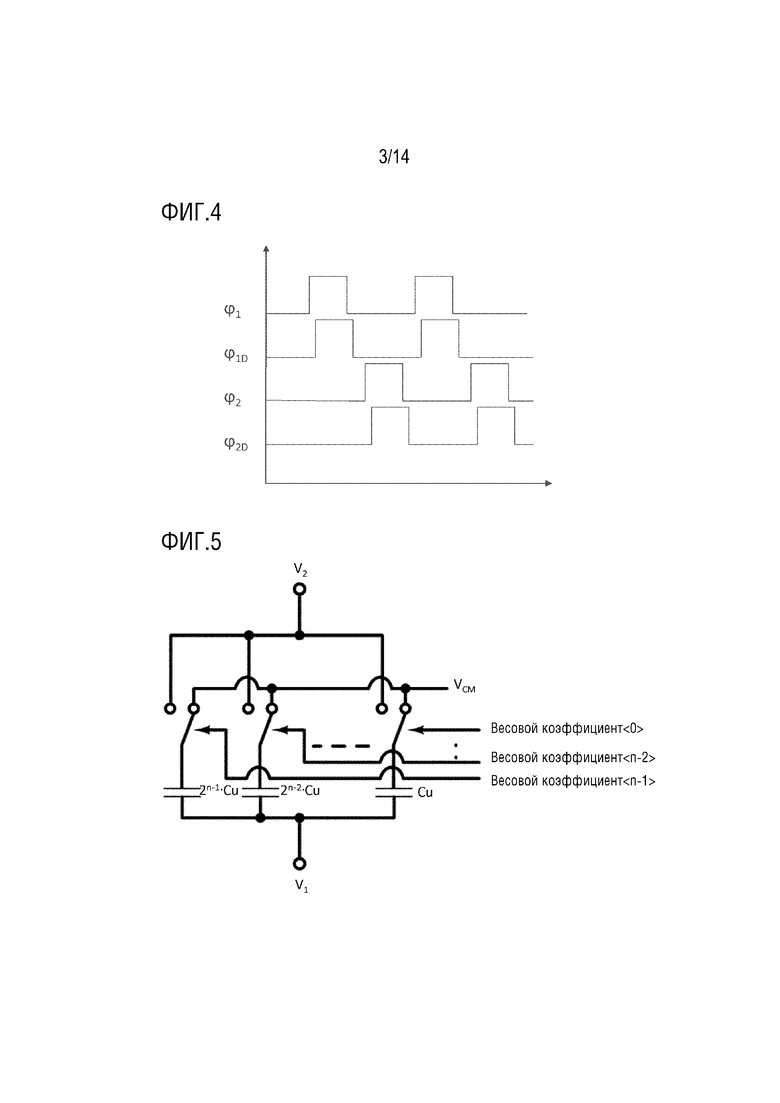

Фиг. 4 показывает примерную диаграмму управляющих сигналов, которые могут применяться к нейронному усилителю согласно фиг. 3;

Фиг. 5 показывает примерную реализацию регулируемого цифровым образом хранилища заряда;

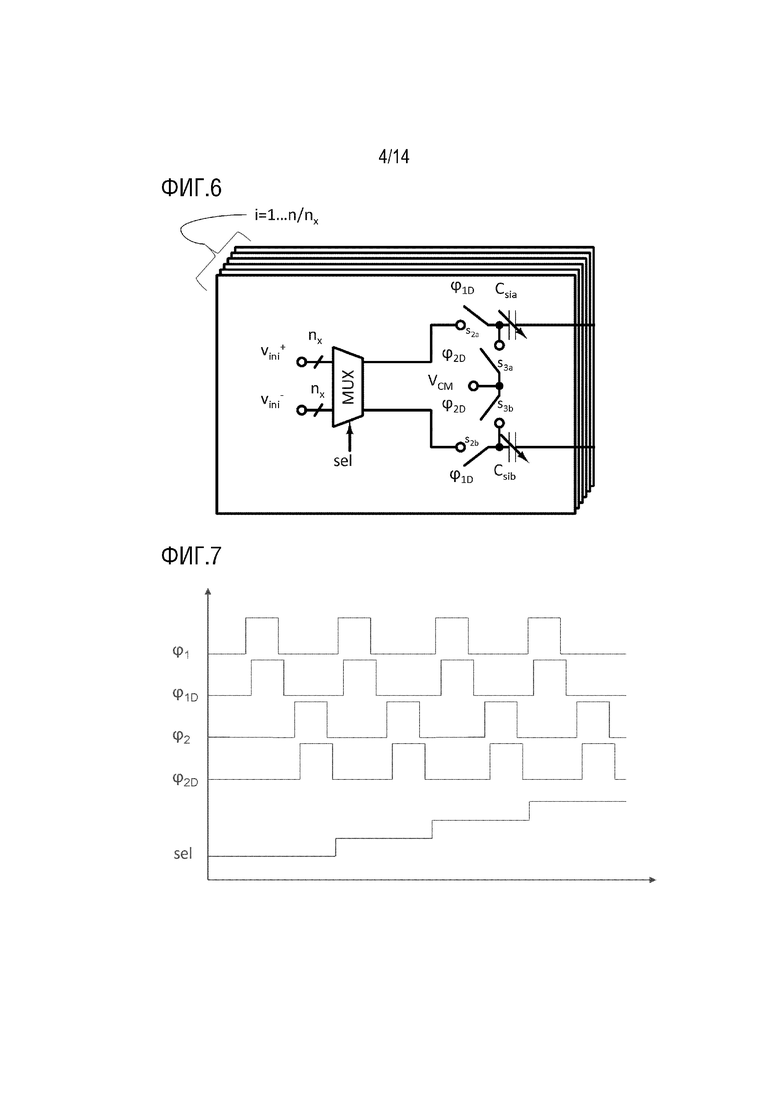

Фиг. 6 показывает примерную реализацию каскада выборки нейронного усилителя;

Фиг. 7 показывает примерную диаграмму управляющих сигналов, которые могут применяться к нейронному усилителю, реализованному согласно фиг. 6;

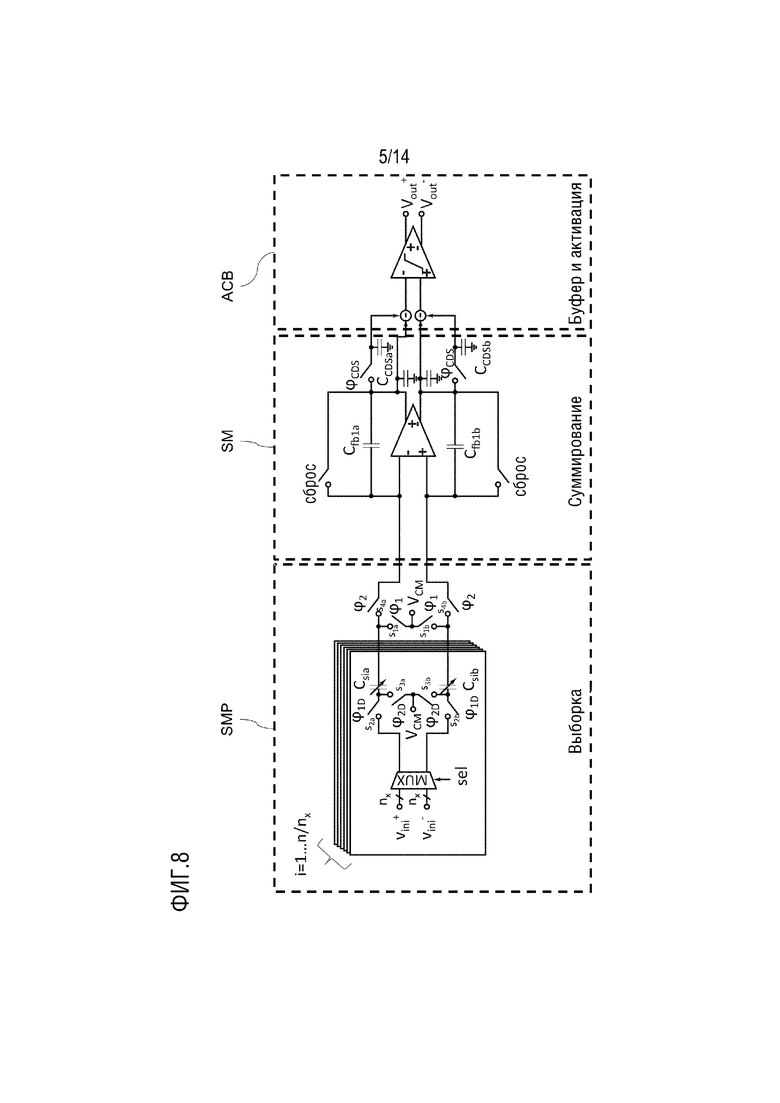

Фиг. 8 показывает дополнительную примерную реализацию нейронного усилителя согласно улучшенной концепции;

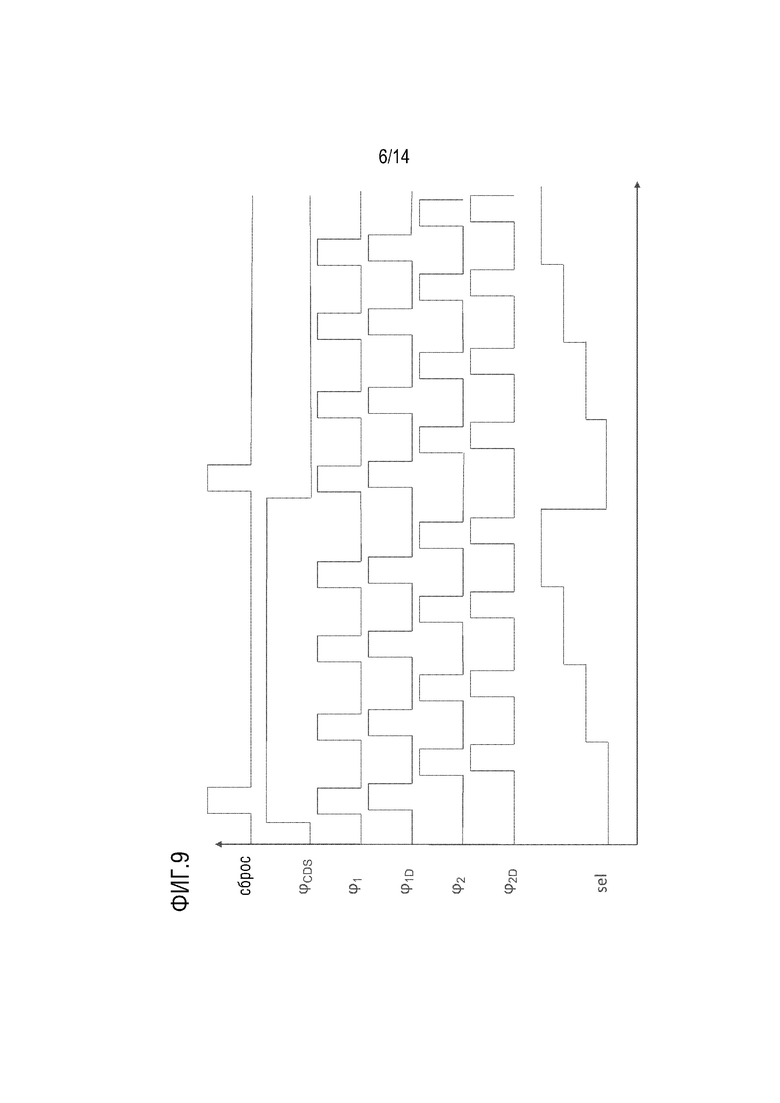

Фиг. 9 показывает примерную диаграмму управляющих сигналов, которые могут применяться к нейронному усилителю согласно фиг. 8;

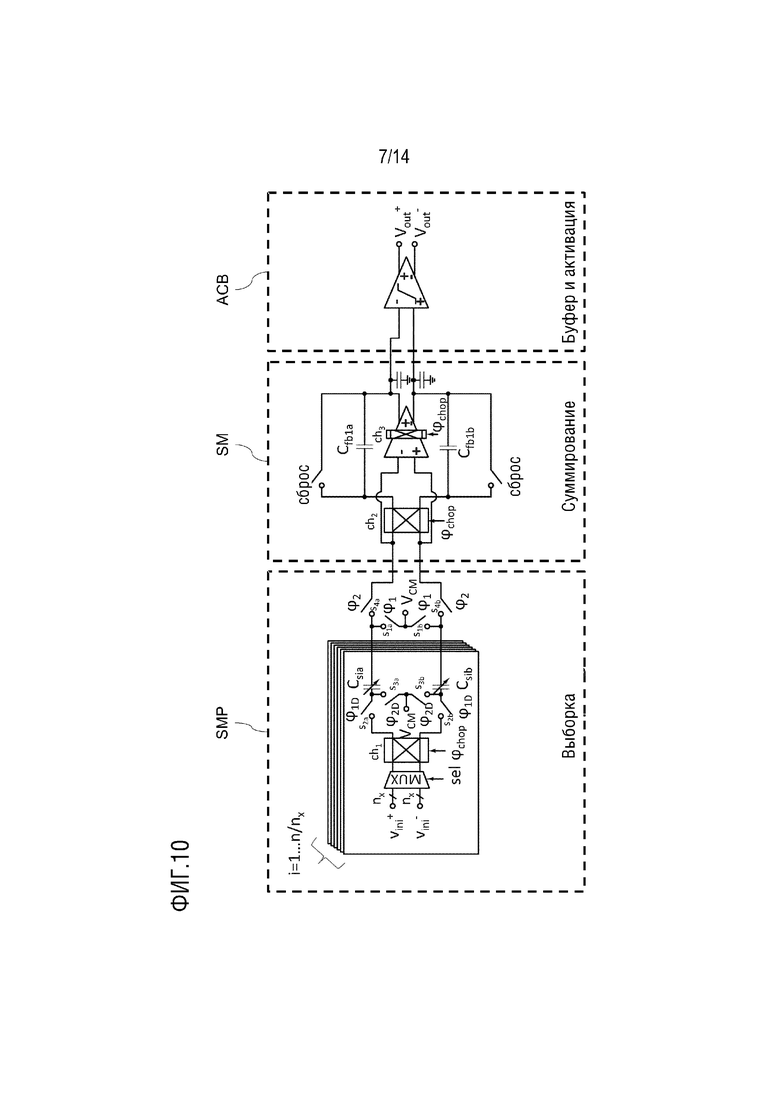

Фиг. 10 показывает дополнительную примерную реализацию нейронного усилителя согласно улучшенной концепции;

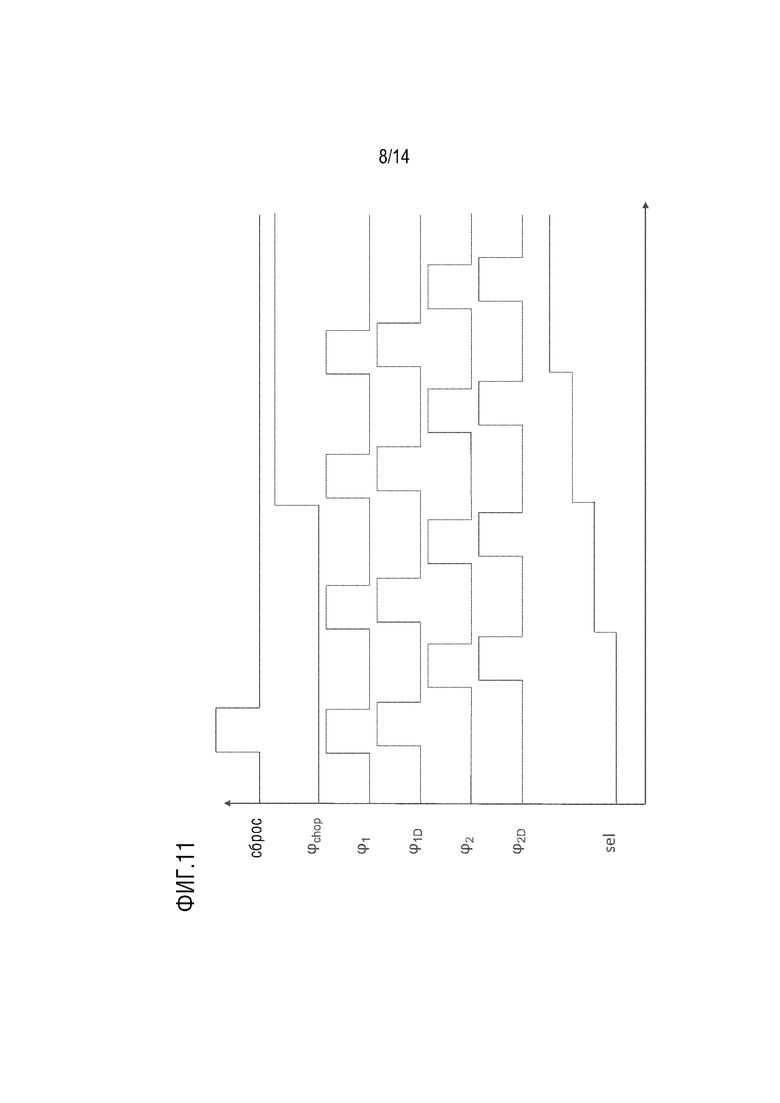

Фиг. 11 показывает примерную диаграмму управляющих сигналов, которые могут применяться к нейронному усилителю согласно фиг. 10;

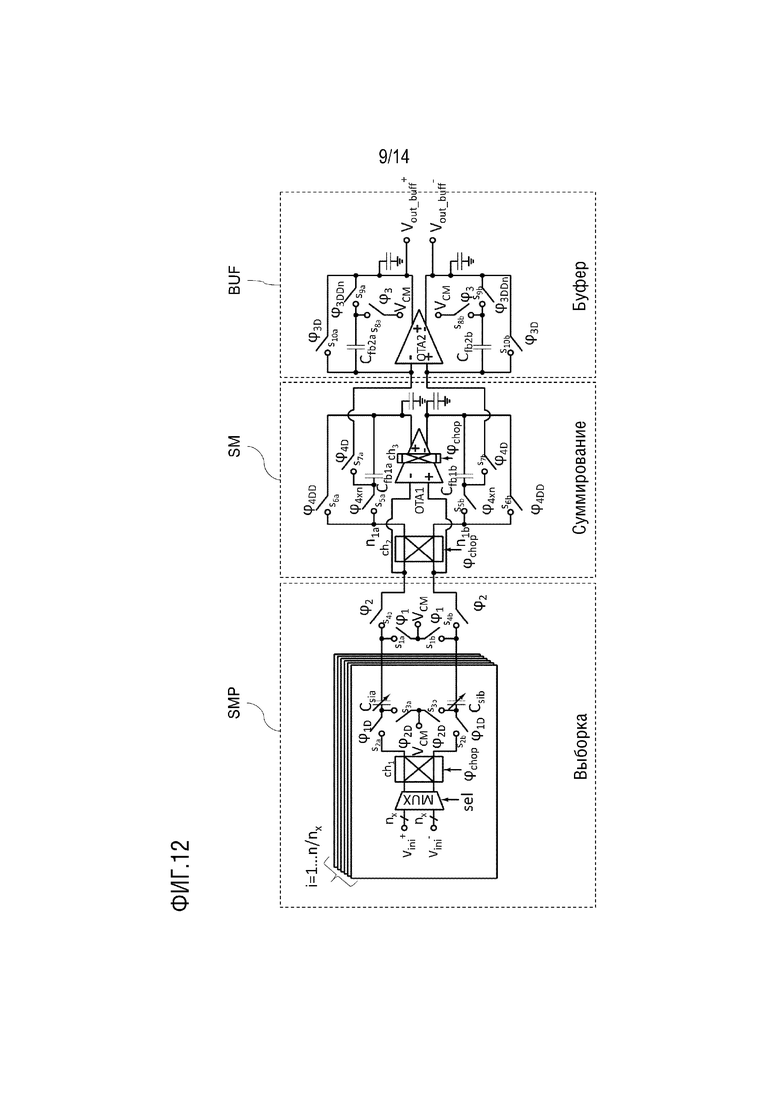

Фиг. 12 показывает дополнительную примерную реализацию нейронного усилителя согласно улучшенной концепции;

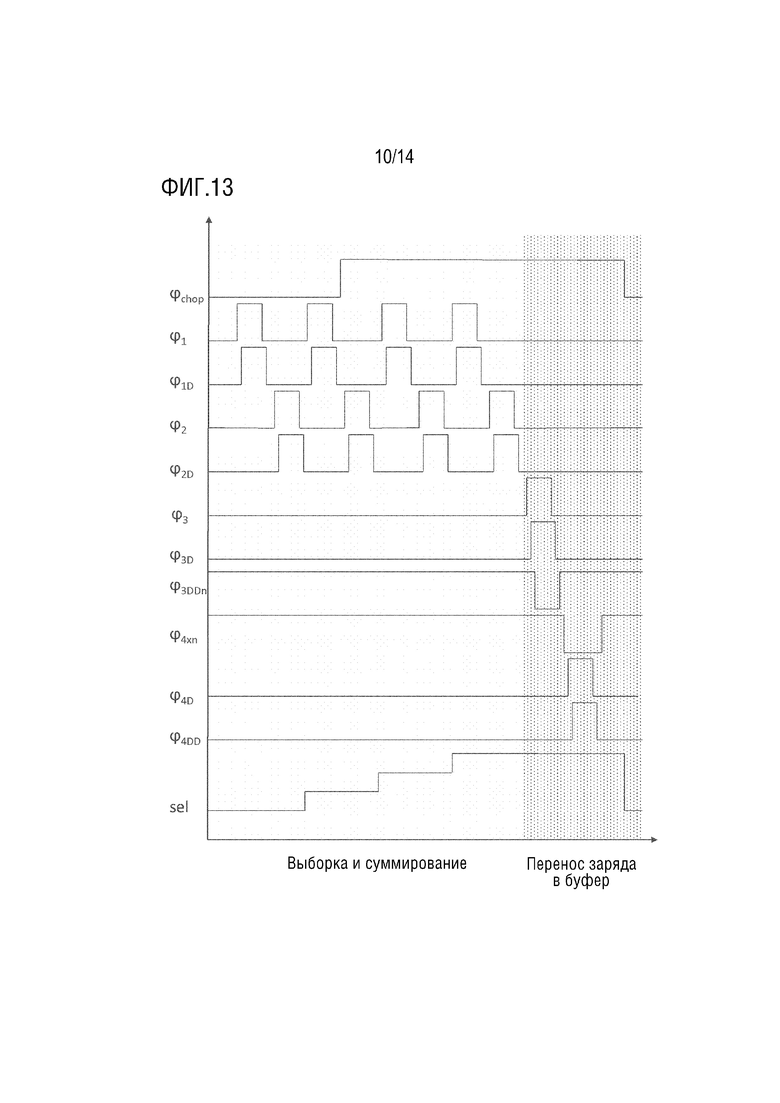

Фиг. 13 показывает примерную диаграмму управляющих сигналов, которые могут применяться к нейронному усилителю согласно фиг. 10;

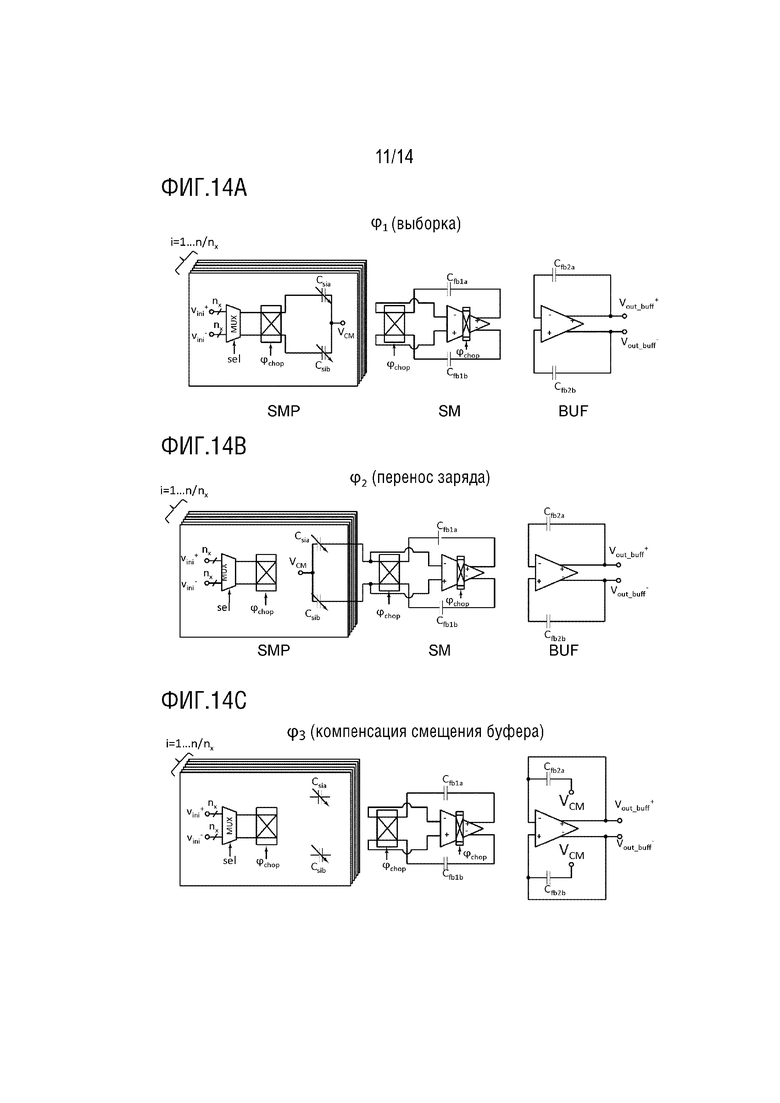

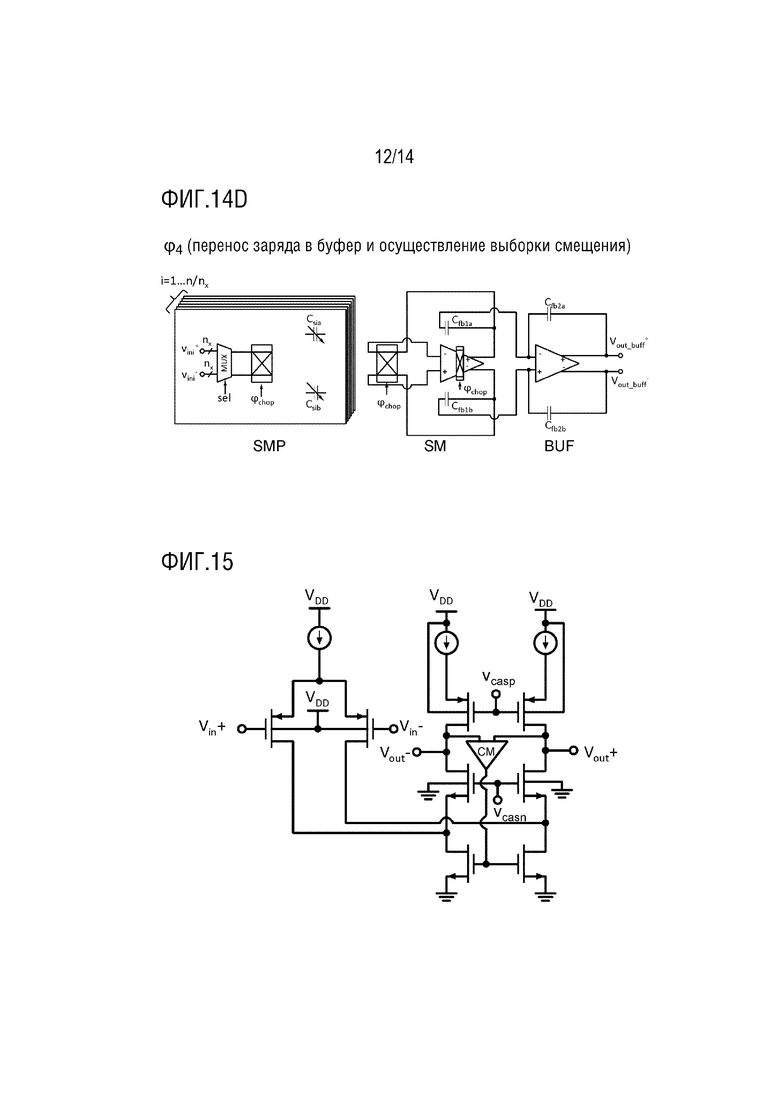

Фиг. 14A-14D показывают несколько примерных фаз, которые должны применяться к нейронному усилителю согласно улучшенной концепции;

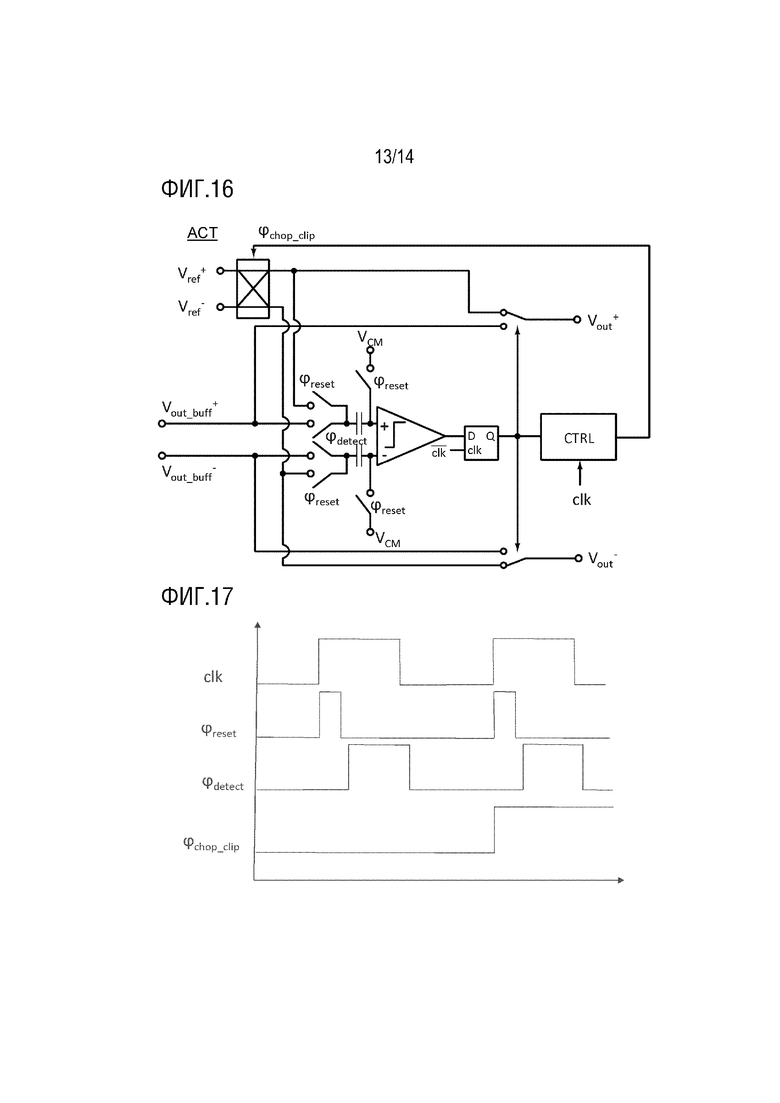

Фиг. 15 показывает примерную реализацию операционного усилителя с активной межэлектродной проводимостью в нейронном усилителе;

Фиг. 16 показывает примерную реализацию отсекающего каскада, используемого в нейронном усилителе;

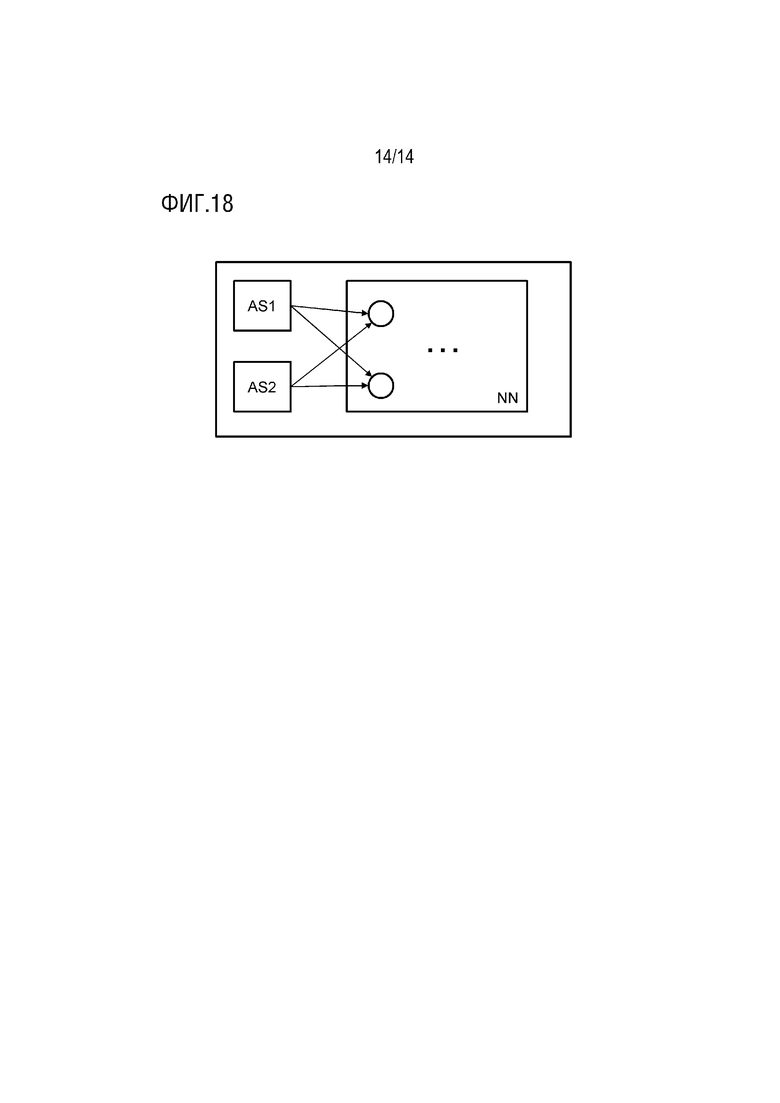

Фиг. 17 показывает примерную диаграмму управляющих сигналов, которые могут применяться к отсекающему каскаду согласно фиг. 14; и

Фиг. 18 показывает примерную реализацию устройства датчика с аналоговой искусственной нейронной сетью.

Фиг. 1 показывает примерную реализацию аналогового нейронного усилителя с множеством входов in1, in2, in3, …, inn, соединяемыми с соответствующим числом взвешивающих элементов w1, w2, w3, …, wn. Выходы взвешивающих элементов соединяются с входами суммирующего каскада для предоставления сигнала суммирования. В основном, суммирующий каскад вместе с взвешивающими элементами выполняет ряд операций умножения с накоплением, MAC, по множеству входов in1, in2, in3, …, inn. Следует понимать, что суммирующий каскад выполняет операцию суммирования в аналоговой области, так что, в частности, преобразование или операция в цифровой области не требуется. Аналоговый сигнал суммирования на выходе суммирующего каскада SM предоставляется каскаду ACT активации для применения функции активации, например, функции отсечки или т.п., к сигналу суммирования. Выходной сигнал каскада ACT активации предоставляется буферному каскаду BUF для предоставления буферизованного выходного сигнала, например, выходного напряжения на выходе OUT нейронного усилителя. Фиг. 1 описывает основную функцию нейронного усилителя, который может быть использован, например, в аналоговой нейронной сети.

Например, нейронная сеть является каскадом нейронных слоев, которые являются взаимосвязанными. Фиг. 2 показывает примерную реализацию такой нейронной сети с множеством нейронов, распределенных по нескольким слоям и представленных кругами на фиг. 2. Например, нейронная сеть содержит входной слой, выходной слой и несколько скрытых слоев. Выход каждого нейрона может быть соединен с одним или более другими нейронами нейронной сети, указанными стрелками, начинающимися от соответствующих нейронов. Следовательно, каждый нейрон может быть соединен с выходом одного или более других нейронов или даже своим собственным выходом, тем самым, устанавливая рекуррентный путь.

Как упомянуто ранее, нейронные сети с большим числом нейронов и высокой взаимосвязанностью должны выполнять огромное число MAC-операций. Сегодняшние нейронные сети, главным образом, реализуются цифровым образом, таким образом, требуя значительной величины вычислительной мощности. В отличие от этого, аналоговая MAC-операция является, в принципе, пошаговой операцией. Тогда как значения в цифровой области представляются множеством битов, в аналоговой только единственный блок хранения требуется для удерживания значения независимо от разрешения. Следовательно, существует возрастающее усилие для перемещения MAC-операций в аналоговую область, открывая большое пространство для аналоговых нейронных сетей. Аналоговые нейронные сети не полагаются на узлы субнанометровой технологии, чтобы добиваться конкурентной производительности. Скорость достигается посредством максимального использования аналоговых свойств, которые не масштабируются хорошо вместе с технологией. Это поддерживает реализацию в более старых бюджетных и аналоговых оптимизированных технологиях. Аналоговые нейронные сети, следовательно, являются привлекательным вариантом для совместного объединения, например, со считывающими схемами аналогового датчика.

Реализация аналогового нейрона для рекуррентной нейронной сети требует усилителя, который может суммировать свои входные данные, в то же время удерживая предыдущее значение и возбуждая другие входы нейрона в то же самое время. Производительность может даже быть увеличена посредством реализации малой ошибки коэффициента усиления и смещения, что предотвращает накопление ошибок в течение различных циклов. Например, в рекуррентных нейронных сетях, результаты сообщаются по обратной связи предыдущим нейронам по соответствующим рекуррентным путям, как указано на фиг. 2.

В последующем, несколько примерных реализаций аналогового нейронного усилителя согласно улучшенной концепции будет описано, которые подходят для эффективной реализации аналоговой нейронной сети с или без рекуррентных путей. Улучшенная концепция предоставляет возможность аналоговой реализации нейрона с обработкой дифференциального сигнала и подходом с переключаемым конденсатором, который снижает эффекты инжекции заряда, таким образом, улучшая позицию аналогового нейрона и, следовательно, аналоговой нейронной сети, реализованной с такими нейронами. Производительность может быть дополнительно улучшена посредством включения переключаемой инжекции заряда и/или схемы нейтрализации смещения усилителя. Вкратце, большое число нейронов может быть соединено с единственным суммирующим узлом даже в рекуррентной операции без значительного накопления смещения. Кроме того, делая ошибки смещения и ошибки коэффициента усиления ничтожными, соответствующие дрейфы по PVT не являются проблемой. Следовательно, периодическое переобучение или калибровка не нужны.

Фиг. 3 показывает примерную реализацию аналогового нейронного усилителя с осуществляющим выборку каскадом SMP, суммирующим каскадом SM и каскадом ACB буфера и активации. Как указано в сочетании с фиг. 1, фиг. 3 реализует осуществляющий выборку каскад с n входами с n параллельными структурами выборки, из которых только примерная структура показана по причинам лучшего обзора. Структура выборки имеет дифференциальную пару Vini+, Vini- входов, представляющую вход i из n возможных входов. Каждая структура дополнительно содержит пару регулируемых цифровым образом хранилищ Csia, Csib заряда, которые имеют свой первый вывод, соединенный с дифференциальным сигнальным входом Vini+, Vini- через соответствующие переключатели S2a, S2b. Первый вывод хранилищ Csia, Csiab заряда также соединяется с выводом VCM синфазного режима через соответствующие переключатели S3a, S3b.

Вторые выводы хранилищ Csia, Csib заряда соединяются с выводом VCM синфазного режима через дополнительные соответствующие переключатели S1a, S1b и дополнительно с суммирующим каскадом SM через соответствующие переключатели S4a, S4b. В то время как пара хранилищ Csia, Csib заряда и соответствующие переключатели S2a, S2b, S3a, S3b присутствуют множество раз в осуществляющем выборку каскаде SMP, т.е., n раз, переключатели S1a, S1b, S4a, S4b могут быть общими для всех таких структур выборки и предоставлены лишь однократно, однако, без исключения возможности многократного присутствия.

Хранилища Csia, Csib заряда являются регулируемыми цифровым образом, в частности, для настройки соответствующего весового коэффициента для ассоциированного входа Vini+, Vini-, на котором дифференциальное входное напряжение может быть принято.

Суммирующий каскад SM, например, содержит усилитель, например, операционный усилитель с активной межэлектродной проводимостью, OTA, с парой интегрирующих хранилищ Cfb1a, Cfb1b заряда на пути обратной связи интегрирующего усилителя. Соответствующие переключатели соединяются параллельно интегрирующим хранилищам Cfb1a, Cfb1b заряда для их сброса. Суммирующий каскад работает в аналоговой области, так что, в частности, преобразование или операция в цифровой области не требуется, и аналоговый сигнал суммирования выводится.

Ниже по потоку по отношению к суммирующему каскаду SM подключается каскад ACB буфера и активации, который конфигурируется, чтобы применять функцию активации и формировать буферизованное выходное напряжение Vout+, Vout- на дифференциальном выходе, на основе сигнала суммирования, сформированного в суммирующем каскаде SM.

Фиг. 4 показывает примерную диаграмму управляющих сигналов, которые могут применяться к нейронному усилителю согласно фиг. 3. В частности, фиг. 4 показывает сигналы φ1, φ1D, φ2 и φ2D управления переключателем. Например, временами, когда φ1 и φ1D, который является слегка задержанной версией φ1, имеют высокий уровень, соответствующие переключатели, управляемые этими сигналами, замыкаются, так что регулируемые хранилища заряда, каждое, подключаются между соответствующим входным выводом Vini+, соответственно Vini- и выводом VCM синфазного режима через переключатели S1a, S1b. Кроме того, интегрирующие хранилища Cfb1a и Cfb1b заряда сбрасываются.

Во времена высокого уровня переключающих сигналов φ2 и слегка задержанного φ2D соответствующие первые выводы регулируемых хранилищ заряда соединяются с выводом VCM синфазного режима, в то время как вторые выводы соединяются с суммирующим каскадом через переключатели S4a, S4b. Это приводит в результате к тому, что суммирующий каскад суммирует заряды, обеспечиваемые в результате из полученного выборкой множества входных напряжений на соответствующих парах регулируемых хранилищ заряда для того, чтобы формировать сигнал суммирования. Дифференциальный подход уменьшает влияния бездействия заряда, получающегося в результате от различных переключателей.

Фиг. 5 показывает примерную реализацию регулируемого цифровым образом хранилища заряда, которое, например, может быть использовано в различных структурах выборки осуществляющего выборку каскада SMP. Например, хранилище заряда содержит первый зарядный вывод V1 и второй зарядный вывод V2 и множество подвергаемых весовой обработке хранилищ заряда, каждое имеет первый конец, соединенный с первым зарядным выводом V1, и второй конец, выборочно соединяемый со вторым зарядным выводом V2 или с выводом VCM синфазного режима, в зависимости от цифрового кода регулировки. В примере на фиг. 5 хранилища заряда бинарно взвешиваются, начиная с первого хранилища заряда, имеющего значение Cu емкости, а n-ое хранилище заряда имеет значение емкости 2n-1∙Cu. Соответствующие переключатели управляются посредством цифрового кода регулировки, содержащего отдельные биты weight<0>, …, weight<n-2>, weight<n-1>. Другие схемы взвешивания вместо бинарной схемы взвешивания также могут быть использованы.

Реализация на фиг. 5 может называться цифро-аналоговым преобразователем, ЦАП, конденсатора выборки, поскольку цифровой код регулировки преобразуется в аналоговое значение емкости, в частности, с помощью схемы бинарного взвешивания.

Обращаясь обратно к фиг. 3, если все n входов нейрона должны быть получены выборкой и суммированы за один цикл, суммарное число отдельных линий маршрутизации будет n*nadj, обозначающим числом битов кода регулировки регулируемого хранилища заряда.

На практике, сложность маршрутизации увеличивается с числом дифференциальных входов и с числом точности nadj по весу. Для того, чтобы получать сложность маршрутизации O(n), мультиплексирование нейронных входов может выполняться, так что, например, различные дифференциальные входные напряжения получаются выборкой и суммируются в последовательных фазах. Это также означает, что пары регулируемых цифровым образом хранилищ заряда или ЦАПов конденсатора повторно используются для нескольких дифференциальных входов.

Обращаясь теперь к фиг. 6, показана примерная реализация части осуществляющего выборку каскада SMP, в частности, другая реализация параллельных структур выборки на входной стороне осуществляющего выборку каскада SMP. В целом, эта примерная реализация основывается на реализации на фиг. 3, но по меньшей мере один мультиплексор MUX вводится между несколькими дифференциальными вводами и ассоциированной парой Csia, Csib хранилищ заряда.

В этой примерной реализации nx входов мультиплексируются с одной парой регулируемых хранилищ Csia, Csib заряда, тем самым уменьшая сложность маршрутизации. Следует отметить, что число параллельных структур выборки, следовательно, уменьшается до n/nx по сравнению с n структур выборки на фиг. 3. Например, если для nadj точности по весу задается коэффициент nx мультиплексирования nx=nadj, непроизводительные затраты маршрутизации увеличиваются линейно с nadj.

Обращаясь теперь к фиг. 7, показана примерная диаграмма управляющих сигналов, которые могут применяться к нейронному усилителю в соответствии с фиг. 6. Для объяснения того или другого ссылка, в общем, выполняется на фиг. 4, которая выражает базовую схему между различными настройками переключателя, регулируемыми посредством сигналов φ1, φ1D, φ2 и φ2D. Теперь что касается фиг. 7, сигнал SEL выбора управляет мультиплексором MUX, чтобы последовательно соединять несколько входов с регулируемыми хранилищами зарядов. Например, nx выбирается равным 4 в этом примере, без потери обобщения.

Следовательно, сложность маршрутизации обменивается на время преобразования. Вследствие многофазного преобразования суммирующий сигнал, предоставляемый суммирующим каскадом, и, следовательно, также буферизованное выходное напряжение является недоступным для возбуждения выхода, соответственно дифференциальных входов других нейронных усилителей во время последующих циклов. Следовательно, сигнал суммирования суммирующего каскада подвергается выборке посредством каскада ACB буфера и активации после прошлой фазы суммирования. Буферизованное выходное напряжение может затем возбуждать дифференциальные входы других нейронных усилителей или один из своих собственных дифференциальных входов во время следующего рекуррентного цикла.

Дифференциальная структура значительно уменьшает ошибки зарядного действия даже для большого числа входных соединений с нейронным усилителем. Однако, ошибки инжекции остаточного заряда могут оставаться, например, возникающие из ошибок смещения, которые могут суммироваться в неничтожную величину, которая может дополнительно накапливаться в рекуррентном режиме работы, в зависимости от числа дифференциальных входов единственного нейронного усилителя и числа нейронов, применяемых в нейронной сети.

Обращаясь теперь к фиг. 8, показано дальнейшее развитие улучшенной концепции для нейронного усилителя, которое основывается на реализациях на фиг. 3 и фиг. 6. В этой примерной реализации, для того, чтобы устранять смещение посредством входного блока выборки и суммирующего усилителя применяется двойная коррелированная выборка, CDS. Для этого суммирующий каскад SM дополнительно содержит пару хранилищ CCDSa, CCDSb заряда двойной выборки, которая соединяется с выходной стороной интегрирующего усилителя через пару соответствующих переключателей, управляемых посредством управляющего сигнала φCDS двойной выборки. Кроме того, пара хранилищ CCDSa, CCDSb заряда двойной выборки соединяется с входной стороной каскада буфера и активации через соответствующие дифференциальные элементы для того, чтобы вычитать заряды, сохраненные в хранилищах CCDSa, CCDSb заряда двойной выборки, из зарядов, сохраненных в интегрирующих хранилищах Cfb1a и Cfb1b заряда.

Во время работы, в нейронном усилителе это может быть реализовано посредством отмены выбора всех блоков ЦАПов конденсатора, например, посредством их соединения с выводом VCM синфазного режима, таким образом, эффективно осуществляя выборку нулевого сигнала. Другими словами, нулевой вес может быть выбран для регулируемых хранилищ заряда во время этой фазы. Соответствующий выходной сигнал нейронного усилителя, таким образом, является эквивалентным его выходному смещению и может быть вычтен из фактического выходного сигнала нейронного усилителя с нейронными входными сигналами. Однако, поскольку выходной сигнал нейронного усилителя является аналоговым, эта операция не может быть реализована в цифре и будет выполняться во время переноса заряда в буфер. Это требует дополнительных хранилищ CCDSa, CCDSb заряда двойной выборки на выходе суммирующего усилителя, чтобы удерживать выходные сигналы суммирования нулевого входного сигнала во время последующего преобразования нейронного входного сигнала.

Однако, одной проблемой с двойной коррелированной выборкой является снижение скорости преобразования в 2 раза. Кроме того, вычитание смещения в аналоговом сигнале может привносить дополнительные источники ошибок.

Обращаясь теперь к фиг. 9, показана примерная диаграмма управляющих сигналов, которые могут применяться к нейронному усилителю согласно фиг. 8.

Обращаясь теперь к фиг. 10, показано дальнейшее развитие улучшенной концепции для нейронного усилителя, которое основывается на реализациях на фиг. 3 и фиг. 6. В дополнение к предыдущим реализациям, добавляется схема прерывания, в частности, посредством включения нескольких блоков ch1, ch2 и ch3 прерывания в нейронный усилитель. Введение прерывания (иногда также называемого заменой) является возможным вследствие многофазной схемы выборки, связанной с мультиплексором.

Например, первый блок ch1 прерывания предусматривается в каждой параллельной структуре выборки между мультиплексором MUX и подключенной парой регулируемых хранилищ Csia, Csib заряда. Кроме того, второй дифференциальный блок ch2 прерывания реализуется в суммирующем каскаде SM и соединяет первый конец пути дифференциальной обратной связи, включающего в себя интегрирующие хранилища Cfb1a, Cfb1b заряда, с входной стороной интегрирующего усилителя. Аналогично, третий дифференциальный блок ch3 прерывания соединяет второй конец пути дифференциальной обратной связи с выходной стороной интегрирующего усилителя.

Блоки ch1, ch2, ch3 прерывания управляются посредством управляющего сигнала φchop прерывания и имеют функцию либо непосредственного соединения дифференциального пути между своими входной и выходной сторонами, либо перекрестного соединения дифференциальных путей, что, в основном, соответствует инверсии дифференциального сигнала. Если фазы прерывания распределены равномерно по различным фазам переключения, прерывание может нейтрализовать любые остаточные смещения от всех входных переключателей выборки, предоставляя возможность почти произвольного числа дифференциальных входов.

Обращаясь теперь к фиг. 11, показана примерная диаграмма управляющих сигналов, которые могут применяться к нейронному усилителю согласно фиг. 10. Снова выполняется ссылка на предыдущие объяснения примерных диаграмм на фиг. 4 и фиг. 7. Например, в дополнение к схеме переключения на фиг. 7, сигнал φchop прерывания равен нулю во время первой половины фаз суммирования, так что смещение интегрирующего усилителя накапливается отрицательно, в то время как в течение второй половины, когда φchop имеет высокий уровень, смещение интегрирующего усилителя накапливается положительно. Следовательно, суммарный переносимый заряд смещения на Cfb1a, Cfb1b нейтрализует друг друга, приводя в результате, по меньшей мере теоретически, к нулевому заряду. Прерывание однократно только во время фаз суммирования уменьшает любое остаточное смещение, привносимое самими переключателями-прерывателями, поскольку их вклад добавляется только однократно.

Эффективность схемы прерывания дополнительно поддерживается в контексте нейронного усилителя, если суммарное эквивалентное смещение, которое является суммой отдельных входных смещений нейрона и смещения интегрирующего усилителя, является постоянным и, таким образом, не зависит от индивидуальных входных сигналов нейрона, управляющих регулируемыми цифровым образом хранилищами заряда во всех фазах. Например, обращаясь обратно к фиг. 5, если все единичные конденсаторы регулируемого цифровым образом хранилища заряда, которые не выбираются для выборки входного сигнала, т.е., не соединяются со вторым выводом V2, соединяются с выводом VCM синфазного режима. Это сохраняет соответствующие единичные конденсаторы активными, но эффективно с нулевым входным сигналом. Кроме того, инжекция заряда от всех переключателей S1a, S1b выборки добавляется независимо от различных весов, соответственно, настроек конденсатора, в различных фазах.

Несмотря на прерывание, точность нейронного усилителя может быть дополнительно увеличена, если сделана необходимой посредством соответствующей прикладной задачи, например, посредством сложности нейронной сети. Например, может быть выходное смещение на выходе суммирующего каскада SM после последней фазы φ2 суммирования, т.е., последнее входное напряжение было взвешено и суммировано, если сам суммирующий каскад SM не компенсирован по смещению.

Обращаясь теперь к фиг. 12, это может быть совершено посредством дополнительного развития нейронного усилителя согласно улучшенной концепции, показанной на фиг. 12, которая основывается на реализации, показанной на фиг. 10. В частности, осуществляющий выборку каскад SMP на фиг. 12 полностью соответствует осуществляющему выборку каскаду на фиг. 10.

В суммирующем каскаде SM вводится переключающая пара переключателей S5a, S5b, которые управляются по сигналу φ4xn переключения и соединяют дифференциальный вход интегрирующего усилителя OTA1 через второй блок ch2 прерывания с первым концом интегрирующих хранилищ Cfb1a, Cfb1b заряда. Переключатели S6a, S6b, управляемые сигналами φ4DD переключения, соответствуют переключателю сброса на фиг. 10. Переключатели S7a, S7b, управляемые сигналами φ4D переключения, соединяют первый вывод интегрирующих хранилищ Cfb1a, Cfb1b заряда с дифференциальным входом емкостного усилителя OTA2 буферного каскада BUF. Каскад активации, являющийся частью каскада ACB буфера и активации, не показан здесь по причинам лучшего обзора.

Буферный каскад BUF содержит дополнительную пару хранилищ Cfb2a, Cfb2b заряда, имеющих первый конец, соединенный с дифференциальным входом емкостного усилителя OTA2. Второй конец хранилищ Cfb2a, Cfb2b заряда соединяется с выводом VCM синфазного режима через переключатели S8a, S8b, управляемые сигналом φ3 переключения, и с дифференциальными выходными выводами буферного каскада BUF через переключатели S9a, S9b, управляемые сигналами φ3DDn переключения. Вход и выход усилителя OTA2 соединяются посредством соответствующих переключателей S10a, S10b, управляемых по сигналам φ3D переключения. Дифференциальное буферизованное выходное напряжение Vout_buf+, Vout_buf- предоставляется на дифференциальном выходе усилителя OTA2.

Фиг. 13 показывает примерную диаграмму управляющих сигналов, которые могут применяться к нейронному усилителю согласно фиг. 12. Что касается функции переключающих сигналов φchop, φ1, φ1D, φ2, φ2D и sel, ссылка выполняется на соответствующие объяснения в соединении с фиг. 7 и фиг. 11. Относительно переключающих сигналов φ3, φ3D и φ3DDn следует отметить, что φ3D является слегка задержанной версией φ3D, а φ3DDn является дополнительно задержанной версией φ3, который также сводится к нулю. Вместе они принадлежат к фазе компенсации буферного смещения, которая будет объяснена более подробно ниже в соединении с фиг. 14A-14D.

Аналогично, переключающие сигналы φ4xn, φ4D и φ4DD соответствуют фазе для переноса заряда в буфер и выборки смещения, которая также будет объяснена более подробно ниже.

Следовательно, как может быть видно на фиг. 13, фазы φ1 и φ2, в целом, соответствуют фазе выборки и суммирования, в то время как переключающие сигналы с индексом 3 и 4 соответствуют переносу заряда в буфер. Следует дополнительно отметить, что также в примерной диаграмме на фиг. 13 nx было выбрано равным 4 для каждого объяснения без потери общности других значений для nx.

Обращаясь теперь к фиг. 14A-14D, изображаются отдельные фазы, упомянутые ранее. Фазы суммирования делятся на фазу φ1 выборки и фазу φ2 переноса заряда, соответственно. Например, фиг. 14A показывает фактическую электрическую конфигурацию нейронного усилителя согласно фиг. 12 с соответствующими настройками переключателя для φ1. Следовательно, во время φ1 входные напряжения на дифференциальных входах, например, входах нейрона, получаются выборкой на выбранных единичных конденсаторах регулируемых хранилищ заряда или ЦАП соответствующего конденсатора в зависимости от соответствующего цифрового кода регулировки.

Как упомянуто ранее, невыбранные единичные конденсаторы могут быть соединены с выводом VCM синфазного режима, таким образом, осуществляя выборку заряда нулевого сигнала, но все еще привнося инжекцию заряда и заряд смещения первого интегрирующего усилителя OTA1. Это может делать суммарное входное смещение независимым от каких-либо весов, соответственно кодов регулировки. Таким образом, оно нейтрализуется посредством прерывания. Когда переключающая пара S2a, S2b возбуждается посредством отложенного тактового сигнала φ1D, она не вносит вклад в смещение инжекции заряда. Кроме того, первый блок ch1 прерывания не вносит вклад, поскольку он переключается в течение неперекрывающегося времени φ1 и φ2, так что заряды могут не переноситься из процесса переключения в блоке ch1 прерывания. Относительно второго блока ch2 прерывания может быть вклад в инжекцию заряда, поскольку заряд остается захваченным на внутренних узлах n1a, n1b, с которыми второй блок ch2 прерывания соединяется. Однако, этот блок ch2 прерывания переключается лишь однажды во время всех фаз суммирования, делая свой вклад небольшим и ничтожным.

Обращаясь теперь к фиг. 14B, показана конфигурация переключения во время фазы φ2 переноса заряда нейронного усилителя на фиг. 12. Соответственно, во время φ2 осуществляющие выборку конденсаторы Csia, Csib разряжаются, и их заряд переносится в интегрирующие хранилища Cfb1a, Cfb1b заряда. Кроме того, заряд Qoff, относящийся к входному смещению интегрирующего усилителя OTA1, переносится следующим образом

Поскольку невыбранные единичные конденсаторы выборки регулируемого хранилища заряда не поддерживаются плавающими, а соединенными с выводом VCM синфазного режима, суммарная емкость выборки, увиденная во время фазы φ2 переноса заряда, является постоянной, и, таким образом, Qoff эффективно нейтрализуется посредством прерывания. Кроме того, переключатели S4a, S4b добавляют инжекцию заряда, которая нейтрализуется также посредством прерывания. Переключатели S3a, S3b не вносят вклад в инжекцию заряда вследствие задержанного переключающего сигнала φ2D.

Обращаясь теперь к фиг. 14C, электрическая конфигурация нейронного усилителя на фиг. 12 показана во время фазы φ3 компенсации смещения буфера. В частности, во время этой фазы φ3, дифференциальный емкостной усилитель OTA2 с хранилищами Cfb2a, Cfb2b заряда сбрасывается. Посредством дополнительного конфигурирования интегрирующего усилителя OTA1 по жесткой обратной связи он предварительно заряжается до напряжения смещения входной стороны буферного каскада BUF для того, чтобы нейтрализовать его в емкостном усилителе OTA2, соответственно, его выходной сигнал, после фазы φ3. Поскольку переключатели S7a, S7b являются разомкнутыми во время этой фазы φ3, инжекция заряда от переключателей S8a, S8b, S9a, S9b, S10a, S10b, главным образом, привлекаются к выходу с более низким импедансом усилителя OTA2, делая остаточную инжекцию заряда небольшой. Кроме того, такая инжекция заряда добавляется лишь однократно для каждого преобразования, дополнительно уменьшая свой вклад.

Обращаясь теперь к фиг. 14D, показана электрическая конфигурация нейронного усилителя согласно фиг. 12 во время фазы φ4 переноса заряда в буфер и выборки смещения. В частности, во время этой фазы φ4, интегрирующие хранилища Cfb1a, Cfb1b заряда соединяются с входной стороной буферного каскада, соответственно, усилителя OTA2, в то время как интегрирующий усилитель OTA1 конфигурируется по жесткой обратной связи, таким образом, вынуждая заряд в интегрирующих хранилищах Cfb1a, Cfb1b заряда переноситься в хранилища Cfb2a, Cfb2b заряда. Поскольку интегрирующие хранилища Cfb1a, Cfb1b заряда были предварительно заряжены до разницы между первым напряжением смещения в усилителе OTA1 и вторым напряжением смещения усилителя OTA2 во время предыдущей фазы φ4, заряд смещения не переносится в хранилища Cfb2a, Cfb2b заряда.

Однако, может быть некоторая инжекция заряда от переключателей S5a, S5b. Поскольку эти переключатели S5a, S5b всегда остаются при потенциале виртуального заземления, этот заряд не является сигнально зависимым и приводит в результате только к некоторому остаточному смещению, если таковое имеется. Кроме того, поскольку этот заряд добавляется лишь однократно для каждого преобразования, его влияние будет все же небольшим. Реализация нейронного усилителя по фиг. 12 избегает каких-либо колебаний сигнала на входе обоих усилителей OTA1, OTA2, так что отсутствуют сигнально зависимые зарядовые эффекты, зависящие от соответствующих входных емкостей усилителей OTA1, OTA2, которые привели бы в результате к какой-либо ошибке коэффициента усиления.

Кроме того, отсутствует сигнально-зависимая утечка инжекции заряда на выходе, делающая ошибку коэффициента усиления зависящей исключительно от коэффициента усиления разомкнутого контура усилителей и от согласования конденсаторов Cfb1a, Cfb1b, Cfb2a, Cfb2b и Csia, Csib.

В различных реализациях вклад усилителей, в частности, если реализованы как множество OTA, может быть сделан небольшим с помощью топологии с высоким коэффициентом усиления, как показано, например, на фиг. 15, делая ошибку коэффициента усиления нечувствительной к разновидностям PVT.

Фиг. 15 показывает примерную реализацию операционного усилителя с активной межэлектродной проводимостью с дифференциальным входным каскадом и дифференциальным выходным каскадом, при этом сигнальные выходы подключены между парой PMOS и NMOS каскодных транзисторов, которые возбуждаются посредством соответствующих каскодных смещающих напряжений Vcasp, Vcasn, соответственно, которые могут быть сформированы посредством соответствующей смещающей схемы. Дифференциальное выходное напряжение также используется для схемы CM обратной связи синфазного режима, регулирующей ток в выходных токовых путях.

Как упомянуто ранее, каскад ASB буфера и активации дополнительно реализует функцию активации, которая может быть функцией отсечки. Отсечка может быть осуществлена посредством ограничения питающего напряжения емкостного усилителя OTA2 и/или самого буферного каскада BUF. Однако, отсечка может также быть реализована посредством специализированного отсекающего каскада.

Обращаясь теперь к фиг. 16, показана примерная реализация такого отсекающего каскада ACT, который может быть соединен с буферным каскадом BUF. На фиг. 16, отсечка выполняется посредством сравнения буферных выходных напряжений Vout_buf+, Vout_buf- до предварительно определенного опорного напряжения, в частности, дифференциального напряжения, и мультиплексирования между буферными напряжениями Vout_buf+, Vout_buf- и опорным напряжением, определяющим уровень отсечки. Если выходной сигнал буфера ниже опорного, выходной сигнал буфера используется для возбуждения выхода нейронного усилителя, т.е., для предоставления буферизованного выходного напряжения. Это напряжение может быть использовано для возбуждения других нейронных усилителей или, если применимо, входной пары того же нейронного усилителя, если реализуется рекуррентная нейронная сеть.

Иначе, опорные напряжения Vref+, Vref- будут использоваться в качестве выходных напряжений Vout+, Vout-.

Поскольку функция отсечки должна быть применена как в положительном, так и отрицательном направлении, отсечка выполняется в два этапа, повторно используя тот же компаратор и применяя блок прерывания, управляемый посредством управляющего сигнала φchop_clip. В частности, первая отсечка проверяется в положительном диапазоне посредством сравнения с положительным опорным напряжением Vref+, в то время как, со ссылкой на примерную схему на фиг. 17, φchop_clip равно нулю. Если отсечка обнаруживается, положительное опорное напряжение переключается на выходное Vout+, Vout-, и операция отсечки завершается. Сравнение выполняется посредством компаратора и затем размещается триггерная схема, которая предоставляет возможность синхронизированной работы на основе тактового сигнала clk.

В случае неположительной отсечки, опорное напряжение переворачивается посредством задания управляющего сигнала φchop_clip в 1 для сравнения с отрицательным опорным напряжением с помощью того же компаратора. Если обнаруживается отрицательная отсечка, отрицательное опорное напряжение направляется к выходу, иначе используется буферное выходное напряжение Vout_buf+, Vout_buf-.

Фактическое сравнение выполняется посредством предварительного заряда емкостей перед компаратором с помощью опорных напряжений и затем приложения буферизованных выходных напряжений Vout_buf+, Vout_buf- к дискретному напряжению для того, чтобы обнаруживать то, являются ли они более высокими или более низкими по сравнению с предварительно заряженными напряжениями.

Как упомянуто ранее, альтернативная реализация отсечки должна питать буферный выходной каскад опорным напряжением. Следовательно, буфер по своей природе отсекает выходной сигнал до желаемых уровней. Это может иметь такой эффект, что одинаковые уровни отсечки применяются ко всем нейронным усилителям, если опорные напряжения или все нейронные усилители снабжаются общим регулятором напряжения, например. Это устраняет сдвиг порога отсечки вследствие смещения компаратора. Однако, отсечка на основе питания не может добиваться жесткой отсечки, а вместо этого является мягкой и похожа на логистическую функцию активации.

Что касается различных реализаций нейронного усилителя, описанных выше, малая ошибка коэффициента усиления и смещения может быть достигнута по сравнению с традиционными подходами нейронных усилителей, в частности, для большого числа входов нейрона, применяя, например, технологии схем в полностью дифференциальном нейронном усилителе. Уменьшение ошибок схемы приводит в результате к меньшим проблемам относительно дрейфа. Кроме того, периодическая повторная калибровка не требуется. Конкретные реализации с буферным каскадом с компенсированным смещением, например, описанные в соединении с фиг. 12-14, улучшают применимость нейронного усилителя для нейронных сетей в рекуррентном режиме работы, когда выходные напряжения сообщаются по обратной связи входам тех же самых или других нейронных усилителей.

Множество экземпляров нейронного усилителя, как описано выше, могут быть использованы, чтобы формировать нейронную сеть, как, например, описано в соединении с фиг. 2. Такие нейронные сети могут быть использованы в любой схеме, требующей взвешенного или невзвешенного аналогового суммирования входных напряжений с высокой точностью, в то же время предоставляя возможность параллельного возбуждения, которое, например, может быть использовано в упомянутых аналоговых нейронных сетях. Например, аналоговые нейронные сети являются интересным вариантом для классификации данных датчика с помощью скрытых или едва видимых шаблонов.

Обращаясь теперь к фиг. 18, показан пример устройства датчика, содержащий один или более датчиков AS1, AS2, и аналоговая искусственная нейронная сеть NN с одним или более нейронными усилителями, как описано выше. Например, выходные сигналы одного или более датчиков AS1, AS2 предоставляются на дифференциальные входы нейронных усилителей, указанных кругами на фиг. 2.

Обучение нейронной сети может выполняться в режиме онлайн, т.е., во время работы сети, оффлайн, например, посредством моделирования нейронной сети для того, чтобы определять соответствующие весовые коэффициенты, или даже как сочетание оффлайн-обучения с последующей онлайн-калибровкой, например. Другие реализации не исключаются этими примерами.

Настоящее раскрытие относится к нейронному усилителю с дифференциальным коммутируемым конденсатором, например, для использования в аналоговой искусственной нейронной сети. Дифференциальный нейронный усилитель с переключаемым конденсатором содержит осуществляющий выборку каскад с множеством дифференциальных входов для приема множества входных напряжений и с по меньшей мере одной парой регулируемых цифровым образом хранилищ заряда для выборки множества входных напряжений, суммирующий каскад для суммирования зарядов, обеспечиваемых в результате из полученного выборкой множества входных напряжений, для того, чтобы формировать сигнал суммирования, причем суммирующий каскад подключается ниже по потоку по отношению к осуществляющему выборку каскаду, и каскад буфера и активации, который конфигурируется, чтобы применять функцию активации и формировать буферизованное выходное напряжение на дифференциальном выходе, на основе сигнала суммирования. Технический результат – повышение производительности и гибкости аналоговой нейронной сети. 3 н. и 13 з.п. ф-лы, 14 ил.

1. Нейронный усилитель с дифференциальным переключаемым конденсатором, в частности, для использования в аналоговой искусственной нейронной сети, причем нейронный усилитель содержит

- осуществляющий выборку каскад (SMP) с множеством дифференциальных входов для приема множества дифференциальных входных напряжений и c по меньшей мере одной парой регулируемых цифровым образом хранилищ заряда для выборки множества дифференциальных входных напряжений;

- суммирующий каскад (SM) для суммирования зарядов, обеспечиваемых в результате из полученного выборкой множества дифференциальных входных напряжений, для того, чтобы формировать сигнал суммирования, причем суммирующий каскад (SM) подключается ниже по потоку по отношению к осуществляющему выборку каскаду (SMP) и содержит дифференциальный интегрирующий усилитель (OTA1) с парой интегрирующих хранилищ (Cfb1a, Cfb1b) заряда на пути дифференциальной обратной связи интегрирующего усилителя; и

- каскад (ACB) буфера и активации, который сконфигурирован, чтобы применять функцию активации и формировать буферизованное выходное напряжение на дифференциальном выходе, на основе сигнала суммирования.

2. Нейронный усилитель по п. 1, при этом число дифференциальных входов соответствует числу пар регулируемых цифровым образом хранилищ заряда.

3. Нейронный усилитель по п. 1, при этом осуществляющий выборку каскад (SMP) содержит по меньшей мере один мультиплексор (MUX) для выборочного соединения множества дифференциальных входов с по меньшей мере одной парой регулируемых цифровым образом хранилищ заряда.

4. Нейронный усилитель по п. 3, при этом число мультиплексоров соответствует числу пар регулируемых цифровым образом хранилищ заряда.

5. Нейронный усилитель по одному из пп. 3 или 4, дополнительно содержащий

- для каждого из по меньшей мере одного мультиплексора первый дифференциальный блок (ch1) прерывания, подключенный между выходом соответствующего мультиплексора и соединенной парой хранилищ заряда;

- второй дифференциальный блок (ch2) прерывания, соединяющий первый конец пути обратной связи с входной стороной интегрирующего усилителя; и

- третий дифференциальный блок (ch3) прерывания, соединяющий второй конец пути обратной связи с выходной стороной интегрирующего усилителя.

6. Нейронный усилитель по п. 5, при этом дифференциальный интегрирующий усилитель суммирующего каскада (SM) содержит схему переключения для выборочной зарядки пары интегрирующих хранилищ заряда с помощью первого напряжения смещения на входной стороне интегрирующего усилителя и второго напряжения смещения на входной стороне каскада (ACB) буфера и активации, в частности, так, что во время суммирования смещение интегрирующего усилителя на выходной стороне интегрирующего усилителя устраняется, а смещение каскада (ACB) буфера и активации применяется, чтобы компенсировать смещение каскада (ACB) буфера и активации.

7. Нейронный усилитель по п. 5 или 6, при этом каскад (ACB) буфера и активации содержит буферный каскад (BUF) с дифференциальным емкостным усилителем (OTA2) с дополнительной парой хранилищ (Cfb2a, Cfb2b) заряда на дополнительном пути дифференциальной обратной связи емкостного усилителя.

8. Нейронный усилитель по п. 7, при этом функция активации реализуется посредством ограничения питающего напряжения емкостного усилителя и/или буферного каскада.

9. Нейронный усилитель по п. 7, при этом каскад (ACB) буфера и активации дополнительно содержит отсекающий каскад, подключенный выше по потоку или ниже по потоку от буферного каскада (BUF), и при этом функция активации реализуется посредством отсекающего каскада.

10. Нейронный усилитель по п. 9, при этом отсекающий каскад (ACT)

- подключается ниже по потоку от буферного каскада (BUF); и

- конфигурируется,

- чтобы сравнивать дифференциальное напряжение на выходе буферного каскада с дифференциальным опорным напряжением;

- выводить дифференциальное опорное напряжение на дифференциальном выходе, если дифференциальное напряжение на выходе буферного каскада превышает дифференциальное опорное напряжение либо в положительном, либо отрицательном направлении; и

- выводить, на дифференциальном выходе, дифференциальное напряжение на выходе буферного каскада в ином случае.

11. Нейронный усилитель по одному из пп. 2-4, при этом дифференциальный интегрирующий усилитель (OTA1) суммирующего каскада (SM) дополнительно содержит пару хранилищ (CCDSa, CCDSb) заряда с двойной выборкой, выборочно подключаемых ниже по потоку от интегрирующего усилителя, при этом нейронный усилитель конфигурируется

- чтобы осуществить выборку нулевого входного сигнала на паре хранилищ (CCDSa, CCDSb) заряда с двойной выборкой во время первой фазы двойной выборки, в частности, посредством установления по меньшей мере одной пары регулируемых цифровым образом хранилищ заряда в нулевое значение; и

- чтобы предоставлять заряды, обеспечиваемые в результате из полученного выборкой нулевого входного сигнала, в каскад (ACB) буфера и активации вместе с зарядами, сохраненными в паре интегрирующих хранилищ (Cfb1a, Cfb1b) заряда.

12. Нейронный усилитель по одному из предшествующих пунктов, при этом каждое регулируемое цифровым образом хранилище заряда из по меньшей мере одной пары регулируемых цифровым образом хранилищ заряда содержит первый и второй зарядный вывод и множество подвергаемых весовой обработке хранилищ заряда, каждое имеет первый конец, соединенный с первым зарядным выводом, и второй конец, выборочно соединенный со вторым зарядным выводом или с выводом синфазного режима, в зависимости от цифрового кода регулировки.

13. Нейронный усилитель по одному из предшествующих пунктов, дополнительно содержащий схему управления для управления функцией переключаемого конденсатора нейронного усилителя и/или для регулирования по меньшей мере одной пары регулируемых цифровым образом хранилищ заряда.

14. Нейронный усилитель по одному из предшествующих пунктов, при этом суммирующий каскад формирует сигнал суммирования в аналоговой области как аналоговый сигнал суммирования.

15. Аналоговая искусственная нейронная сеть, в частности рекуррентная нейронная сеть, содержащая множество нейронных усилителей по одному из предшествующих пунктов, при этом дифференциальный выход по меньшей мере одного из нейронных усилителей соединяется с одним из дифференциальных входов того же самого или другого нейронного усилителя из нейронных усилителей.

16. Устройство датчика, содержащее один или более датчиков и аналоговую искусственную нейронную сеть по предшествующему пункту, при этом выходные сигналы одного или более датчиков предоставляются по меньшей мере одному из нейронных усилителей.

| WO 9531043 A2, 16.11.1995 | |||

| US 10389375 B1, 20.08.2019 | |||

| EP 3300251 A1, 28.03.2018 | |||

| US 2012229204 A1, 13.09.2012. |

Авторы

Даты

2023-06-08—Публикация

2020-11-16—Подача