Область техники

Настоящее изобретение относится к схеме компаратора, которая сравнивает два входных напряжения и устройство отображения, снабженное схемой компаратора.

Уровень техники

В качестве одного способа уменьшения размера и снижения энергопотребления жидкокристаллического устройства отображения известен способ объединенного формирования пиксельных схем и схемы возбуждения для пиксельных схем на одной и той же подложке. При использовании этого способа схема возбуждения образуется тонкопленочными транзисторами (далее именуемыми TFT), выполненными, например, из низкотемпературного поликремния и CG-кремния (кремния с непрерывной структурой кристаллов).

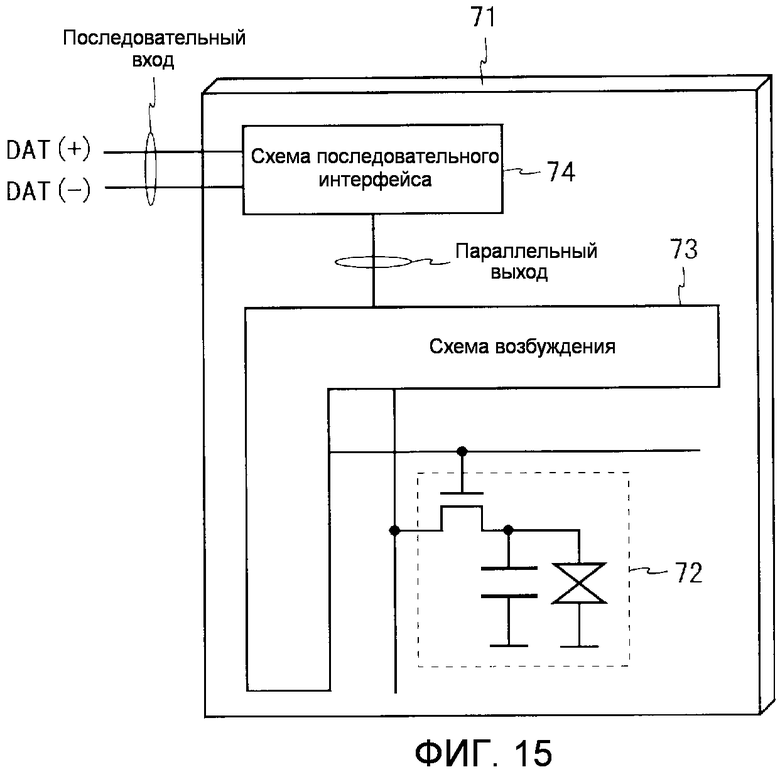

С другой стороны, для повышения надежности жидкокристаллического устройства отображения, предпочтительно сокращать количество сигнальных линий, подключенных к жидкокристаллической панели. Таким образом, известен также способ использования последовательного интерфейса для сигнала, поступающего на жидкокристаллическую панель (см. фиг.15). Жидкокристаллическое устройство отображения, показанное на фиг.15, снабжено жидкокристаллической панелью 71, в которой пиксельная схема 72, схема возбуждения 73 и схема 74 последовательного интерфейса сформированы воедино на стеклянной подложке. Схема 74 последовательного интерфейса преобразует дифференциальные сигналы, поступающие с двух входных контактов DAT(+) и DAT(-), в недифференциальные сигналы осуществляет последовательно-параллельное преобразование и выводит эти сигналы на схему возбуждения 73. Схема возбуждения 73 возбуждает пиксельную схему 72 на основании сигналов, выводимых из схемы 74 последовательного интерфейса. Очевидно, что сигналы, поступающие через последовательный интерфейс, не ограничиваются дифференциальными сигналами и могут быть недифференциальными сигналами.

Например, использование параллельного интерфейса при вводе 6-битовых видеосигналов для RGB в жидкокристаллическую панель требует 18 сигнальных линий для ввода видеосигналов. Напротив, при использовании последовательного интерфейса, для ввода видеосигналов требуется только две (в случае дифференциальных сигналов) или одна (в случае недифференциальных сигналов) сигнальные(ая) линии(я).

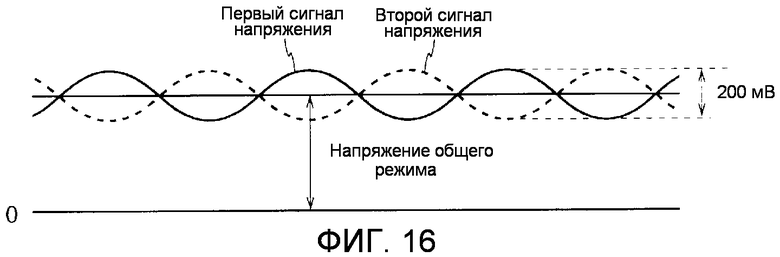

При использовании последовательного интерфейса входной сигнал должен изменяться с более высокой скоростью, чем в случае использования параллельного интерфейса. Однако вследствие задержки в проводных соединениях (RC-задержки), имеющей место в сигнальной линии, подключенной к жидкокристаллической панели, практически невозможно заставить входной сигнал жидкокристаллической панели изменяться с высокой скоростью. Следовательно, при использовании последовательного интерфейса необходимо уменьшать амплитуду напряжения входного сигнала жидкокристаллической панели. Например, дифференциальный сигнал с удвоенной амплитудой 200 мВ, относительно напряжения общего режима Vcm, обычно используется в LVDS (низковольтной дифференциальной сигнализации), как показано на фиг.16, и также необходимо снижать амплитуду напряжения входного сигнала таким образом, когда последовательный интерфейс используется для сигнала, поступающего на жидкокристаллическую панель.

В дальнейшем рассматривается случай, когда дифференциальный сигнал используется для сигнала, поступающего на жидкокристаллическую панель. В этом случае для преобразования входного дифференциального сигнала в недифференциальный сигнал, схема компаратора для сравнения двух напряжений предусмотрена для входного каскада жидкокристаллической панели. Скорость работы схемы компаратора в значительной степени определяется характеристиками (в частности, пороговым напряжением) транзисторов, которые образуют схему компаратора, и напряжением общего режима входного сигнала.

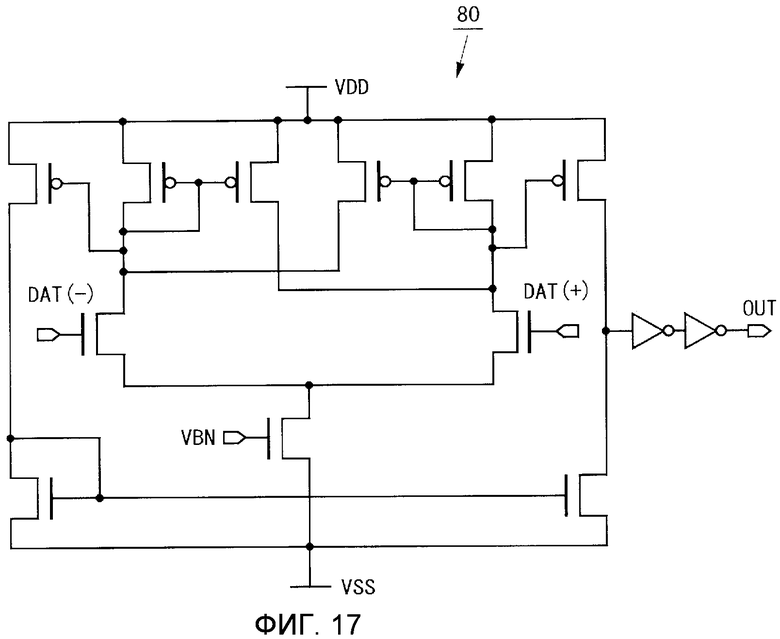

В качестве схемы компаратора, которая преобразует дифференциальный сигнал в недифференциальный сигнал, известна схема компаратора, показанная на фиг.17. Схема компаратора 80, показанная на фиг.17, представляет собой схему на основе схемы дифференциального усилителя, сравнивает два напряжения, поступающие с двух входных контактов DAT(+) и DAT(-), и выводит результат сравнения через выходной контакт OUT с амплитудой напряжения источника питания. Схема компаратора 80 обеспечивает преимущество работы с высокой скоростью благодаря высокому коэффициенту усиления, но имеет проблему в том, что подвержена флуктуации напряжения общего режима входного сигнала (скорость работы легко изменяется при изменении напряжения общего режима).

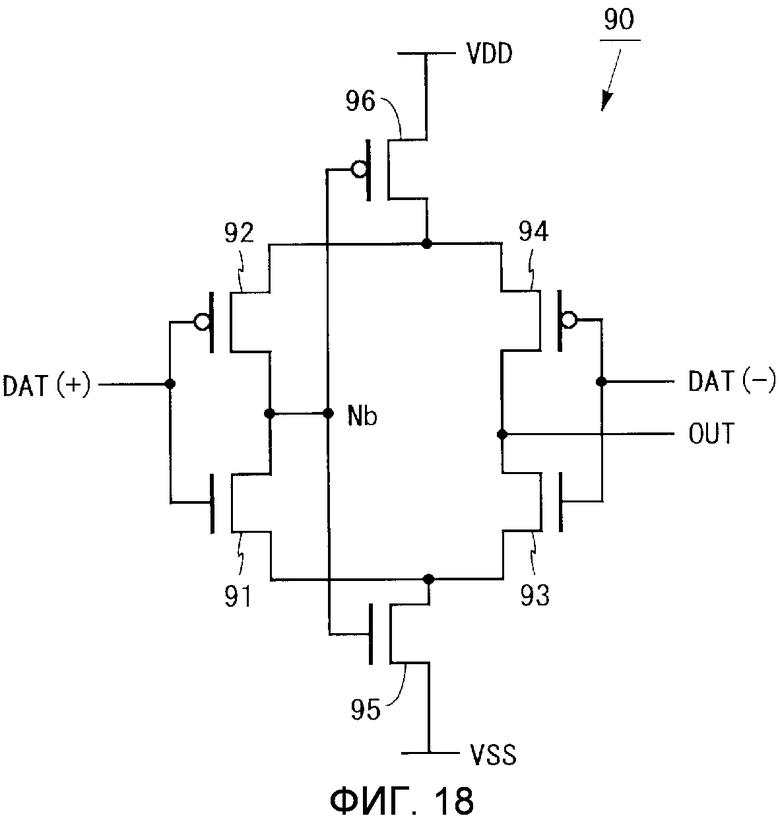

Кроме того, в непатентном документе 1 описана схема компаратора с автоматическим смещением, показанная на фиг.18. Схема компаратора 90, показанная на фиг.18, включает в себя два инвертера между двумя проводами питания, и между двумя проводами питания предусмотрены транзисторы 95 и 96, которые подают напряжение смещения, общее для двух инвертеров.

Согласно схеме компаратора 90, когда напряжение, подаваемое на входной контакт DAT(+), превышает напряжение, подаваемое на входной контакт DAT(-), ток, текущий через транзистор 91, увеличивается, и ток, текущий через транзистор 92, уменьшается. Следовательно, напряжение узла смещения Nb уменьшается. Таким образом, ток, текущий через транзистор 96, увеличивается, что облегчает увеличение напряжения на выходном контакте OUT. Вместе с тем, ток, текущий через транзистор 95, уменьшается, что затрудняет снижение напряжения на выходном контакте OUT. В результате напряжение на выходном контакте OUT увеличивается.

С другой стороны, когда напряжение на входном контакте DAT(+) становится меньше напряжения на входном контакте DAT(-), ток, текущий через транзистор 91, уменьшается, и ток, текущий через транзистор 92, увеличивается. Следовательно, напряжение узла смещения Nb увеличивается. Таким образом, ток, текущий через транзистор 95, увеличивается, что облегчает снижение напряжения на выходном контакте OUT. Вместе с тем, ток, текущий через транзистор 96, уменьшается, что препятствует увеличению напряжения на выходном контакте OUT. В результате напряжение на выходном контакте OUT уменьшается. Таким образом, схема компаратора 90 сравнивает два входных напряжения.

Методы, относящиеся к настоящему изобретению, также описаны в нижеперечисленных документах. В патентном документе 1 описан пример схемы преобразования уровня сигнала, предусмотренной для входного каскада жидкокристаллической панели. В патентном документе 2 описан пример TFT, имеющего два затворных контакта (в двухзатворного TFT).

[Патентный документ 1] Выложенная патентная заявка Японии № 2001-85988.

[Патентный документ 2] Выложенная патентная заявка Японии № 2007-157986.

[Непатентный документ 1] M. Bazes "Two Novel Fully Complementary Self-Biased CMOS Differential Amplifiers", IEEE Journal of Solid-State Circuits, т. 26, № 2, стр. 165-168, февраль 1991.

Сущность изобретения

Задачи изобретения

Вышеописанная схема компаратора 90 обеспечивает преимущество сравнительной невосприимчивости к изменению пороговых напряжений транзисторов, а также невосприимчивости к флуктуациям напряжения общего режима входных сигналов. Однако схема компаратора 90 имеет асимметричную структуру, и напряжение смещения изменяется в зависимости только от выходной характеристики одного из транзисторов (инвертера, образованного транзисторами 91 и 92). Следовательно, схема компаратора 90 не способна следовать изменению пороговых напряжений транзисторов 93 и 94, которые образуют другой инвертер. Проблема также состоит в том, что рабочий диапазон ограничен пороговыми напряжениями транзисторов 95 и 96, которые выдают напряжение смещения. Кроме того, проблема также состоит в том, что, поскольку транзисторы 95 и 96 обеспечены между проводами питания и инвертерами, скорость работы снижается вследствие паразитного сопротивления и паразитной емкости транзисторов 95 и 96. При использовании схемы компаратора с пониженной скоростью работы трудно вводить сигналы в жидкокристаллическую панель с использованием последовательного интерфейса.

Таким образом, задачей настоящего изобретения является обеспечение схемы компаратора, которая невосприимчива к изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима входного сигнала и способна работать с высокой скоростью, а также устройства отображения, снабженного такой схемой компаратора.

РЕШЕНИЕ ЗАДАЧ

Согласно первому аспекту настоящего изобретения, предусмотрена схема компаратора, способная сравнивать два входных напряжения, схема включает в себя: первый инвертер, на который поступает первое входное напряжение, причем первый инвертер имеет структуру, в которой транзистор P-типа и транзистор N-типа соединены последовательно между двумя проводами питания; и второй инвертер, на который поступает второе входное напряжение, причем второй инвертер имеет структуру, идентичную структуре первого инвертера, причем, по меньшей мере, один из первого и второго инвертеров образован двухзатворными транзисторами, каждый из которых имеет два затворных контакта, и на один из затворных контактов каждого двухзатворного транзистора подается входное напряжение, и другой из затворных контактов подключен к выходу другого инвертера.

Согласно второму аспекту настоящего изобретения, в первом аспекте настоящего изобретения, каждый из первого и второго инвертеров образован двухзатворными транзисторами, причем на один из затворных контактов каждого двухзатворного транзистора, который образует первый инвертер, поступает первое входное напряжение, и другой из затворных контактов подключен к выходу второго инвертера, и на один из затворных контактов каждого двухзатворного транзистора, который образует второй инвертер, поступает второе входное напряжение, и другой из затворных контактов подключен к выходу первого инвертера.

Согласно третьему аспекту настоящего изобретения, в первом аспекте настоящего изобретения, каждый из первого и второго инвертеров образован двухзатворными транзисторами, причем на оба затворных контакта каждого двухзатворного транзистора, который образует первый инвертер, поступает первое входное напряжение, и на один из затворных контактов каждого двухзатворного транзистора, который образует второй инвертер, поступает второе входное напряжение, и другой из затворных контактов подключен к выходу первого инвертера.

Согласно четвертому аспекту настоящего изобретения, в первом аспекте настоящего изобретения, только второй инвертер из первого и второго инвертеров образован двухзатворными транзисторами, и на один из затворных контактов каждого двухзатворного транзистора, который образует второй инвертер, поступает второе входное напряжение, и другой из затворных контактов подключен к выходу первого инвертера.

Согласно пятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения, каждый из первого и второго инвертеров образован тонкопленочными транзисторами.

Согласно шестому аспекту настоящего изобретения, в пятом аспекте настоящего изобретения, каждый из первого и второго инвертеров образован с использованием тонкопленочных транзисторов на подложке, на которой располагается пиксельная схема.

Согласно седьмому аспекту настоящего изобретения, предусмотрено устройство отображения, сформированное на подложке, устройство включает в себя: совокупность пиксельных схем; схему возбуждения для пиксельных схем; и схему интерфейса, которая преобразует вводимый извне дифференциальный сигнал в недифференциальный сигнал и выводит недифференциальный сигнал на схему возбуждения, причем схема интерфейса включает в себя схему компаратора согласно любому из аспектов настоящего изобретения с первого по шестой, и осуществляет преобразование дифференциального сигнала с использованием схемы компаратора.

Преимущества изобретения

Согласно первому аспекту настоящего изобретения, можно сформировать схему компаратора, которая невосприимчива к изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима входного сигнала, с использованием двух инвертеров, подключенных друг к другу. Кроме того, сформировав, по меньшей мере, одного из двух инвертеров посредством двухзатворных транзисторов и соединив один из затворных контактов каждого двухзатворного транзистора с выходом другого инвертера, можно управлять пороговым напряжением инвертера, образованного двухзатворными транзисторами, на основании выходного сигнала другого инвертера для облегчения операции переключения инвертера, что позволяет схеме компаратора работать с высокой скоростью.

Согласно второму аспекту настоящего изобретения, сформировав первый и второй инвертеры посредством двухзатворных транзисторов и соединив один из затворных контактов каждого двухзатворного транзистора, который образует первый инвертер, с выходом второго инвертера, и соединив один из затворных контактов каждого двухзатворного транзистора, который образует второй инвертер, с выходом первого инвертера, можно управлять пороговыми напряжениями первого и второго инвертеров на основании выходного сигнала другого инвертера для облегчения операций переключения обоих инвертеров, что позволяет схеме компаратора работать с высокой скоростью.

Согласно третьему аспекту настоящего изобретения, сформировав первый и второй инвертеры посредством двухзатворных транзисторов, и подавая первое входное напряжение на два из затворных контактов каждого двухзатворного транзистора, который образует первый инвертер, и соединив один из затворных контактов каждого двухзатворного транзистора, который образует второй инвертер, с выходом первого инвертера, можно управлять пороговым напряжением первого инвертера на основании выхода первого входного напряжения для облегчения операции переключения первого инвертера, и управлять пороговым напряжением второго инвертера на основании выхода первого инвертера для облегчения операции переключения второго инвертера, что позволяет схеме компаратора работать с высокой скоростью.

Согласно четвертому аспекту настоящего изобретения, сформировав второй инвертер посредством двухзатворных транзисторов и соединив один из затворных контактов каждого двухзатворного транзистора с выходом первого инвертера, можно управлять пороговым напряжением второго инвертера на основании выхода первого инвертера для облегчения операции переключения второго инвертера, что позволяет схеме компаратора работать с высокой скоростью. Кроме того, можно упростить структуру схемы компаратора.

Согласно пятому аспекту настоящего изобретения, даже при использовании тонкопленочных транзисторов, в которых изменение порогового напряжения сравнительно велико, можно сформировать схему компаратора в планарной форме, которая невосприимчива к изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима входного сигнала и способна работать с высокой скоростью.

Согласно шестому аспекту настоящего изобретения, схема компаратора, которая невосприимчива к изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима входного сигнала и способна работать с высокой скоростью, может быть сформирована воедино с пиксельной схемой на подложке с использованием тонкопленочного транзистора, и может использоваться для устройства отображения.

Согласно седьмому аспекту настоящего изобретения, обеспечив схему компаратора, которая невосприимчива к изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима входного сигнала и способна работать с высокой скоростью, для схемы интерфейса, сформированной на подложке, можно сформировать устройство отображения, способное осуществлять сигнал, поступающий на подложку с высокой скоростью с использованием дифференциального сигнала. Кроме того, осуществляя сигнал, поступающий на подложку с использованием последовательного интерфейса, можно сократить количество сигнальных линий, подключенных к подложке, и повысить надежность устройства отображения.

Краткое описание изобретения

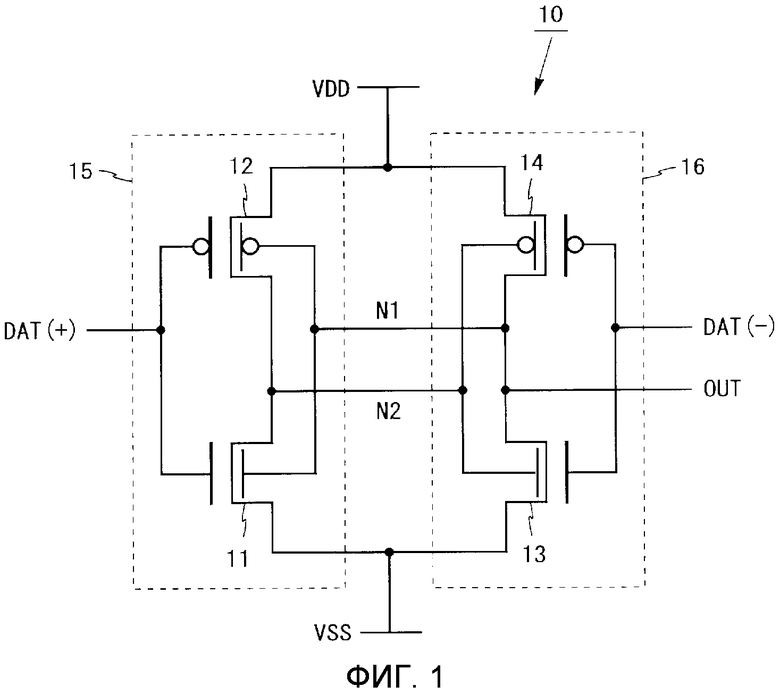

Фиг.1 - принципиальная схема схемы компаратора согласно первому варианту осуществления настоящего изобретения.

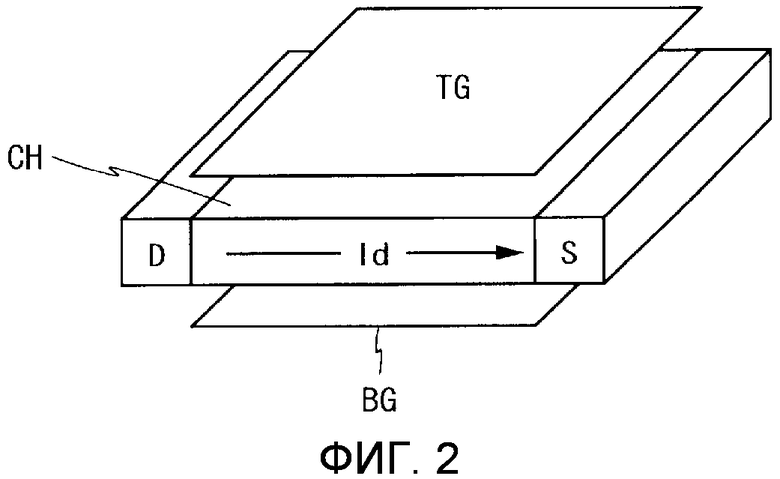

Фиг.2 - схематический вид, иллюстрирующий структуру двухзатворного TFT.

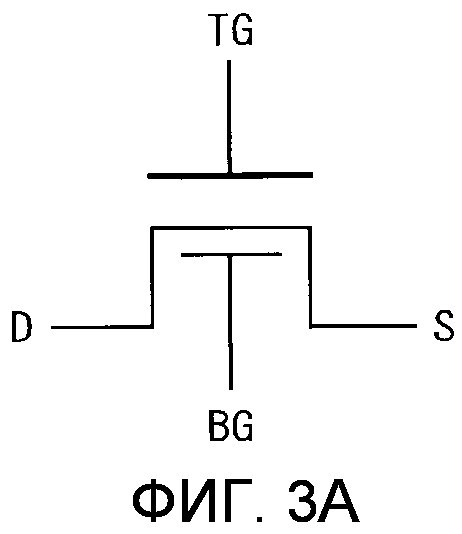

Фиг.3A - схема двухзатворного TFT N-типа, представленная схемным символом.

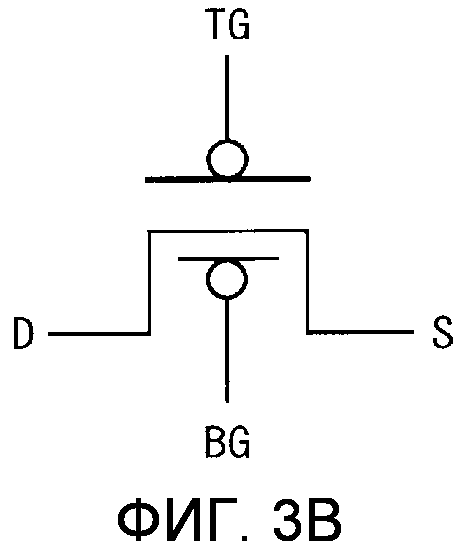

Фиг.3B - схема двухзатворного TFT P-типа, представленного схемным символом.

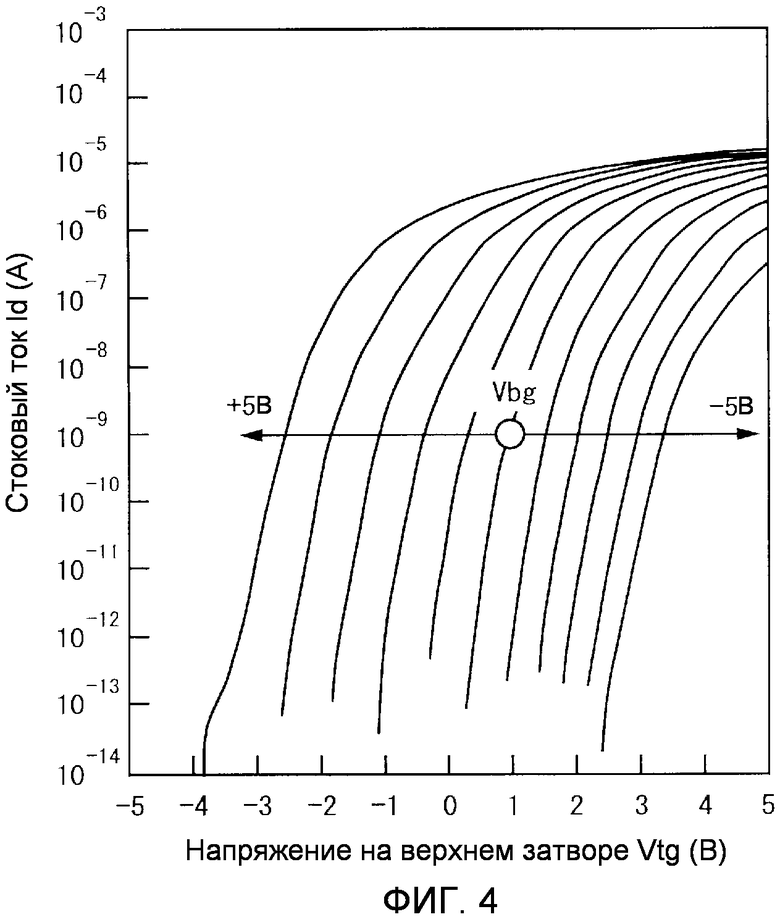

Фиг.4 - диаграмма, иллюстрирующая пример характеристики I-V двухзатворного TFT N-типа.

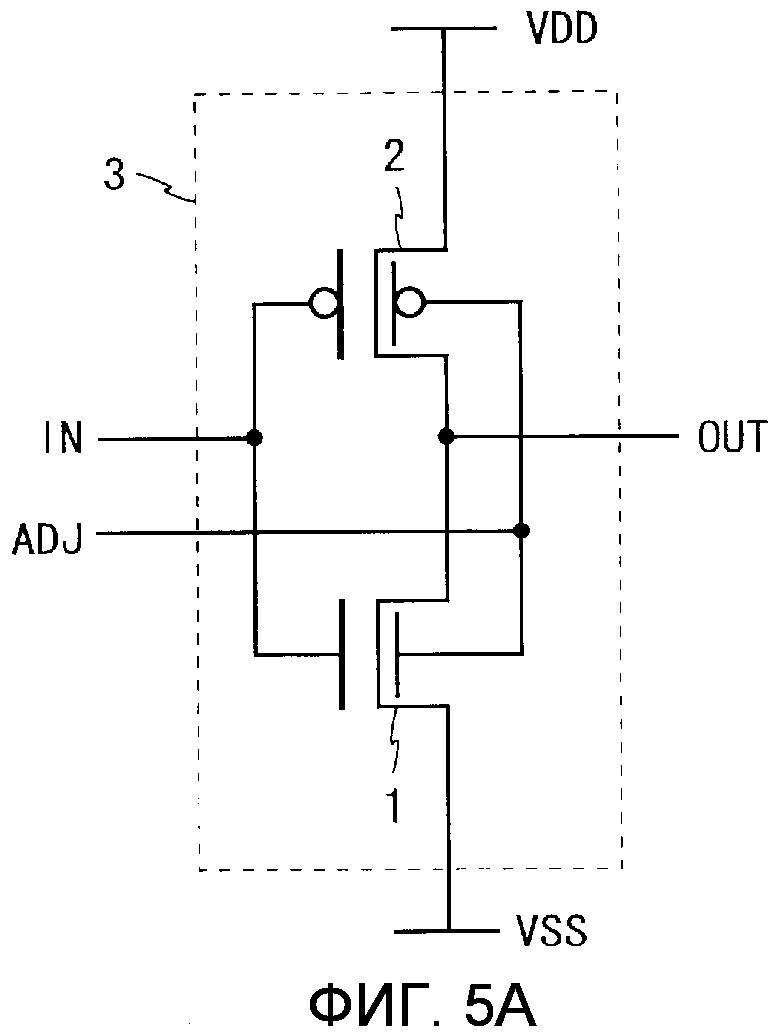

Фиг.5A - принципиальная схема инвертера, образованного двухзатворным TFT.

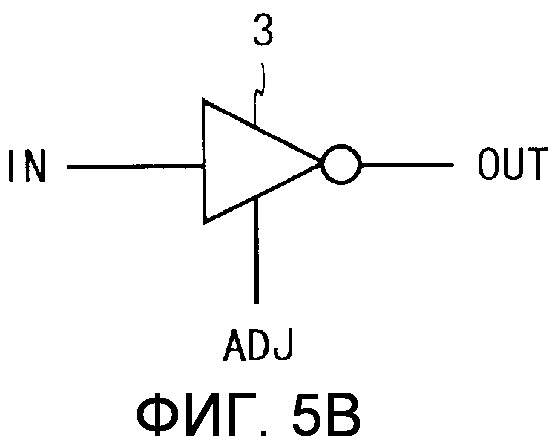

Фиг.5B - схема инвертера, показанного на фиг.5A, представленного схемным символом.

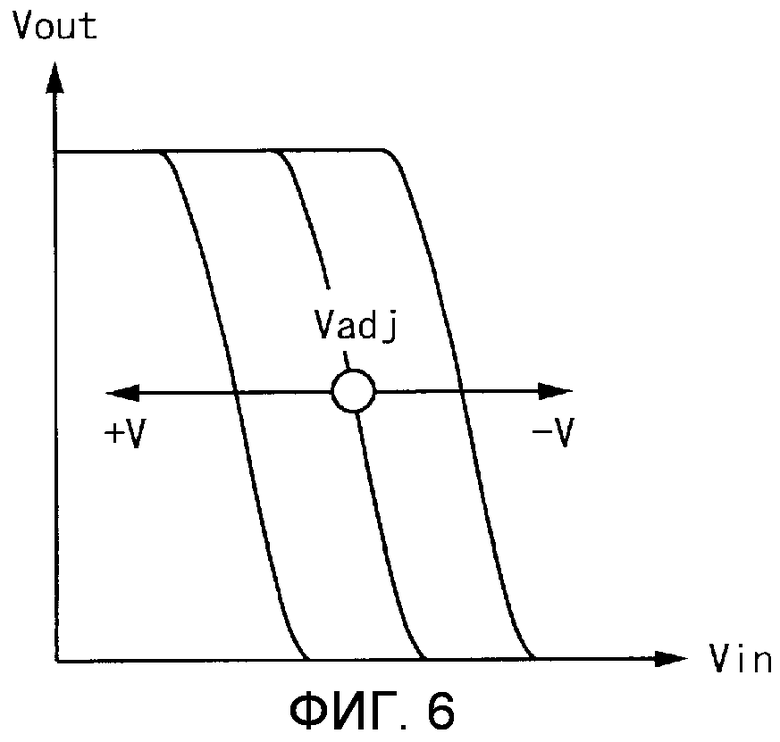

Фиг.6 - диаграмма, иллюстрирующая входные/выходные характеристики инвертера, показанного на фиг.5A.

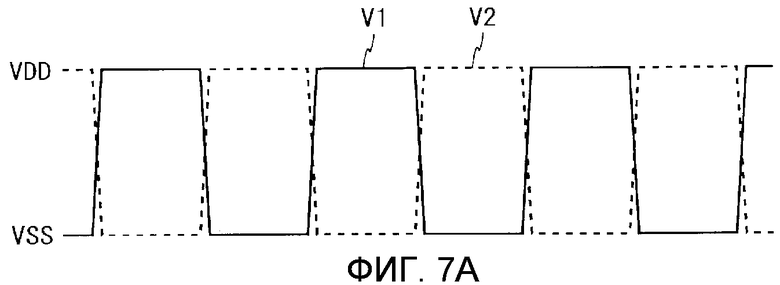

Фиг.7A - диаграмма формы волны сигнала, иллюстрирующая цифровой сигнал, поступающий на схему компаратора, показанную на фиг.1.

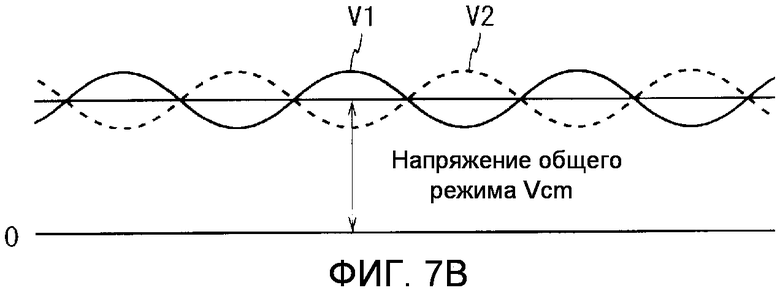

Фиг.7B - диаграмма формы волны сигнала, иллюстрирующая дифференциальный сигнал, поступающий на схему компаратора, показанную на фиг.1.

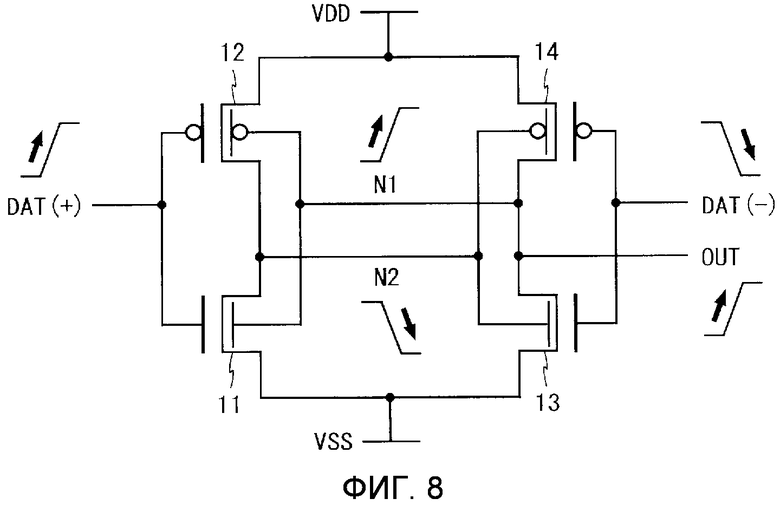

Фиг.8 - схема, демонстрирующая работу схемы компаратора, показанной на фиг.1, при вводе цифрового сигнала.

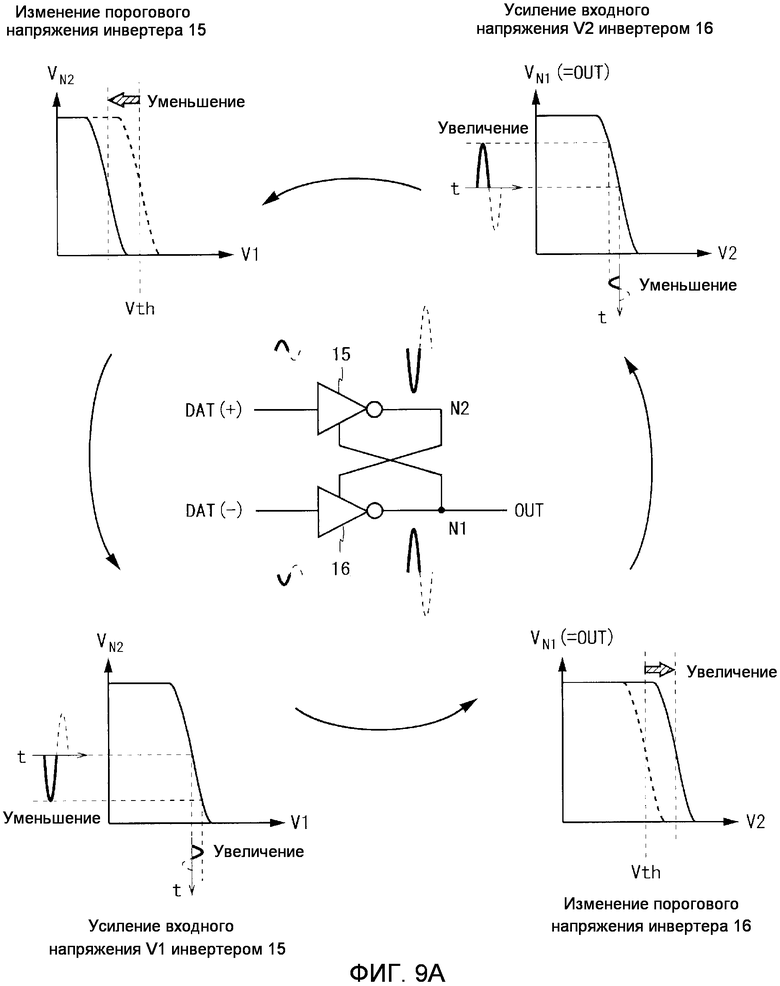

Фиг.9A - схема, демонстрирующая работу схемы компаратора, показанной на фиг.1, при вводе дифференциального сигнала (когда выходное напряжение увеличивается).

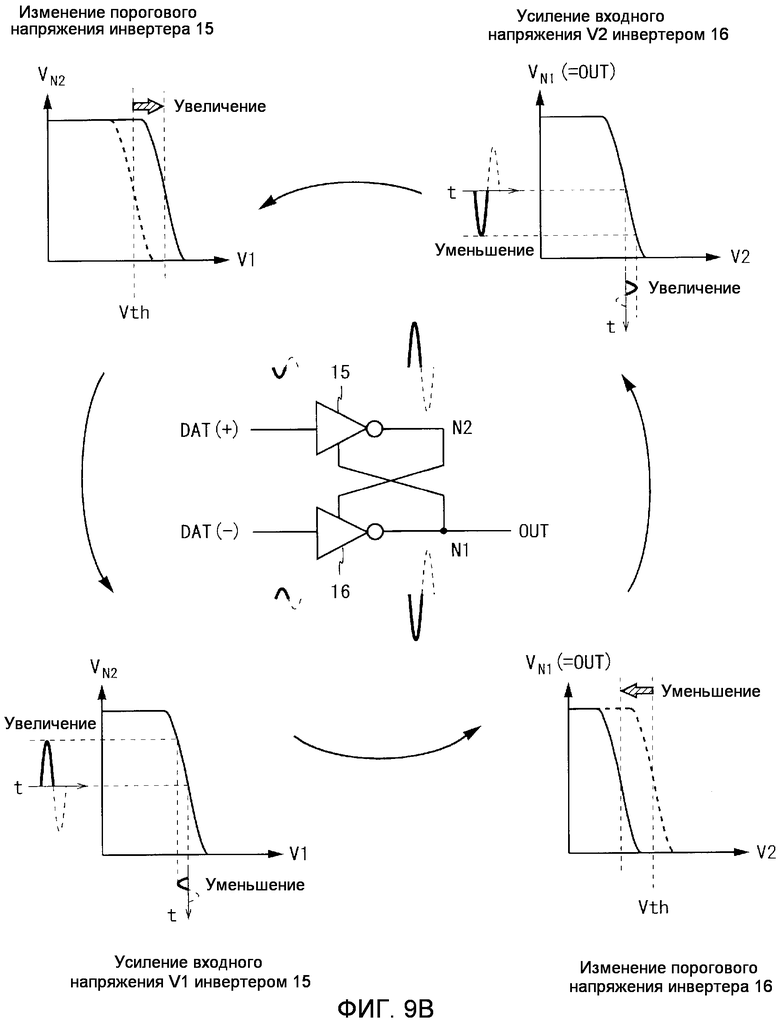

Фиг.9B - схема, демонстрирующая работу схемы компаратора, показанной на фиг.1, при вводе дифференциального сигнала (когда выходное напряжение уменьшается).

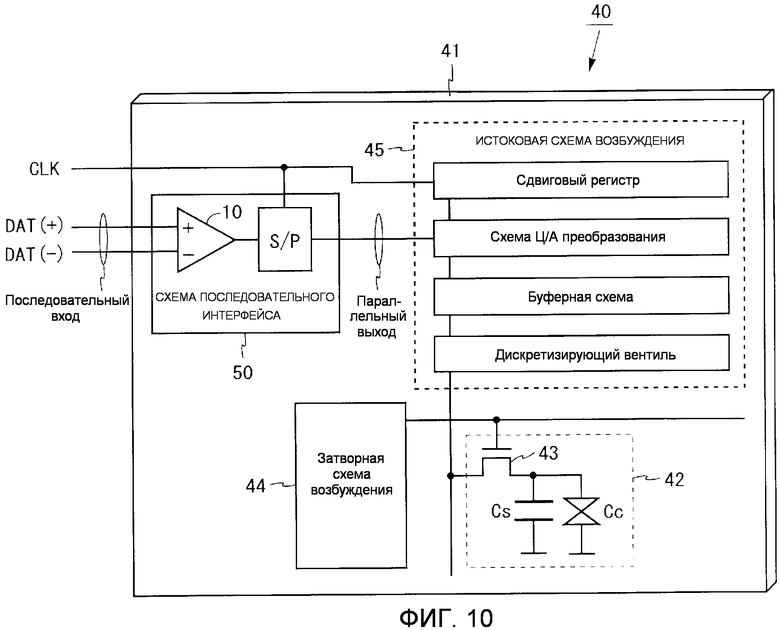

Фиг.10 - блок-схема, демонстрирующая структуру жидкокристаллического устройства отображения, снабженного схемой компаратора, показанной на фиг.1.

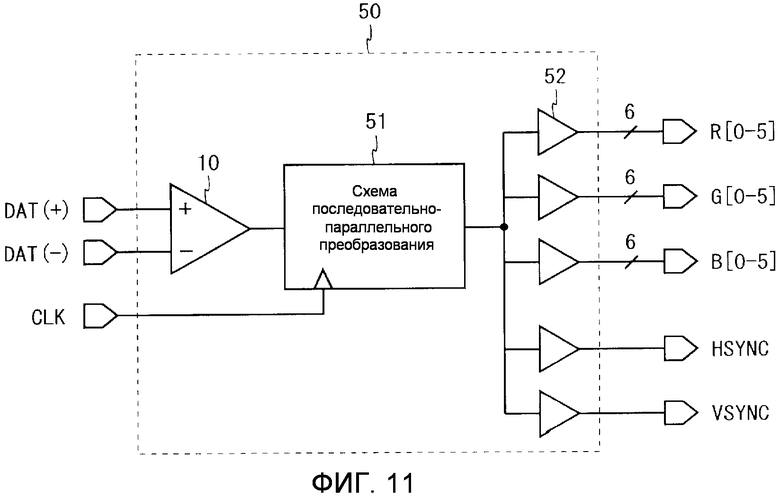

Фиг.11 - схема, демонстрирующая детали схемы последовательного интерфейса, показанной на фиг.10.

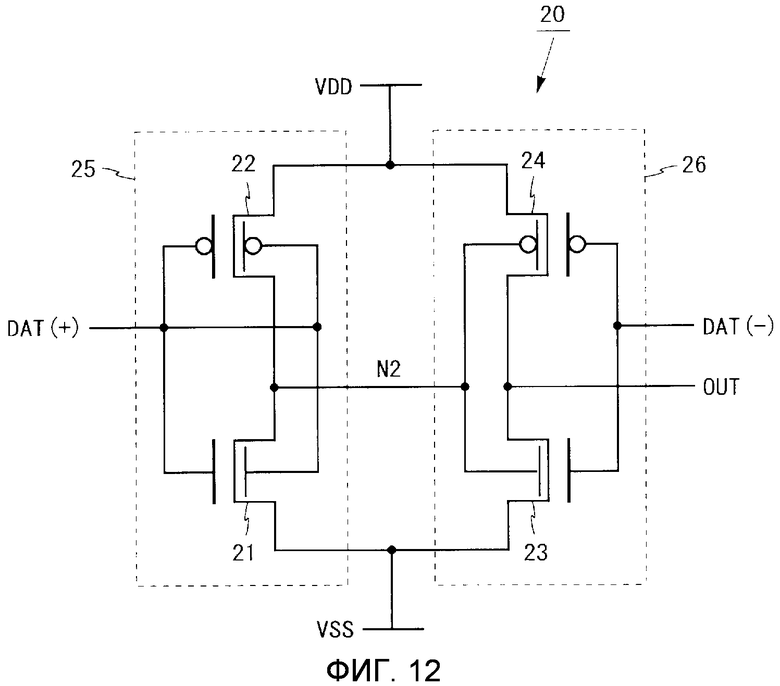

Фиг.12 - принципиальная схема схемы компаратора согласно второму варианту осуществления настоящего изобретения.

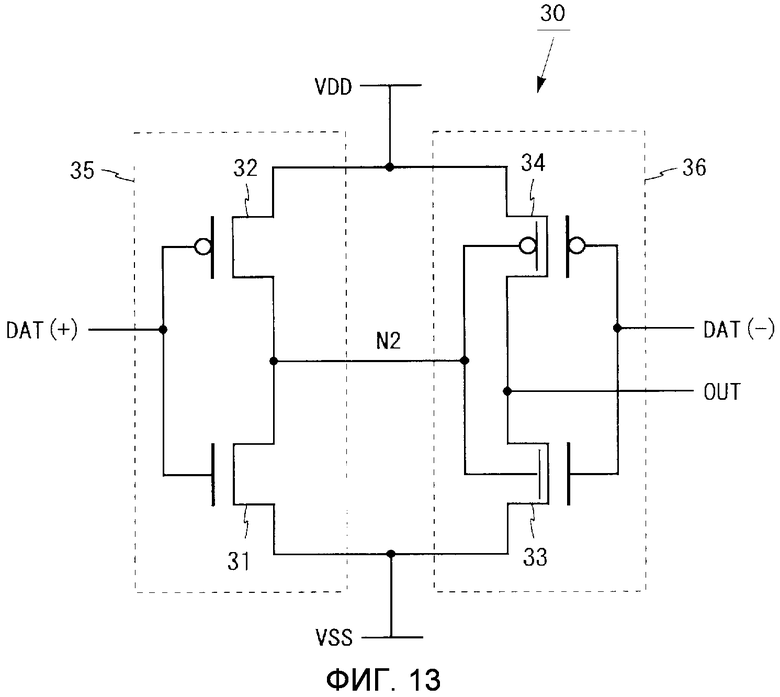

Фиг.13 - принципиальная схема схемы компаратора согласно третьему варианту осуществления настоящего изобретения.

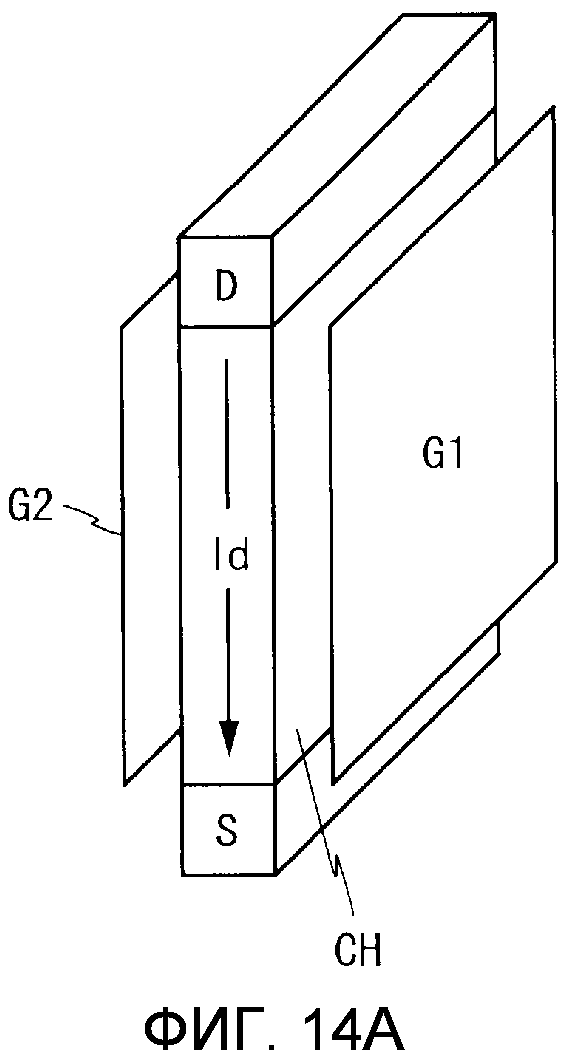

Фиг.14A - схематический вид, иллюстрирующий структуру вертикального двухзатворного ПТ.

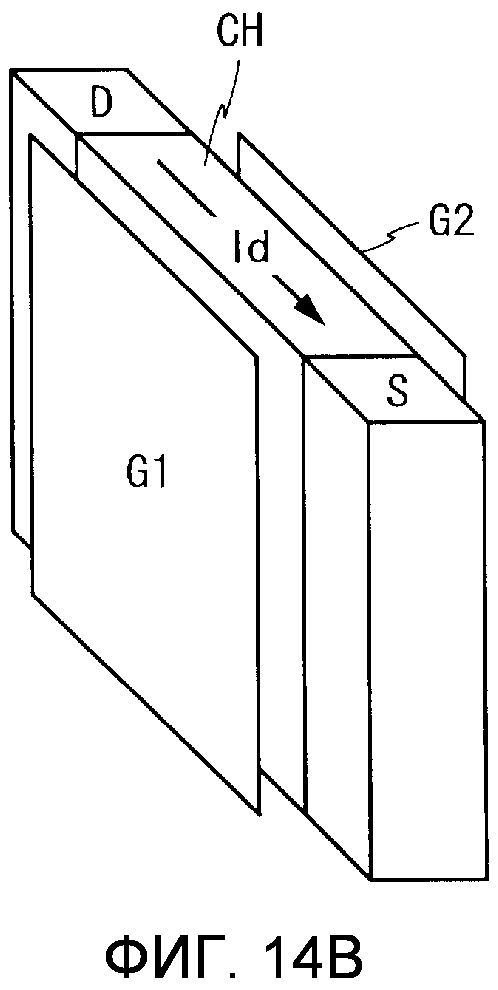

Фиг.14B - схематический вид, иллюстрирующий структуру двухзатворного ПТ плавникового типа.

Фиг.15 - блок-схема, демонстрирующая структуру традиционного жидкокристаллического устройства отображения.

Фиг.16 - диаграмма формы волны сигнала, иллюстрирующая сигнал, используемый в LVDS.

Фиг.17 - принципиальная схема традиционной схемы компаратора (первый пример).

Фиг.18 - принципиальная схема традиционной схемы компаратора (второй пример).

Перечень условных обозначений

1, 2, 11-14, 21-24 и 31-34: TFT

3, 15, 16, 25, 26, 35 и 36: ИНВЕРТЕР

10, 20 и 30: СХЕМА КОМПАРАТОРА

40: ЖИДКОКРИСТАЛЛИЧЕСКОЕ УСТРОЙСТВО ОТОБРАЖЕНИЯ

41: ЖИДКОКРИСТАЛЛИЧЕСКАЯ ПАНЕЛЬ

42: ПИКСЕЛЬНАЯ СХЕМА

43: TFT

44: ЗАТВОРНАЯ СХЕМА ВОЗБУЖДЕНИЯ

45: ИСТОКОВАЯ СХЕМА ВОЗБУЖДЕНИЯ

50: СХЕМА ПОСЛЕДОВАТЕЛЬНОГО ИНТЕРФЕЙСА

Предпочтительные варианты осуществления изобретения

Первый вариант осуществления

На фиг.1 показана принципиальная схема схемы компаратора согласно первому варианту осуществления настоящего изобретения. Схема компаратора 10, показанная на фиг.1, снабжена двумя инвертерами, образованными двухзатворными TFT, и сравнивает два входных напряжения с использованием инвертеров. Схема компаратора 10 обеспечена для входного каскада жидкокристаллической панели, на которой, например, воедино сформированы пиксельные схемы и схемы возбуждения для пиксельных схем. Прежде чем перейти к подробному описанию схемы компаратора 10, опишем двухзатворный TFT и инвертеры, образованные двухзатворными TFT, со ссылкой на фиг.2-6.

Двухзатворный TFT это один тип многозатворного транзистора, отличающийся тем, что имеет два затворных контакта. На фиг.2 показан схематический вид, иллюстрирующий структуру двухзатворного TFT. В двухзатворном TFT истоковый контакт S, стоковый контакт D и участок формирования канала CH между этими контактами расположены в одной плоскости. Верхний затворный контакт TG обеспечен над участком формирования канала CH, и нижний затворный контакт BG обеспечен под участком формирования канала CH. Стоковый ток Id, который соответствует напряжениям, подаваемым на верхний затворный контакт TG и нижний затворный контакт BG, течет между стоковым контактом D и истоковым контактом S. С использованием схемных символов двухзатворный TFT N-типа представлен, как показано на фиг.3A, и двухзатворный TFT P-типа представлен, как показано на фиг.3B. Двухзатворный TFT обычно формируется так, что области инверсионного слоя располагаются сверху и снизу и используются для увеличения возможностей токового возбуждения.

На фиг.4 показана диаграмма, иллюстрирующая пример характеристики I-V двухзатворного TFT N-типа. На фиг.4 показана связь между напряжением на верхнем затворе Vtg и стоковым током Id, когда напряжение между стоком и истоком Vds постоянно и равно заранее определенному значению (здесь, 0.1 В), и напряжение на нижнем затворе Vbg изменяется. Стоковый ток Id, по существу, равен 0, когда напряжение на верхнем затворе Vtg ниже определенного значения (далее именуемого пороговым напряжением Vth), и резко увеличивается, когда напряжение на верхнем затворе Vtg превышает пороговое напряжение Vth. Пороговое напряжение Vth уменьшается с увеличением напряжения на нижнем затворе Vbg и увеличивается с уменьшением напряжения на нижнем затворе Vbg. Таким образом, в двухзатворном TFT N-типа пороговое напряжение Vth транзистора, управляемое с использованием верхнего затворного контакта, можно изменять, управляя напряжением на нижнем затворе Vbg. Это также применимо к двухзатворному TFT P-типа.

В общем случае можно сформировать КМОП-инвертер, последовательно соединив МОП-транзистор (полевой транзистор со структурой металл-оксид-полупроводник) P-типа и МОП-транзистор N-типа, и обеспечив их между двумя проводами питания. Аналогично, можно сформировать инвертер с использованием двухзатворного TFT P-типа и двухзатворного TFT N-типа.

На фиг.5A показана принципиальная схема инвертера, образованного двухзатворным TFT. Инвертер 3, показанный на фиг.5A, снабжен двумя TFT 1 и 2, входным контактом IN, выходным контактом OUT и регулировочным контактом ADJ. TFT 1 является двухзатворным TFT N-типа, и TFT 2 является двухзатворным TFT P-типа. Истоковый контакт TFT 1 подключен к проводу питания, на который подается низкое напряжение VSS, и истоковый контакт TFT 2 подключен к проводу питания, на который подается высокое напряжение VDD. Верхние затворные контакты TFT 1 и 2 подключены к входному контакту IN, стоковые контакты - к выходному контакту OUT, и задние затворные контакты - к регулировочному контакту ADJ соответственно. Инвертер 3 представлен, как показано на фиг.5B с использованием схемного символа.

На фиг.6 показана диаграмма, иллюстрирующая входные/выходные характеристики инвертера 3. На фиг.6 показана связь между входным напряжением Vin и выходным напряжением Vout при изменении регулировочного напряжения Vadj. Согласно фиг.6, выходное напряжение Vout находится на заранее определенном уровне, который выше 0, когда входное напряжение Vin ниже порогового напряжения Vth, и, по существу, равен 0, когда входное напряжение Vin превышает пороговое напряжение Vth. Пороговое напряжение Vth уменьшается с увеличением регулировочного напряжения Vadj и увеличивается с уменьшением регулировочного напряжения Vadj. Согласно инвертеру 3, можно изменять точку переключения (граничное напряжение между состоянием включения и состоянием выключения), управляя напряжениями на нижних затворах TFT 1 и 2.

Ниже подробно описана схема компаратора 10 со ссылкой на фиг.1. Схема компаратора 10, показанная на фиг.1, снабжена четырьмя TFT 11-14, двумя входными контактами DAT(+) и DAT(-) и выходным контактом OUT. TFT 11 и 13 являются двухзатворными TFT N-типа, и TFT 12 и 14 являются двухзатворными TFT P-типа. Истоковые контакты TFT 11 и 13 подключены к проводу питания, на который подается низкое напряжение VSS, и истоковые контакты TFT 12 и 14 подключены к проводу питания, на который подается высокое напряжение VDD. Стоковые контакты TFT 11 и 12 подключены друг к другу, и стоковые контакты TFT 13 и 14 подключены к выходному контакту OUT. Верхние затворные контакты TFT 11 и 12 подключены к входному контакту DAT(+), и нижние затворные контакты подключены к стоковым контактам TFT 13 и 14 и выходному контакту OUT. Верхние затворные контакты TFT 13 и 14 подключены к входному контакту DAT(-), и нижние затворные контакты подключены к стоковым контактам TFT 11 и 12. В дальнейшем, узел, к которому подключены нижний затворный контакт TFT 11 и т.п., обозначен как N1, и узел, к которому подключены нижний затворный контакт TFT 13 и т.п., обозначен как N2.

В схеме компаратора 10 TFT 11 и 12 образуют инвертер 15, и TFT 13 и 14 образуют инвертер 16. Входной контакт инвертера 15 подключен к входному контакту DAT(+), и выходной контакт подключен к регулировочному контакту инвертера 16. Входной контакт инвертера 16 подключен к входному контакту DAT(-), и выходной контакт подключен к регулировочному контакту инвертера 15 и выходному контакту OUT. Первое входное напряжение V1 подается на входной контакт DAT(+), и второе входное напряжение V2 подается на входной контакт DAT(-). Таким образом, можно сформировать контур отрицательной обратной связи, который облегчает операцию переключения в комплементарном режиме, соединяя инвертеры 15 и 16 друг с другом.

Дифференциальный сигнал вводится в схему компаратора 10 с использованием двух входных контактов DAT(+) и DAT(-). В схему компаратора 10 вводятся, например, пара цифровых сигналов, соответственно изменяющихся в противоположных направлениях (фиг.7A), или, например, дифференциальные сигналы малой амплитуды (фиг.7B). При вводе цифровых сигналов, как показано на фиг.7A, первое входное напряжение V1 становится высоким напряжением VDD или низким напряжением VSS, и второе входное напряжение V2 принимает противоположное напряжение. При вводе дифференциальных сигналов малой амплитуды, как показано на фиг.7B, первое входное напряжение V1 и второе входное напряжение V2 изменяются в противоположных направлениях относительно напряжения общего режима Vcm. Альтернативно, в схему компаратора 10 можно вводить недифференциальный сигнал. При вводе недифференциального сигнала недифференциальный сигнал поступает на один из двух входных контакта DAT(+) и DAT(-), и на другой поступает опорное напряжение для сравнения.

Как описано ниже, схема компаратора 10 выводит, в качестве выходного напряжения VO, высокое напряжение VDD, когда первое входное напряжение V1 больше, чем второе входное напряжение V2 (V1>V2), и низкое напряжение VSS, когда первое входное напряжение V1 меньше, чем второе входное напряжение V2 (V1<V2).

Прежде всего, рассмотрим случай V1>V2 вследствие увеличения первого входного напряжения V1 и снижения второго входного напряжения V2. При увеличении первого входного напряжения V1 TFT 11 переходит в состояние включения, и TFT 12 переходит в состояние выключения, и напряжение на узле N2 (выходное напряжение инвертера 15) уменьшается. Поскольку узел N2 подключен к регулировочному контакту инвертера 16, пороговое напряжение инвертера 16 увеличивается при уменьшении напряжения на узле N2. Следовательно, выходное напряжение инвертера 16 также увеличивается. Вместе с тем, при уменьшении второго входного напряжения V2 TFT 13 переходит в состояние выключения, и TFT 14 переходит в состояние включения, и напряжение на узле N1 (выходное напряжение инвертера 16) увеличивается. Поскольку узел N1 подключен к регулировочному контакту инвертера 15, пороговое напряжение инвертера 15 уменьшается при увеличении напряжения на узле N1. Следовательно, выходное напряжение инвертера 15 также уменьшается. Уменьшение выходного напряжения инвертера 15 облегчает увеличение выходного напряжения инвертера 16, и увеличение выходного напряжения инвертера 16 облегчает уменьшение выходного напряжения инвертера 15. Таким образом, выходное напряжение VO меняется на высокое напряжение VDD за короткий период времени.

Теперь рассмотрим случай V1<V2 вследствие снижения первого входного напряжения V1 и увеличения второго входного напряжения V2. При уменьшении первого входного напряжения V1, TFT 11 переходит в состояние выключения, и TFT 12 переходит в состояние включения, и напряжение на узле N2 увеличивается. Следовательно, пороговое напряжение инвертера 16 уменьшается, и выходное напряжение инвертера 16 также уменьшается. Вместе с тем, при увеличении второго входного напряжения V2, TFT 13 переходит в состояние включения, и TFT 14 переходит в состояние выключения, и напряжение на узле N1 уменьшается. Следовательно, пороговое напряжение инвертера 15 увеличивается, и выходное напряжение инвертера 15 также увеличивается. Увеличение выходного напряжения инвертера 15 облегчает уменьшение выходного напряжения инвертера 16, и уменьшение выходного напряжения инвертера 16 облегчает увеличение выходного напряжения инвертера 15. Таким образом, выходное напряжение VO меняется на низкое напряжение VSS за короткий период времени. Таким образом, как в случае V1>V2, так и в случае V1<V2, выходное напряжение VO достигает окончательного значения за короткий период времени.

Рассмотрим в порядке примера случай, когда первое входное напряжение V1 меняется на высокое напряжение VDD, и второе входное напряжение V2 меняется на низкое напряжение VSS при вводе цифровых сигналов в схему компаратора 10 (фиг.7A). В этом случае, как показано на фиг.8, напряжение на узле N1 меняется на высокое напряжение VDD, и напряжение на узле N2 меняется на низкое напряжение VSS. Увеличение напряжения на узле N1 приводит к снижению порогового напряжения Vth инвертера 16 и облегчает уменьшение выходного напряжения инвертера 16. Кроме того, уменьшение напряжения на узле N2 приводит к увеличению порогового напряжения Vth инвертера 15 и облегчает увеличение выходного напряжения инвертера 15. Таким образом, выходное напряжение VO достигает высокого напряжения VDD за короткий период времени. Также в случае, когда первое входное напряжение V1 меняется на низкое напряжение VSS, и второе входное напряжение V2 меняется на высокое напряжение VDD, аналогично, выходное напряжение VO достигает низкого напряжения VSS за короткий период времени.

Кроме того, при вводе дифференциальных сигналов малой амплитуды (фиг.7B) схема компаратора 10 работает, как показано на фиг.9A и 9B. Когда выходное напряжение VO увеличивается, схема компаратора 10 работает, как показано на фиг.9A. При увеличении первого входного напряжения V1 напряжение на узле N2 уменьшается в значительной степени благодаря усилительному действию инвертера 15 (слева внизу на фиг.9A). В результате пороговое напряжение Vth инвертера 16 увеличивается (справа внизу на фиг.9A), и выходное напряжение инвертера 16 легко увеличивается. Кроме того, при уменьшении второго входного напряжения V2 напряжение на узле N1 увеличивается в значительной степени благодаря усилительному действию инвертера 16 (справа вверху на фиг.9A). В результате пороговое напряжение Vth инвертера 15 уменьшается (слева вверху на фиг.9A), и выходное напряжение инвертера 15 легко уменьшается.

Когда выходное напряжение VO уменьшается, схема компаратора 10 работает, как показано на фиг.9B. При уменьшении первого входного напряжения V1 напряжение на узле N2 увеличивается в значительной степени благодаря усилительному действию инвертера (слева внизу на фиг.9B). В результате пороговое напряжение Vth инвертера 16 уменьшается (справа внизу на фиг.9B), и выходное напряжение инвертера 16 легко уменьшается. Кроме того, при увеличении второго входного напряжения V2, напряжение на узле N1 уменьшается в значительной степени благодаря усилительному действию инвертера 16 (справа вверху на фиг.9B). В результате пороговое напряжение Vth инвертера 15 увеличивается (слева вверху на фиг.9B), и выходное напряжение инвертера 16 легко увеличивается.

Таким образом, первое входное напряжение V1 усиливается инвертером 15, и сигнал, усиленный инвертером 15, приводит к изменению порогового напряжения Vth инвертера 16 для облегчения операции переключения инвертера 16. Вместе с тем, второе входное напряжение V2 усиливается инвертером 16, и сигнал, усиленный инвертером 16, приводит к изменению порогового напряжения Vth инвертера 15 для облегчения операции переключения инвертера 15. Усиление первого входного напряжения V1, изменение порогового напряжения инвертера 16, усиление второго входного напряжения V2 и изменение порогового напряжения Vth инвертера 15 повторно осуществляются в мгновенном режиме, что, соответственно, облегчает операции переключения инвертеров 15 и 16 на ступени ускорения. Таким образом, напряжение на выходном контакте OUT достигает окончательного значения за короткий период времени.

Как описано выше, схема компаратора 10 эффективно использует обратную связь посредством контура отрицательной обратной связи и последовательно изменяет пороговые напряжения двух инвертеров 15 и 16 в направлении легкого переключения. Рассмотрим в порядке примера случай, когда пороговое напряжение инвертера 16 меньше назначенного значения вследствие изменения процесса. В этом случае инвертер 16 не осуществляет операцию переключения легко, даже если второе входное напряжение V2 уменьшается. Однако, когда первое входное напряжение V1 увеличивается, и выходное напряжение инвертера 15 уменьшается, пороговое напряжение инвертера 16 динамически увеличивается, и инвертер 16 легко осуществляет операцию переключения. Аналогично, в случае, когда пороговое напряжение инвертера 16 больше назначенного значения, операция переключения инвертером 16 облегчается за счет динамического управления характеристикой инвертера 16 с использованием выходного сигнала инвертера 15. Это также применимо к случаю, когда пороговое напряжение инвертера 15 отличается от назначенного значения. Таким образом, поскольку операция переключения облегчается в комплементарном режиме с использованием двух инвертеров 15 и 16, схема компаратора 10 невосприимчива к изменению пороговых напряжений транзисторов.

Кроме того, схема компаратора 10 также невосприимчива к флуктуации напряжения общего режима. Рассмотрим в порядке примера случай, когда напряжение общего режима ниже нормального уровня. В начальном состоянии напряжение на узле N2 (выходное напряжение инвертера 15) не очень сильно снижается, даже если первое входное напряжение V1 увеличивается. Однако, когда второе входное напряжение V2 уменьшается, напряжение на узле N1 (выходное напряжение инвертера 16) увеличивается в достаточной степени. В результате пороговое напряжение инвертера 15 уменьшается, что облегчает операцию переключения инвертера 15. Аналогично, в случае, когда напряжение общего режима выше нормального уровня, когда напряжение на узле N1 уменьшается, пороговое напряжение инвертера 15 увеличивается, что облегчает операцию переключения инвертера 15. Как описано выше, эти изменения повторно осуществляются в мгновенном режиме, что облегчает, соответственно, операции переключения инвертеров 15 и 16 в комплементарном режиме. По вышеописанным причинам схема компаратора 10 также невосприимчива к флуктуации общего режима.

Ниже описано жидкокристаллическое устройство отображения, снабженное схемой компаратора 10 на входном каскаде жидкокристаллической панели в качестве одного варианта применения схемы компаратора 10. На фиг.10 показана блок-схема, демонстрирующая структуру жидкокристаллического устройства отображения, снабженного схемой компаратора 10. Жидкокристаллическое устройство отображения 40, показанное на фиг.10, снабжено жидкокристаллической панелью 41, в которой пиксельная схема 42, затворная схема возбуждения 44, истоковая схема возбуждения 45 и схема 50 последовательного интерфейса сформированы воедино на стеклянной подложке. Схемы на стеклянной подложке образованы TFT, выполненными, например, из низкотемпературного поликремния и CG-кремния.

Жидкокристаллическая панель 41 снабжена совокупностью пиксельных схем 42, каждая из которых включает в себя TFT 43, емкость жидкого кристалла Cc и дополнительную емкость Cs (на фиг.10 показана только одна пиксельная схема). Кроме того, жидкокристаллическая панель 41 снабжена затворной схемой возбуждения 44 и истоковой схемой возбуждения 45 в качестве схем возбуждения пиксельных схем 42. Истоковая схема возбуждения 45 включает в себя сдвиговый регистр, схему Ц/А преобразования, буферную схему и дискретизирующий вентиль.

Согласно жидкокристаллическому устройству отображения 40, последовательный интерфейс используется для сигнала, поступающего на жидкокристаллическую панель 41 для сокращения количества сигнальных линий, подключенных к жидкокристаллической панели 41. Кроме того, дифференциальный сигнал используется для сигнала, поступающего на жидкокристаллическую панель 41. Следовательно, жидкокристаллическая панель 41 снабжена схемой 50 последовательного интерфейса, и схема компаратора 10 предусмотрена для входного каскада жидкокристаллической панели 41.

На фиг.11 показана схема, демонстрирующая детали схемы 50 последовательного интерфейса. Схема 50 последовательного интерфейса, показанная на фиг.11, включает в себя схему компаратора 10, схему 51 последовательно-параллельного преобразования и совокупность буферов 52. Схема компаратора 10 сравнивает напряжение на входном контакте DAT(+) и напряжение на входном контакте DAT(-) и выводит результат сравнения. Схема 51 последовательно-параллельного преобразования осуществляет последовательно-параллельное преобразование в сигналы, последовательно выводимые из схемы компаратора 10, и параллельно выводит совокупность сигналов. Выходные сигналы схемы 51 последовательно-параллельного преобразования выводятся, например, на затворную схему возбуждения 44 и истоковую схему возбуждения 45 через буферы 52.

Схема 50 последовательного интерфейса, показанная на фиг.11, параллельно выводит красный сигнал яркости R, зеленый сигнал яркости G, синий сигнал яркости B (каждый из них имеет размер 6 битов), сигнал горизонтальной синхронизации HSYNC и сигнал вертикальной синхронизации VSYNC (каждый из них имеет размер 1 бит). Очевидно, что схема 50 последовательного интерфейса может выводить другие сигналы помимо вышеперечисленных.

Обеспечив схему компаратора 10, которая невосприимчива к изменению пороговых напряжений транзисторов и к флуктуации напряжения общего режима входного сигнала и способна работать с высокой скоростью, для схемы 50 последовательного интерфейса, сформированной таким образом на жидкокристаллической панели 41, можно сформировать жидкокристаллическое устройство отображения 40, способное вводить сигналы в жидкокристаллическую панель 41 с высокой скоростью с использованием дифференциального сигнала. Кроме того, вводя сигналы в жидкокристаллическую панель 41 с использованием последовательного интерфейса, можно сократить количество сигнальных линий, подключенных к жидкокристаллической панели 41, и повысить надежность жидкокристаллического устройства отображения 40.

Как описано выше, согласно схеме компаратора 10 этого варианта осуществления, инвертеры 15 и 16 образованы двухзатворным TFT, и нижние затворные контакты двухзатворных TFT, которые образуют инвертер 15, подключены к выходу инвертера 16, и нижние затворные контакты двухзатворных TFT, которые образуют инвертер 16, подключены к выходу инвертера 15. Таким образом, можно управлять пороговым напряжением инвертера 15 на основании выходного сигнала инвертера 16 для облегчения операции переключения инвертера 15, и управлять пороговым напряжением инвертера 16 на основании выходного сигнала инвертера 15 для облегчения операции переключения инвертера 16. Таким образом, вне зависимости от пороговых напряжений транзисторов и напряжения общего режима, схема компаратора 10 может стабильно работать с высокой скоростью.

Кроме того, можно сформировать схему компаратора в планарной форме, которая невосприимчива к изменению пороговых напряжений транзисторов и к флуктуации напряжения общего режима входного сигнала и способна работать с высокой скоростью, когда инвертеры 15 и 16, входящие в состав схемы компаратора 10, образованы TFT. В общем случае, изменение характеристики TFT превышает изменение характеристики транзистора с использованием монокристального кремния. Следовательно, преимущество стабильной и высокоскоростной работы схемы компаратора 10 оказывается более выраженным в случае, когда схема компаратора 10 образована TFT. Схему компаратора 10, обеспечивающую такой эффект, можно использовать для жидкокристаллического устройства отображения 40 и т.п., путем объединенного формирования схемы компаратора 10 и пиксельных схем 42 на жидкокристаллической панели 41 с использованием TFT.

Второй вариант осуществления

На фиг.12 показана принципиальная схема схемы компаратора согласно второму варианту осуществления настоящего изобретения. Схема компаратора 20, показанная на фиг.12, снабжена четырьмя TFT 21-24, двумя входными контактами DAT(+) и DAT(-) и выходным контактом OUT. TFT 21 и 23 являются двухзатворными TFT N-типа, и TFT 22 и 24 являются двухзатворными TFT P-типа. Нижние затворные контакты TFT 21 и 22 подключены к верхним затворным контактам TFT 21 и 22 и входному контакту DAT(+). В остальном соединение между компонентами схемы компаратора 20 такое же, как в схеме компаратора 10.

В схеме компаратора 20 TFT 21 и 22 образуют инвертер 25, и TFT 23 и 24 образуют инвертер 26. Входной контакт и регулировочный контакт инвертера 25 подключены к входному контакту DAT(+), и выходной контакт подключен к регулировочному контакту инвертера 26. Входной контакт инвертера 26 подключен к входному контакту DAT(-), и выходной контакт подключен к выходному контакту OUT.

Согласно схеме компаратора 20, нижние затворные контакты TFT 21 и 22 подключены к входному контакту DAT(+), на который подается первое входное напряжение V1, а не выходной сигнал инвертера 26. Выходной сигнал инвертера 26 увеличивается с увеличением первого входного напряжения V1 и уменьшается с уменьшением первого входного напряжения V1. Таким образом, схема компаратора 20, в которой цели соединения нижних затворных контактов TFT 21 и 22 изменены с выхода инвертера 26 на входной контакт DAT(+), действует таким же образом, как схема компаратора 10 согласно первому варианту осуществления. Схема компаратора 20 используется в том же варианте применения, что и схема компаратора 10. Поскольку схема компаратора 20 облегчает операцию переключения только в одном направлении, схема компаратора 20 немного более подвержена изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима, чем схема компаратора 10, что облегчает операцию переключения в комплементарном режиме. Однако в схеме компаратора 20, поскольку выходной контакт инвертера 26 не подключен к регулировочному контакту инвертера 25, нагрузка, сопровождающая выходной сигнал инвертера 26, оказывается меньше, чем в случае схемы компаратора 10. Таким образом, схема компаратора 20 обеспечивает то преимущество, что сила токового возбуждения выходного сигнала больше, чем в случае схемы компаратора 10.

Как описано выше, согласно схеме компаратора 20 этого варианта осуществления, инвертеры 25 и 26 образованы двухзатворным TFT, и на нижние затворные контакты двухзатворных TFT, которые образуют инвертер 25, подается первое входное напряжение V1, и нижние затворные контакты двухзатворных TFT, которые образуют инвертер 26, подключены к выходу инвертера 25. Таким образом, можно управлять пороговым напряжением инвертера 25 на основании входного сигнала инвертера 25 для облегчения операции переключения инвертера 25, и управлять пороговым напряжением инвертера 26 на основании выходного сигнала инвертера 25 для облегчения операции переключения инвертера 26. Таким образом, схема компаратора 20 может работать с высокой скоростью.

Третий вариант осуществления

На фиг.13 показана принципиальная схема схемы компаратора согласно третьему варианту осуществления настоящего изобретения. Схема компаратора 30, показанная на фиг.13, снабжена четырьмя TFT 31-34, двумя входными контактами DAT(+) и DAT(-) и выходным контактом OUT. TFT 31 является однозатворным TFT N-типа, TFT 32 является однозатворным TFT P-типа, TFT 33 является двухзатворным TFT N-типа, и TFT 34 является двухзатворным TFT P-типа. Затворные контакты TFT 31 и 32 подключены к входному контакту DAT(+). Кроме того, в схеме компаратора 30 не существует проводки для подключения к нижним затворным контактам TFT 31 и 32. В остальном соединение между компонентами схемы компаратора 30 такое же, как в схеме компаратора 10.

В схеме компаратора 30 TFT 31 и 32 образуют инвертер 35, и TFT 33 и 34 образуют инвертер 36. Входной контакт инвертера 35 подключен к входному контакту DAT(+), и выходной контакт подключен к регулировочному контакту инвертера 36. Входной контакт инвертера 36 подключен к входному контакту DAT(-), и выходной контакт подключен к выходному контакту OUT.

Согласно схеме компаратора 30, по аналогии со схемой компаратора 10 согласно первому варианту осуществления, управление пороговым напряжением инвертера 36 осуществляется на основании выходного сигнала инвертера 35 для облегчения операции переключения инвертера 36. Однако, поскольку инвертер 35 образован однозатворными TFT, управление пороговым напряжением инвертера 35 не осуществляется на основании выходного сигнала инвертера 36. В остальном схема компаратора 30 действует таким же образом, как схема компаратора 10 согласно первому варианту осуществления. Схема компаратора 30 используется в том же варианте применения, что и схема компаратора 10. По аналогии со схемой компаратора 20 согласно второму варианту осуществления, хотя схема компаратора 30 немного более подвержена изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима, чем схема компаратора 10, схема компаратора 30 отличается тем, что сила токового возбуждения выхода больше, чем в случае схемы компаратора 10.

Как описано выше, согласно схеме компаратора 30 этого варианта осуществления, из инвертеров 35 и 36 только инвертер 36 образован двухзатворным TFT, и нижние затворные контакты двухзатворных TFT подключены к выходу инвертера 35. Таким образом, можно управлять пороговым напряжением инвертера 36 на основании входного сигнала инвертера 35 для облегчения операции переключения инвертера 36. Таким образом, схема компаратора 30 может работать с высокой скоростью. Кроме того, согласно схеме компаратора 30, можно упростить структуру схемы по сравнению со схемой компаратора 10 или 20.

Как следует из вышеприведенного описания, схема компаратора, отвечающая настоящему изобретению, включает в себя первый инвертер, на который поступает первое входное напряжение, причем первый инвертер имеет структуру, в которой транзистор P-типа и транзистор N-типа соединены последовательно между двумя проводами питания, и второй инвертер, на который поступает второе входное напряжение, причем второй инвертер имеет структуру, идентичную структуре первого инвертера, причем, по меньшей мере, один из первого и второго инвертеров образован двухзатворными TFT, каждый из которых имеет два затворных контакта, и на верхний затворный контакт каждого двухзатворного TFT поступает входное напряжение, и нижний затворный контакт подключен к выходу другого инвертера. Таким образом, сформировав, по меньшей мере, один из двух инвертеров посредством двухзатворных TFT и соединив нижние затворные контакты двухзатворных TFT с выходом другого инвертера, можно управлять пороговым напряжением инвертера, образованного двухзатворным TFT, на основании выходного сигнала другого инвертера для облегчения операции переключения инвертера, что позволяет схеме компаратора работать с высокой скоростью.

Кроме того, согласно вышеприведенному описанию, в двухзатворном TFT пороговое напряжение Vth транзисторов, управляемое с использованием верхних затворных контактов, изменяется путем управления напряжением на нижнем затворе Vbg. Однако, напротив, пороговое напряжение Vth транзисторов, управляемое с использованием нижних затворных контактов, может изменяться путем управления напряжением на верхнем затворе Vtg. В этом случае, вышеприведенное описание можно применить, заменив верхние затворные контакты и нижние затворные контакты.

Кроме того, согласно вышеприведенному описанию, схема компаратора настоящего изобретения образована TFT. Однако схема компаратора настоящего изобретения может быть образована МОП-транзисторами и т.п. Если схема компаратора настоящего изобретения образована МОП-транзисторами, можно использовать планарные двухзатворные ПТ, имеющие такую же структуру, которая показана на фиг.2, вертикальные двухзатворные ПТ (фиг.14A) или двухзатворные ПТ плавникового типа (фиг.14B). В случае вертикальных двухзатворных ПТ стоковый ток Id течет в вертикальном направлении, как показано на фиг.14A. В случае двухзатворных ПТ плавникового типа стоковый ток Id течет в горизонтальном направлении, как показано на фиг.14B. В случае этих двух типов двухзатворных ПТ первый затворный контакт G1 и второй затворный контакт G2 обеспечены вдоль двух противоположных боковых поверхностей участка формирования канала CH. При использовании этих двух типов двухзатворных ПТ, вышеприведенное описание можно применять, рассматривая верхний затворный контакт в качестве первого затворного контакта и нижний затворный контакт в качестве второго затворного контакта.

Промышленное применение

Схема компаратора, отвечающая настоящему изобретению, невосприимчива к изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима входного сигнала, и способна работать с высокой скоростью, и, соответственно, может использоваться в различных применениях, в которых два входных напряжения сравниваются, например, в схеме интерфейса устройства отображения. Устройство отображения, отвечающее настоящему изобретению, можно использовать в качестве различных устройств отображения, например жидкокристаллического устройства отображения.

Изобретение относится к схеме компаратора, которая сравнивает два входных напряжения, и к устройству отображения, снабженному схемой компаратора. Техническим результатом является обеспечение невосприимчивости схемы компаратора к изменению пороговых напряжений транзисторов и флуктуации напряжения общего режима входного сигнала, обеспечение высокой скорости работы компаратора, а также высокой скорости осуществления сигнала, поступающего на подложку, устройством отображения, кроме того, обеспечение сокращения сигнальных линий, подключенных к подложке, и повышение надежности устройства отображения. Схема компаратора, способная сравнивать два входных напряжения, содержит первый инвертер, на который поступает первое входное напряжение, причем первый инвертер имеет структуру, в которой транзистор Р-типа и транзистор N-типа соединены последовательно между двумя проводами питания, и второй инвертер, на который поступает второе входное напряжение, причем второй инвертер имеет структуру, идентичную структуре первого инвертера, причем, по меньшей мере, один из первого и второго инвертеров образован двухзатворными транзисторами, каждый из которых имеет два затворных контакта, и на один из затворных контактов каждого двухзатворного транзистора подается входное напряжение, и другой из затворных контактов подключен к выходу другого инвертера. 2 н. и 5 з.п. ф-лы, 23 ил.

1. Схема компаратора, способная сравнивать два входных напряжения, схема содержит

первый инвертер, на который поступает первое входное напряжение, причем первый инвертер имеет структуру, в которой транзистор Р-типа и транзистор N-типа соединены последовательно между двумя проводами питания, и

второй инвертер, на который поступает второе входное напряжение, причем второй инвертер имеет структуру, идентичную структуре первого инвертера, причем, по меньшей мере, один из первого и второго инвертеров образован двухзатворными транзисторами, каждый из которых имеет два затворных контакта, и на один из затворных контактов каждого двухзатворного транзистора подается входное напряжение, и другой из затворных контактов подключен к выходу другого инвертера.

2. Схема компаратора по п.1, в которой

каждый из первого и второго инвертеров образован двухзатворными транзисторами,

на один из затворных контактов каждого двухзатворного транзистора, который образует первый инвертер, поступает первое входное напряжение, и другой из затворных контактов подключен к выходу второго инвертера, и

на один из затворных контактов каждого двухзатворного транзистора, который образует второй инвертер, поступает второе входное напряжение, и другой из затворных контактов подключен к выходу первого инвертера.

3. Схема компаратора по п.1, в которой

каждый из первого и второго инвертеров образован двухзатворными транзисторами,

на оба затворных контакта каждого двухзатворного транзистора, который образует первый инвертер, поступает первое входное напряжение, и

на один из затворных контактов каждого двухзатворного транзистора, который образует второй инвертер, поступает второе входное напряжение, и другой из затворных контактов подключен к выходу первого инвертера.

4. Схема компаратора по п.1, в которой

только второй инвертер из первого и второго инвертеров образован двухзатворными транзисторами, и

на один из затворных контактов каждого двухзатворного транзистора, который образует второй инвертер, поступает второе входное напряжение, и другой из затворных контактов подключен к выходу первого инвертера.

5. Схема компаратора по п.1, в которой

каждый из первого и второго инвертеров образован тонкопленочными транзисторами.

6. Схема компаратора по п.5, в которой

каждый из первого и второго инвертеров образован с использованием тонкопленочных транзисторов на подложке, на которой располагается пиксельная схема.

7. Устройство отображения, сформированное на подложке, устройство содержит

совокупность пиксельных схем,

схему возбуждения для пиксельных схем, и

схему интерфейса, которая преобразует вводимый извне дифференциальный сигнал в недифференциальный сигнал и выводит недифференциальный сигнал на схему возбуждения, причем

схема интерфейса включает в себя схему компаратора по любому из пп.1-6 и осуществляет преобразование дифференциального сигнала с использованием схемы компаратора.

| US 6462585 В1, 08.10.2002 | |||

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| Неполноповоротный гидродвигатель | 1979 |

|

SU840452A1 |

| Компаратор на МДП-транзисторах | 1983 |

|

SU1126943A1 |

| Компаратор напряжений | 1989 |

|

SU1688398A1 |

Авторы

Даты

2012-04-27—Публикация

2009-03-17—Подача