Настоящая заявка на патент испрашивает приоритет по предварительной заявке номер 61/014257, озаглавленной "APPARATUS AND METHOD FOR ADAPTING WORD LINE PULSE WIDTHS IN MEMORY SYSTEMS", поданной 17 декабря 2007 года, правообладателем которой является заявитель настоящей заявки и которая включена сюда посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Варианты осуществления изобретения связаны с запоминающими системами. Более конкретно, варианты осуществления изобретения связаны с адаптацией ширин импульсов словарной шины, используемой в запоминающих системах.

УРОВЕНЬ ТЕХНИКИ

По мере того как технология CMOS непрерывно масштабируется к меньшим размерам, изменения параметров процесса вследствие ограничений управления процессом, а также фундаментальных физических пределов имеют тенденцию увеличиваться. Встроенные запоминающие устройства, такие как встроенное SRAM, в частности, подвержены большим изменениям параметров процесса вследствие жестких проектных норм и их небольшого размера по сравнению с другой цифровой логикой. Чтобы удовлетворять такому большому увеличению изменений параметров процесса конструкторы запоминающих схем типично используют чрезмерно консервативные подходы к проектированию, чтобы достигать высоко параметрического и функционального выхода годных изделий.

Например, разработчик может выбирать оптимальное соотношение между производительностью (к примеру, скоростью) и/или потребляемой мощностью посредством конструирования конкретной интегральной схемы (IC) так, чтобы она функционировала в широком диапазоне изменений параметров процесса, включающих в себя как локальные (в рамках каждой IC), так и глобальные (между IC) изменения. Это приводит к большему проценту рабочих IC из числа изготовленных (т.е. увеличенному выходу годных изделий), но потери в производительности и/или потребляемой мощности могут быть существенными в тех IC, которые не подвергаются полному диапазону изменений параметров процесса. Вследствие статистического характера изменений параметров процесса фактическое число IC, подвергающихся существенному снижению производительности и/или потребляемой мощности, может быть весьма высоким.

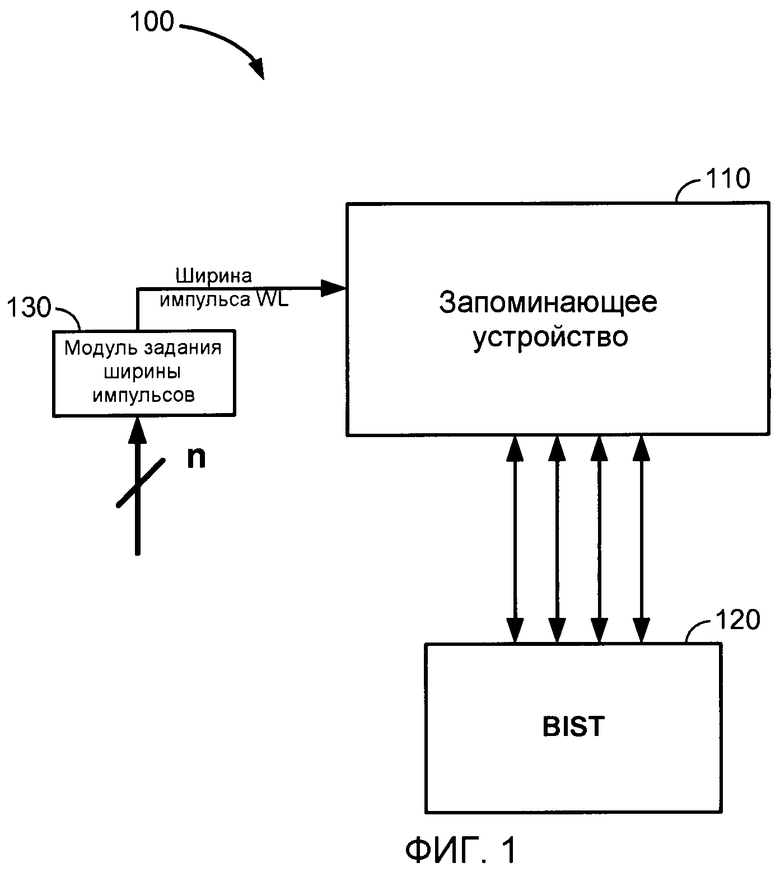

Фиг.1 является схематичным представлением, иллюстрирующим традиционную запоминающую систему 100. Система 100 включает в себя запоминающее устройство 110, схему (BIST) 120 встроенного самотестирования и модуль 130 задания ширины импульсов. BIST 120 тестирует всю или часть внутренней функциональности запоминающего устройства 110. Модуль 130 задания ширины импульсов задает ширину импульса WL, которая должна использоваться для циклов считывания/записи в запоминающем устройстве 110. Модуль 130 задания ширины импульсов может принимать внешний n-битовый код от системного контроллера и т.п., указывающий требуемую ширину импульса WL.

Как известно в данной области техники, ширина импульса WL определяет продолжительность, которую каждая операция считывания или записи требует для своего выполнения, что непосредственно влияет как на производительность, так и на потребляемую мощность этого запоминающего устройства. В общем, увеличенная ширина импульса WL обеспечивает более точную операцию считывания/записи, но работает медленнее и требует большей мощности. Напротив, уменьшенная ширина импульса WL может быть менее точной, в частности в широком диапазоне изменений параметров процесса, но может работать быстрее и требует меньшей мощности. Таким образом, задание требуемой ширины импульса WL зачастую является конструктивным компромиссом между производительностью запоминающего устройства и выходом годных изделий.

Когда серия IC, реализующих запоминающую систему 100, изготавливается, одна из традиционных технологий после изготовления, используемых для того, чтобы оптимизировать производительность запоминающего устройства и увеличивать выход годных изделий, состоит в том, чтобы использовать цифровую подгонку кремниевых кристаллов на уровне пластины. Как правило, внешний цифровой код, используемый для того, чтобы управлять шириной импульса WL (кодом ширины импульса WL), задается так, чтобы достигать целевого выхода годных изделий для определенного запоминающего устройства. Измерения выполняются для большой выборки запоминающих устройств, и выход годных изделий определяется для различных ширин импульсов WL. Оптимальная ширина импульса WL определяется на основе целевого выхода годных изделий и устанавливается для всех запоминающих устройств.

Этот подход имеет несколько ограничений. Одно ограничение заключается в том, что ширина импульса WL фиксируется для всех IC на основе критических изменений параметров процесса. Как пояснено выше, многие, если не большинство IC, не подвергаются такому критическому изменению параметров процесса. Следовательно, большие потери производительности и дополнительная потребляемая мощность могут затрагивать большую часть изготовленных IC. Другое ограничение заключается в том, что большое время тестирования требуется для того, чтобы измерять большие размеры выборок, необходимые, чтобы точно определять значение оптимальной ширины импульса WL для данного целевого выхода годных изделий.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Примерные варианты осуществления изобретения направлены на системы, схемы и способы для адаптации ширин импульсов WL, используемых в запоминающих системах.

Один вариант осуществления изобретения направлен на устройство, содержащее импульс словарной шины (WL) с ассоциированной шириной импульса WL; модуль встроенного самотестирования (BIST), который взаимодействует с запоминающим устройством, причем BIST-модуль выполнен с возможностью проводить самотестирование внутренней функциональности запоминающего устройства и предоставлять сигнал, указывающий то, прошло или не прошло запоминающее устройство самотестирование; и схему адаптивного управления WL, которая взаимодействует с BIST-модулем и запоминающим устройством, причем схема адаптивного управления WL выполнена с возможностью регулировать ширину импульса WL запоминающего устройства на основе сигнала, предоставленного посредством BIST-модуля.

Другой вариант осуществления изобретения направлен на способ регулирования ширины импульса словарной шины (WL) в запоминающей системе, включающей в себя запоминающее устройство, работающее согласно импульсу WL. Способ содержит: выполнение самотестирования в запоминающей системе, чтобы тестировать внутреннюю функциональность запоминающего устройства при текущей ширине импульса WL; регулирование ширины импульса WL запоминающего устройства на основе результатов самотестирования с использованием схем адаптивного управления WL на микросхеме.

Другой вариант осуществления изобретения направлен на устройство для регулирования ширины импульса словарной шины (WL) в запоминающей системе, включающей в себя запоминающее устройство, работающее согласно импульсу WL. Устройство содержит: средство для выполнения самотестирования в запоминающей системе, чтобы тестировать внутреннюю функциональность запоминающего устройства при текущей ширине импульса WL; средство на микросхеме для регулирования ширины импульса WL запоминающего устройства на основе результатов самотестирования.

Другой вариант осуществления изобретения направлен на машиночитаемый носитель, включающий в себя наборы инструкций, выполняемые посредством процессора, чтобы регулировать ширину импульса словарной шины (WL) в запоминающей системе, включающей в себя запоминающее устройство, работающее согласно импульсу WL. Машиночитаемый носитель содержит: первый набор инструкций, выполняемых посредством процессора, чтобы выполнять самотестирование в запоминающей системе, чтобы тестировать внутреннюю функциональность запоминающего устройства при текущей ширине импульса WL; второй набор инструкций, выполняемых посредством процессора, чтобы регулировать ширину импульса WL запоминающего устройства на основе результатов самотестирования.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Прилагаемые чертежи представлены для того, чтобы помочь в описании вариантов осуществления изобретения, и предоставлены исключительно для иллюстрации вариантов осуществления, а не их ограничения.

Фиг.1 является схематичным представлением, иллюстрирующим традиционную запоминающую систему, которая считывает/записывает данные в соответствии с импульсом словарной шины (WL).

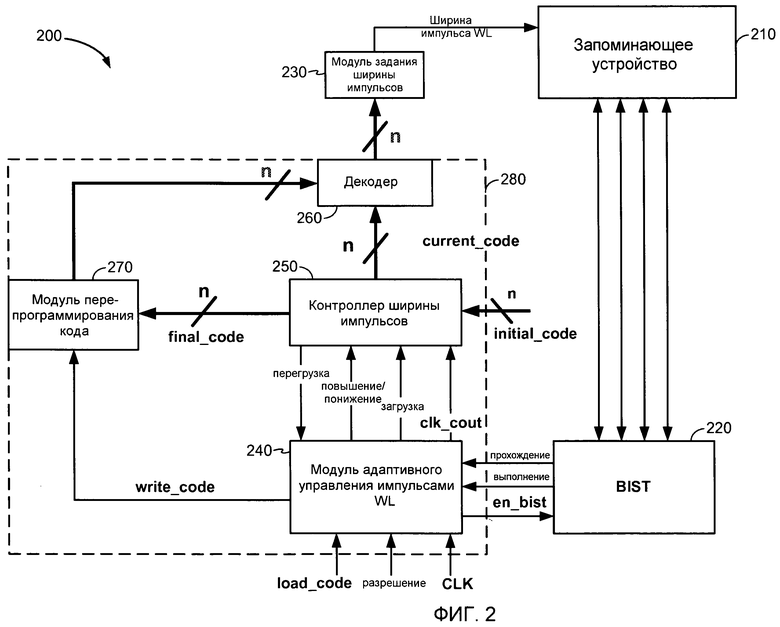

Фиг.2 изображает примерную запоминающую систему согласно вариантам осуществления настоящего изобретения.

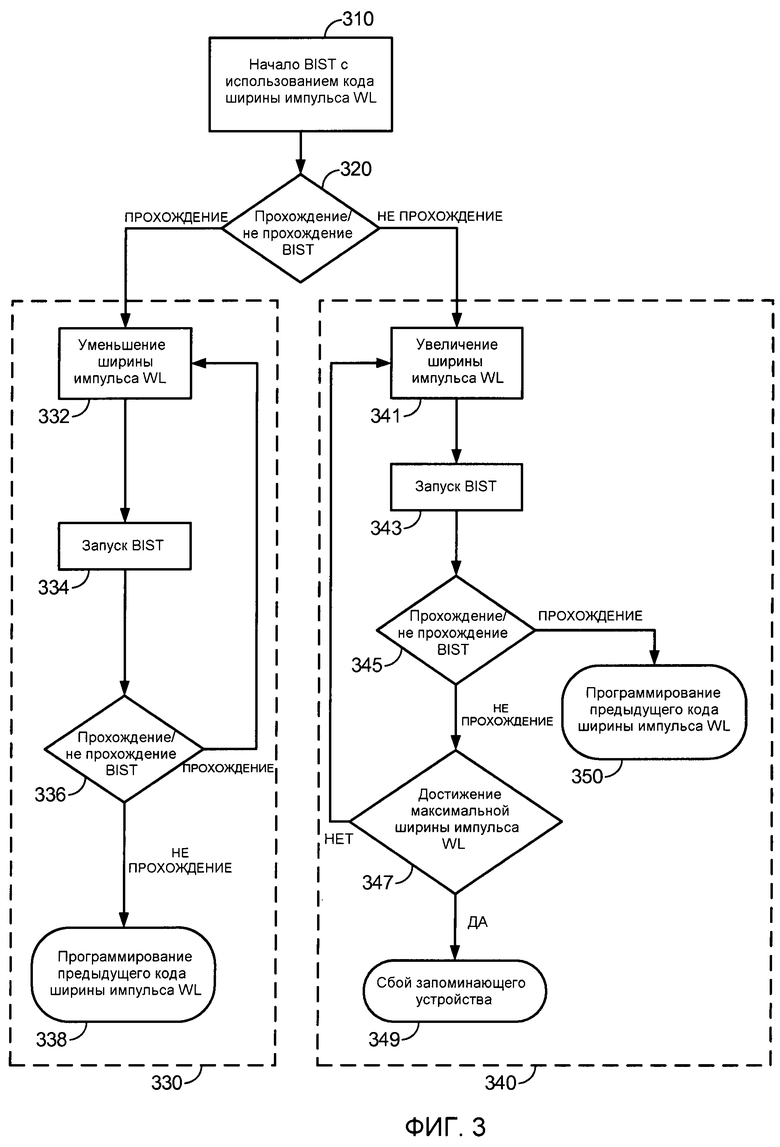

Фиг.3 является блок-схемой последовательности операций, иллюстрирующей операцию контура адаптивного управления WL.

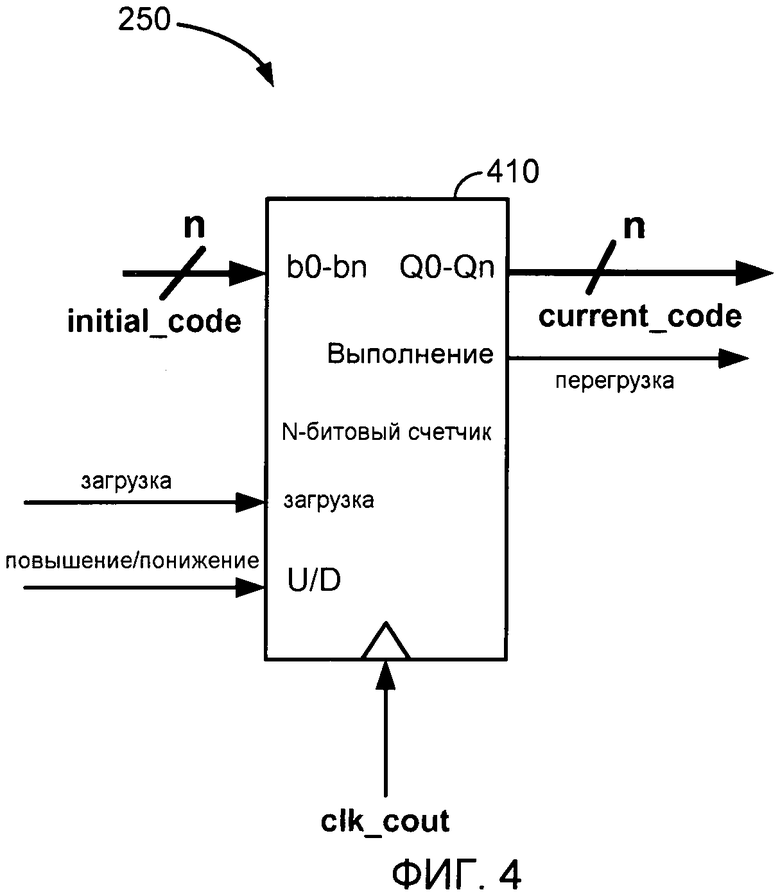

Фиг.4 иллюстрирует примерную реализацию контроллера ширины импульсов по Фиг.2 с помощью n-битового счетчика.

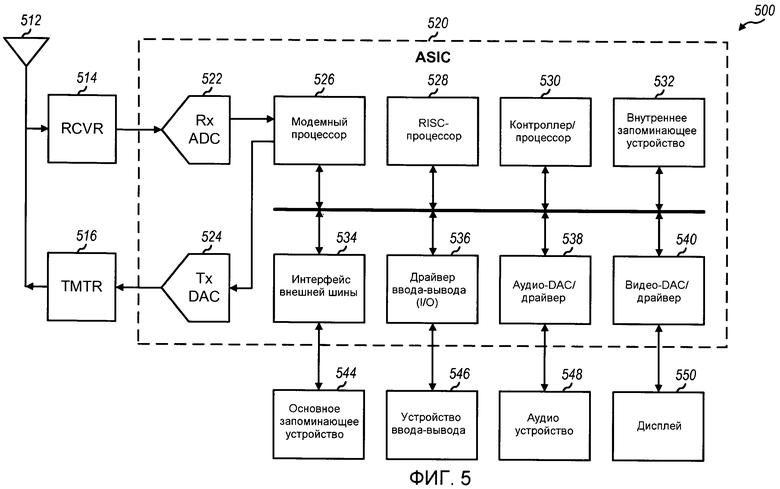

Фиг.5 показывает блок-схему компоновки устройства беспроводной связи в системе беспроводной связи.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Аспекты вариантов осуществления раскрыты в последующем описании и на прилагаемых чертежах, направленных на конкретные варианты осуществления изобретения. Альтернативные варианты осуществления могут быть разработаны без отступления от области применения изобретения. Дополнительно, хорошо известные элементы изобретения не описываются подробно или опускаются с тем, чтобы не отвлекать от важных подробностей изобретения.

Слово "примерный" используется в данном документе для того, чтобы обозначать "служащий в качестве примера, отдельного случая или иллюстрации". Любой вариант осуществления, описанный в данном документе как "примерный", не обязательно должен быть истолкован как предпочтительный или преимущественный по сравнению с другими вариантами осуществления. Аналогично, термин "варианты осуществления изобретения" не требует того, чтобы все варианты осуществления изобретения включали в себя описанный признак, преимущество или режим работы.

Как пояснено в разделе уровня техники, традиционный подход к оптимизации ширин импульсов словарной шины (WL) для запоминающих систем в данной серии интегральных схем (IC) учитывает широкий диапазон изменений параметров процесса посредством выбора оптимального соотношения между производительностью и/или потребляемой мощностью в отдельных IC, чтобы увеличивать общий выход годных изделий. Тем не менее, этот подход типично является чрезмерно консервативным для многих, если не большинства запоминающих систем в IC. Чтобы увеличивать производительность и уменьшать потребляемую мощность при одновременном сохранении и возможном увеличении общего выхода годных изделий, варианты осуществления изобретения регулируют ширину импульса WL для каждой IC по отдельности. Принимая во внимание, что традиционные подходы ограничивают ширину импульса WL в каждой IC установившимся значением на основе средних измерений для группы IC, варианты осуществления изобретения дают возможность адаптации ширины импульса WL к каждой IC по отдельности, чтобы оптимизировать производительность и потребляемую мощность с учетом фактических изменений параметров процесса, которым подвергается эта IC.

Фиг.2 иллюстрирует запоминающую систему 200 согласно варианту осуществления изобретения. Запоминающая система 200 включает в себя запоминающее устройство 210, встроенное самотестирование (BIST), описанное в разделе уровня техники. Тем не менее, запоминающая система 200 добавляет модуль 240 адаптивного управления импульсами WL, контроллер 250 ширины импульсов, декодер 260 и модуль 270 перепрограммирования кода, которые взаимодействуют с заранее существующей традиционной инфраструктурой запоминающей системы, включающей в себя запоминающее устройство 210, BIST 220 и модуль 230 задания ширины импульсов, чтобы формировать контур 280 адаптивного управления WL, который по отдельности управляет шириной импульса WL для каждого запоминающего устройства в одной или более IC, как описано ниже подробнее.

Модуль 240 адаптивного управления импульсами WL взаимодействует непосредственно с BIST 220, контроллером 250 ширины импульсов и модулем 270 перепрограммирования кода с помощью последовательности управляющих сигналов. Как проиллюстрировано на Фиг.2, модуль 240 адаптивного управления импульсами WL принимает сигнал load_code, сигнал разрешения и сигнал CLK от системного контроллера и т.п. (не показан). Сигнал load_code указывает, что начальный код ширины импульса WL должен загружаться. Сигнал разрешения инструктирует модулю 240 адаптивного управления импульсами WL начинать процедуру определения оптимальной ширины импульса WL. Сигнал CLK просто предоставляет в модуль 240 адаптивного управления импульсы WL системный синхросигнал.

Модуль 240 адаптивного управления импульсами WL отправляет сигнал en_bist в BIST 220, который инструктирует BIST 220 выполнять самотестирование в запоминающем устройстве 210. En_bist может быть реализован либо просто как один бит, где, например, 1 инструктирует BIST 220 выполнять самотестирование, а 0 инструктирует BIST 220 не выполнять самотестирование, либо за счет более сложной схемы. В ответ BIST 220 отправляет сигнал прохождения и сигнал выполнения в модуль 240 адаптивного управления импульсами WL. Сигнал прохождения указывает, прошло запоминающее устройство 210 самотестирование (т.е. запоминающее устройство 210 является удовлетворительно работающим) или не прошло запоминающее устройство 210 самотестирование (т.е. запоминающее устройство 210 не является удовлетворительно работающим). Сигнал прохождения может быть реализован либо просто как один бит, где, например, 1 указывает "прохождение", а 0 указывает "не прохождение", либо с помощью более сложной схемы. Сигнал выполнения указывает, что BIST 220 закончил выполнение самотестирования в запоминающем устройстве 210. Сигнал выполнения может быть реализован либо просто как один бит, где, например, 1 указывает, что самотестирование завершено, а 0 указывает, что самотестирование не завершено, либо с помощью более сложной схемы.

Модуль 240 адаптивного управления импульсами WL обменивается данными с контроллером 250 ширины импульсов посредством отправки сигнала загрузки и сигнала увеличения/уменьшения. Сигнал загрузки инструктирует контроллеру 250 ширины импульсов загружать начальный код ширины импульса WL. Начальный код ширины импульса WL может предоставляться в контроллер 250 ширины импульсов, например, посредством системного контроллера. Значение начального кода ширины импульса WL может быть определено на основе того, как начальный код ширины импульса WL может указывать ширину импульса WL, которая не может быть первоначально оптимальной (т.е. или слишком большой, или слишком небольшой), сигнал увеличения/уменьшения инструктирует контроллеру 250 ширины импульсов увеличивать или уменьшать код ширины импульса WL от начального значения. Сигнал увеличения/уменьшения может быть реализован либо просто как один бит, где 1, например, инструктирует контроллеру 250 ширины импульсов увеличивать значение кода ширины импульса WL, а 0 инструктирует контроллеру 250 ширины импульсов уменьшать значение кода ширины импульса WL либо с помощью более сложной схемы. Помимо этого, модуль 240 адаптивного управления импульсами WL также предоставляет в контроллер 250 ширины импульсов синхросигнал clk_cout. Сигнал clk_cout может быть преобразованной с понижением частоты версией сигнала CLK, например, чтобы упрощать увеличение или уменьшение посредством контроллера 250 ширины импульсов кода ширины импульса WL.

Модуль 240 адаптивного управления импульсами WL также принимает сигнал перегрузки от контроллера 250 ширины импульсов, указывающий то, увеличен код ширины импульса WL до максимального значения или уменьшен до минимального значения. Сигнал перегрузки может быть реализован либо просто как один бит, где, например, 1 указывает, что максимум или минимум достигнут, а 0 указывает, что максимум или минимум не достигнут, либо с помощью более сложной схемы, такой, как сигнал в два бита, где 10 указывает, что максимум достигнут, 01 указывает, что минимум достигнут, а 00 указывает, что максимум или минимум не достигнут.

Когда конечный код выбран, контроллер 250 ширины импульсов выводит этот конечный код в модуль 270 перепрограммирования кода, и модуль 240 адаптивного управления импульсами WL отправляет сигнал write_code в модуль 270 перепрограммирования кода, который инструктирует модулю 270 перепрограммирования кода программировать оптимизированный конечный код ширины импульса WL в запоминающем устройстве, содержащемся в нем. Write_code может быть реализован либо просто как один бит, где 1, например, инструктирует модулю 270 перепрограммирования кода программировать конечный код, а 0 инструктирует модулю 270 перепрограммирования кода не программировать конечный код, либо с помощью более сложной схемы. Модуль 270 перепрограммирования кода предоставляет возможность динамического перепрограммирования в реальном времени запоминающей системы 100 и постоянного хранения оптимизированного конечного кода ширины импульса WL. В некоторых вариантах применения запоминающее устройство в модуле 270 перепрограммирования кода может быть энергонезависимым запоминающим устройством, допускающим неограниченное хранение оптимизированного конечного кода импульсов WL. Например, модуль 270 перепрограммирования кода может быть реализован с помощью запоминающего устройства eFUSE или любого другого известного программируемого энергонезависимого запоминающего устройства. Тем не менее, в других вариантах применения могут быть варианты применения, где энергозависимое запоминающее устройство может использоваться.

Декодер 260 принимает код ширины импульса WL либо от контроллера 250 ширины импульсов во время определения ширины импульса WL, либо от модуля 270 перепрограммирования кода, когда код ширины импульса WL полностью сформирован. Поскольку коды ширины импульса WL не обязательно могут иметь монотонную зависимость от фактических ширин импульсов WL, декодер 260 используется для того, чтобы преобразовывать или декодировать каждый код ширины импульса WL так, что выводимая ширина импульса WL от модуля 230 задания ширины импульсов увеличивается/уменьшается монотонно с предварительно декодированным кодом ширины импульса WL. Модуль 230 задания ширины импульсов в свою очередь задает ширину импульса WL 210, используемую для считывания или записи в запоминающее устройство.

Специалисты в данной области техники должны принимать во внимание, что декодер 260 дает возможность контуру 280 адаптивного управления WL выполнять поиск в потенциальных кодах ширины импульса WL на предмет оптимизированного кода без отслеживания того, в каких кодах выполнен поиск, посредством поиска в одном направлении увеличения/уменьшения. Тем не менее, использование декодера 260 не имеет намерение ограничивать объем различных вариантов осуществления изобретения, которое альтернативно может использовать запоминающее устройство и т.п., чтобы отслеживать, какие коды тестированы.

Фиг.3 является блок-схемой последовательности операций, иллюстрирующей работу контура адаптивного управления WL согласно варианту осуществления изобретения. Операция оптимизации ширины импульса WL запоминающей системы 200 далее описывается ниже со ссылкой на Фиг.2 и 3 и со ссылкой на управляющие сигналы, описанные выше.

Согласно вариантам осуществления изобретения каждая IC независимо задает собственную ширину импульса WL. Это может выполняться, например, при начальном включении питания или каждый раз, когда необходимо. Например, известные эффекты ухудшения характеристик запоминающего устройства со временем, такие как эффекты горячих носителей, эффекты неустойчивости температуры при отрицательном смещении (NBTI) и т.д. могут уменьшать производительность запоминающего устройства со временем. Следовательно, может быть желательным регулировать ширину импульса WL запоминающего устройства согласно вариантам осуществления изобретения не только первоначально, но также и впоследствии оптимизировать работу запоминающего устройства в свете ухудшаемых характеристик IC.

Когда системный контроллер активирует контур 280 адаптивного управления WL с помощью сигнала разрешения, он инструктирует модулю 240 адаптивного управления импульсами WL загружать начальный код ширины импульса WL с использованием сигнала load_code. Модуль 240 адаптивного управления импульсами WL в свою очередь инструктирует контроллеру 250 ширины импульсов загружать начальный код ширины импульса WL с использованием сигнала загрузки. Контроллер 250 ширины импульсов выводит начальный код ширины импульса WL в декодер 260, который затем задает ширину импульса WL равной начальному значению.

Когда ширина импульса WL задана, модуль 240 адаптивного управления импульсами WL инструктирует BIST 220 выполнять самотестирование в запоминающем устройстве 210 с помощью сигнала en_bist (этап 310). BIST 220 выполняет самотестирование и указывает выполнение в модуль 240 адаптивного управления импульсами WL с помощью сигнала выполнения. BIST 220 также передает результаты самотестирования в модуль 240 адаптивного управления импульсами WL с помощью сигнала прохождения (этап 320).

Если прохождение указывается посредством сигнала прохождения, IC, по меньшей мере, удовлетворяет минимальным конструктивным техническим требованиям. Соответственно, модуль 240 адаптивного управления импульсами WL должен пытаться увеличивать производительность и уменьшать потребляемую мощность этой конкретной IC. Для этого модуль 240 адаптивного управления импульсами WL переходит в режим оптимизации (группа 330 этапов). В этом режиме модуль 240 адаптивного управления импульсами WL инструктирует контроллеру 250 ширины импульсов уменьшать код ширины импульса WL с использованием сигнала увеличения/уменьшения (этап 332). Код уменьшения ширины импульса WL и, соответственно, ширина импульса WL может давать возможность IC функционировать с увеличенной производительностью и уменьшенным потреблением мощности. Текущая ширина импульса WL применяется к запоминающему устройству 210 из текущего кода ширины импульса WL способом, описанным выше для начального кода ширины импульса WL.

Когда ширина импульса WL обновлена, модуль 240 адаптивного управления импульсами WL инструктирует BIST 220 выполнять последующее самотестирование в запоминающем устройстве 210 с помощью сигнала en_bist, чтобы тестировать, работает или нет запоминающее устройство 210 при текущем значении ширины импульса WL (этап 334). Как и выше, BIST 220 выполняет самотестирование и указывает выполнение в модуль 240 адаптивного управления импульсами WL с помощью сигнала выполнения. BIST 220 также передает результаты самотестирования в модуль 240 адаптивного управления импульсами WL с помощью сигнала прохождения (этап 336). Если запоминающее устройство 210 проходит это последующее самотестирование, оно является по-прежнему работающим даже согласно увеличенным функциональным требованиям, вытекающим из уменьшенной ширины импульса WL. Модуль 240 адаптивного управления импульсами WL затем должен пытаться увеличивать производительность и уменьшать потребляемую мощность дополнительно посредством повторения вышеуказанных операций (этап 332-336) итерационным способом до тех пор, пока запоминающее устройство 210 не сбоит при последующем самотестировании.

Когда не прохождение указывается посредством последующего самотестирования, функциональные пределы запоминающего устройства 210 достигнуты. Соответственно, модуль 240 адаптивного управления импульсами WL инструктирует модулю 270 перепрограммирования кода с помощью сигнала write_code программировать последний код ширины импульса WL, который привел к прохождению самотестирования (т.е. предыдущий код ширины импульса WL в этом режиме) (этап 338). Если минимальный код ширины импульса WL достигается, выдается сигнал перегрузки. Если запоминающее устройство 210 по-прежнему проходит последующее самотестирование с минимальной шириной импульса WL, то минимальный код ширины импульса WL должен программироваться в модуле 270 перепрограммирования кода.

Соответственно, посредством перехода в режим оптимизации контур адаптивного управления WL согласно вариантам осуществления изобретения может потенциально увеличивать производительность и уменьшать потребляемую мощность конкретной IC.

Возвращаясь теперь к начальному прохождению/не прохождению BIST (этап 320), если не прохождение указывается посредством сигнала прохождения, IC не удовлетворяет минимальным конструктивным техническим требованиям. В традиционной запоминающей системе 100 это означает, что данная конкретная IC является дефектной и должна отбрасываться. Тем не менее, согласно вариантам осуществления изобретения, эта конкретная IC все еще может быть восстановлена. Например, сбой BIST может потенциально уменьшаться посредством увеличения допустимого запаса считывания (т.е. увеличения ширины импульса WL). Для этого модуль 240 адаптивного управления импульсами WL переходит в режим восстановления (группа 340 этапов). В этом режиме модуль 240 адаптивного управления импульсами WL инструктирует контроллеру 250 ширины импульсов увеличивать код ширины импульса WL с использованием сигнала увеличения/уменьшения (этап 341). Увеличение кода ширины импульса WL и, соответственно, ширины импульса WL может давать возможность IC устойчиво функционировать, хотя при уменьшенной производительности и с более высоким потреблением мощности. Текущая ширина импульса WL применяется к запоминающему устройству 210 из текущего кода ширины импульса WL способом, описанным выше для начального кода ширины импульса WL.

Когда ширина импульса WL обновлена, модуль 240 адаптивного управления импульсами WL инструктирует BIST 220 выполнять последующее самотестирование в запоминающем устройстве 210 с помощью сигнала en_bist, чтобы тестировать, работает или нет запоминающее устройство 210 при текущем значении ширины импульса WL (этап 343). Как и выше, BIST 220 выполняет самотестирование и указывает выполнение в модуль 240 адаптивного управления импульсами WL с помощью сигнала выполнения. BIST 220 также передает результаты самотестирования в модуль 240 адаптивного управления импульсами WL с помощью сигнала прохождения (этап 345). Если запоминающее устройство 210 не проходит это последующее самотестирование, оно по-прежнему не работает даже согласно сниженным функциональным требованиям, вытекающим из увеличенной ширины импульса WL. До тех пор, пока максимальная допустимая ширина импульса WL не достигнута (этап 347), модуль 240 адаптивного управления импульсами WL далее должен пытаться уменьшать функциональные требования еще дополнительно посредством повторения вышеуказанных операций (этап 341-345) итерационным способом до тех пор, пока запоминающее устройство 210 не проходит последующее самотестирование.

Когда прохождение указывается посредством последующих самотестирований, функциональные пределы инструктируют модулю 270 перепрограммирования кода с помощью сигнала write_code программировать последний код ширины импульса WL, который привел к прохождению самотестирования (т.е. текущий код ширины импульса WL в этом режиме) (этап 350). Если максимальный код ширины импульса WL достигается и запоминающее устройство 210 по-прежнему не проходит последующее самотестирование, то контроллер 250 ширины импульсов оповещает модуль 240 адаптивного управления импульсами WL об этом с помощью сигнала перегрузки (этап 347). В этом случае это конкретное запоминающее устройство не прошло восстановление и считается нерабочим (этап 349).

Соответственно, посредством перехода в режим восстановления запоминающая система согласно вариантам осуществления изобретения может потенциально увеличивать выход годных изделий посредством восстановления IC, которые не удовлетворяют минимальным исходным конструктивным требованиям, но по-прежнему могут функционировать согласно пониженным требованиям, которые предоставляют некоторый уровень нормальной работы.

Когда конечный код ширины импульса WL запрограммирован, системный сигнал разрешения может быть деактивирован и контур 280 адаптивного управления WL отключен. Здесь, оптимизированный конечный код ширины импульса WL сохраняется в модуле 270 перепрограммирования кода и передается в декодер 260 для использования в запоминающем устройстве 210.

Специалисты в данной области техники должны принимать во внимание, что алгоритм пошагового поиска, описанный выше, показывается в качестве иллюстрации и не имеет намерение ограничивать диапазон алгоритмов поиска, которые могут быть реализованы согласно различным вариантам осуществления изобретения. Например, алгоритм поиска по дереву, алгоритм случайного поиска или другие алгоритмы поиска, которые известны в данной области техники, также могут использоваться согласно различным вариантам осуществления изобретения.

Фиг.4 иллюстрирует примерную реализацию контроллера ширины импульсов по Фиг.2 с помощью n-битового счетчика.

Как показано, n-битовый счетчик 410 принимает сигнал загрузки, сигнал увеличения/уменьшения и сигнал clk_cout. Как описано выше со ссылкой на Фиг.2, эти управляющие сигналы могут быть выведены из модуля 240 адаптивного управления импульсами WL. N-битовый счетчик 410 также принимает n-битовый начальный код ширины импульса WL от системного контроллера и т.п. N-битовый счетчик 410 выводит n-битовый текущий код ширины импульса WL и сигнал перегрузки. Как описано выше со ссылкой на Фиг.2, сигнал перегрузки может приниматься посредством модуля 240 адаптивного управления импульсами WL, и n-битовый текущий код ширины импульса WL может приниматься посредством декодера 260 и/или модуля 270 перепрограммирования кода.

N-битовый счетчик 410 включает в себя схемы для увеличения и уменьшения начального кода ширины импульса WL в соответствии с операциями, описанными выше со ссылкой на значения кодов ширины импульса b0-bn, в последовательности устройств хранения битов (к примеру, триггеров). Когда сигнал увеличения/уменьшения принимается, n-битовый счетчик 410 увеличивает или уменьшает сохраненный код ширины импульса WL в соответствии с сигналом clk_cout с использованием схем счетчика, которые известны в данной области техники и дополнительное описание которых опускается здесь.

Когда текущий код ширины импульса WL обновлен, он выводится как текущие значения кода ширины импульса WL Q0-Qn, которые могут использоваться для того, чтобы регулировать ширину импульса WL и т.д. Операция подсчета также отслеживает все формируемые биты переполнения из вычислений. Биты переполнения выводятся с использованием сигнала перегрузки, чтобы указывать, что максимальное или минимальное значение достигнуто. Как пояснено выше, это полезно при определении того, достигнута или нет максимальная или минимальная функциональность.

Технологии, описанные в данном документе, могут использоваться для различных электронных устройств, таких как устройства беспроводной связи, карманные устройства, игровые устройства, вычислительные устройства, компьютеры, портативные компьютеры, потребительские электронные устройства и т.д. Примерное использование технологий для устройства беспроводной связи описывается ниже.

Фиг.5 показывает блок-схему компоновки устройства 500 беспроводной связи в системе беспроводной связи. Беспроводное устройство 500 может быть сотовым телефоном, терминалом, телефонной трубкой, персональным цифровым устройством (PDA) и т.д. Система беспроводной связи может быть системой с множественным доступом с кодовым разделением каналов (CDMA), глобальной системой мобильной связи (GSM) и т.д.

Беспроводное устройство 500 допускает предоставление двунаправленной связи через тракт приема и тракт передачи. В тракте приема сигналы, передаваемые посредством базовых станций (не показаны), принимаются посредством антенны 512 и предоставляются в приемное устройство (RCVR) 514. Приемное устройство 514 приводит к требуемым параметрам принимаемый сигнал и предоставляет аналоговый входной сигнал в специализированную интегральную схему (ASIC) 520. В тракте передачи передающее устройство (TMTR) 516 принимает и приводит к требуемым параметрам аналоговый выходной сигнал от ASIC 520 и формирует модулированный сигнал, который передается через антенну 512 в базовые станции.

ASIC 520 может включать в себя различные модули обработки, интерфейса и запоминающие устройства, такие как, к примеру, ADC приема (Rx ADC) 522, DAC передачи (Tx DAC) 524, модемный процессор 526, процессор с сокращенным набором команд (RISC) 528, контроллер/процессор 530, внутреннее запоминающее устройство 532, интерфейс 534 внешней шины, драйвер ввода-вывода (I/O) 536, аудио-DAC/драйвер 538 и видео-DAC/драйвер 540. Rx ADC 522 оцифровывает аналоговый входной сигнал от приемного устройства 514, и предоставляет выборки в модемный процессор 526, и предоставляет аналоговый выходной сигнал в передающее устройство 516. Модемный процессор 526 выполняет обработку для передачи и приема данных, к примеру кодирование, модуляцию, демодуляцию, декодирование и т.д. RISC-процессор 528 может выполнять различные типы обработки для беспроводного устройства 500, к примеру обработку для видео, графики, приложений верхнего уровня и т.д. Контроллер/процессор 530 может направлять работу различных модулей обработки и интерфейса в рамках ASIC 520. Внутреннее запоминающее устройство 532 сохраняет данные и/или инструкции для различных модулей в рамках ASIC 520.

EBI 534 упрощает передачу данных между ASIC 520 и основным запоминающим устройством 544. Драйвер 536 ввода-вывода управляет устройством 546 ввода-вывода через аналоговый или цифровой интерфейс. Аудио-DAC/драйвер 538 управляет аудиоустройством 548, которое может быть динамиком, гарнитурой, наушник и т.д. Видео-DAC/драйвер 540 управляет дисплеем 550, который может быть жидкокристаллическим дисплеем (ЖК-дисплеем) и т.д.

Внутреннее запоминающее устройство 532, основное запоминающее устройство 544 и/или другие модули могут реализовывать технологии, описанные в данном документе. Например, любое из запоминающих устройств может быть сформировано, как показано на Фиг.2.

В связи с вышеизложенным следует принимать во внимание, что варианты осуществления изобретения также могут включать в себя способы для выполнения функций, последовательности действий и/или алгоритмов, описанных в данном документе. Например, способ адаптации ширин импульсов WL, используемых в запоминающих системах, может выполняться в соответствии с блок-схемой последовательности операций, проиллюстрированной на Фиг.3.

Также следует принимать во внимание, что способы согласно вариантам осуществления изобретения могут быть реализованы в аппаратных средствах и/или программном обеспечении. Аппаратные/программные реализации могут включать в себя комбинацию процессора(ов) и изделия(й). Например, RISC-процессор 528 может быть выполнен с возможностью реализовывать технологии для адаптации ширин импульсов WL, описанной в данном документе, чтобы оптимизировать работу внутреннего запоминающего устройства 532 и/или основного запоминающего устройства 544. Изделие(я) дополнительно может включать в себя носители хранения данных и выполняемую компьютерную программу(ы), например компьютерный программный продукт, сохраненный на машиночитаемом носителе. Выполняемая компьютерная программа(ы) может включать в себя наборы инструкций, чтобы выполнять описанные операции или функции. Следует принимать во внимание, что при использовании в данном документе набор инструкций может включать в себя одну или более инструкций.

Варианты осуществления изобретения, описанные выше, предоставляют несколько преимуществ по сравнению с другими традиционными технологиями. Например, технологии, описанные в данном документе, предусматривают увеличение общего выхода годных изделий. Кроме того, IC, которые изготавливаются, не предполагают изменения параметров процесса по сценарию наихудшего случая, приводящих к уменьшению ширины импульса WL, что позволяет улучшать характеристики производительности и потребляемой мощности, а также повышать стабильность запоминающих ячеек, например, посредством уменьшения вероятности смены состояния ячеек. Вследствие более жесткого распределения потребляемой мощности по различным IC может осуществляться лучшее прогнозирование полной мощности IC. Помимо этого, поскольку большая часть изготовленных IC может иметь меньшее потребление мощности, среднее потребление мощности для всех изготовленных IC может уменьшаться. Допустимый запас чувствительности также может уменьшаться до тех пор, пока запоминающее устройство не сбоит, что приводит к более быстрому срабатыванию по допустимому запасу чувствительности. Допустимый запас чувствительности также может быть оптимизирован для каждого запоминающего устройства по отдельности, как требуется для корректной работы запоминающего устройства. Воздействие на время тестирования также является незначительным, поскольку технологии, описанные в данном документе, используют BIST на микросхеме для того, чтобы адаптировать ширину импульса WL, что не требует дополнительного внешнего тестирования.

Хотя вышеприведенное описание показывает иллюстративные варианты осуществления изобретения, следует отметить, что различные изменения и модификации могут быть выполнены в них без отступления от объема изобретения, задаваемого посредством прилагаемой формулы изобретения. Например, специалисты в данной области техники должны принимать во внимание, что алгоритм пошагового поиска, описанный выше, является только одним из множества алгоритмов поиска, которые могут быть реализованы для того, чтобы находить оптимизированный код ширины импульса WL. Алгоритм поиска по дереву, алгоритм случайного поиска или другие алгоритмы поиска, которые известны в данной области техники, также могут использоваться согласно различным вариантам осуществления изобретения. Функции, этапы и/или действия в формуле изобретения на способ согласно вариантам осуществления изобретения, описанным в данном документе, не обязательно должны выполняться в каком-либо конкретном порядке. Более того, хотя элементы изобретения могут быть описаны или приведены в формуле изобретения в единственном числе, множественное число подразумевается, если ограничение на единственное число не указано в явной форме.

Изобретение относится к компьютерной технике и может быть использовано для адаптации ширин импульсов словарной шины в запоминающих системах. Технический результат заключается в увеличении характеристик производительности, потребляемой мощности и стабильности работы запоминающих ячеек. Раскрыты системы, схемы и способы для адаптации ширин импульсов словарной шины (WL), используемых в запоминающих системах. Один вариант осуществления изобретения направлен на устройство, содержащее запоминающую систему. Устройство содержит: запоминающее устройство, работающее согласно импульсу словарной шины (WL) с ассоциированной шириной импульса WL; модуль встроенного самотестирования (BIST), который взаимодействует с запоминающим устройством, причем BIST-модуль выполнен с возможностью проводить самотестирование внутренней функциональности запоминающего устройства и предоставлять сигнал, указывающий то, прошло или не прошло запоминающее устройство самотестирование; схему адаптивного управления WL, которая взаимодействует с BIST-модулем и запоминающим устройством, причем схема адаптивного управления WL выполнена с возможностью регулировать ширину импульса WL запоминающего устройства на основе сигнала, предоставленного посредством BIST-модуля. 4 н. и 34 з.п. ф-лы, 5 ил.

1. Устройство для регулирования ширин импульсов словарной шины, содержащее запоминающую систему, причем запоминающая система содержит:

запоминающее устройство, работающее согласно импульсу словарной шины (WL) с ассоциированной шириной импульса WL;

модуль встроенного самотестирования (BIST), который взаимодействует с запоминающим устройством, причем BIST-модуль выполнен с возможностью проводить самотестирование внутренней функциональности запоминающего устройства и предоставлять сигнал, указывающий то, прошло или не прошло запоминающее устройство самотестирование; и

схему адаптивного управления WL, которая взаимодействует с BIST-модулем и запоминающим устройством, причем схема адаптивного управления WL выполнена с возможностью регулировать ширину импульса WL запоминающего устройства в пределах заранее определенных максимального и минимального разрешенных значений ширины импульса WL на основе сигнала, предоставленного посредством BIST-модуля.

2. Устройство по п.1, в котором схема адаптивного управления WL выполнена с возможностью увеличивать ширину импульса WL, если сигнал, предоставленный посредством BIST-модуля, указывает, что запоминающее устройство не прошло самотестирование, и уменьшать ширину импульса WL, если сигнал, предоставленный посредством BIST-модуля, указывает, что запоминающее устройство прошло самотестирование.

3. Устройство по п.2, в котором схема адаптивного управления WL дополнительно выполнена с возможностью инструктировать BIST-модуль на выполнение последующих самотестирований внутренней функциональности запоминающего устройства по мере того, как ширина импульса WL увеличивается или уменьшается, до тех пор пока результат самотестирования не изменяется с прохождения на непрохождение или с непрохождения на прохождение.

4. Устройство по п.3, в котором схема адаптивного управления WL выполнена с возможностью задавать ширину импульса WL запоминающего устройства равной значению ширины импульса WL, используемому непосредственно перед тем, как самотестирование изменено с прохождения на непрохождение.

5. Устройство по п.3, в котором схема адаптивного управления WL выполнена с возможностью задавать ширину импульса WL запоминающего устройства равной значению ширины импульса WL, используемому, когда самотестирование изменяется с непрохождения на прохождение.

6. Устройство по п.3, в котором схема адаптивного управления WL выполнена с возможностью увеличивать или уменьшать ширину импульса WL от начального значения способом контура с обратной связью посредством предоставления нового значения, определенного на основе сигнала, предоставленного посредством BIST-модуля.

7. Устройство по п.6, в котором схема адаптивного управления WL выполнена с возможностью увеличивать или уменьшать ширину импульса WL.

8. Устройство по п.1, в котором схема адаптивного управления WL содержит:

первую схему управления, которая взаимодействует с BIST-модулем, причем первая схема управления выполнена с возможностью определения того, увеличивать или уменьшать ширину импульса WL запоминающего устройства, на основе сигнала, предоставленного посредством BIST-модуля, и предоставлять первый управляющий сигнал, указывающий определенные регулирования ширины импульса WL; и

вторую схему управления, которая взаимодействует с первой схемой управления, причем вторая схема управления выполнена с возможностью регулировать ширину импульса WL на основе первого управляющего сигнала, предоставленного посредством первой схемы управления.

9. Устройство по п.8, в котором первая схема управления определяет увеличивать ширину импульса WL, если сигнал, предоставленный посредством BIST-модуля, указывает, что запоминающее устройство не прошло самотестирование, и уменьшать ширину импульса WL, если сигнал, предоставленный посредством BIST-модуля, указывает, что запоминающее устройство прошло самотестирование.

10. Устройство по п.8, в котором вторая схема управления дополнительно выполнена с возможностью предоставлять сигнал перегрузки в первую схему управления, указывающий то, что ширина импульса WL достигла упомянутого заранее определенного максимального или минимального разрешенного значения ширины импульса WL.

11. Устройство по п.10, в котором вторая схема управления представляет собой счетчик, выполненный с возможностью увеличивать или уменьшать значение ширины импульса WL согласно первому управляющему сигналу, предоставленному посредством первой схемы управления, и выполненный с возможностью предоставлять отрегулированную ширину импульса WL как увеличенное/уменьшенное значение и предоставлять сигнал перегрузки как бит переполнения операции увеличения/уменьшения.

12. Устройство по п.8, в котором схема адаптивного управления WL дополнительно выполнена с возможностью преобразовывать отрегулированную ширину импульса WL в допустимые ширины импульсов WL запоминающего устройства способом монотонного увеличения или уменьшения.

13. Устройство по п.8, в котором схема адаптивного управления WL дополнительно включает в себя модуль перепрограммирования, который взаимодействует с первой и второй схемами управления, причем вторая схема управления выполнена с возможностью предоставлять отрегулированное значение ширины импульса WL в модуль перепрограммирования, при этом первая схема управления выполнена с возможностью предоставлять сигнал записи, который инструктирует модулю перепрограммирования сохранять отрегулированное значение ширины импульса WL, предоставленное посредством второй схемы управления, и модуль перепрограммирования выполнен с возможностью предоставлять энергонезависимое хранение отрегулированного значения ширины импульса WL.

14. Устройство по п.8, которое представляет собой устройство беспроводной связи, причем устройство дополнительно содержит системный контроллер.

15. Устройство по п.14, в котором системный контроллер выполнен с возможностью инструктировать запоминающей системе регулировать ширину импульса WL при начальном включении питания устройства беспроводной связи.

16. Устройство по п.14, в котором системный контроллер выполнен с возможностью инструктировать запоминающей системе периодически регулировать ширину импульса WL согласно заданному интервалу времени.

17. Способ регулирования ширины импульса словарной шины (WL) в запоминающей системе, включающей в себя запоминающее устройство, работающее согласно импульсу WL, при этом способ содержит этапы, на которых:

выполняют самотестирование в запоминающей системе, чтобы тестировать внутреннюю функциональность запоминающего устройства при текущей ширине импульса WL; и

регулируют ширину импульса WL запоминающего устройства в пределах заранее определенных максимального и минимального разрешенных значений ширины импульса WL на основе результатов самотестирования с использованием схем адаптивного управления WL на микросхеме.

18. Способ по п.17, в котором этап регулирования включает в себя этап, на котором увеличивают ширину импульса WL, если запоминающее устройство не проходит самотестирование, и уменьшают ширину импульса WL, если запоминающее устройство проходит самотестирование.

19. Способ по п.18, дополнительно содержащий этап, на котором повторяют упомянутые выполнение и регулирование до тех пор, пока результат самотестирования не изменяется с прохождения на непрохождение или с непрохождения на прохождение.

20. Способ по п.19, дополнительно содержащий этап, на котором преобразуют отрегулированную ширину импульса WL в допустимые ширины импульсов WL запоминающего устройства способом монотонного увеличения или уменьшения.

21. Способ по п.19, дополнительно содержащий этап, на котором задают ширину импульса WL запоминающего устройства равной значению ширины импульса WL, используемому непосредственно перед тем, как самотестирование изменено с прохождения на непрохождение.

22. Способ по п.19, дополнительно содержащий этап, на котором задают ширину импульса WL запоминающего устройства равной значению ширины импульса WL, используемому, когда самотестирование изменяется с непрохождения на прохождение.

23. Способ по п.17, в котором операции выполнения и регулирования инициируются при начальном включении питания запоминающей системы.

24. Способ по п.17, в котором операции выполнения и регулирования инициируются периодически согласно заданному интервалу времени.

25. Устройство для регулирования ширины импульса словарной шины (WL) в запоминающей системе, включающей в себя запоминающее устройство, работающее согласно импульсу WL, при этом устройство содержит:

средство для выполнения самотестирования в запоминающей системе, чтобы тестировать внутреннюю функциональность запоминающего устройства при текущей ширине импульса WL; и

средство на микросхеме для регулирования ширины импульса WL запоминающего устройства в пределах заранее определенных максимального и минимального разрешенных значений ширины импульса WL на основе результатов самотестирования.

26. Устройство по п.25, в котором средство для регулирования включает в себя средство для увеличения ширины импульса WL, если запоминающее устройство не проходит самотестирование, и средство для уменьшения ширины импульса WL, если запоминающее устройство проходит самотестирование.

27. Устройство по п.26, дополнительно содержащее средство для повторения выполнения и регулирования до тех пор, пока результат самотестирования не изменяется с прохождения на непрохождение или с непрохождения на прохождение.

28. Устройство по п.27, дополнительно содержащее средство для преобразования отрегулированной ширины импульса WL в допустимые ширины импульсов WL запоминающего устройства способом монотонного увеличения или уменьшения.

29. Устройство по п.27, дополнительно содержащее средство для задания ширины импульса WL запоминающего устройства равной значению ширины импульса WL, используемому непосредственно перед тем, как самотестирование изменено с прохождения на непрохождение.

30. Устройство по п.27, дополнительно содержащее средство для задания ширины импульса WL запоминающего устройства равной значению ширины импульса WL, используемому, когда самотестирование изменяется с непрохождения на прохождение.

31. Машиночитаемый носитель, включающий в себя наборы инструкций, исполняемых посредством процессора, чтобы регулировать ширину импульса словарной шины (WL) в запоминающей системе, включающей в себя запоминающее устройство, работающее согласно импульсу WL, при этом машиночитаемый носитель содержит:

первый набор инструкций для выполнения самотестирования в запоминающей системе, чтобы тестировать внутреннюю функциональность запоминающего устройства при текущей ширине импульса WL; и

второй набор инструкций для регулирования ширины импульса WL запоминающего устройства в пределах заранее определенных максимального и минимального разрешенных значений ширины импульса WL на основе результатов самотестирования.

32. Машиночитаемый носитель по п.31, в котором второй набор инструкций включает в себя инструкции, исполняемые посредством процессора, чтобы увеличивать ширину импульса WL, если запоминающее устройство не проходит самотестирование, и уменьшать ширину импульса WL, если запоминающее устройство проходит самотестирование.

33. Машиночитаемый носитель по п.32, дополнительно содержащий третий набор инструкций для повторения первого и второго наборов инструкций до тех пор, пока результат самотестирования не изменяется с прохождения на непрохождение или с непрохождения на прохождение.

34. Машиночитаемый носитель по п.33, дополнительно содержащий четвертый набор инструкций для преобразования отрегулированной ширины импульса WL в допустимые ширины импульсов WL запоминающего устройства способом монотонного увеличения или уменьшения.

35. Машиночитаемый носитель по п.33, дополнительно содержащий пятый набор инструкций для задания ширины импульса WL запоминающего устройства равной значению ширины импульса WL, используемому непосредственно перед тем, как самотестирование изменено с прохождения на непрохождение.

36. Машиночитаемый носитель по п.33, дополнительно содержащий шестой набор инструкций для задания ширины импульса WL запоминающего устройства равной значению ширины импульса WL, используемому, когда самотестирование изменяется с непрохождения на прохождение.

37. Машиночитаемый носитель по п.31, дополнительно содержащий седьмой набор инструкций для выполнения первого и второго наборов инструкций при начальном включении питания запоминающей системы.

38. Машиночитаемый носитель по п.31, дополнительно содержащий восьмой набор инструкций для выполнения первого и второго наборов инструкций периодически согласно заданному интервалу времени.

| US 2002024062 A1, 28.02.2002 | |||

| US 2005286332 A1, 29.12.2005 | |||

| US 6535752 B1, 18.03.2003 | |||

| US 2004210803 A1, 21.10.2004 | |||

| САМОКОРРЕКТИРУЮЩЕЕСЯ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297032C2 |

Авторы

Даты

2012-07-10—Публикация

2008-12-15—Подача