Область техники

Настоящее раскрытие относится в целом к области процессоров и в частности к способу тестирования многопортовых массивов памяти на рабочей частоте.

Уровень техники

Микропроцессоры осуществляют вычислительные операции в самых разнообразных приложениях. Процессор может играть роль центрального или главного блока обработки в стационарной вычислительной системе, например на сервере или настольном компьютере. Высокая скорость выполнения является основной характеристикой для таких процессоров настольных компьютеров. Кроме того, расширяется применение процессоров в мобильных компьютерах, например портативных компьютерах и карманных персональных компьютерах (КПК), и во встроенных приложениях, например мобильных телефонах, приемниках глобальной системы позиционирования (GPS), портативных клиентах электронной почты и пр. В таких мобильных приложениях, помимо высокой скорости выполнения, желательно обеспечивать низкое энергопотребление и компактные размеры.

Многие программы пишутся из расчета, что компьютер, на котором они выполняются, имеет очень большой (в идеале, неограниченный) объем быстрой памяти. Обычно современные процессоры эмулируют идеальное условие неограниченной быстрой памяти с использованием иерархии типов памяти, каждый из которых имеет соответствующие скоростные и стоимостные характеристики. Типы памяти в иерархии варьируются от очень быстрой и очень дорогой на верхнем уровне, с постепенным переходом к более медленным, но более дешевым типам памяти при переходе на более низкие уровни. Типичная иерархия памяти процессора может содержать регистры (вентили) в процессоре на верхнем уровне; один или несколько блоков кэш-памяти на кристалле, выполненных в виде статической оперативной памяти (SRAM); возможно, внекристальный кэш (SRAM); главную память в виде динамической памяти с произвольным доступом (DRAM); дисковое запоминающее устройство (магнитный носитель с электромеханическим доступом); и ленту или компакт-диск (CD) (магнитный или оптический носитель) на самом низком уровне. Большинство портативных электронных устройств имеют ограниченное, если вообще имеют, дисковое хранилище, вследствие чего главная память, часто ограниченная в объеме, является самым низким уровнем в иерархии памяти.

Высокоскоростные регистры на кристалле образуют верхний уровень иерархии памяти процессора. Дискретные регистры и/или защелки используются в качестве элементов памяти в конвейере выполнения команд. Большинство архитектур на основе набора команд RISC включает в себя набор регистров общего назначения (РОН), которые используются процессором для хранения самых разнообразных данных, например кодов операций для команд, адресов, смещений, операндов, а также промежуточных и конечных результатов арифметических и логических операций и пр.

В некоторых процессорах логические РОН соответствуют физическим элементам памяти. В других процессорах производительность повышается за счет динамического присвоения идентификатора каждого логического РОН одной из ячеек памяти, образующих большой набор, или одному из физических регистров (операция, известная в технике как переименование регистров). В любом случае элементы памяти, доступ к которым осуществляется через идентификаторы логических РОН, можно реализовать не как дискретные регистры, но как ячейки памяти в массиве памяти. Регистры или элементы памяти массива памяти, реализующие логические РОН, являются многопортовыми (многоканальными). Таким образом, несколько разных элементов процессора, например различные каскады конвейера, АЛУ, кэш-память и пр., могут производить в них запись и/или считывать их содержимое.

Тестирование является важной составляющей производства ИС, призванной выявлять и устранять дефектные или некондиционные компоненты. Тестирование массивов памяти сопряжено с особыми трудностями. Способ автоматической генерации тестовых шаблонов (ATPG) предусматривает сканирование шаблона возбуждения в одном наборе регистров или защелок, объединенных в цепочку сканирования, применение шаблона для тестирования произвольной логики, сбор результатов в другом наборе регистров или защелок, объединенных в цепочку сканирования, и сканирование собранных результатов для сравнения с предполагаемыми значениями. Массивы памяти невозможно эффективно тестировать с использованием методов ATPG вследствие промежуточного хранения тестовых шаблонов в массиве.

Массивы памяти в процессоре можно тестировать путем функционального тестирования, в котором в конвейере процессора выполняется код для записи тестовых шаблонов в массив (например, в логические РОН), затем считывать значения и сравнивать их с предполагаемыми значениями. Функциональное тестирование требует много времени и неэффективно, поскольку до выполнения тестов необходимо инициализировать процессор и загружать тестовый код в кэш. Дополнительно, пункт контроля и наблюдения - в конвейере - значительно удален от тестируемых ячеек памяти, и изоляция выявленных дефектов от схем, вносящих помехи, может вызывать затруднения.

Соответственно, многие отвечающие уровню техники процессоры со встроенными массивами памяти включают в себя схему встроенного самотестирования (BIST), которая тестирует массив памяти в режиме тестирования. Контроллер BIST записывает шаблоны данных в массив памяти, считывает шаблоны данных и сравнивает данные чтения с предполагаемыми данными. В функциональном режиме контроллер BIST неактивен, и массив памяти контролируется схемами управления процессора. Системы BIST, отвечающие уровню техники, включают в себя выделенный тестовый порт в массиве памяти для записи и/или чтения в массиве в ходе тестирования. Это налагает ограничение снизу на длительность тестирования за счет ограничения диапазона доступа к памяти; не позволяет тестировать схемы ввода/вывода памяти, включая функциональные порты чтения и записи; и может препятствовать выявлению электрических предельных состояний, которые выявляются только в случае одновременного доступа к массиву через два или более порта.

Сущность изобретения

Согласно одному или более вариантам осуществления многопортовый массив памяти тестируется контроллером BIST путем одновременной записи данных в массив через два или более порта записи и/или одновременного считывания данных из массива через два или более порта чтения, на рабочей частоте процессора. Сравнение данных, считанных из массива, с данными, записанными в массив, можно осуществлять последовательно или параллельно. Компараторные схемы эффективно отключаются в ходе нормальной работы процессора. Путем одновременной записи и/или чтения данных через несколько портов можно выявлять латентные электрические предельные состояния (ограничения), и время тестирования сокращается, по сравнению со способами тестирования, отвечающими уровню техники.

Один вариант осуществления предусматривает способ тестирования массива памяти, имеющего множество портов записи, в процессоре. Первый шаблон данных записывается по первому адресу в массив через первый порт записи. Второй шаблон данных одновременно записывается по второму адресу в массив через второй порт записи. Первый и второй шаблоны данных считываются из массива. Первый и второй шаблоны данных, считанные из массива, сравниваются с первым и вторым шаблонами данных, записанными в массив, соответственно.

Другой вариант осуществления предусматривает способ тестирования массива памяти, имеющего множество портов чтения, в процессоре. Первый шаблон данных записывается по первому адресу в массив. Второй шаблон данных записывается по второму адресу в массив. Первый шаблон данных считывается из массива через первый порт чтения. Второй шаблон данных одновременно считывается из массива через второй порт чтения. Первый и второй шаблоны данных, считанные из массива, сравниваются с первым и вторым шаблонами данных, записанными в массив, соответственно.

Еще один вариант осуществления предусматривает способ тестирования массива памяти в процессоре. Один или несколько заранее определенных шаблонов данных записываются в массив. Шаблоны данных одновременно считываются из массива через два или более порта чтения, что позволяет выявлять электрические предельные состояния в массиве и/или портах чтения, не выявленные путем чтения данных через один порт чтения единовременно.

Еще один вариант осуществления предусматривает процессор. Процессор включает в себя массив памяти, имеющий по меньшей мере один порт записи и множество портов-защелок чтения; первый компаратор данных, имеющий входы для данных чтения и данных сравнения и выводящий индикацию, совпадают ли данные чтения с шаблоном данных сравнения; и первый селектор, избирательно направляющий данные из двух или более первых портов чтения на вход данных чтения первого компаратора. Процессор дополнительно включает в себя контроллер BIST, управляющий портом записи, первыми портами чтения, и первый селектор, выдающий данные записи на порт записи и данные сравнения на вход данных сравнения первого компаратора и принимающий выход первого компаратора. Контроллер BIST способен записывать один или более заранее определенный шаблон данных в массив через порт записи; одновременно считывать записанные данные из массива через два или более первых порта чтения; и последовательно предписывать первому селектору направлять данные из каждого первого порта чтения на первый компаратор, выдавать соответствующие данные сравнения на первый компаратор и проверять массив путем проверки выхода первого компаратора.

Краткое описание чертежей

Фиг.1 - функциональная блок-схема процессора.

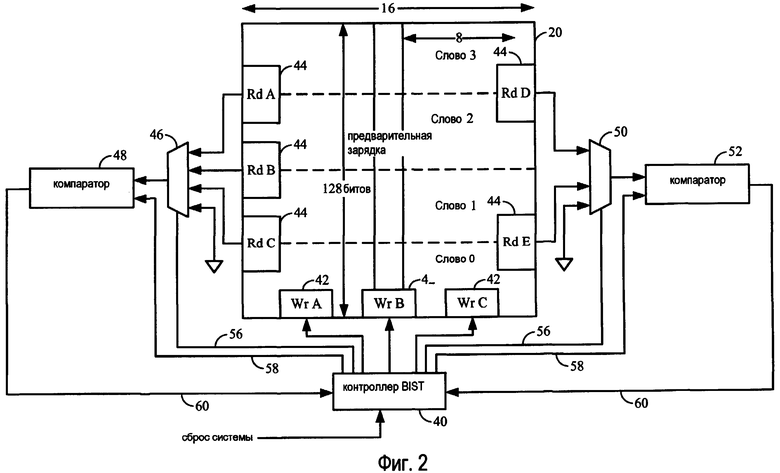

Фиг.2 - функциональная блок-схема массива памяти, реализующего многопортовый регистровый файл, и схемы BIST.

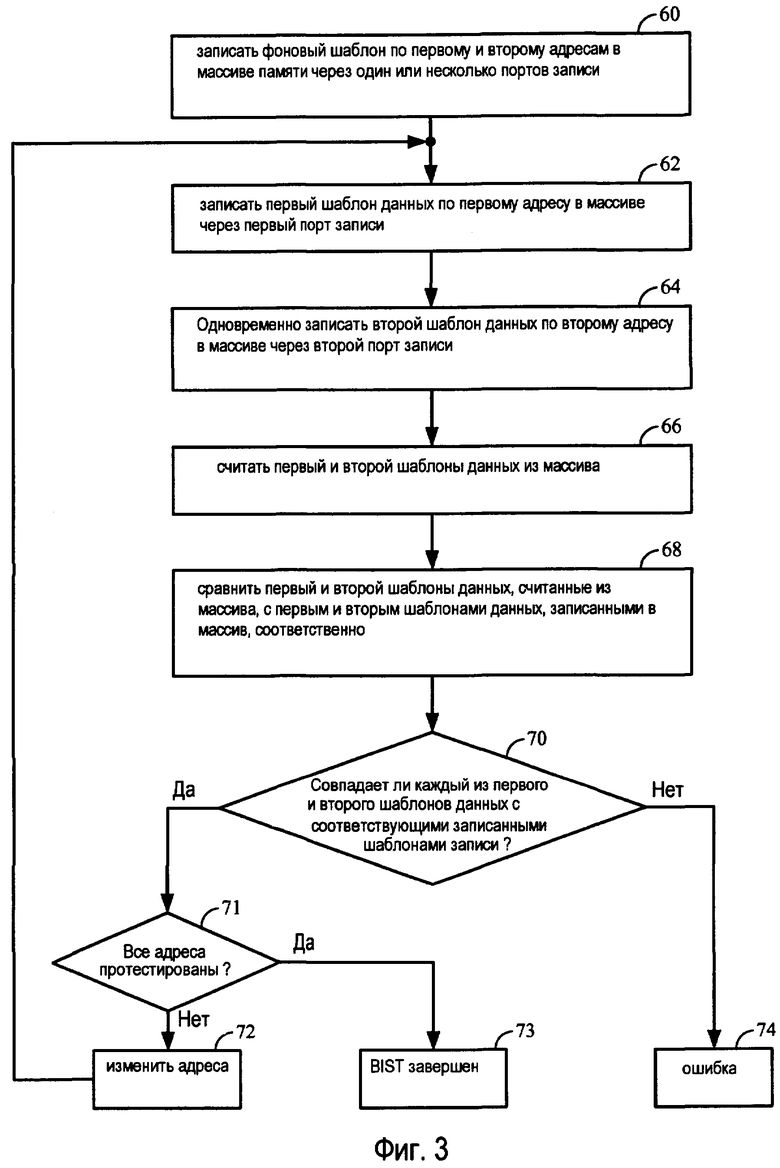

Фиг.3 - последовательность операций способа BIST для массива памяти путем одновременной записи тестовых шаблонов через два или более порта записи.

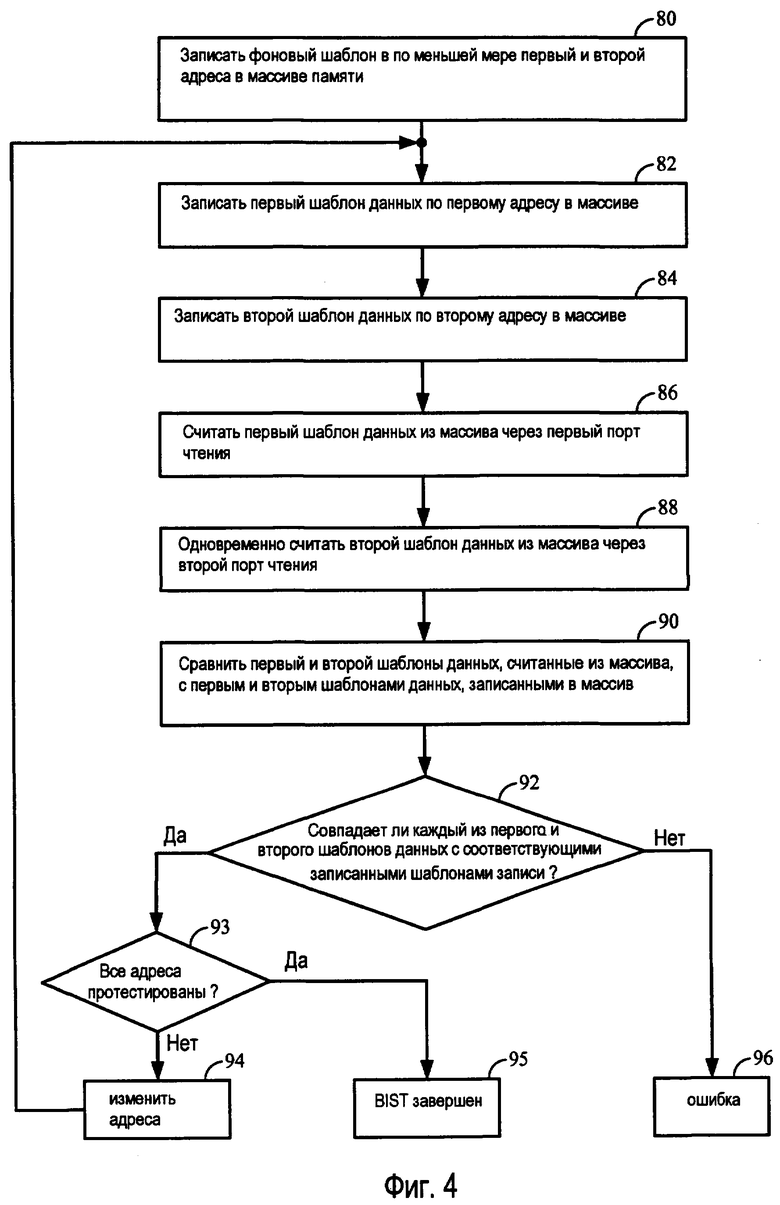

Фиг.4 - последовательность операций способа BIST для массива памяти путем одновременного считывания тестовых шаблонов через два или более порта чтения.

Подробное описание

На фиг.1 показана функциональная блок-схема процессора 10. Процессор 10 выполняет команды в конвейере 12 выполнения команд согласно логике управления 14. Конвейер 12 может иметь суперскалярную структуру, имеющую несколько параллельных конвейеров, например, 12a и 12b. Конвейеры 12a, 12b включают в себя различные регистры или защелки 16, организованные в каскады конвейера, и одно или несколько арифметико-логических устройств (АЛУ) 18. Массив памяти 20 обеспечивает множество ячеек памяти, которые отображаются в логические регистры общего назначения (РОН).

Конвейеры 12a, 12b извлекают команды из командного кэша (I-кэш) 22, при этом управление адресацией памяти и правами доступа осуществляется буфером предыстории трансляций на стороне команд (ITLB) 24. Доступ к данным осуществляется из кэша данных (D-кэш) 26, при этом управление адресацией памяти и правами доступа осуществляется главным буфером предыстории трансляций (TLB) 28. В различных вариантах осуществления ITLB может содержать копию части TLB. Альтернативно, ITLB и TLB могут быть объединены. Аналогично, в различных вариантах осуществления процессора 10, I-кэш 22 и D-кэш 26 могут быть объединены или интегрированы. Промахи в I-кэше 22 и/или D-кэше 26 обуславливают обращение к главной (внекристальной) памяти 32, под управлением интерфейса 30 памяти. Процессор 10 может включать в себя интерфейс ввода/вывода 34, управляющий доступом к различным периферийным устройствам 36. Специалистам в данной области техники очевидно, что возможны многочисленные разновидности процессора 10. Например, процессор 10 может включать в себя кэш второго уровня (L2) для любого из I- и D-кэшей или обоих. Кроме того, один или несколько функциональных блоков, показанных в процессоре 10, может быть исключен из конкретного варианта осуществления.

На фиг.2 показан многопортовый массив памяти 20, реализующий набор логических РОН, и контроллер встроенного самотестирования (BIST) 40. Массив памяти 20 организован в виде 16 ячеек по 128 битов, хотя раскрытые здесь способ и устройство тестирования применимы к любой конфигурации многопортовой памяти. Каждая 128-битовая ячейка в массиве памяти 20 является пословно считываемой, и массив 20 логически и физически сегментирован по границам слова (32 бита). Совместно используемая схема предварительной зарядки и распределения питания располагается ниже центра массива памяти 20.

Конкретный массив памяти 20, показанный на фиг.2, включает в себя три порта записи 42 и пять портов чтения 44, при этом три порта чтения 44 расположены на одной стороне массива памяти 20, и два порта чтения 44 расположены на другой стороне. Это лишь иллюстративная конфигурация. Три порта чтения 44, обозначенные A, B и C, подключены к селекторной схеме 46, например мультиплексору. Контроллер BIST 20 предписывает селектору 46 посредством сигнала управления 56 направлять данные, считанные из массива памяти 20 через один из портов чтения 44 A, B или C, на вход данных компаратора 48. Контроллер BIST дополнительно выдает шаблоны данных на вход сравнения компаратора 48 по сигнальной линии 58. Данные, считанные через порты чтения 44 D и E, аналогично направляются через селектор 50 на второй компаратор 52, при этом контроллер BIST 40 управляет селектором 50 и выдает данные сравнения на компаратор 52. Выходы компараторов 48, 52 поступают на контроллер BIST 40 по сигнальным линиям 60.

В режиме тестирования контроллер BIST 40 записывает фоновый шаблон данных в массив памяти 20 через порты записи 42 A, B и/или C. Затем контроллер BIST 40 записывает тестовые шаблоны данных в одну или несколько ячеек памяти массива памяти 20 через порты записи 42 A, B и/или C. В по меньшей мере некоторых тестах контроллер BIST 40 записывает тестовые шаблоны данных через все три порта записи 40 одновременно для выявления электрических предельных состояний в массиве памяти 20, которые могут не проявляться при записи данных через только один порт записи 42 единовременно.

Затем контроллер BIST 40 считывает одновременно тестовые шаблоны данных из массива памяти 20 через по меньшей мере два порта чтения 44. Для максимального нагружения массива памяти 20 и выявления любых латентных электрических предельных состояний, и дополнительно для минимизации времени тестирования, контроллер BIST 40 одновременно считывает данные через все доступные порты чтения 44 (то есть все пять портов чтения 44 согласно варианту осуществления, показанному на фиг.2). Затем контроллер BIST 40 последовательно направляет данные из каждого порта чтения 44 на компаратор 48, 52, одновременно подавая на компаратор 48, 52 соответствующий предполагаемый шаблон данных, и исследует выходной сигнал компаратора 48, 52, чтобы удостовериться в том, что из массива памяти 20 считан правильный шаблон данных. Поскольку контроллер BIST 40 располагается на компоненте процессора 10, все тестирование осуществляется "на скорости", то есть на рабочей частоте процессора 10.

Согласно варианту осуществления, показанному на фиг.2, в одном тесте контроллер BIST 40 максимально нагружает массив памяти 20 и минимизирует время тестирования путем одновременного считывания тестовых шаблонов через все пять портов 44 чтения. Затем данные из портов 44 A и D чтения одновременно направляются на соответствующий компаратор 48, 52, обеспечиваются соответствующие шаблоны сравнения, и выходные сигналы компаратора проверяются. В следующем цикле данные из портов чтения 44 B и E одновременно проверяются. Наконец, данные из порта чтения 44 C проверяются на компараторе 48. Одновременное считывание данных из массива памяти 20 через все пять портов чтения 44 нагружает массив памяти 20 для выявления латентных электрических предельных состояний. Использование двух компараторов 48, 52 для одновременной проверки данных чтения из двух портов чтения 44 минимизирует время тестирования.

Специалистам в данной области техники очевидно, что количество компараторов 48, 52 можно увеличить, чтобы еще больше сократить время тестирования за счет параллельного осуществления сравнения данных. Время тестирования можно минимизировать, обеспечив компаратор 48, 52 для каждого порта чтения 44 (очевидно, необходим селектор 46, 50). Однако при этом увеличивается площадь кремния, и может происходить перегрузка записи для схем тестирования, которые неактивны в ходе нормальной работы процессора. В другом предельном случае можно обеспечить один компаратор 48, 50, при этом данные из всех портов чтения 44 поступают на него через один селектор 46, 50. Это позволяет минимизировать схему тестирования, но при этом налагается ограничение снизу на длительность тестирования, поскольку каждое слово в массиве памяти 20 нужно сравнивать последовательно. Однако, даже с одним компаратором 48, 52, массив памяти 20 можно тестировать более тщательно и реалистически, чем позволяют методы тестирования согласно уровню техники, благодаря одновременному считыванию данных через два или более (и вплоть до всех возможных) порта чтения 44.

Раскрытые здесь устройство и способ тестирования дополнительно позволяют осуществлять более детальную диагностику, чем системы тестирования, отвечающие уровню техники, многие из которых ограничиваются минимальным тестом работоспособности (то есть определением годен/не годен). Контроллер BIST 40 может минимизировать время тестирования путем одновременной записи тестовых шаблонов данных в три разные ячейки памяти через три порта записи 42 и одновременного считывания данных из пяти разных ячеек памяти через пять портов чтения 44. Альтернативно, контроллер BIST 40 может нагружать отдельные ячейки памяти (и соответствующие схемы ввода/вывода) путем записи данных и/или чтения данных в/из одну/ой ячейку/и памяти с использованием всех доступных соответствующих портов.

Способ тестирования полностью применим к любому массиву памяти, имеющему два или более порта записи 42 и/или два или более порта чтения 44. На фиг.3 показан способ BIST для массива памяти, имеющего по меньшей мере два порта записи 42, независимо от количества портов чтения 44 или компараторов 48, 52. Фоновый шаблон записывается в по меньшей мере первый и второй адреса в массив памяти 20 через один или несколько портов записи (этап 60). Первый шаблон данных записывается по первому адресу в массив 20 через первый порт записи 42 (этап 62). Одновременно второй шаблон данных записывается по второму адресу в массив 20 через второй порт записи 42 (этап 64). Первый и второй шаблоны данных могут быть одинаковыми или разными. Аналогично, первый и второй адреса могут указывать соседние или далеко разнесенные ячейки памяти. Первый и второй шаблоны данных считываются из массива 20 (этап 66). При наличии нескольких портов чтения 44 операции чтения данных можно осуществлять одновременно; альтернативно, операции чтения можно осуществлять последовательно с использованием одного порта чтения 44. Каждый из первого и второго шаблонов данных, считанных из массива 20, сравнивается с соответствующим шаблоном данных, записанным в массив 20 (этап 68). Если шаблоны данных совпадают (этап 70) и не все адреса протестированы (этап 71), адреса изменяются (этап 72), и тестирование продолжается. Если шаблоны данных совпадают (этап 70) и все адреса протестированы (этап 71), BIST завершается (этап 73). Если шаблоны данных не совпадают (этап 70), обозначается ошибка (этап 74), что может указывать на необходимость дополнительного тестирования или на дефект массива памяти 20 и/или соответствующего порта записи 42 и/или порта(ов) чтения 44.

На фиг.4 показан способ BIST для массива памяти, имеющего по меньшей мере два порта чтения 44, независимо от количества портов записи 42 или компараторов 48, 52. Фоновый шаблон предпочтительно записывается в по меньшей мере первый и второй адреса в массив памяти 20 (этап 80). Первый шаблон данных записывается по первому адресу в массив 20 (этап 82), и второй шаблон данных записывается по второму адресу в массив 20 (этап 84). При наличии нескольких портов записи 42 первый и второй шаблоны данных можно записывать одновременно; в противном случае их можно записывать последовательно через один порт записи 42. Первый и второй шаблоны данных могут быть одинаковыми или разными, и первый и второй адреса могут быть соседними или далеко разнесенными. Первый шаблон данных считывается из массива 20 через первый порт чтения 44 (этап 86). Одновременно второй шаблон данных считывается из массива 20 через второй порт чтения 44 (этап 88). Каждый из первого и второго шаблонов данных, считанных из массива 20, сравнивается с соответствующим шаблоном данных, записанным в массив 20 (этап 90). При наличии более одного компаратора сравнения можно осуществлять параллельно; альтернативно, их можно осуществлять последовательно. Если шаблоны данных совпадают (этап 92) и не все адреса протестированы (этап 93), адреса изменяются (этап 94), и тестирование продолжается. Если шаблоны данных совпадают (этап 92) и все адреса протестированы (этап 93), BIST завершается (этап 95). Если шаблоны данных не совпадают (этап 92), обозначается ошибка (этап 96).

Согласно фиг.2 компараторные схемы 48, 52 содержат статические логические вентили. Таким образом, компаратор 48, 52 будет сравнивать любой шаблон данных, поступающий на его вход данных, с данными, поступающими на его вход сравнения, и будет генерировать сигнал, указывающий, совпадают ли шаблоны данных. В ходе нормальной работы процессора (то есть не в режиме тестирования) данные, выводимые через порты чтения 44, будут постоянно изменяться. Если по меньшей мере один порт чтения 44 подключен к входу данных компаратора 48, 52 через селектор 46, 50, логические вентили в компараторе 48, 52 будут постоянно переключаться, потребляя энергию, вырабатывая тепло и внося свой вклад в электрический шум на шинах питания и заземления.

Соответственно, компараторные схемы 48, 50 эффективно отключаются в ходе нормальной работы, когда определено, что на входе данных компаратора 48, 52 присутствует постоянный шаблон данных. Один вход каждого селектора 46, 50 подключен к постоянному шаблону данных, например заземлению (как показано на фиг.2), хотя можно использовать любой шаблон данных. После перезапуска системы (или в соответствии с любым другим указателем режима нормальной работы процессора) контроллер BIST 40 предписывает селектору 46, 52 выбрать фиксированный шаблон данных. В результате статический шаблон данных поступает на вход данных компараторов 48, 52. Контроллер BIST 40 может в необязательном порядке подавать соответствующий статический шаблон данных на вход сравнения компараторов 48, 52. Вне зависимости от того, указывает ли выход компаратора 48, 52 совпадение или несовпадение данных, поскольку входные сигналы являются статическими, вентили компаратора 48, 52 не будут переключаться после начального одноциклового сравнения.

Многочисленные латентные электрические предельные состояния можно выявлять путем одновременной записи шаблонов данных через два или более порта записи 42 и/или путем одновременного считывания шаблонов данных через два или более порта чтения 44. Способы тестирования, отвечающие уровню техники, совершенно неспособны выявлять эти предельные состояния. При одновременной записи шаблонов данных через два или более порта записи 42 одновременно запускается несколько драйверов записи. Это нагружает электросеть, что позволяет выявлять предельные состояния. Кроме того, можно выявлять шумовую связь между "тихой" и "переключающейся" разрядными шинами.

Одновременное считывание шаблонов данных через два или более порта чтения 44 позволяет выявлять предельные состояния электросети благодаря одновременному включению множества предварительных зарядных устройств. Аналогично, множество разрядных шин чтения разряжаются одновременно, что также позволяет выявлять предельные состояния электросети. Предельные состояния электросети также можно выявлять, одновременно включая множественные глобальные и/или локальные числовые шины. Шумовую связь между "тихой" и "переключающейся" разрядными шинами можно выявлять, одновременно разряжая несколько разрядных шин чтения. Кроме того, несколько выходов защелок данных чтения переключаются одновременно, обуславливая связь на длинных неэкранированных цепях. Этот шум приводит к удалению задержки, которое позволяет выявлять предельные состояния шума и/или тактирования.

Хотя настоящее раскрытие описано здесь в отношении конкретных признаков, аспектов и вариантов осуществления изобретения, очевидно, что многочисленные вариации, модификации и другие варианты осуществления допустимы в широком объеме настоящего раскрытия, и, соответственно, все вариации, модификации и варианты осуществления следует рассматривать как соответствующие объему раскрытия. Поэтому настоящие варианты осуществления следует рассматривать во всех отношениях как иллюстративные и неограничительные, и допустимы любые изменения, происходящие в рамках смысла и объема эквивалентности прилагаемой формулы изобретения.

Представленное изобретение относится к способу тестирования многопортовых массивов памяти на рабочей частоте. Техническим результатом является сокращение времени тестирования массивов памяти. Способ тестирования массива памяти включает, во время режима теста: одновременную запись первого шаблона данных по первому адресу в массив памяти через первый порт записи и второго шаблона данных по второму адресу в массив памяти через второй порт записи, причем первый шаблон данных отличается от второго шаблона данных, считывание первого и второго шаблонов данных из массива памяти через, по меньшей мере, первый порт считывания, и одновременное сравнение первого шаблона данных, считанного из массива памяти, с первым шаблоном данных, записанным в массив памяти, на первом компараторе и сравнение второго шаблона данных, считанного из массива памяти, со вторым шаблоном данных, записанным в массив памяти, на втором компараторе, который является отличным от первого компаратора, не в режиме теста: прием постоянного шаблона данных на вход данных первого компаратора. 3 н. и 17 з.п. ф-лы, 4 ил.

1. Способ тестирования массива памяти, имеющего множество портов записи, в процессоре, содержащий этапы, на которых

во время режима теста:

одновременно записывают первый шаблон данных по первому адресу в массив памяти через первый порт записи и второй шаблон данных по второму адресу в массив памяти через второй порт записи, причем первый шаблон данных отличается от второго шаблона данных,

считывают первый и второй шаблоны данных из массива памяти через по меньшей мере первый порт считывания, и

одновременно сравнивают первый шаблон данных, считанный из массива памяти, с первым шаблоном данных, записанным в массив памяти, на первом компараторе и сравнивают второй шаблон данных, считанный из массива памяти, со вторым шаблоном данных, записанным в массив памяти, на втором компараторе, который является отличным от первого компаратора,

не в режиме теста:

принимают постоянный шаблон данных на вход данных первого компаратора.

2. Способ по п.1, дополнительно содержащий этап, на котором записывают фоновый шаблон данных по первому адресу в массив памяти до записи первого шаблона данных.

3. Способ по п.1, в котором постоянный шаблон данных является сигналом заземления.

4. Способ по п.1, дополнительно содержащий во время режима теста этап одновременного считывания первого шаблона данных и второго шаблона данных из массива памяти через первый порт считывания и второй порт считывания, соответственно.

5. Способ по п.1, в котором логические вентили схемы компаратора в первом компараторе не переключаются после сравнения постоянного шаблона данных и шаблона данных, принятого на входе сравнения первого компаратора.

6. Способ по п.1, дополнительно содержащий прием не в режиме теста постоянного шаблона данных на входе данных второго компаратора.

7. Способ по п.6, дополнительно содержащий запись фонового шаблона данных по второму адресу в массиве памяти до записи второго шаблона данных.

8. Способ по п.6, в котором постоянный шаблон данных, принятый на входе данных второго компаратора, является сигналом заземления.

9. Способ по п.6, в котором логические вентили схемы компаратора во втором компараторе не переключаются после сравнения постоянного шаблона данных и второго шаблона данных, принятого на входе сравнения второго компаратора.

10. Способ по п.1, дополнительно содержащий прием первого шаблона данных, считанного из массива памяти на схему первого селектора, для избирательной передачи считанного первого шаблона данных на первый компаратор.

11. Способ по п.10, дополнительно содержащий прием второго шаблона данных, считанного из массива памяти на схему второго селектора, для избирательной передачи считанного второго шаблона данных на второй компаратор.

12. Процессор, содержащий

массив памяти,

первый порт записи, сконфигурированный передавать в режиме теста первый шаблон данных в массив памяти,

второй порт записи, сконфигурированный передавать в режиме теста второй шаблон данных в массив памяти, причем первый шаблон данных отличается от второго шаблона данных,

первый порт считывания, сконфигурированный передавать в режиме теста первый шаблон данных из массива памяти,

второй порт считывания, сконфигурированный передавать в режиме теста второй шаблон данных из массива памяти,

первый компаратор, сконфигурированный сравнивать в режиме теста первый шаблон данных, переданный в массив памяти первым портом записи, с первым шаблоном данных, переданным из массива памяти первым портом считывания, и

второй компаратор, отличный от первого компаратора, сконфигурированный сравнивать второй шаблон данных, переданный в массив памяти вторым портом записи, со вторым шаблоном данных, переданным из массива памяти вторым портом считывания, во время режима теста,

причем сравнение первого шаблона данных, считанного из массива памяти, с первым шаблоном данных, записанным в массив памяти, и сравнение второго шаблона данных, считанного из массива памяти, со вторым шаблоном данных, записанным в массив памяти, имеют место одновременно,

при этом не в режиме теста первый компаратор сконфигурирован принимать постоянный шаблон данных на входе данных.

13. Процессор по п.12, в котором в режиме теста первый компаратор сконфигурирован принимать первый шаблон данных на входе данных.

14. Процессор по п.12, в котором логические вентили схемы компаратора в первом компараторе не переключаются после сравнения постоянного шаблона данных и шаблона данных, принятого на входе сравнения первого компаратора.

15. Процессор по п.12, в котором постоянный шаблон данных ассоциирован с сигналом заземления.

16. Процессор по п.13, в котором второй компаратор сконфигурирован принимать в режиме теста второй шаблон данных, переданный из массива памяти, и сконфигурирован принимать не в режиме теста второй постоянный шаблон данных на входе данных второго компаратора.

17. Процессор по п.16, в котором логические вентили схемы компаратора во втором компараторе не переключаются после сравнения второго постоянного шаблона данных и второго шаблона данных, принятого на входе сравнения второго компаратора.

18. Процессор по п.12, дополнительно содержащий

схему первого селектора, сконфигурированную принимать во время режима теста первый шаблон данных, переданный из массива памяти, и избирательно направлять упомянутый первый шаблон данных, переданный из массива памяти, на первый компаратор, и

схему второго селектора, сконфигурированную принимать во время режима теста второй шаблон данных, переданный из массива памяти, и избирательно направлять упомянутый второй шаблон данных, переданный из массива памяти, на второй компаратор.

19. Процессор по п.18, в котором каждая из схемы первого селектора и схемы второго селектора является мультиплексором.

20. Процессор, содержащий

массив памяти, подсоединенный к контроллеру,

по меньшей мере один порт записи, сконфигурированный передавать в режиме теста первый шаблон данных и второй шаблон данных в массив памяти,

первый порт считывания, сконфигурированный передавать в режиме теста первый шаблон данных из массива памяти,

второй порт считывания, отличный от первого порта считывания, сконфигурированный передавать в режиме теста второй шаблон данных из массива памяти, причем первый шаблон данных и второй шаблон данных одновременно передаются из массива памяти, причем первый шаблон данных отличается от второго шаблона данных,

схему первого селектора, реагирующую на контроллер и сконфигурированную принимать во время режима теста первый шаблон данных, переданный из массива памяти, и избирательно направлять упомянутый первый шаблон данных, переданный из массива памяти, на первый компаратор, и

схему второго селектора, реагирующую на контроллер и сконфигурированную принимать во время режима теста второй шаблон данных, переданный из массива памяти, и избирательно направлять упомянутый второй шаблон данных, переданный из массива памяти, на второй компаратор, который отличается от первого компаратора,

причем первый компаратор сконфигурирован сравнивать в режиме теста первый шаблон данных, переданный в массив памяти первым портом записи, с первым шаблоном данных, переданным из массива памяти первым портом считывания через первую схему селектора, и

причем второй компаратор сконфигурирован сравнивать в режиме теста второй шаблон данных, переданный в массив памяти вторым портом записи, со вторым шаблоном данных, переданным из массива памяти вторым портом считывания, через вторую схему селектора, при этом сравнения на первом компараторе и втором компараторе выполняются одновременно,

при этом не в режиме теста каждый из первого компаратора и второго компаратора сконфигурирован принимать постоянный шаблон данных на соответствующем входе данных.

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| US 6681358 B1, 20.01.2004 | |||

| US 5912850 A, 15.06.1999 | |||

| US 6442717 В1, 27.08.2002 | |||

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 6671842 B1, 30.12.2003. | |||

Авторы

Даты

2010-12-27—Публикация

2007-03-01—Подача