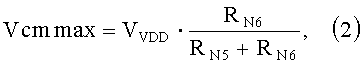

Настоящее изобретение относится к интегральной электронной технике и может быть использовано в составе высокочастотных устройств тактовой синхронизации цифровых схем. Генератор, управляемый напряжением (ГУН), преимущественно используется в системах фазовой автоподстройки частоты (ФАПЧ, фиг.1), выполняющих функцию синтезатора частот, синхронизации микросхем, фильтра шумов в тактовых сигналах. Система ФАПЧ, на вход которой поступает опорный сигнал Vref, состоит из фазового детектора 101, фильтра нижних частот (ФНЧ) 102, ГУН 103, делителя частоты в цепи обратной связи (ДЧ) 104. В системах на кристалле наибольшее распространение получили кольцевые генераторы ввиду малости занимаемой площади и приемлемой стабильности. ГУН, используемые в ФАПЧ общего назначения, должны отвечать следующим требованиям:

- для обеспечения возможности синтезирования непрерывной сетки частот в ФАПЧ с целочисленным ДЧ диапазон рабочих частот ГУН должен перекрываться по меньшей мере в 2 раза при всех рабочих условиях;

- для корректного расчета номиналов компонентов ФНЧ функция передачи цепи ФАПЧ, а следовательно, и функция передачи ГУН, должна минимально варьироваться при изменении рабочей частоты;

- для генерации более плотной сетки частот при помощи выходных делителей при заданной входной частоте в ФАПЧ с целочисленным ДЧ необходимо использование ГУН с более высокой максимальной частотой, при этом важно ограничить потребляемую мощность.

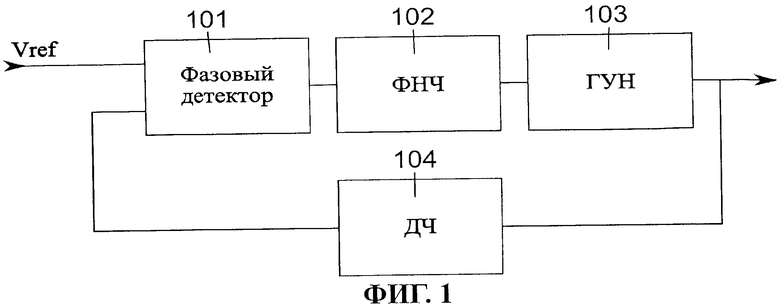

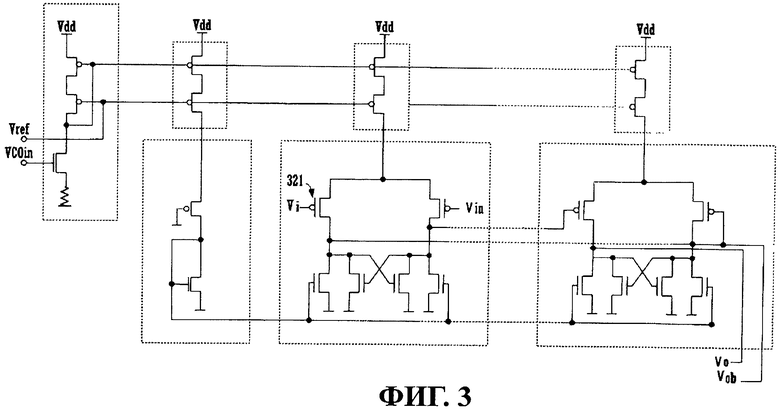

Известны схемы кольцевых КМОП ГУН, описанные в патентах США №5239274 «Voltage-controlled ring oscillator using complementary differential buffers for generating multiple phase signals», МПК H03B 27/00; H03B 5/20 [1], №6104254 «VCO in CMOS technology having operating frequency of 1GHz and greater», МПК Н03К 3/00 [2]. Общим признаком с заявляемым изобретением является наличие N (N - целое, больше единицы) дифференциальных инверторов с двумя входами (положительным и отрицательным) и двумя выходами (отрицательным и положительным), соединенными в кольцо так, что отрицательный выход каждого инвертора идет на положительный вход следующего инвертора во всех соседних парах инверторов в случае нечетного числа инверторов N, и во всех парах инверторов, кроме одной выделенной, в случае четного числа инверторов N, при этом в единственной выделенной паре соседних инверторов отрицательный выход первого инвертора идет на отрицательный вход следующего инвертора, а положительный выход первого инвертора - на положительный вход следующего инвертора. Частота колебаний определяется количеством инверторов в кольце и задержкой переключения каждого из них. Задержка переключения определяется величиной тока переключения и величиной, эквивалентной емкости нагрузки. Управление величиной тока переключения осуществляется во всех инверторах генератора одновременно. Схема инвертора [1] представлена на фиг.2, схема инвертора [2] представлена на фиг.3.

Данные схемы генераторов имеют следующие недостатки. В [1] необходимо дополнительно формировать напряжение смещения для р-канальных транзисторов. Время переключения инверторов ограничено р-канальными транзисторами, что понижает максимальную частоту генератора. Кроме того, функция передачи ГУН распределена неравномерно по диапазону управляющих напряжений, имея ярко выраженный максимум в области порогового напряжения n-канального транзистора. В [2] активным является р-канальный транзистор, а n-канальный используется в качестве нагрузки, что снижает максимальную частоту.

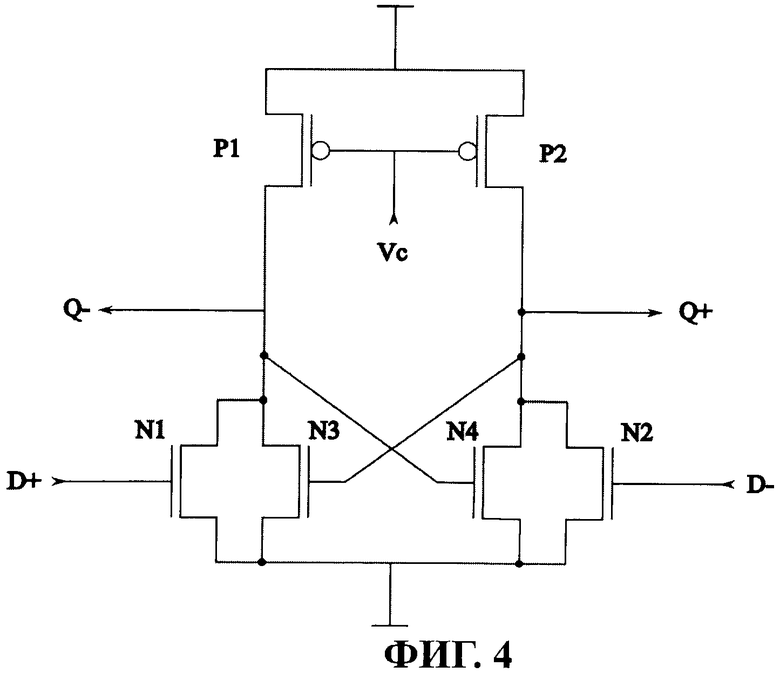

Наиболее близким техническим решением к заявляемому изобретению является схема кольцевого КМОП ГУН, основанная на дифференциальных инверторах, изображенных на фиг.4 (Fei Yuan. CMOS Current-Mode Circuits for Data Communications / Fei Yuan. - New York: Springer, 2007. - с.184-185 [3]). Эта схема выбрана в качестве прототипа заявляемого изобретения. Каждый дифференциальный инвертор ГУН [3] содержит р-канальные транзисторы Р1 и Р2 и n-канальные транзисторы N1, N2, N3 и N4, затвор транзистора N1 является первым (положительным) входом инвертора D+, затвор транзистора N2 является вторым (отрицательным) входом инвертора D-, стоки транзисторов N1 и N3 и сток транзистора Р1 соединены с затвором транзистора N4 и образуют первый (отрицательный) выход инвертора Q-, стоки транзисторов N2 и N4 и сток транзистора Р2 соединены с затвором транзистора N3 и образуют второй (положительный) выход инвертора Q+, истоки обоих р-канальных транзисторов подключены к линии VDD напряжения питания, истоки всех n-канальных транзисторов подключены к линии земли GND, на затворы транзисторов Р1 и Р2 подается управляющее напряжение. Недостатком данной схемы является то, что частота ГУН, составленного из таких дифференциальных инверторов, не изменяется при управляющем напряжении, большем, чем разница между напряжением питания и пороговым напряжением р-канального транзистора, поскольку в этом состоянии р-канальные транзисторы Р1 и Р2 закрыты. В остальном диапазоне управляющих напряжений функция передачи ГУН (крутизна) сильно зависит от управляющего напряжения, что затрудняет расчет элементов устройств, содержащих данный ГУН.

Основной задачей данного изобретения является повышение линейности модуляционной характеристики ГУН, что позволяет расширить диапазон его рабочих частот и проектировать ФАПЧ с более предсказуемыми характеристиками. Техническим результатом настоящего изобретения является создание КМОП ГУН, имеющего перекрытие частот в четыре раза, обладающего функцией передачи, изменяющейся не более, чем в два раза во всем диапазоне управляющих напряжений и рабочих температур.

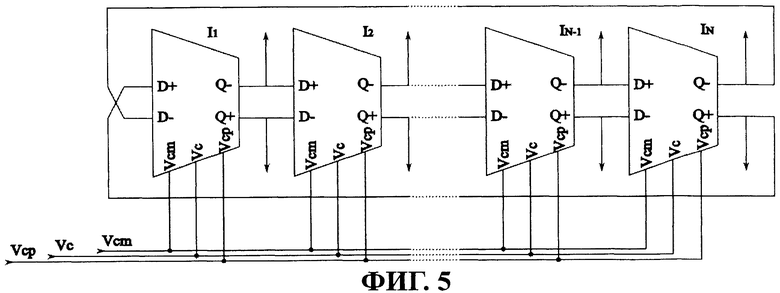

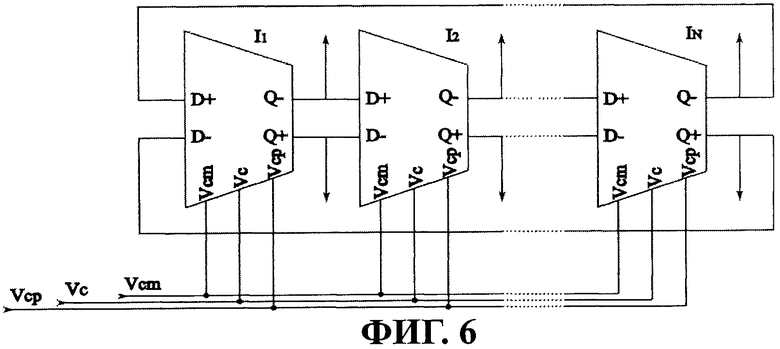

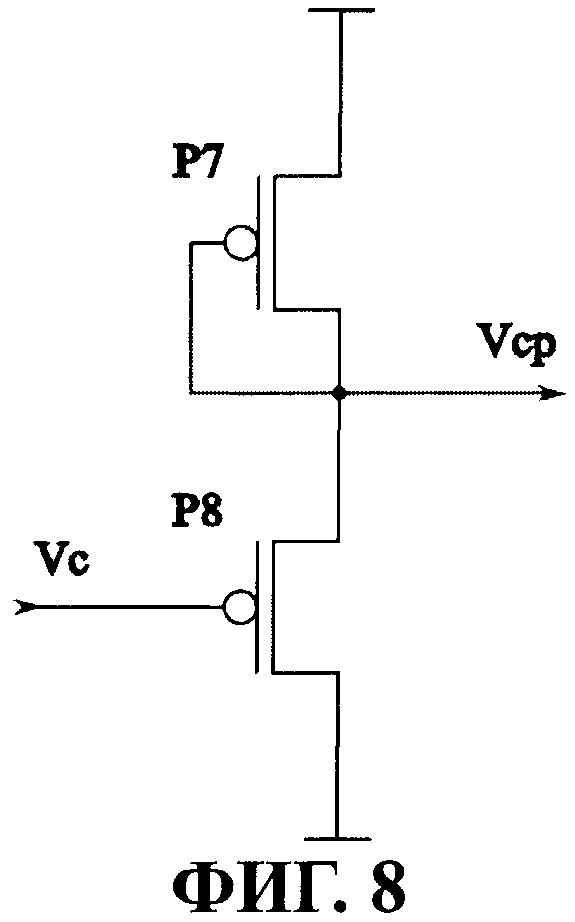

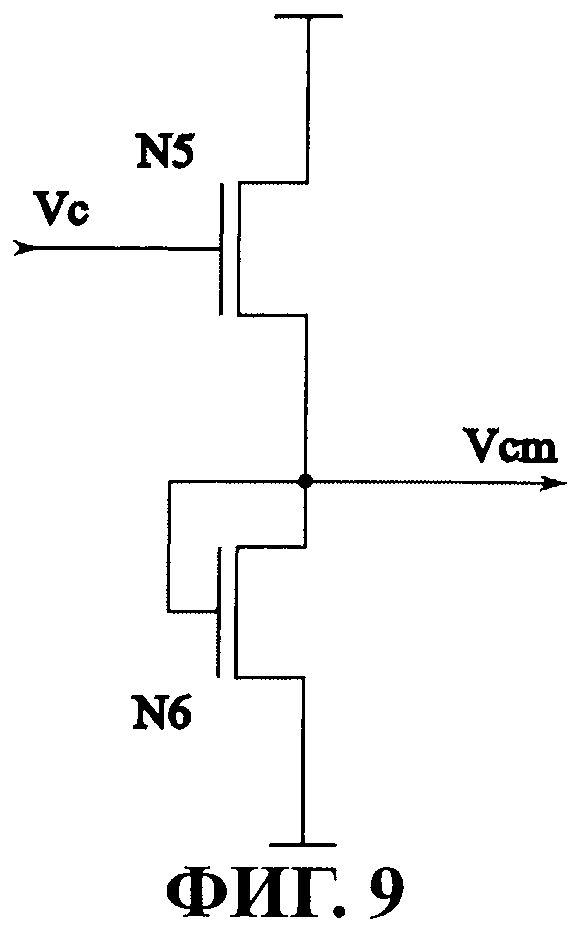

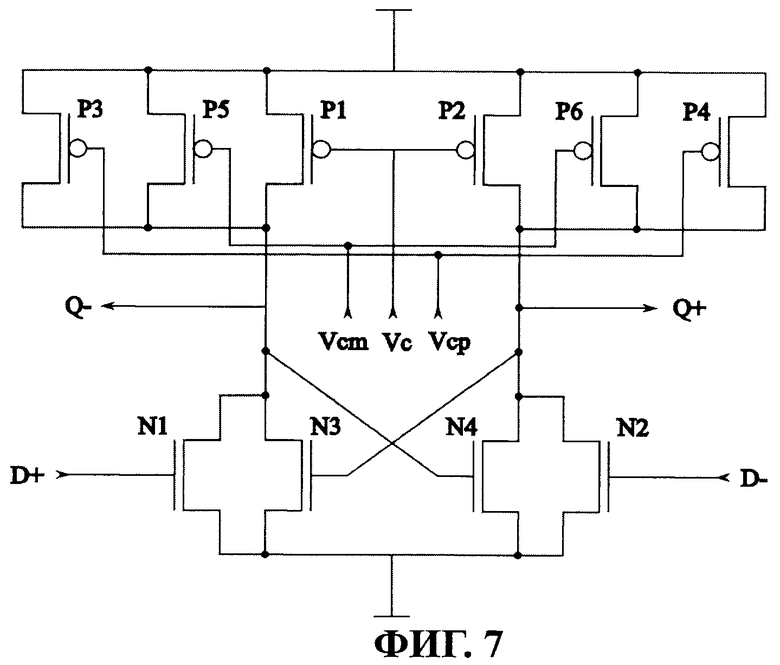

Заявляемый генератор состоит из N дифференциальных инверторов I1, I2.. IN (фиг.5,6 для четного и нечетного числа N, соответственно), скорость переключения которых управляется изменением нагрузки в виде полуоткрытых р-канальных транзисторов. Дифференциальный инвертор (фиг.7) отличается от инвертора, описанного в [3], тем, что параллельно транзистору Р1 подключены транзисторы Р3 и Р5, а параллельно транзистору Р2 подключены транзисторы Р4 и Р6 так, что стоки транзисторов N1 и N3 и стоки транзисторов Р1, Р3, Р5 соединены с затвором транзистора N4 и образуют выход Q-инвертора, стоки транзисторов N2 и N4 и стоки транзисторов Р2, Р4, Р6 соединены с затвором транзистора N3 и образуют выход Q-инвертора, истоки транзисторов Р1, Р3, Р5, Р2, Р4 и Р6 подключены к линии VDD напряжения питания, истоки транзисторов N1, N2, N3 и N4 подключены к линии земли GND, на затворы транзисторов Р1 и Р2 подается основное управляющее напряжение Vc, сформированное на ФНЧ, на затворы транзисторов Р3 и Р4 подается управляющее напряжение Vcp, сформированное из основного управляющего напряжения при помощи цепи 1 (фиг.8), на затворы транзисторов Р5 и Р6 подается управляющее напряжение Vcm, сформированное из основного управляющего напряжения при помощи цепи 2 (фиг.9). Цепь 1 состоит из транзисторов Р7 и Р8, исток транзистора Р7 соединен с линией VDD напряжения питания, затвор и сток транзистора Р7, а также исток транзистора Р8 объединены и образуют линию управляющего напряжения Vcp, сток транзистора Р8 подключен к линии земли GND, затвор транзистора Р8 подключен к линии управляющего напряжения Vc. Цепь 2 состоит из транзисторов N5 и N6, сток транзистора N5 соединен с линией VDD напряжения питания, затвор транзистора N5 подключен к линии управляющего напряжения Vc, затвор и сток транзистора N6, а также исток транзистора N5 объединены и образуют линию управляющего напряжения Vcm, исток транзистора N6 подключен к линии земли GND.

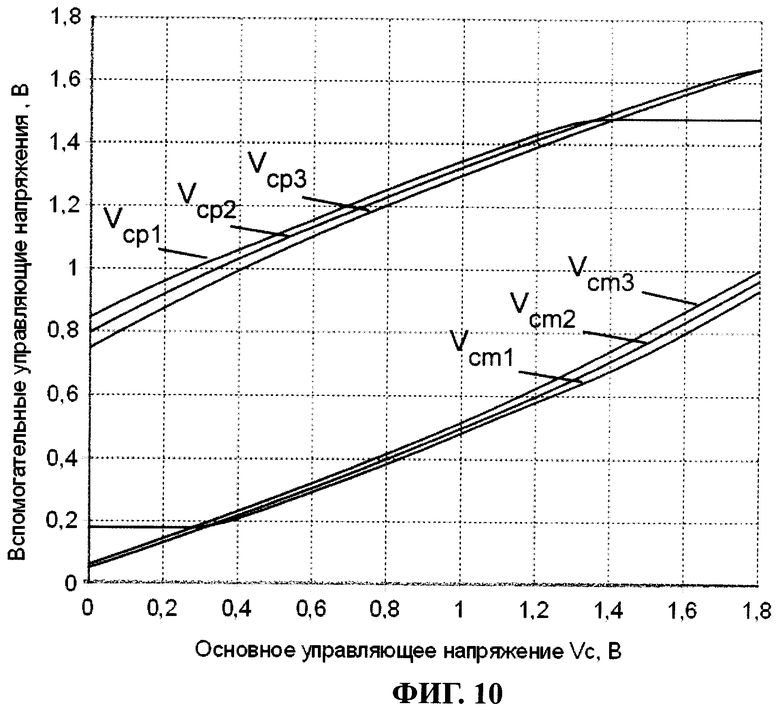

Указанное перекрытие частот и равномерность функции передачи осуществляется за счет того, что каждому активному n-канальному транзистору соответствуют три нагрузочных р-канальных транзистора, на затворы которых подаются различные управляющие напряжения: основное управляющее напряжение Vc и два дополнительных управляющих напряжения, формирующиеся из основного с помощью цепей формирования 1 и 2: Vcp и Vcm. Графики зависимостей вспомогательных управляющих напряжений от основного при трех различных температурах представлены на фиг.10. Наличие трех управляющих напряжений обеспечивает равномерное изменение сопротивления цепи, состоящей из параллельно включенных нагрузочных р-канальных транзисторов. Каждый транзистор в отдельности имеет максимальную скорость уменьшения сопротивления при напряжении на затворе, близком к пороговому напряжению, т.е. при различных значениях основного управляющего напряжения Vc. Благодаря их параллельному включению функция зависимости производной суммарного сопротивления по управляющему напряжению имеет менее ярко выраженные максимумы, что обеспечивает более постоянную функцию передачи ГУН, чем в [3].

Заявляемое изобретение иллюстрируется следующими графическими материалами:

Фиг.1. Базовая схема ФАПЧ, использующая кольцевой ГУН для генерации частоты.

Фиг.2. Схема дифференциального инвертора [1].

Фиг.3. Схема ГУН [2].

Фиг.4. Схема дифференциального инвертора [3].

Фиг.5. Схема ГУН, составленного из N дифференциальных инверторов и имеющего 2N выходов, смещенных по фазе друг относительно друга на фазовый угол π/N, где N - четное целое число, больше единицы.

Фиг.6. Схема ГУН, составленного из N дифференциальных инверторов и имеющего 2N выходов, смещенных по фазе друг относительно друга на фазовый угол π/N, где N - нечетное целое число, больше единицы.

Фиг.7. Схема дифференциального инвертора, скорость переключения которого управляется тремя напряжениями, заявленная в данном изобретении.

Фиг.8. Схема формирователя вспомогательного управляющего напряжения Vcp.

Фиг.9. Схема формирователя вспомогательного управляющего напряжения Vcm.

Фиг.10. График зависимости вспомогательных управляющих напряжений Vcp, Vcm от основного управляющего напряжения Vc, где

Vcp1, Vcp2, Vcp3 - зависимость Vcp от Vc при температурах -60°С, 27°С и 125°С, соответственно;

Vcm1, Vcm2, Vcm3 - зависимость Vcm от Vc при температурах -60°С, 27°С и 125°С, соответственно.

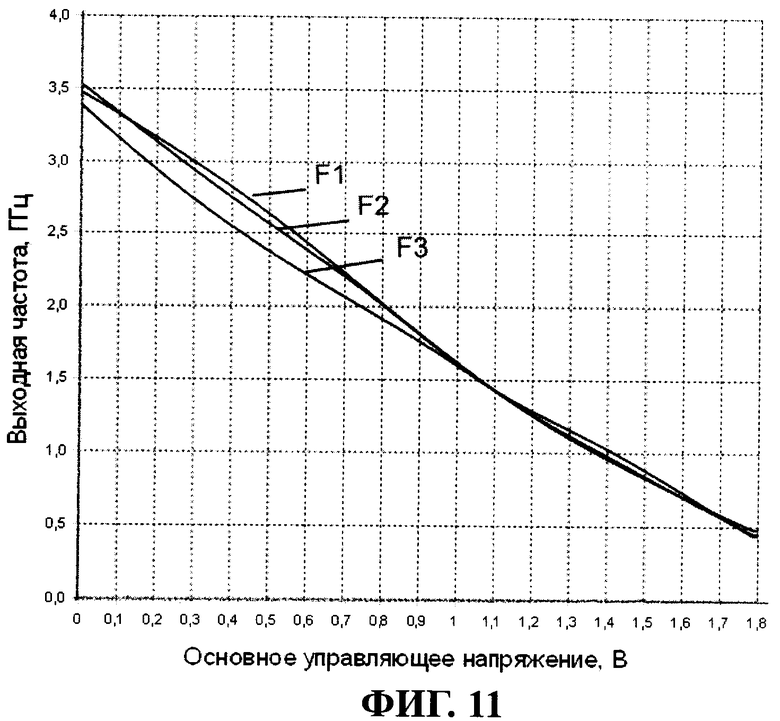

Фиг.11. Графики зависимости частоты ГУН F1, F2, F3 от управляющего напряжения Vc при температурах -60°С, 27°С и 125°С, соответственно.

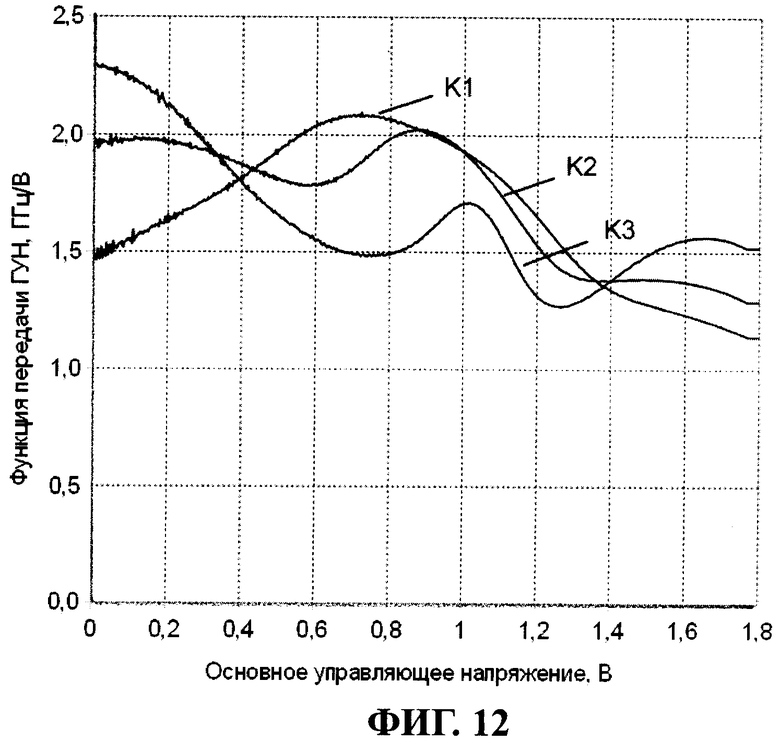

Фиг.12. Графики зависимости функции передачи ГУН K1, K2, К3 от управляющего напряжения Vc при температурах -60°С, 27°С и 125°С, соответственно.

Заявленное изобретение работает следующим образом. На вход ГУН подается основное управляющее напряжение Vc, находящееся в диапазоне от напряжения земли до напряжения питания. С помощью цепей формирования управляющих напряжений из него формируются два вспомогательных управляющих напряжения: Vcp и Vcm.

Рассмотрим цепь формирования напряжения Vcp (фиг.8). При Vc, равном напряжению линии земли VGND, транзистор Р8 открыт, Vcp принимает значение

где VVDD - напряжение питания;

RP7 - сопротивление полуоткрытого транзистора Р7;

RP8 - сопротивление открытого транзистора Р8.

При Vc, равном VVDD, транзистор Р8 закрыт. За счет того, что затвор транзистора Р7 соединен с его стоком, токи утечки через транзистор Р7 плавно поднимают напряжение Vcp практически до уровня напряжения питания. При Vc, лежащем между VGND и VVDD, напряжение Vcp устанавливается в промежуточное положение между значением Vcpmin (1) и VVDD, как показано на фиг.10.

Рассмотрим процесс формирования напряжения Vcm (фиг.9). При Vc, равном VVDD, транзистор N5 открыт, Vcm принимает значение

где RN5 - сопротивление открытого транзистора N5;

RN6 - сопротивление полуоткрытого транзистора N6.

При Vc, равном VGND, транзистор N5 закрыт. За счет того, что затвор транзистора N6 соединен с его стоком, токи утечки через транзистор N6 плавно опускают напряжение Vcm практически до уровня земли. При Vc в пределах от VGND до VVDD напряжение Vcm устанавливается в промежуточное положение между VGND и значением Vcmmax (2), как показано на фиг.10.

Управляющие напряжения Vc, Vcp, Vcm подаются на соответствующие входы всех дифференциальных инверторов генератора. Каждый из дифференциальных инверторов состоит из пары инверторов, работающих в противофазе и состоящих из транзисторов N1, N3, P1, Р3, Р5 и N2, N4, Р2, Р4, Р6. Допустим, вход D+ имеет уровень логической единицы, тогда вход D- имеет уровень логического нуля. Транзистор N1 открыт, и, поскольку в этом состоянии его сопротивление меньше, чем сопротивление цепи из параллельно соединенных транзисторов Р1, Р3, Р5, то на выходе Q-устанавливается уровень логического нуля. Транзистор N2 закрыт, параллельно включенный с ним транзистор N4 также закрыт, так как на его затвор подается напряжение с Q-, а как минимум один из транзисторов Р2, Р4 или Р6, в зависимости от величины основного управляющего напряжения Vc, находится в открытом или полуоткрытом состоянии, поэтому на выходе Q+ устанавливается напряжение логической единицы. Допустим теперь, что вход D+ имеет уровень логического нуля, тогда вход D- имеет уровень логической единицы. Транзистор N2 открыт, и, поскольку в этом состоянии его сопротивление меньше, чем сопротивление цепи из параллельно соединенных транзисторов Р2, Р4, Р6, то на выходе Q+ устанавливается уровень логического нуля. Транзистор N1 закрыт, параллельно включенный с ним транзистор N3 также закрыт, так как на его затвор подается напряжение с Q+, а как минимум один из транзисторов Р1, Р3 или Р5, в зависимости от величины основного управляющего напряжения Vc, находится в открытом или полуоткрытом состоянии, поэтому на выходе Q- устанавливается напряжение логической единицы.

Рассмотрим зависимость скорости переключения инвертора от значения основного управляющего напряжения Vc. При Vc, равном VGND, транзисторы Р1, Р2, Р5, Р6 находятся в открытом состоянии, транзисторы Р3, Р4 находятся в полуоткрытом состоянии. За счет этого скорость нарастания сигнала в точках Q- и Q+ максимальна, что соответствует максимальной скорости переключения инвертора. При Vc, равном VVDD, транзисторы Р1, Р2, Р3, Р4 находятся в закрытом состоянии, транзисторы Р5, Р6 находятся в полуоткрытом состоянии. При таком значении управляющего напряжения скорость нарастания сигнала в точках Q- и Q+ минимальна, что соответствует минимальной скорости переключения инвертора. При Vc, лежащем в пределах от VGND до VVDD, скорость переключения инвертора устанавливается в промежуточное состояние.

Транзисторы N3 и N4 используются для увеличения скорости переключения инвертора. Если в течение какого-то промежутка времени напряжение в точке Q- нарастает от уровня земли до уровня питания, то, так как вторая половина дифференциального инвертора работает в противофазе с первой, напряжение в точке Q+ в это время спадает. При этом, чем выше скорость нарастания в точке Q-, тем быстрее открывается транзистор N4, что ускоряет спадание сигнала в точке Q+ от уровня питания к уровню земли. Таким образом, по мере уменьшения значения управляющего напряжения Vc, уменьшается длительность переднего фронта выходного сигнала инвертора за счет уменьшения сопротивления группы параллельно соединенных нагрузочных р-канальных транзисторов Р1, Р3, Р5 и Р2, Р4, Р6, а за счет увеличения скорости открытия транзисторов N3, N4 уменьшается длительность заднего фронта выходного сигнала. Равномерность функции передачи ГУН при этом достигается за счет того, что нагрузочные транзисторы Р1, Р3, Р5 и Р2, Р4, Р6 открываются при различных значениях управляющего напряжения Vc.

Схемотехника генератора показана на фиг.5, фиг.6, фиг.7, фиг.8 и фиг.9. Фиг.5 представляет конфигурацию ГУН, имеющего четное число дифференциальных инверторов N. Отрицательный выход каждого инвертора идет на положительный вход следующего инвертора во всех парах инверторов, кроме одной, в которой отрицательный выход первого инвертора идет на отрицательный выход следующего инвертора, а положительный выход первого инвертора - на положительный выход следующего инвертора. Фиг.6 представляет конфигурацию ГУН, имеющего нечетное число дифференциальных инверторов N (N больше единицы), где отрицательный выход каждого инвертора идет на положительный вход следующего инвертора во всех соседних парах инверторов. Такие способы соединения дифференциальных инверторов обеспечивают наличие в кольце ГУН отрицательной обратной связи по постоянному току. Фиг.7 представляет дифференциальный инвертор, скорость переключения которого управляется тремя напряжениями Vc, Vcp, Vcm. На фиг.8 и 9 показаны цепи формирования вспомогательных управляющих напряжений Vcp и Vcm из основного управляющего напряжения Vc, диаграммы их зависимостей от напряжения Vc при температурах -60°С, 27°С и 125°С представлены на фиг.10. Диаграммы значений выходных частот и функции передачи ГУН, состоящего из четырех дифференциальных инверторов, при температурах -60°С, 27°С и 125°С приведены на фиг.11 и фиг.12, соответственно. Все зависимости получены для технологии КМОП 180 нм, работающей при напряжении питания 1,8 В, моделирование проводилось в симуляторе Cadence Spectre Simulator.

Из графиков видно, что благодаря наличию трех управляющих напряжений инвертора функция передачи ГУН изменяется не более чем в 2 раза на всем диапазоне основного управляющего напряжения при рабочей температуре, лежащей в диапазоне от -60°С до +125°С (фиг.12). Это позволяет, например, при использовании в составе системы ФАПЧ (фиг.1) с большей точностью выбирать номиналы компонентов ФНЧ для получения прогнозируемых выходных характеристик, таких как джиттер, фазовый шум, время установления рабочего режима ФАПЧ. Широкий диапазон перекрытия частот позволяет выбирать частоту генератора в зависимости от того, какая характеристика ГУН является наиболее приоритетной - низкий фазовый шум или низкое энергопотребление. Например, для получения частоты на выходе ФАПЧ, равной 1200 МГц, ГУН можно настроить на работу с частотой 1200 МГц или 2400 МГц, поделив на выходе частоту на 2. В первом случае ФАПЧ будет обладать худшими параметрами стабильности выходного сигнала (джиттер, фазовый шум) относительно второго варианта, но ГУН будет потреблять меньшую мощность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ШИРОКОДИАПАЗОННЫЙ КОЛЬЦЕВОЙ ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2009 |

|

RU2397603C1 |

| ДИНАМИЧЕСКИЙ D-ТРИГГЕР | 2018 |

|

RU2679220C1 |

| УСТРОЙСТВО, СИСТЕМА И СПОСОБ ПЕРЕКЛЮЧЕНИЯ УРОВНЯ НАПРЯЖЕНИЯ | 2012 |

|

RU2595648C2 |

| ОКТАВНЫЙ МИКРОПОТРЕБЛЯЮЩИЙ ВЫСОКОЧАСТОТНЫЙ КМОП ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2012 |

|

RU2485668C1 |

| ТРИГГЕР, РЕГИСТР СДВИГА, СХЕМА ВОЗБУЖДЕНИЯ УСТРОЙСТВА ОТОБРАЖЕНИЯ, УСТРОЙСТВО ОТОБРАЖЕНИЯ И ПАНЕЛЬ УСТРОЙСТВА ОТОБРАЖЕНИЯ | 2010 |

|

RU2507680C2 |

| СХЕМА УПРАВЛЕНИЯ ДЛЯ ЭНЕРГОНЕЗАВИСИМОГО ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1998 |

|

RU2221286C2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ НАПРЯЖЕНИЙ ДЛЯ ГЕНЕРАТОРА, УПРАВЛЯЕМОГО НАПРЯЖЕНИЕМ | 2017 |

|

RU2642405C1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ УРОВНЯ СИГНАЛА В СХЕМАХ С ПРОГРАММИРУЕМОЙ КОММУТАЦИЕЙ | 2011 |

|

RU2469472C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ИНЖЕКТОРОМ | 2013 |

|

RU2563038C2 |

| Генератор импульсов,управляемый напряжением | 1980 |

|

SU902229A1 |

Настоящее изобретение относится к интегральной электронной технике и может быть использовано в составе высокочастотных устройств тактовой синхронизации цифровых схем. Достигаемый технический результат: повышение линейности модуляционной характеристики, расширение диапазона рабочих частот с перекрытием частот в четыре раза. Кольцевой КМОП генератор, управляемый напряжением (ГУН), содержит N дифференциальных инверторов с двумя входами и двумя выходами, соединенных таким образом, чтобы в кольце обеспечивалась отрицательная обратная связь по постоянному току, каждый дифференциальный инвертор содержит два активных инвертирующих n-канальных транзистора, три p-канальных транзистора, на затворы которых подается основное и два вспомогательных управляющих напряжения, формируемых из основного двумя дополнительными цепями, состоящими из пары p-канальных и пары n-канальных транзисторов. 2 з.п. ф-лы. 12 ил.

1. Широкополосный высокочастотный кольцевой генератор, управляемый напряжением, в котором целое число дифференциальных КМОП инверторов с управляемой скоростью переключения последовательно соединены в кольцо, обеспечивающее отрицательную обратную связь по постоянному току, каждый дифференциальный инвертор содержит первый и второй p-канальные транзисторы и первый, второй, третий и четвертый n-канальные транзисторы, затвор первого n-канального транзистора является первым входом инвертора, затвор второго n-канального транзистора является вторым входом инвертора, стоки первого и третьего n-канальных транзисторов и сток первого р-канального транзистора соединены с затвором четвертого n-канального транзистора и образуют первый выход инвертора, стоки второго и четвертого n-канальных транзисторов и сток второго p-канального транзистора соединены с затвором третьего n-канального транзистора и образуют второй выход инвертора, истоки всех p-канальных транзисторов подключены к линии напряжения питания, истоки всех n-канальных транзисторов подключены к линии земли, на затворы первого и второго p-канальных транзисторов подается основное управляющее напряжение, отличающийся тем, что каждый дифференциальный инвертор содержит третий, четвертый, пятый, шестой p-канальные транзисторы, а также наличием двух цепей формирования вспомогательных управляющих напряжений из основного управляющего напряжения; на затворы третьего и четвертого p-канальных транзисторов подается управляющее напряжение, сформированное из основного управляющего напряжения при помощи первой цепи формирования вспомогательного управляющего напряжения, на затворы пятого и шестого р-канальных транзисторов подается управляющее напряжение, сформированное из основного управляющего напряжения при помощи второй цепи формирования вспомогательного управляющего напряжения, истоки третьего, четвертого, пятого и шестого р-канальных транзисторов подключены к линии напряжения питания, стоки третьего и пятого р-канальных транзисторов объединены со стоком первого р-канального транзистора, стоки четвертого и шестого р-канальных транзисторов объединены со стоком второго р-канального транзистора; в состав первой цепи формирования вспомогательного управляющего напряжения входят седьмой и восьмой р-канальные транзисторы, исток седьмого р-канального транзистора соединен с линией напряжения питания, затвор и сток седьмого р-канального транзистора, а также исток восьмого р-канального транзистора объединены и образуют линию первого вспомогательного управляющего напряжения, сток восьмого р-канального транзистора подключен к линии земли, затвор восьмого р-канального транзистора подключен к линии основного управляющего напряжения; в состав второй цепи формирования вспомогательного управляющего напряжения входят пятый и шестой n-канальные транзисторы, сток пятого n-канального транзистора соединен с линией напряжения питания, затвор пятого n-канального транзистора подключен к линии основного управляющего напряжения, затвор и сток шестого n-канального транзистора, а также исток пятого n-канального транзистора объединены и образуют линию второго вспомогательного управляющего напряжения, исток шестого n-канального транзистора подключен к линии земли.

2. Устройство по п.1, состоящее из четного числа дифференциальных инверторов, соединенных в кольцо так, что первый выход каждого инвертора идет на первый вход следующего инвертора, а второй выход каждого инвертора идет на второй вход следующего инвертора во всех соседних парах инверторов, кроме одной, в которой первый выход первого инвертора идет на второй вход следующего инвертора, а второй выход первого инвертора - на первый вход следующего инвертора.

3. Устройство по п.1, состоящее из нечетного числа дифференциальных инверторов, соединенных в кольцо так, что первый выход каждого инвертора идет на первый вход следующего инвертора, а второй выход каждого инвертора идет на второй вход следующего инвертора во всех соседних парах инверторов.

| ШИРОКОДИАПАЗОННЫЙ КОЛЬЦЕВОЙ ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2009 |

|

RU2397603C1 |

| ПОЛУПРОВОДНИКОВЫЙ ИНТЕГРАЛЬНЫЙ КОЛЬЦЕВОЙ ГЕНЕРАТОР | 1996 |

|

RU2108654C1 |

| Способ управления N-фазным инвертором | 1986 |

|

SU1352604A1 |

| US 7859354 В1, 28.12.2010 | |||

| Кормушка для птицы | 1974 |

|

SU657796A1 |

Авторы

Даты

2012-07-10—Публикация

2011-03-01—Подача