Настоящее изобретение относится к интегральной электронной технике и может быть использовано в составе боков синтезаторов сетки частот (ССЧ), а именно при реализации генератора, управляемого напряжением (ГУН) для повышения стабильности частоты выходного сигнала ГУН к действию помех по цепям напряжения питания.

В составе многих интегральных микросхем средств вычислительной техники широко используются ССЧ, основанные на стабилизации частоты и фазы выходного сигнала ГУН с помощью контура импульсной фазовой автоподстройки частоты (ФАПЧ). В таких ССЧ блок ГУН является наиболее важным элементом, определяющим диапазон частот и величину фазового шума выходного сигнала.

Одной из причин возникновения фазового шума блока ГУН являются помехи по цепям напряжения питания, возникающие при переключениях элементов других блоков микросхемы. Так как помехи по цепям напряжения питания являются высокочастотными, то вызываемый ими фазовый шум в выходном сигнале блока ГУН также высокочастотный, и, соответственно, он не может быть подавлен действием обратной связи контура ФАПЧ.

Использование фильтрации цепей напряжения питания хотя и уменьшает амплитуду помех, но ввиду ограничения емкости, размещаемой на кристалле микросхемы, не всегда обеспечивает требуемое подавление. Эффективность использования внешних по отношению к микросхеме конденсаторов ограничена наличием индуктивности у выводов микросхемы.

Таким образом, разработка решений, направленных на повышение стабильности частоты выходного сигнала блока ГУН к действию помех по цепям напряжения питания, является актуальной задачей.

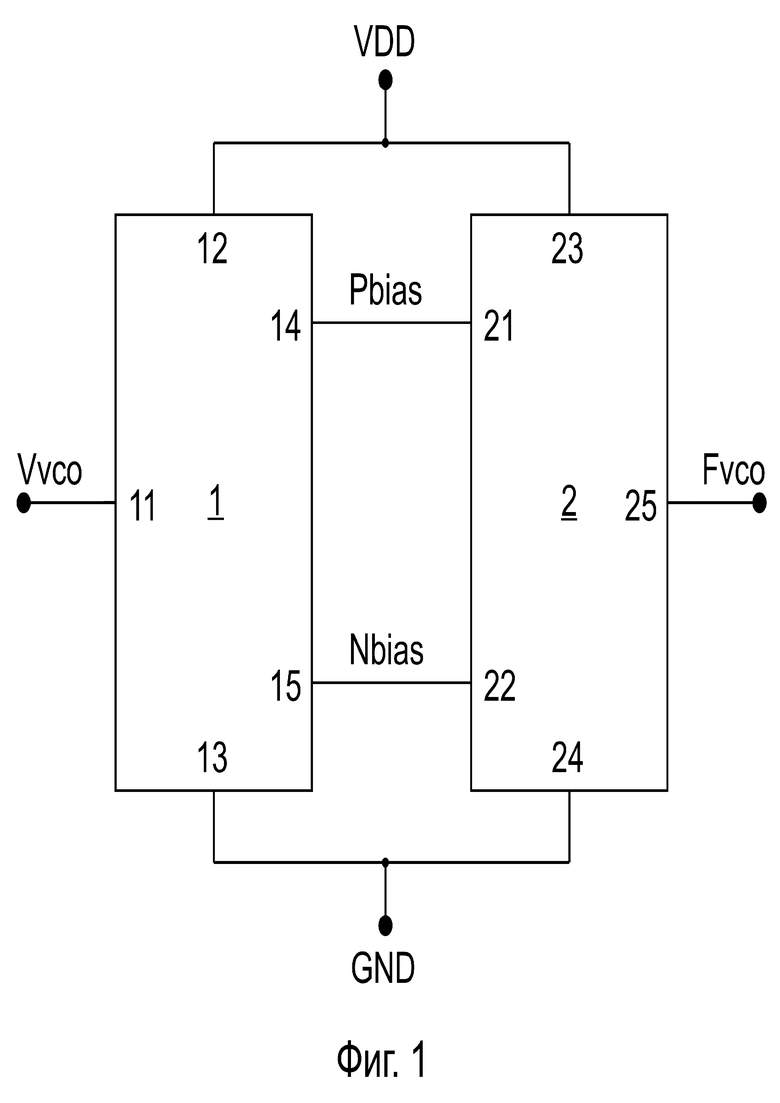

Структурная схема блока ГУН представлена на фиг.1. В ее состав входит устройство 1 формирования выходных управляющих напряжений Pbias и Nbias в соответствии с потенциалом входного управляющего напряжения Vvco и собственно генератор 2, вырабатывающий сигнал Fvco частота которого определяется потенциалами напряжений Pbias и Nbias. Цепь VDD является цепью напряжения питания. Цепь GND является цепью «общий» напряжения питания.

Генератор 2 обычно выполняют на базе LC колебательного контура или на базе кольцевого генератора. Чувствительность к помехам по цепям питания для кольцевых генераторов существенно выше, чем LC генераторов. Однако именно кольцевые генераторы получили наибольшее распространение в блоках ССЧ в составе микросхем средств вычислительной техники, так как содержат только транзисторы, что определяет компактность и конструктивную и технологическую совместимость ССЧ с другими блоками микросхемы.

Одним из способов уменьшения фазового шума выходного сигнала блока ГУН из-за действия помех по цепям напряжения питания является использование устройства формирования управляющих напряжений ГУН с автоматической коррекцией, позволяющей так управлять этими напряжениями, чтобы значение частоты генерируемого сигнала оставалось стабильным.

Направление и величина коррекции управляющих напряжений зависят от конкретной схемы ГУН. В частности, для кольцевых ГУН коррекция управляющих напряжений, как правило, должна иметь тот же знак, что и изменение напряжения питания.

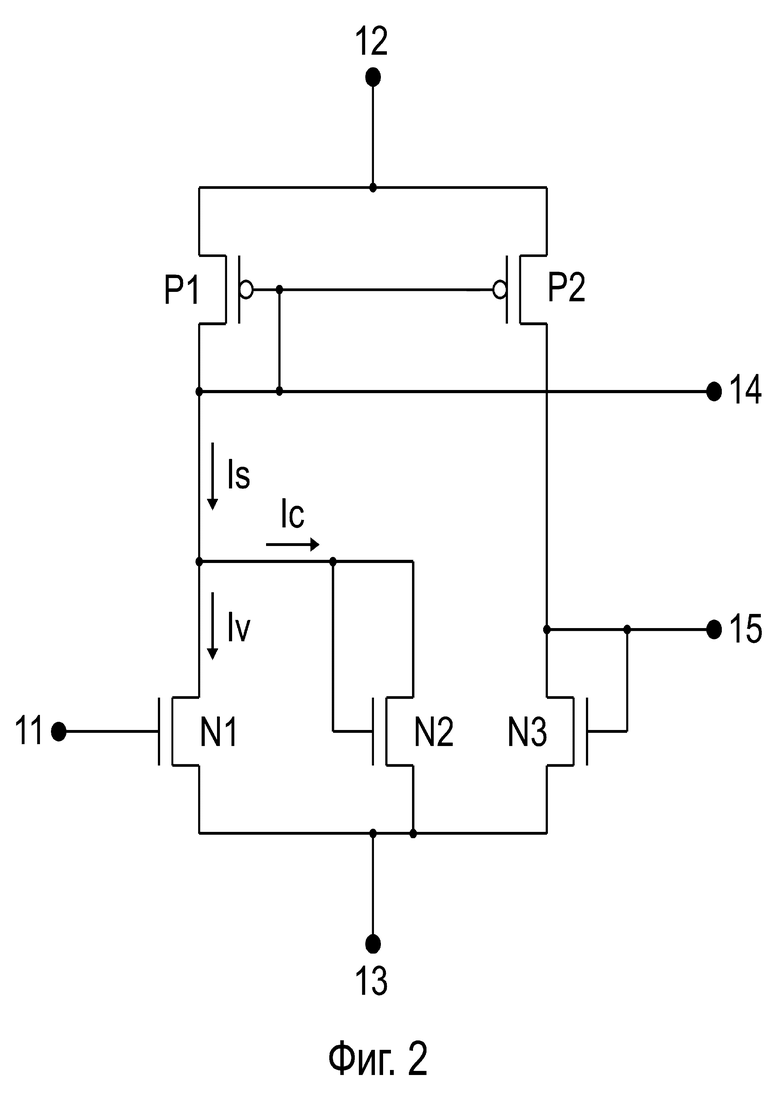

Наиболее близким техническим решением к заявляемому изобретению является устройство формирования управляющих напряжений для кольцевого ГУН, описанное в статье [1]: Kuo-Hsing Cheng, Wei-Bin Yang, Shyh-Shyuan Sheu. A CMOS Low Power and high Noise Immunity Voltage Controlled Oscillator // 6th WSEAS International Multiconference on Circuits, Systems, Communications and Computers (CSCC 2002). 7 - 14 July 2002. Rethymno, Crete, Greece. – 2002. – P. 7001 – 7003. Это устройство является прототипом заявляемого изобретения и представлено на фиг.2.

Общим признаком устройства [1] с заявляемым изобретением является то, что устройство содержит элемент, который, в зависимости от изменений напряжения питания, изменяет значение тока, используемого для формирования управляющих напряжений для кольцевого ГУН и, таким образом, осуществляет автоматическую коррекцию, противодействующую изменению частоты генерируемого сигнала.

В состав устройства [1] входит: первый P1 и второй P2 P–канальные транзисторы и первый N1, второй N2 и третий N3 N–канальные транзисторы; затвор первого N–канального транзистора соединен с первым выводом 11 устройства; истоки первого и второго P–канальных транзисторов соединены между собой и подключены к второму выводу 12 устройства; истоки первого, второго и третьего N–канальных транзисторов соединены между собой и подключены к третьему выводу 13 устройства; затвор и сток первого P–канального транзистора, затвор второго P–канального транзистора, сток первого N–канального транзистора и затвор и сток второго N–канального транзистора соединены между собой и подключены к четвертому выводу 14 устройства; сток второго P–канального транзистора, затвор и сток третьего N–канального транзистора соединены между собой и подключены к пятому выводу 15 устройства.

P–канальные и N–канальные транзисторы имеют структуру метал-диэлектрик-полупроводник (МДП).

В соответствии с фиг.1, на вывод 11 устройства фиг.2 подают входное управляющее напряжение Vvco; вывод 12 устройства подключают к цепи VDD напряжения питания; вывод 13 устройства подключают к цепи GND «общий» напряжения питания; выводы 14 и 15 устройства являются выходными управляющими напряжениями Pbias и Nbias соответственно.

Значение тока Iv определяется потенциалом напряжения Vvco относительно цепи GND. Ток Is является суммой токов Iv и Ic. Транзисторы P1 и P2 образуют токовое зеркало, где P1 использован в режиме диода, на котором, в зависимости от значения тока Is, формируется выходное напряжение Pbias. На транзисторе N3, используемого в режиме диода, формируется выходное напряжение Nbias. Изменение напряжения Vvco приводит к изменению тока Iv и далее к изменению тока Is и, соответственно, напряжений Pbias и Nbias.

Коррекция напряжений Pbias и Nbias при неизменном напряжении Vvco и при изменении (из-за помех) напряжения питания осуществляется следующим образом. Так как транзисторы P1 и N2 образуют цепь из последовательно включенных диодов, то увеличение напряжения питания приводит к увеличению тока Ic и далее к увеличению тока Is и напряжений Pbias и Nbias. Аналогично, уменьшение напряжения питания приводит к уменьшению тока Ic и далее к уменьшению тока Is и напряжений Pbias и Nbias.

Однако устройство [1] имеет недостаток, заключающийся в невозможности обеспечения эффективной коррекции напряжений Pbias и Nbias для диапазона частот выходного сигнала блока ГУН более одной октавы.

Причина данного недостатка следующая. Для кольцевых ГУН диапазон изменений тока Is соизмерим с диапазоном изменений частоты генерируемого сигнала. При этом относительное изменение тока Ic к значению тока Iv из-за изменений напряжения питания должно быть близким к постоянному во всем рабочем диапазоне тока Is. Следовательно, при увеличении тока Iv амплитуда изменений тока Ic должна быть во столько же раз увеличена, а при уменьшении тока Iv амплитуда изменений тока Ic должна быть во столько же раз уменьшена.

В устройстве [1] происходит наоборот. С увеличением тока Iv увеличивается напряжение Pbias (относительно потенциала цепи VDD) т.е. уменьшается напряжение на транзисторе N2, что приводит к уменьшению тока Ic. При уменьшении тока Iv уменьшается напряжение Pbias, т.е. увеличивается напряжение на транзисторе N2 и, соответственно, увеличивается ток Ic.

Таким образом, эффективная коррекция напряжений Pbias и Nbias из-за помех по цепям питания может быть обеспечена только для узкого диапазона изменений тока Is и, следовательно, для соизмеримого (менее одной октавы) диапазона изменения частот выходного сигнала блока ГУН.

Техническим результатам заявляемого изобретения является автоматическая коррекция выходных управляющих напряжений, осуществляемая таким образом, что в условиях действия помех по цепям напряжения питания обеспечивается стабильность частоты выходного сигнала блока ГУН в диапазоне не менее двух октав.

Указанный технический результат достигается тем, что в устройстве [1], содержащем: первый и второй P–канальные транзисторы и первый, второй и третий N–канальные транзисторы; затвор первого N–канального транзистора соединен с первым выводом устройства; истоки первого и второго P–канальных транзисторов соединены между собой и подключены к второму выводу устройства; истоки второго и третьего N–канальных транзисторов соединены между собой и подключены к третьему выводу устройства; затвор и сток первого P–канального транзистора, затвор второго P– канального транзистора, сток первого N–канального транзистора соединены между собой и подключены к четвертому выводу устройства; сток второго P–канального транзистора, затвор и сток третьего N–канального транзистора соединены между собой и подключены к пятому выводу устройства, предложено исток первого и сток второго N–канальных транзисторов соединить между собой; затвор второго N–канального транзистора подключить к второму выводу устройства.

В результате при изменении (из-за помех) напряжения питания изменяется сопротивление канала транзистора N2, что приводит к изменению результирующего тока Is и далее к изменению выходных напряжений на четвертом (Pbias) и пятом (Nbias) выводах устройства. Так как транзисторы N1 и N2 включены последовательно, протекающий через них ток одинаковый и относительное его изменение из-за изменений напряжения питания близко к постоянному значению в широком диапазоне тока и, соответственно, в широком диапазоне частот выходного сигнала блока ГУН (например, не менее двух октав).

Заявляемое изобретение иллюстрируется следующими графическими материалами:

Фиг.1. Структурная схема блока ГУН.

Фиг.2. Устройство формирования управляющих напряжений для ГУН [1], выбранное в качестве прототипа заявляемого изобретения.

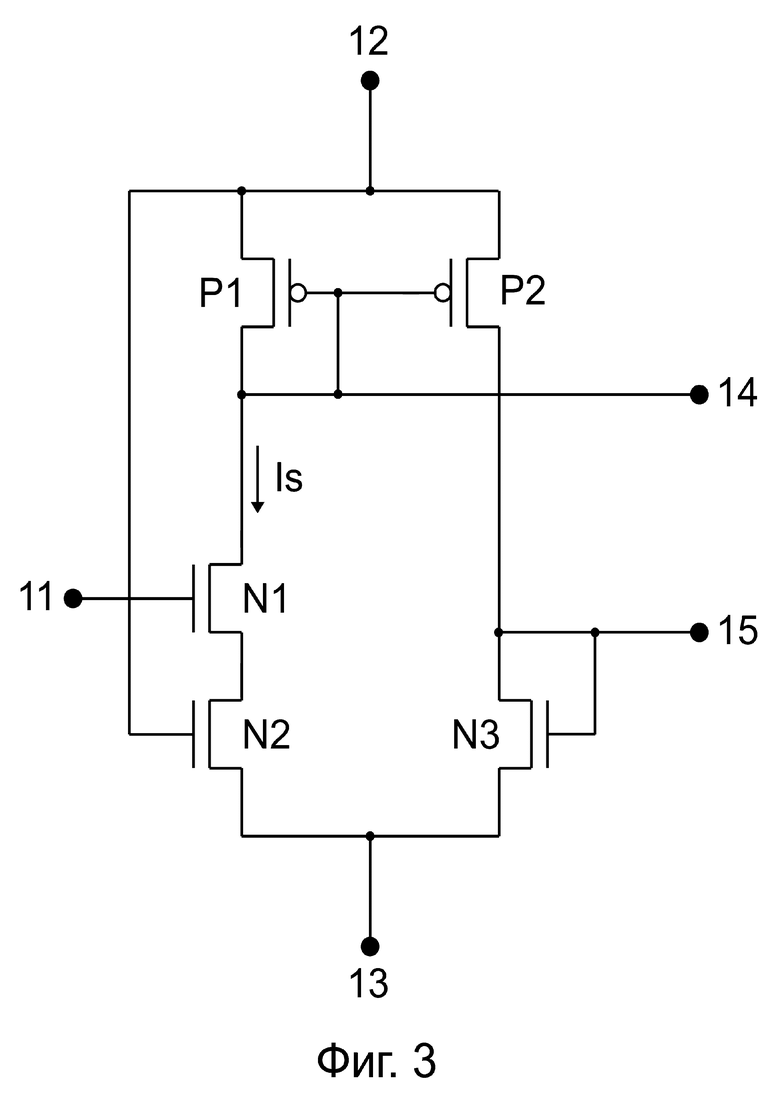

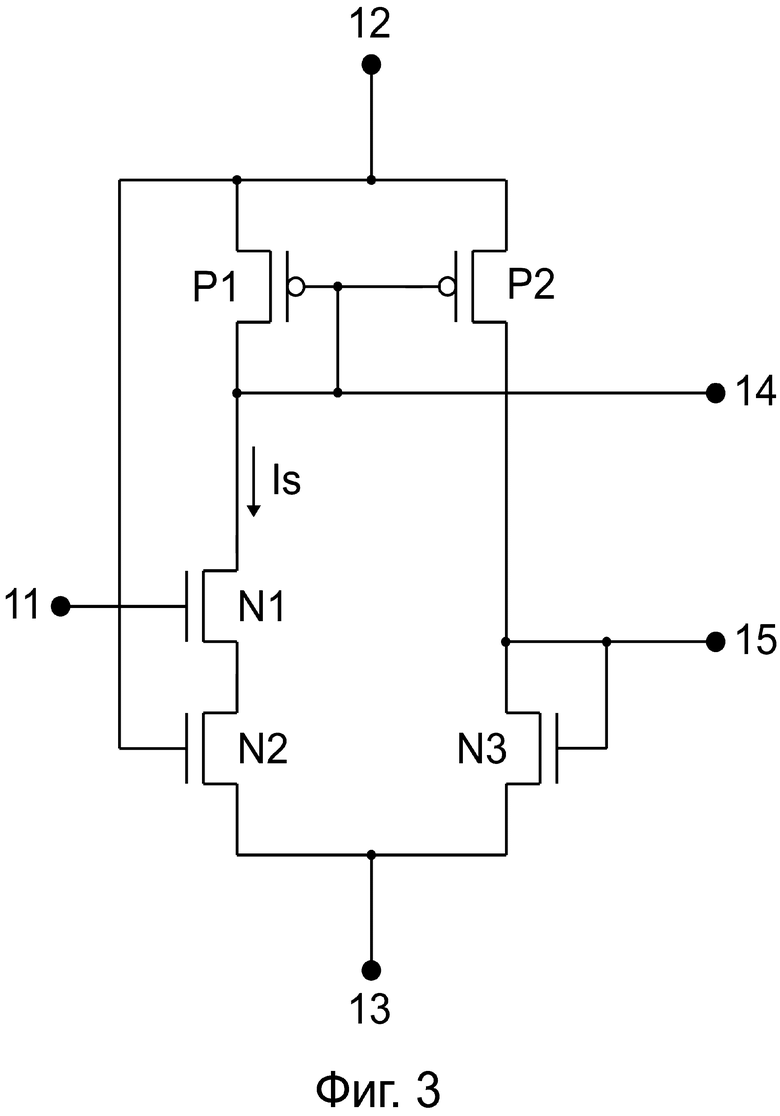

Фиг.3. Устройство формирования управляющих напряжений для ГУН, заявляемое в данном изобретении.

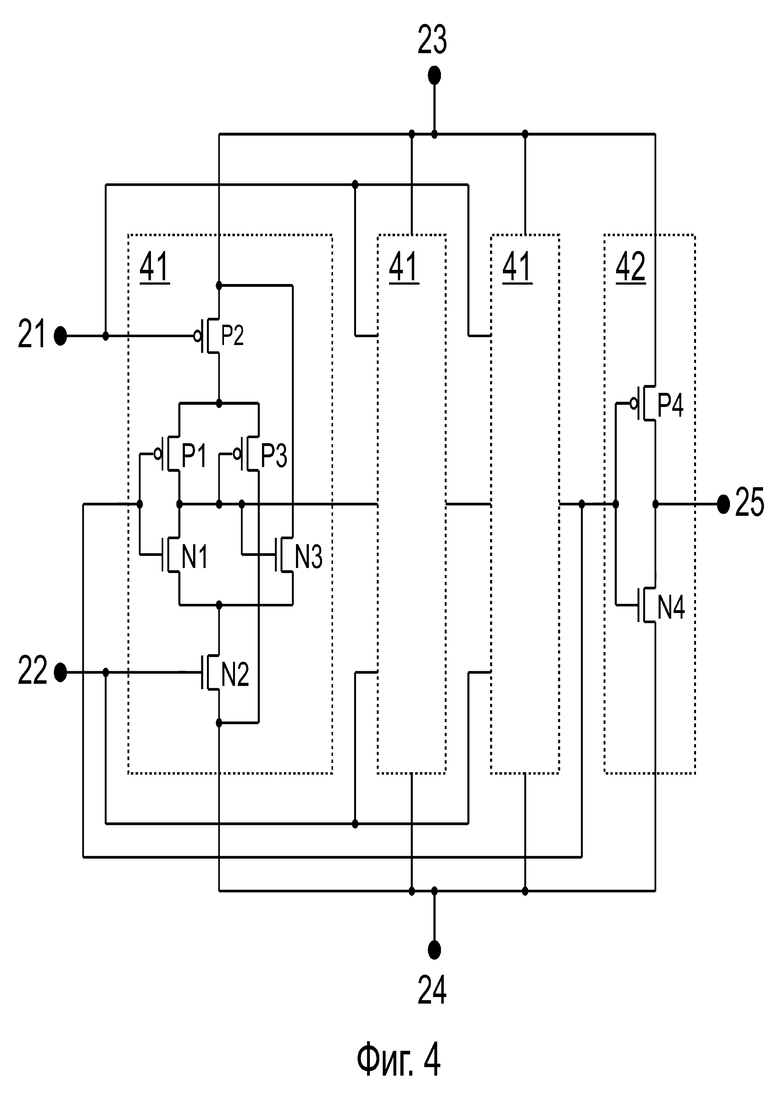

Фиг.4. Кольцевой генератор.

Фиг.5. Вольт-частотные характеристики блока ГУН.

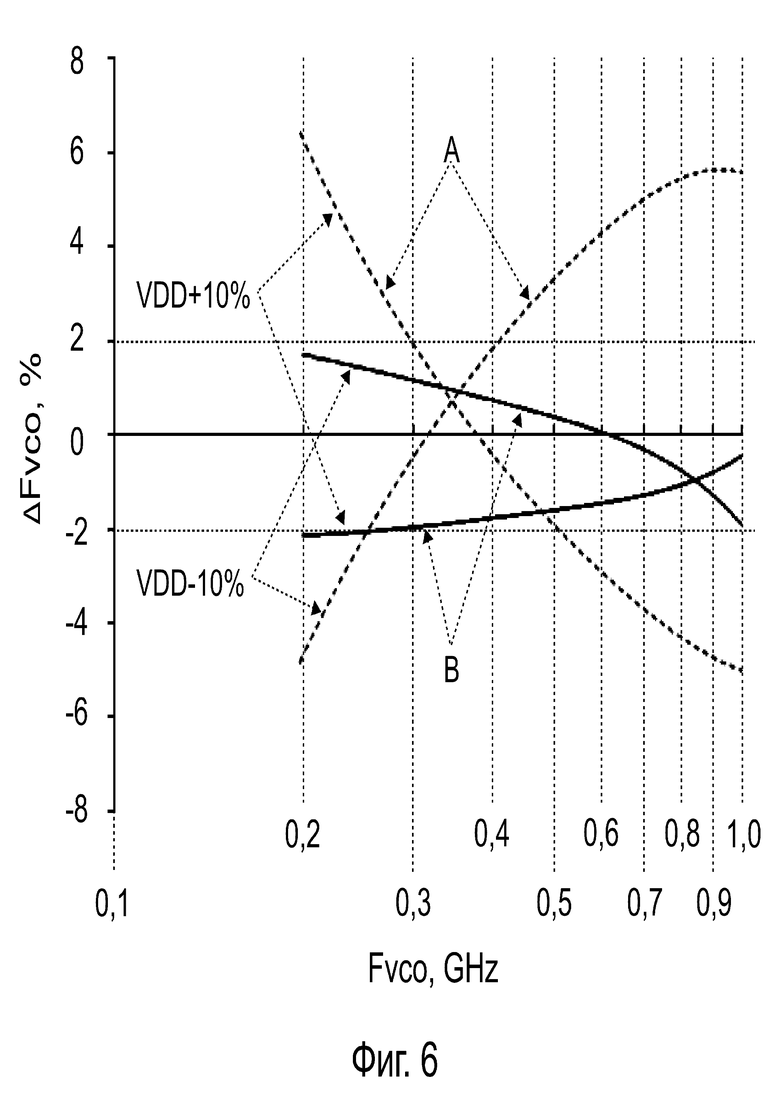

Фиг.6. Отклонения частоты выходного сигнала блока ГУН при изменении напряжения питания на ±10%.

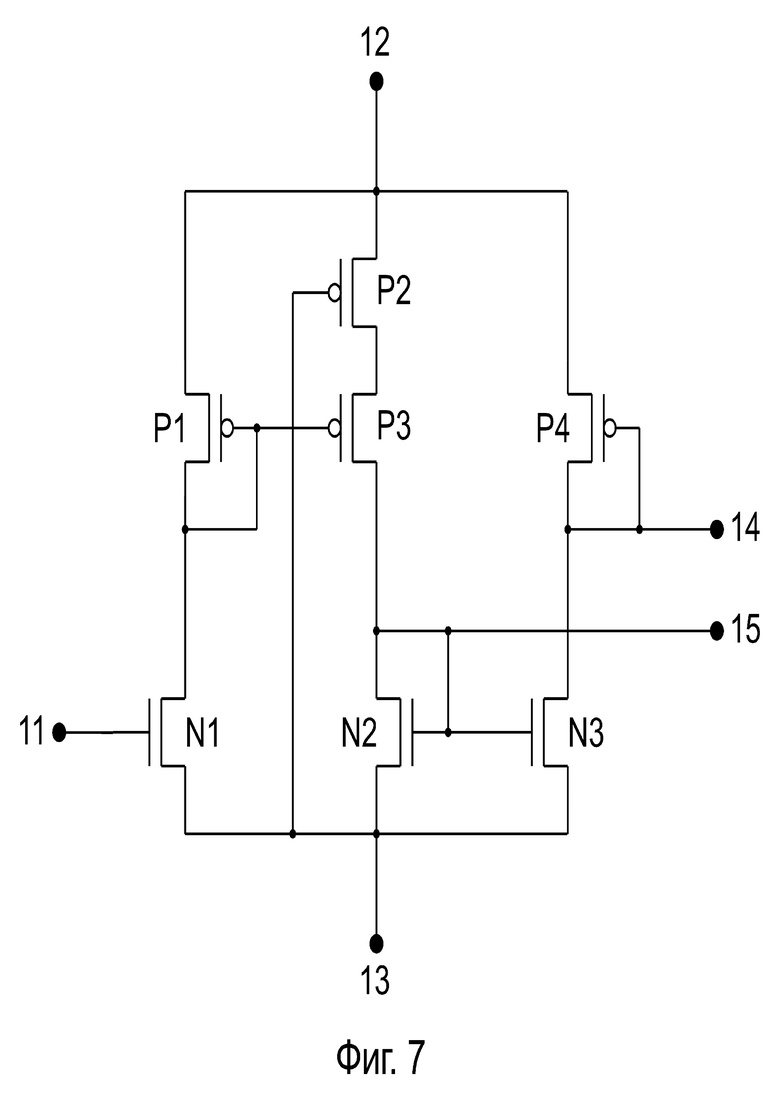

Фиг.7. Первый альтернативный вариант реализации устройства, заявляемого в данном изобретении.

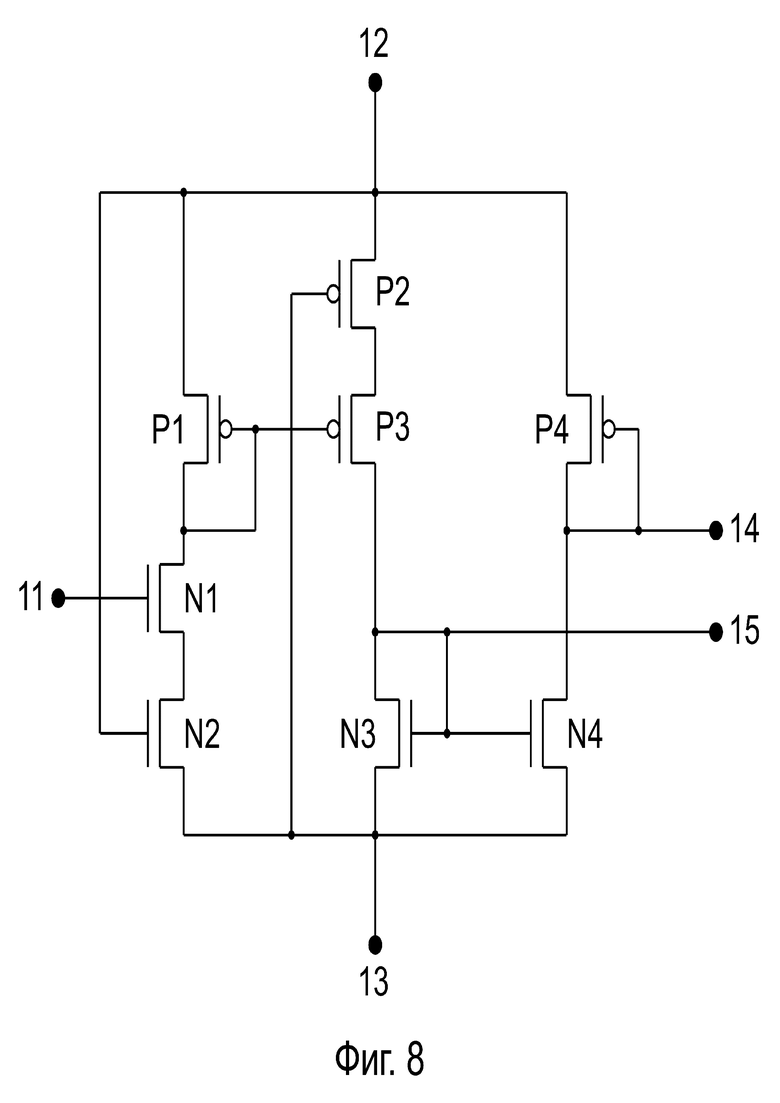

Фиг.8. Второй альтернативный вариант реализации устройства, заявляемого в данном изобретении.

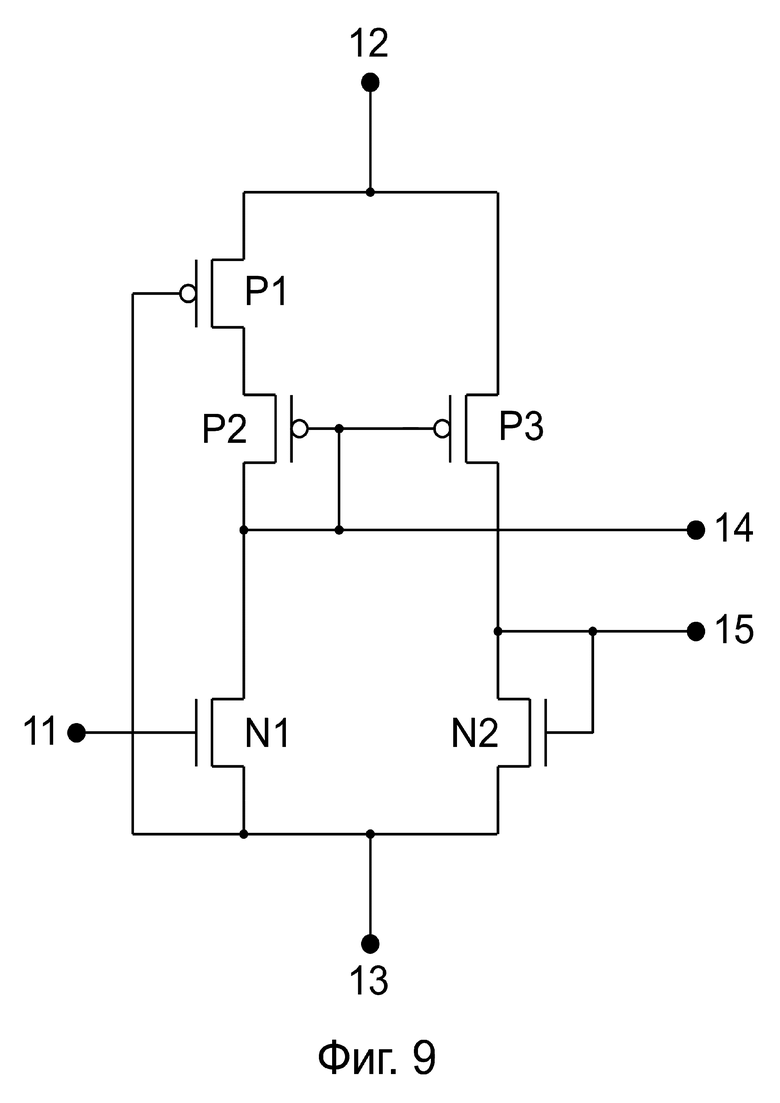

Фиг.9. Третий альтернативный вариант реализации устройства, заявляемого в данном изобретении.

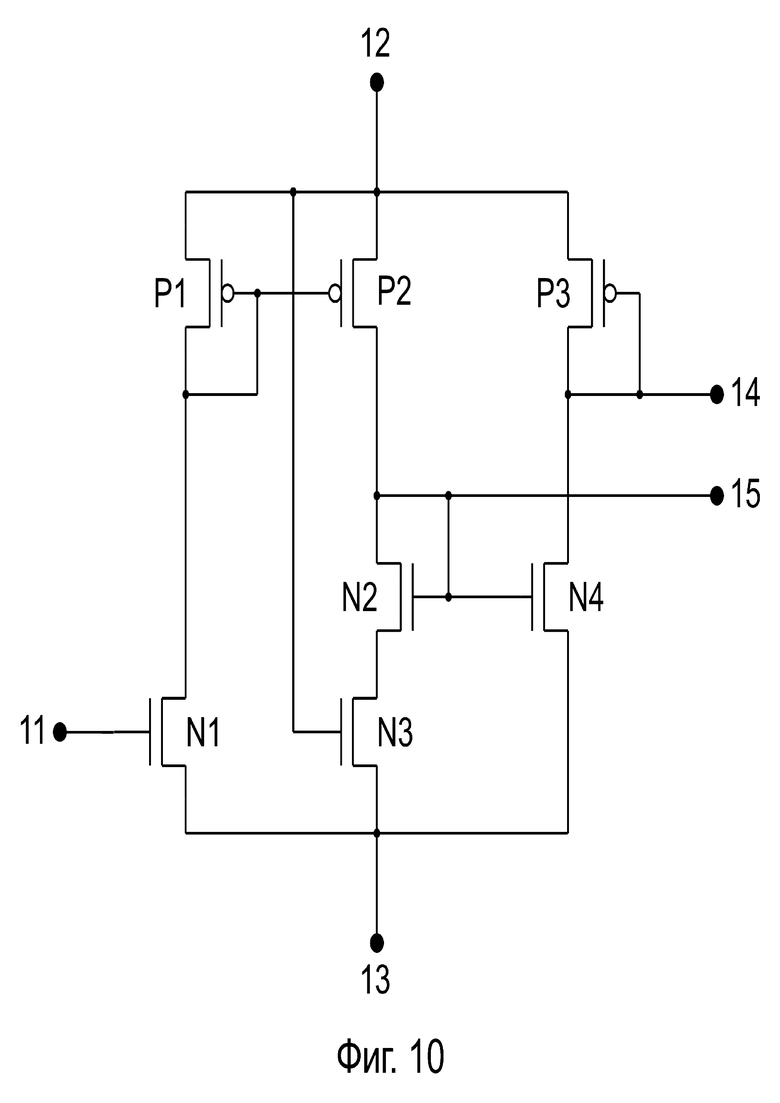

Фиг.10. Четвертый альтернативный вариант реализации устройства, заявляемого в данном изобретении.

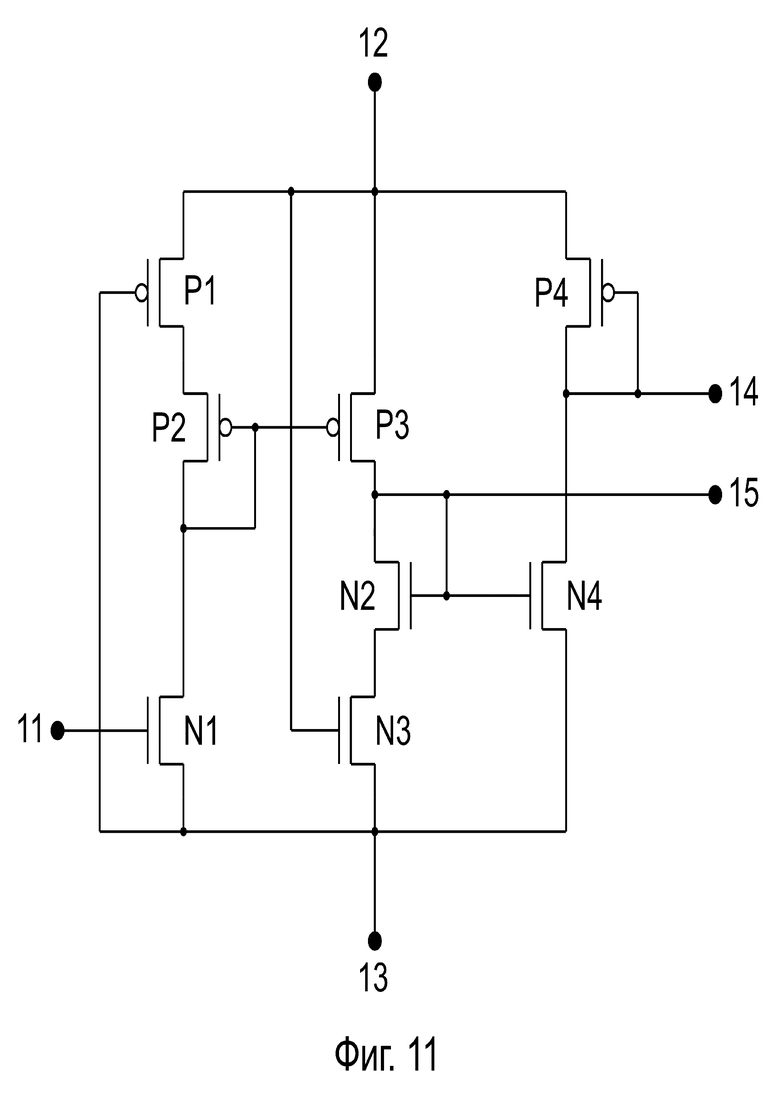

Фиг.11. Пятый альтернативный вариант реализации устройства, заявляемого в данном изобретении.

Заявляемое в данном изобретении устройство формирования управляющих напряжений для ГУН представлено на фиг.3.

В состав устройства входит: первый P1 и второй P2 P–канальные транзисторы и первый N1, второй N2 и третий N3 N–канальные транзисторы; затвор первого N–канального транзистора соединен с первым выводом 11 устройства; исток первого и сток второго N–канальных транзисторов соединены между собой; истоки первого и второго P–канальных транзисторов и затвор второго N–канального транзистора соединены между собой и подключены к второму выводу 12 устройства; истоки второго и третьего N–канальных транзисторов соединены между собой и подключены к третьему выводу 13 устройства; затвор и сток первого P–канального транзистора, затвор второго P– канального транзистора, сток первого N–канального транзистора соединены между собой и подключены к четвертому выводу 14 устройства; сток второго P–канального транзистора, затвор и сток третьего N–канального транзистора соединены между собой и подключены к пятому выводу 15 устройства.

P–канальные и N–канальные транзисторы имеют структуру МДП.

В соответствии с фиг.1 на вывод 11 устройства фиг.3 подают управляющее напряжение Vvco; вывод 12 устройства подключают к цепи VDD напряжения питания; вывод 13 устройства подключают к цепи GND «общий» напряжения питания; выводы 14 и 15 устройства являются выходными напряжениями Pbias и Nbias соответственно.

Устройство заявляемого изобретения работает следующим образом. Пусть потенциал напряжения Vvco находится в рабочем диапазоне и не изменяет свое значение. В этом случае при увеличении напряжения питания сопротивление канала транзистора N2 уменьшится. Так как транзистор N2 включен в исток транзистора N1, то ток Is будет увеличен. Увеличение тока Is вызовет увеличение напряжений Pbias и Nbias. Соответственно, при уменьшении напряжения питания сопротивление канала транзистора N2 увеличится и ток Is будет уменьшен, что вызовет уменьшение напряжений Pbias и Nbias.

Таким образом, в устройстве заявляемого изобретения происходит автоматическая коррекция напряжений Pbias и Nbias, осуществляемая таким образом, чтобы при неизменном значении входного управляющего напряжения Vvco противодействовать изменению выходной частоты ГУН из-за действия помех по цепям напряжения питания.

Так как транзисторы N1 и N2 включены последовательно, протекающий через них ток одинаковый и относительное его изменение из-за помех по цепям напряжения питания близко к постоянному значению в широком диапазоне тока и, соответственно, в широком диапазоне частот выходного сигнала блока ГУН (например, не менее двух октав).

Эффективность заявляемого изобретения может быть продемонстрирована на примере сравнения результатов моделирования отклонений частоты выходного сигнала блока ГУН при изменении напряжения питания на ±10% с использованием устройства [1] и с использованием устройства заявляемого изобретения.

На фиг.4 представлен кольцевой генератор, состоящий из последовательно включенных инверторов 41 с регулируемой длительностью распространения сигнала переключения.

В соответствии с фиг.1, на выводы 21 и 22 подают управляющие напряжения Pbias и Nbias соответственно; вывод 23 подключают к цепи VDD напряжения питания; вывод 24 подключают к цепи GND «общий» напряжения питания; с вывода 25 снимают сигнал выходной частоты блока ГУН Fvco.

За счет общей отрицательной обратной связи в кольцевом генераторе происходит вынужденное колебание, частота которого определяется количеством инверторов 41 и общей длительностью их переключений. Элемент 42 предназначен для увеличения крутизны фронта и спада и, в целом, нагрузочной способности выхода ГУН.

Моделирование проводилось для условия реализации устройств фиг.2 -4 по технологии 180 нм, типовое напряжение питания 1,8 В.

На фиг.5 представлены вольт-частотные характеристики ГУН. Пунктирная линия (A) соответствует характеристике ГУН с использованием устройства [1]. Сплошная линия (B) соответствует характеристике ГУН с использованием устройства заявляемого изобретения. Рабочий диапазон выходных частот составляет от 200 МГц до 1 ГГц. Значения и диапазоны изменений напряжения Vvco в обоих случаях практически равны.

На фиг.6 представлены диаграммы отклонений частоты выходного сигнала Fvco блока ГУН при изменении напряжения питания VDD от значения 1,8 В на +10% (1,98 В) и на -10% (1,62 В). Пунктирные линии (A) соответствуют отклонениям частоты выходного сигнала Fvco для блока ГУН с использованием устройства [1]. Сплошные линии (B) соответствуют отклонениям частоты выходного сигнала Fvco для блока ГУН с использованием устройства заявляемого изобретения.

Пусть задана чувствительность блока ГУН к нестабильности напряжения питания не более 0,2, т.е. при изменении напряжения питания на ±10% допустимое отклонение частоты выходного сигнала блока ГУН ограничено значением ±2%.

Для ГУН с использованием устройства [1] при отклонении напряжения питания на +10% отклонение частоты изменяется от +6,27% до -5,01% с увеличением значения частоты. При отклонении напряжения питания на -10% отклонение частоты изменяется от -4,68% до +5,65% с увеличением значения частоты. Диапазоны частот, удовлетворяющие условию ограничения отклонений выходной частоты ±2%, будут от 297 МГц до 510 МГц и от 255 МГц до 411 МГц соответственно, что меньше одной октавы.

Для ГУН с использованием устройства формирования управляющих напряжений заявляемого изобретения при отклонении напряжения питания на ±10% практически весь диапазон частот от 200 МГц до 1 ГГц (т. е. 2,3 октавы) можно считать удовлетворяющим условию отклонения выходной частоты не более ±2%.

На основании представленных на фиг.6 диаграмм можно сделать следующий вывод: заявляемое в данном изобретении устройство формирования управляющих напряжений в условиях действия помех по цепям напряжения питания обеспечивает стабильность частоты выходного сигнала блока ГУН в диапазоне не менее двух октав.

Заявляемое в данном изобретении устройство формирования управляющих напряжений может иметь различные альтернативные варианты реализации без изменения сущности изобретения.

Первый альтернативный вариант представлен на фиг.7, где элементом, осуществляющим требуемую коррекцию, является транзистор P2. Второй альтернативный вариант представлен на фиг.8, где элементами, осуществляющими коррекцию, являются транзисторы P2 и N2, что позволяет добиться существенного усиления коррекции.

Если требуется, чтобы управляющие напряжения для ГУН не изменялись или изменялись со знаком, противоположным изменению напряжения питания, то устройство формирования управляющих напряжений может быть реализовано вариантами, представленными на фиг.9 - 11.

На фиг.9 (третий альтернативный вариант) элементом, осуществляющим коррекцию, является транзистор P1. На фиг.10 (четвертый альтернативный вариант) элементом, осуществляющим коррекцию, является транзистор N3. На фиг.11 (пятый альтернативный вариант) элементами, осуществляющими коррекцию, являются транзисторы P1 и N3, что позволяет добиться существенного усиления коррекции.

Устройства, представленные на фиг.3 и фиг.7 - 11, могут иметь также альтернативные комплементарные варианты реализации, что не меняет сущности изобретения. При этом потенциал входного управляющего напряжения Vvco будет устанавливаться относительно потенциала цепи VDD.

Изобретение относится к интегральной электронной технике и может быть использовано в составе боков синтезаторов сетки частот, а именно при реализации генератора, управляемого напряжением (ГУН). Технический результат заключается в повышения стабильности частоты выходного сигнала ГУН к действию помех по цепям напряжения питания. Устройство формирования управляющих напряжений для управления частотой выходного сигнала ГУН содержит элемент, корректирующий в зависимости от изменений напряжения питания значение тока, используемого при формировании управляющих напряжений. Элемент, осуществляющий коррекцию, включен последовательно с основным токозадающим элементом, что обеспечивает близкое к постоянному значению относительное изменение тока в широком диапазоне. 11 ил.

Устройство формирования управляющих напряжений для генератора, управляемого напряжением, содержащее первый и второй P–канальные транзисторы и первый, второй и третий N–канальные транзисторы; затвор первого N–канального транзистора соединен с первым выводом устройства; истоки первого и второго P–канальных транзисторов соединены между собой и подключены к второму выводу устройства; истоки второго и третьего N–канальных транзисторов соединены между собой и подключены к третьему выводу устройства; затвор и сток первого P–канального транзистора, затвор второго P– канального транзистора, сток первого N–канального транзистора соединены между собой и подключены к четвертому выводу устройства; сток второго P–канального транзистора, затвор и сток третьего N–канального транзистора соединены между собой и подключены к пятому выводу устройства, отличающееся тем, что исток первого и сток второго N–канальных транзисторов соединены между собой; затвор второго N–канального транзистора подключен к второму выводу устройства.

| ШИРОКОДИАПАЗОННЫЙ КОЛЬЦЕВОЙ ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2009 |

|

RU2397603C1 |

| КОЛЬЦЕВОЙ КМОП ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2011 |

|

RU2455755C1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| US 7268636B2, 11.09.2007 | |||

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2018-01-24—Публикация

2017-01-31—Подача