Настоящее изобретение относится к интегральной электронной технике и может быть использовано в составе программируемых логических интегральных схем (ПЛИС).

Одной из особенностей ПЛИС является наличие нескольких уровней межсоединений, различающихся протяженностью. Соединения между проводниками разных уровней осуществляются с помощью программируемых ключей, состояние каждого из которых (замкнут/разомкнут) определяется содержимым соответствующей ячейки конфигурационной памяти. Таким образом, содержимое конфигурационной памяти ПЛИС определяет конкретное соединение между всеми проводниками, то есть трассировку межсоединеий.

Потенциально возможные соединения между проводниками одного уровня и выбранным проводником другого образуют древовидную структуру (дерево мультиплексоров), в каждой ветви которой находится ключ, к входам подключены проводники одного уровня, а к единственному выходу - проводник другого уровня. После прохождения цепочки ключей (ветвей дерева) входной сигнал ослабляется, а потому на выходе требуется буферизация, восстанавливающая уровень сигнала. Таким образом, возникают две связанные между собой проблемы - реализация ключей и устройства восстановления уровня сигнала (УВУС).

Ранее для реализации ключей использовались пары параллельно включенных Р- и N-канальных транзисторов, на истоки которых подавался входной сигнал, а со стоков снимался выходной. При этом в качестве УВУС использовался обычный инвертор, состоящий из pull-up Р-канального и pull-down N-канального транзисторов, объединенные затворы которых являются входом инвертора, а объединенные стоки - его выходом. Такая схема наряду с очевидным достоинством - дерево мультиплексоров этой схемы проводит сигнал без потери потенциала, имеет также ряд отмечавшихся ранее недостатков. Во-первых, она имеет удвоенное по сравнению с числом ключей число транзисторов, что ведет к соответствующему увеличению площади кристалла, а также паразитных емкостей и, как следствие, ухудшению временных характеристик. Во-вторых, каждый из управляющих сигналов, подаваемых на затворы транзисторов ключей, должен быть представлен как пара из прямого и инвертированного сигналов, что требует дополнительного инвертирования сигналов и также ведет к увеличению площади.

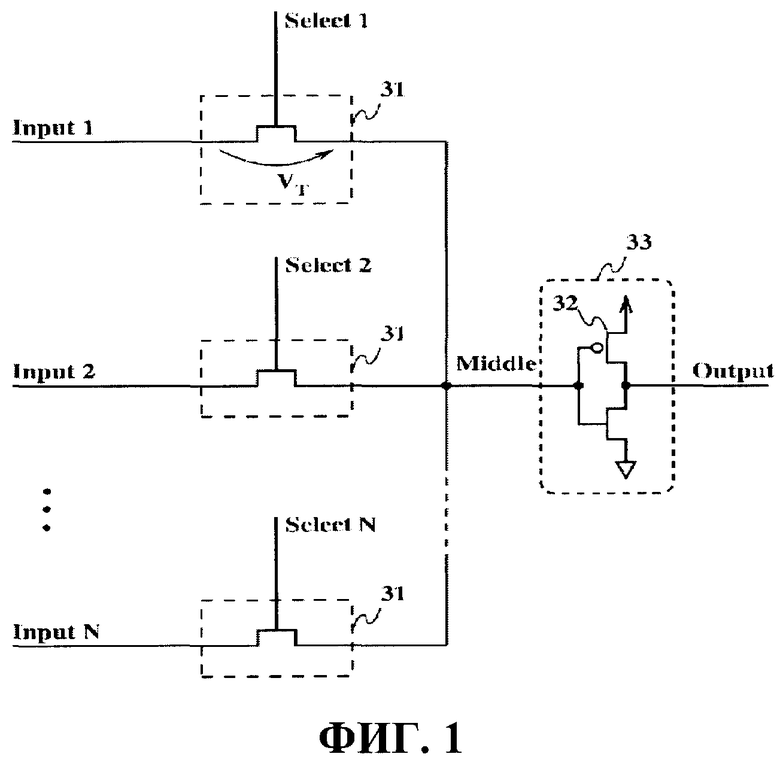

Общеизвестным способом ([1] Жан М. Рабаи, Ананта Чандракасан, Бориврож Николич. Цифровые интегральные схемы. Методология проектирования. - М.: - Вильямс. - 2007. - С.338; [2] патент США №US 2008/0265937 A1 «Level-restoring buffers for programmable interconnect circuits and method for building the same»; [3] патент США №5894227 «Level restoration circuit for pass logic devices») решения этих проблем, приведенным на фиг.1, является использование в качестве ключей дерева мультиплексоров проходных N-канальных транзисторов, что сразу же вдвое уменьшает число транзисторов в дереве и исключает необходимость инвертирования управляющих сигналов. Кроме того, поскольку скорость переключения N-канальных транзисторов выше, чем Р-канальных, следует ожидать большего быстродействия ПЛИС с такой коммутацией межсоединений. Однако использование проходных N-канальных транзисторов приводит к тому, что уровень выходного сигнала логической «1» после прохождения цепочки N-канальных транзисторов дерева мультиплексоров уменьшается по сравнению с напряжением питания на величину порогового напряжения этих транзисторов. В результате в случае использования в качестве выходного буфера обычного инвертора Р-канальный транзистор этого инвертора закрыт не полностью, то есть находится в подпороговом состоянии, что ведет к значительному увеличению сквозного тока через инвертор. Кроме того, существенно снижается шумовой порог.

Известны несколько методов решения этих проблем.

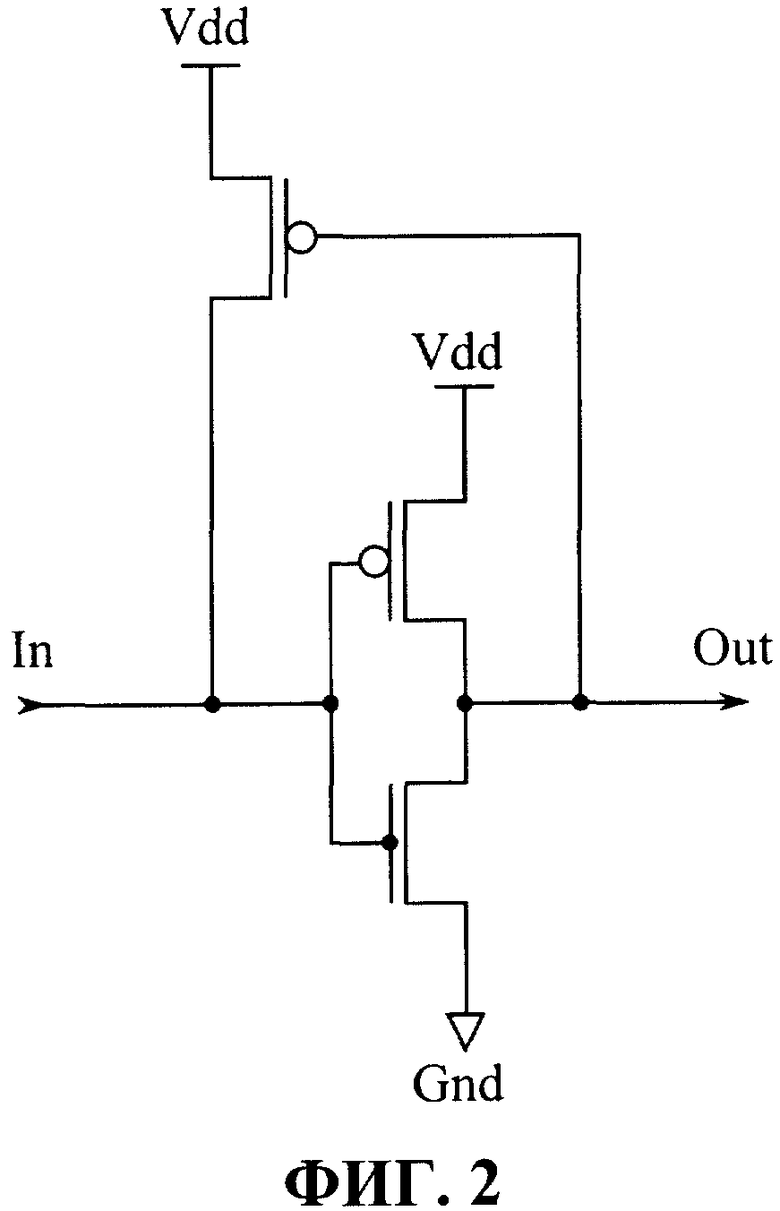

1. Первый, наиболее широко применяющийся в ПЛИС, заключается в том, что для выходного инвертора вводится цепь обратной связи, состоящая из pull-up Р-канального транзистора, сток которого соединен с входом инвертора, а на затвор подается выходное напряжение ([1] - с.345; [2, 3]). Такая схема приведена на фиг.2. Это решение снижает статическое энергопотребление и является хорошим для статического и низкочастотного режимов. Однако с ростом частоты появляется проблема, связанная с выбором соотношения между длиной и шириной канала pull-up Р-канального транзистора. При переключении входного сигнала из состояния логического нуля в логическую единицу (передний фронт) для достаточно быстрого переключения необходимо, чтобы этот транзистор имел короткий канал при относительно большой ширине. Для быстрого переключения входного сигнала из состояния логической единицы в логический нуль (задний фронт) pull-up Р-канальный транзистор должен иметь обратные пропорции - длинный канал небольшой ширины. Поэтому приходится выбирать тот или иной компромисс в пропорциях pull-up Р-канального транзистора, в результате которого передний фронт входного сигнала оказывается «заваленным», то есть напряжение на входе УВУС возрастает с небольшой скоростью, стремясь к напряжению питания лишь в пределе. По этой причине, УВУС на фиг.2 имеет относительно небольшую область работоспособности по напряжению питания, поскольку с уменьшением напряжения питания момент переключения инвертора, определяемый достижением напряжения на входе величины порогового напряжения, все больше и больше запаздывает. Это, во-первых, ограничивает снизу диапазон питающих напряжений, а во-вторых, ограничивает сверху предельную максимальную частоту работоспособности схемы. Эти факторы оказываются очень важными, поскольку именно область работоспособности УВУС чаще всего ограничивает область работоспособности ПЛИС в целом. Кроме того, в период медленного нарастания входного напряжения УВУС существенно снижен шумовой порог.

2. Можно указать также группу методов, требующих для осуществления УВУС второго источника напряжения: [4] патент США №4486670 «Monolitic CMOS low power digital level shifter»; [5] патент США №4958091 «CMOS voltage converter»; [6] патент США №5136190 «CMOS voltage level translator circuit». Однако такие подходы являются сложными в техническом отношении, увеличивают площадь кристалла и противоречат общей тенденции снижения энергопотребления.

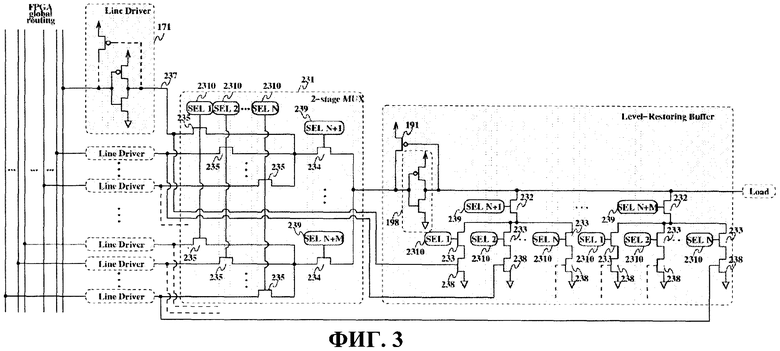

3. В [2] приведены 12 вариантов УВУС (один из вариантов изображен на фиг.3), общим для которых является то, что между выходом УВУС и шиной земли включен набор N-канальных транзисторов, который при прохождении переднего фронта входного сигнала открывается и притягивает этот выход к уровню земли, после чего открывается pull-up Р-канальный транзистор цепи обратной связи. Поскольку напряжение, открывающее N-канальные транзисторы, подается на затворы с опережением соответствующего переключения на входе УВУС, это ускоряет переключение входа из состояния логического «0» в состояние логической «1». При прохождении заднего фронта входного сигнала выход с опережением отключается от уровня земли, а потому переключение из логической единицы в логический нуль происходит в обычном порядке, как и для схемы, изображенной на фиг.2. Однако число дополнительных N-канальных транзисторов схемы на фиг.3 пропорционально числу входов дерева мультиплексоров (или числу его средних точек), которое может быть достаточно велико (20 и более), поэтому дополнительная площадь оказывается значительной. Далеко не всегда в реально существующих ПЛИС имеются промежуточные буферы (Line Driver 171 на фиг.3), поэтому на всех шинах верхнего уровня, даже отключенных соответствующим ключом SEL, появляется дополнительная нагрузка (затворы транзисторов 238 на фиг.3), что вызывает увеличение размеров драйверов этих шин. Даже в том случае, если промежуточные буферы (Line Driver 171 на фиг.3) присутствуют, их размеры должны быть увеличены для переключения упомянутой выше дополнительной нагрузки. И в том, и в другом случае площадь кристалла и динамическое энергопотребление возрастают. Наконец, дополнительная нагрузка в виде затворов транзисторов 232, 233 на фиг.3 появляется на драйверах сигналов SEL, вызывая необходимость увеличения площади и энергопотребления этих драйверов. Таким образом, в целом схема на фиг.3 оказывается очень затратной по площади и с увеличенным энергопотреблением, поскольку уменьшение энергопотребления выходного инвертора УВУС с избытком компенсируется увеличенным энергопотреблением драйверов.

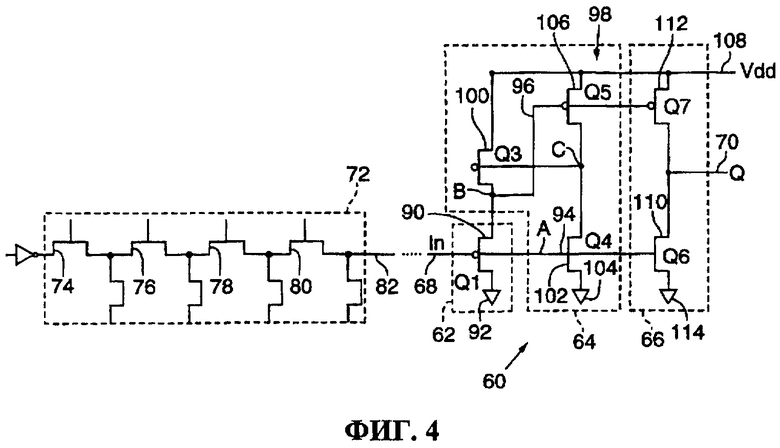

4. На фиг.4 приведена схема УВУС из патента [3], особенностью которой является последовательное включение между шинами питания и земли pull-up Р-канального транзистора 100 и pull-down Р-канального транзистора 90. Однако уровень входного сигнала In в состоянии логической «1» вследствие прохождения цепочки N-канальных транзисторов дерева мультиплексоров уменьшается по сравнению с напряжением питания на величину порогового напряжения этих транзисторов. В результате pull-down Р-канальный транзистор 90 может быть закрыт не полностью, то есть находиться в подпороговом состоянии, тогда как последовательно включенный с ним pull-up Р-канальный транзистор 100 в это время полностью открыт.Это ведет к значительному увеличению сквозного тока через эти транзисторы и возрастанию уровня энергопотребления. Кроме того, существенно снижается шумовой порог.

Прототипом настоящего изобретения является стандартное УВУС, схема которого изображена на фиг.2.

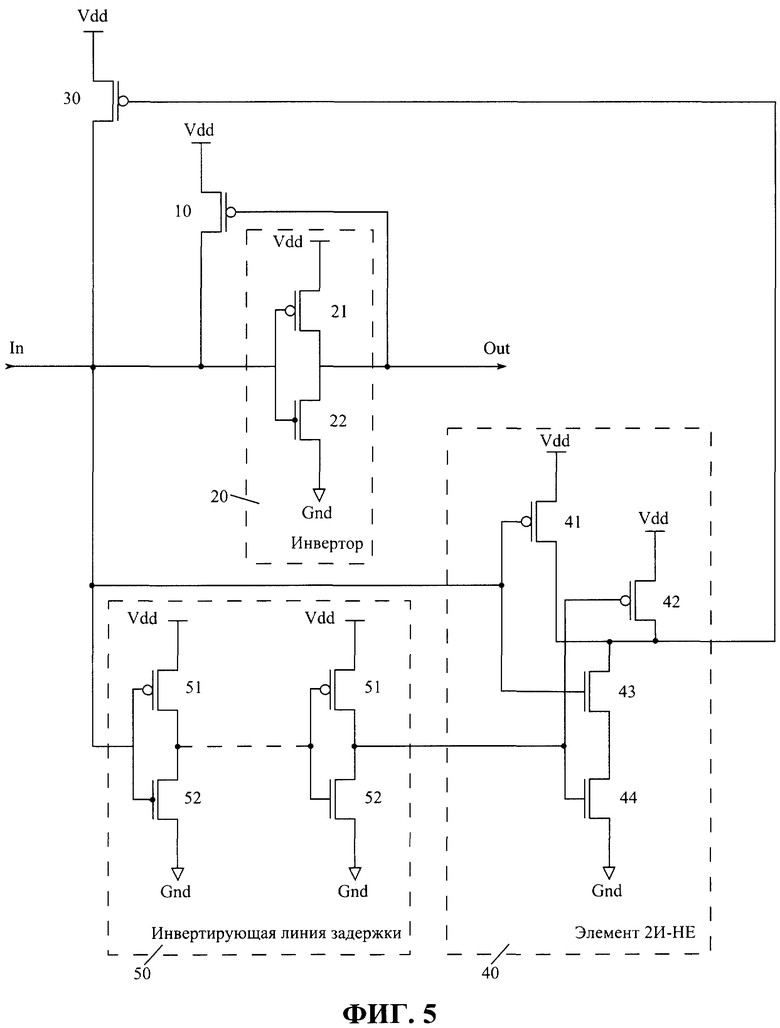

Заявляемое УВУС, схема которого приведена на фиг.5, содержит полный набор компонентов, имеющихся в стандартном УВУС на фиг.2: pull-up Р-канальный транзистор 10, сток которого соединен с входом In УВУС, а на затвор подается выходной сигнал Out. Вход In УВУС соединен также с входом инвертора 20, состоящего из pull-up Р-канального транзистора 21 и pull-down N-канального транзистора 22, объединенные затворы которых являются входом инвертора, а объединенные стоки - его выходом, являющимся также выходом Out УВУС. Дополнительно заявляемое УВУС содержит включенный параллельно транзистору 10 pull-up Р-канальный транзистор 30, сток которого также соединен с входом In УВУС, а затвор управляется выходным сигналом логического элемента 2И-НЕ 40, образованного pull-up Р-канальными транзисторами 41 и 42, pull-down N-канальным транзистором 44 и N-канальным транзистором 43, исток которого соединен со стоком N-канального транзистора 44. Объединенные стоки транзисторов 41, 42 и 43 являются выходом элемента 2И-НЕ 40, затворы транзисторов 41 и 43 объединены и образуют первый вход элемента 2И-НЕ 50, который соединен с входом In УВУС, затворы транзисторов 42 и 44 также объединены и образуют второй вход элемента 2И-НЕ 40, который соединен с входом In УВУС через инвертирующую линию задержки (ИЛЗ) 50, состоящую из нечетного числа последовательно включенных инверторов. Каждый из этих инверторов состоит из pull-up Р-канального транзистора 51 и pull-down N-канального транзистора 52, объединенные затворы которых являются входом инвертора, а объединенные стоки - его выходом. Вход первого инвертора, являющийся входом ИЛЗ 50, соединен с входом In УВУС, выход последнего инвертора, являющийся выходом ИЛЗ 50, соединен с вторым входом элемента 2И-НЕ 40.

Основной задачей данного изобретения является расширение области работоспособности УВУС по напряжению питания и частоте.

Техническим результатом при использовании настоящего изобретения является уменьшение времени задержки переключения и увеличение крутизны переднего фронта сигнала, уменьшение нижней границы допустимого диапазона питающих напряжений, увеличение предельной максимальной частоты работоспособности схемы и повышение шумового порога.

Заявляемое изобретение иллюстрируется следующими графическими материалами.

Фиг.1. Выходной каскад дерева мультиплексоров с ключами на проходных N-канальных транзисторах и выходной инвертор.

Фиг.2. Схема стандартного УВУС с pull-up Р-канальным транзистором.

Фиг.3. Схема одного из двенадцати УВУС патент [2].

Фиг.4. Схема УВУС патент [3].

Фиг.5. Схема заявляемого УВУС.

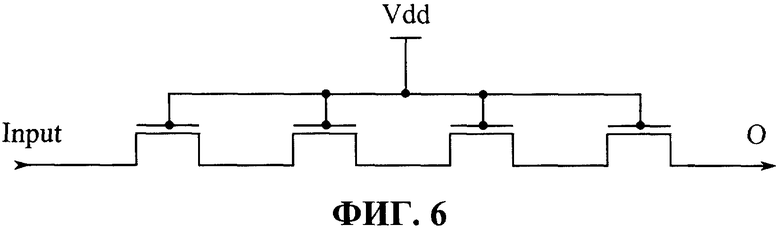

Фиг.6. Цепочка открытых N-канальных транзисторов для моделирования прохождения сигнала через открытые ветви дерева мультиплексоров.

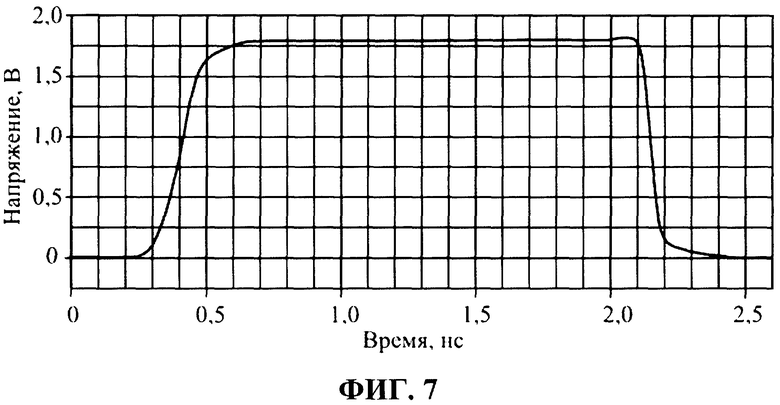

Фиг.7. График зависимости входного напряжения на входе Input схемы на фиг.6 от времени.

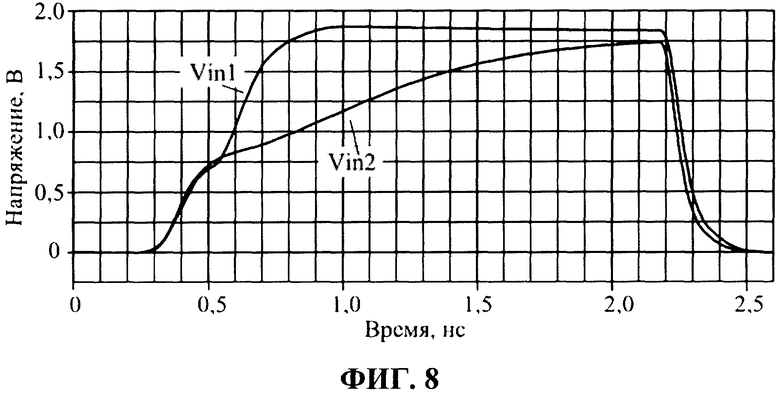

Фиг.8. Графики зависимости напряжения на входе In УВУС от времени при напряжении питания 1,8 В, где Vin1 - для заявляемого УВУС, Vin2 - для УВУС на фиг.2.

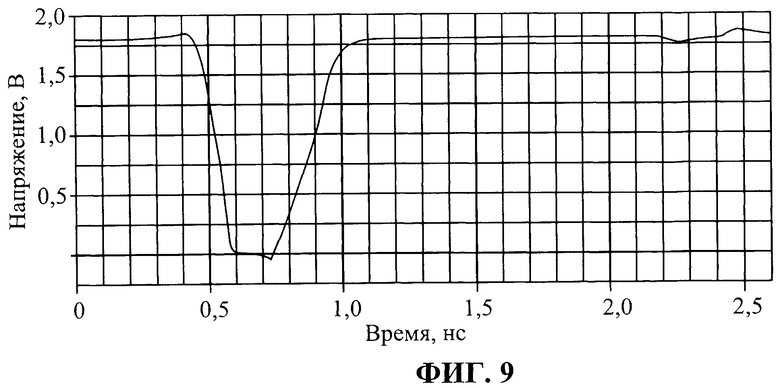

Фиг.9. График зависимости напряжения на выходе элемента 2И-НЕ 50 от времени при напряжении питания 1,8 В.

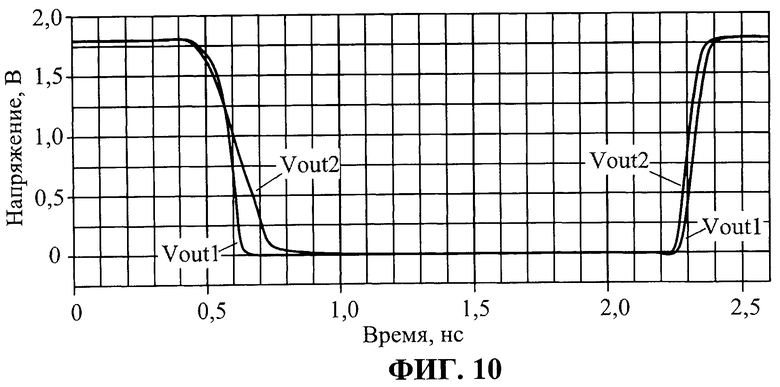

Фиг.10. Графики зависимости напряжения на выходе Out УВУС от времени при напряжении питания 1,8 В, где Vout1 - для заявляемого УВУС, Vout2 - для УВУС на фиг.2.

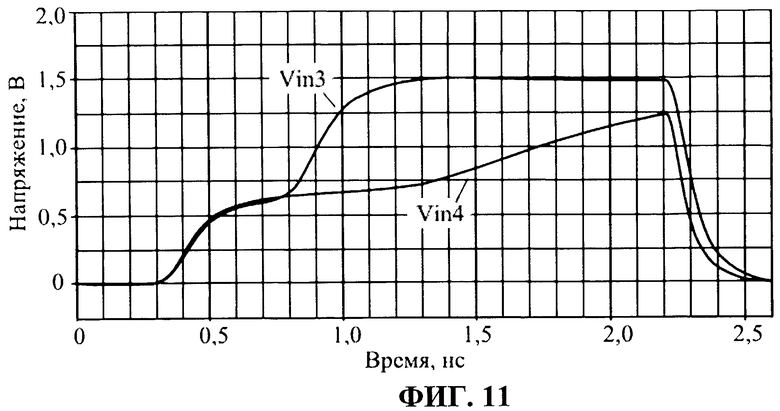

Фиг.11. Графики зависимости напряжения на входе In УВУС от времени при напряжении питания 1,44 В, где Vin3 - для заявляемого УВУС, Vin4 - для УВУС на фиг.2.

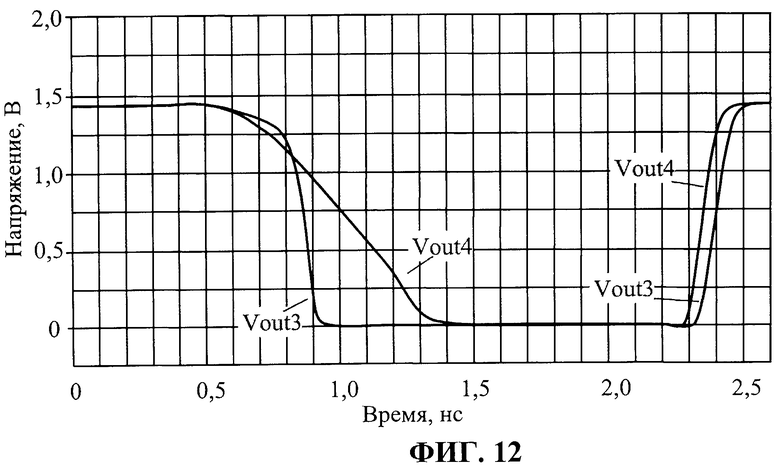

Фиг.12. Графики зависимости напряжения на выходе Out УВУС от времени при напряжении питания 1,44 В, где Vout3 - для заявляемого УВУС, Vout4 - для УВУС на фиг.2.

Заявляемое изобретение осуществляет работу следующим образом.

В стационарном состоянии, когда на вход In подается сигнал уровня логического «0» или логической «1», на первый вход элемента 2И-НЕ 40 поступает входной сигнал, а на второй - через нечетное число инверторов ИЛЗ 50 инверсный к нему, в результате чего выход элемента 2И-НЕ 40 в стационарном состоянии всегда находится в состоянии уровня логической «1». Поскольку сигнал с выхода элемента 2И-НЕ 40 подается на затвор pull-up Р-канального транзистора 30 (см. фиг.5), то этот транзистор закрыт и не оказывает влияния на состояние входа и выхода схемы. Таким образом, в стационарном состоянии заявляемое изобретение работает фактически как стандартная схема на фиг.2. Когда вход In находится в состоянии уровня земли, на выход Out через инвертор 20 поступает инверсный к нему сигнал уровня напряжения питания, который по цепи обратной связи запирает транзистор 10, отключая тем самым вход In от шины питания. Когда вход In находится в состоянии логической единицы, на вход In в действительности после прохождения цепочки N-канальных транзисторов дерева мультиплексоров поступает напряжение, уменьшенное по сравнению с напряжением питания на величину порогового напряжения этих транзисторов. Однако на выход Out через инвертор 20 поступает сигнал уровня земли, который по цепи обратной связи открывает транзистор 10 и восстанавливает уровень входного сигнала In до уровня напряжения питания.

Рассмотрим теперь работу схемы в динамическом режиме. При нахождении входа In в состоянии логического «0» первый и второй входы элемента 2И-НЕ 40 находятся соответственно в состояниях логического «0» и «1», а его выход - в состоянии логической «1», удерживая pull-up Р- канальный транзистор 30 в запертом состоянии. При переключении входа In УВУС из состояния логического «0» в состояние логической «1», то есть при прохождении переднего фронта входного сигнала, этот сигнал сразу же поступает на первый вход элемента 2И-НЕ 40. Поскольку на второй вход этого элемента сигнал с входа In поступает через ИЛЗ 50, состоящую из нечетного числа инверторов, то в течение некоторого промежутка времени на этом входе сохраняется прежнее состояние логической «1». Таким образом, в течение времени задержки ИЛЗ 50 после прохождения переднего фронта на обоих входах элемента 2И-НЕ 40 устанавливаются состояния логической «1», формируя тем самым на его выходе сигнал уровня земли, который поступает на затвор pull-up Р-канального транзистора 30 и открывает этот транзистор. В результате потенциал шины питания через этот открытый транзистор поступает на вход In УВУС и восстанавливает его до уровня шины питания. Процесс этот происходит намного быстрее, чем для схемы на фиг.2, поскольку транзистор 30 включен параллельно транзистору 10 и на размеры Р-канального транзистора 30 ограничений не налагается, то есть его канал может быть выбран коротким и широким, так чтобы транзистор 30 переключался очень быстро. После того, как инвертированный сигнал с входа In через ИЛЗ 50 достигнет второго входа элемента 2И-НЕ 40, на этом входе установится уровень логического «0», что приведет к состоянию логической «1» на выходе этого элемента, которое вновь закроет Р-канальный транзистор 30. В дальнейшем уровень напряжения питания на входе In поддерживается открывшимся к этому моменту Р-канальным транзистором 10. Таким образом, крутизна переднего фронта сигнала при использовании настоящего УВУС увеличивается, а время задержки переключения уменьшается.

Непосредственно перед прохождением заднего фронта через вход In последний находится в состоянии логической «1», первый и второй входы элемента 2И-НЕ 40 - соответственно в состояниях логической «1» и «0», а его выход - в состоянии логической «1», удерживая pull-up Р-канальный транзистор 30 в запертом состоянии. При переключении входа In УВУС из состояния логической «1» в состояние логического «0», то есть при прохождении заднего фронта входного сигнала, этот сигнал логического «0» сразу же поступает на первый вход элемента 2И-НЕ 40 и продолжает удерживать на выходе элемента 2И-НЕ 40 состоянии логической «1» даже после поступления через ИЛЗ 50 на второй вход элемента 2И-НЕ 40 сигнала логической «1». Таким образом, при прохождении заднего фронта на выходе элемента 2И-НЕ 40 сохраняется состояние логической «1» и, следовательно, закрытое состояние pull-up Р-канального транзистора 30. Pull-up Р-канальный транзистор 10, затвор которого соединен с входом In через инвертор 20, при этом также запирается, отключая тем самым вход In от шины питания, после чего на In устанавливается состояние логической «1», а на выходе Out - состояние логического «0»

Таким образом, дополнительный транзистор 30 открыт лишь при переключении входа In УВУС из состояния логического «0» в состояние логической «1» в течение промежутка времени, определяемого задержкой сигнала в ИЛЗ 50. Скорость этого переключения (крутизна) определяется главным образом параметрами pull-up Р-канального транзистора 30, канал которого может быть выбран коротким и широким для обеспечения максимальной крутизны. Поскольку при этом pull-up Р-канальный транзистор 10 играет вспомогательную роль, то необходимость упомянутого выше компромисса в выборе пропорций его канала исчезает, и размеры pull-up Р-канального транзистора 10 следует выбрать так, чтобы обеспечить максимальную крутизну определяемого этим транзистором заднего фронта, то есть выбрать максимальную длину канала при его минимальной ширине.

При прохождении переднего фронта входного сигнала момент переключения инвертора УВУС на фиг.2 определяется достижением напряжения на входе величины порогового напряжения этого инвертора. Так как с уменьшением напряжения питания скорость нарастания напряжения на входе УВУС уменьшается, то переключение УВУС на фиг.2 будет все больше запаздывать вплоть до потери работоспособности при некотором минимальном напряжении питания. Поскольку заявляемое УВУС переключается значительно быстрее, то это означает, что оно сохранит свою работоспособность при существенно более низких напряжениях, то есть оно имеет более широкую область работоспособности по напряжению питания по сравнению с УВУС на фиг.2. Кроме того, так как заявляемое УВУС имеет более высокую скорость нарастания входного напряжения, оно имеет более высокий шумовой порог.

Поскольку заявляемое изобретение обеспечивает существенно более высокую крутизну и меньшую задержку переключения переднего фронта при сохранении крутизны и незначительном увеличении задержки заднего фронта, то это приводит к увеличению предельной максимальной частоты работоспособности схемы.

Возможность осуществления изобретения также подтверждается результатами моделирования данного УВУС, выполненного в симуляторе Cadence Spectre Simulator для технологии КМОП 180 нм, номинального напряжения питания 1,8 В, температуры 25°С и инвертирующей линии задержки, содержащей три инвертора. Результаты сопоставлялись с соответствующими данными для УВУС, схема которого приведена на фиг.2. Последовательность открытых ветвей дерева мультиплексоров моделировалась цепочкой, состоящей из четырех последовательно включенных открытых N-канальных транзисторов, изображенной на фиг.6. Выход О этой цепочки подключался к входу In заявляемого УВУС при его моделировании или к входу In УВУС на фиг.2 при моделировании последнего, на вход цепочки подавался формируемый предварительными буферами сигнал, вид которого показан на фиг.7. После прохождения цепочки напряжение на входе УВУС имеет вид, показанный на фиг.8, где Vin1 - зависимость входного напряжения от времени для заявляемого УВУС, Vin2 - для УВУС на фиг.2. Как видно из фиг.8, при переключении из состояния логического «0» в состояние логической «1» напряжение Vin2 на входе УВУС на фиг.2 восстанавливается очень медленно и не достигает уровня напряжения питания вплоть до переключения входа в состояние логического «0», то есть в течение всего этого промежутка времени через pull-up Р-канальный транзистор протекает ток, а схема имеет существенно сниженный шумовой порог. Напряжение Vin1 на входе заявляемого УВУС на начальном промежутке в течение порядка 0,2 нс после начала переключения ведет себя подобно Vin2, то есть возрастает очень медленно. Однако после того, как на выходе элемента 2И-НЕ 40 на короткий промежуток времени устанавливается напряжение состояния логического «0» (см. фиг.9), которое поступает на затвор pull-up Р-канального транзистора 30 и открывает этот транзистор, напряжение Vin1 быстро возрастает и восстанавливает свой уровень до уровня напряжения питания. Характерный момент времени, в который открывается транзистор 30, определяется точкой перегиба на кривой Vin1.

На фиг.10 показаны графики зависимости напряжения на выходе Out УВУС от времени: Vout1 - для заявляемого УВУС, Vout2 - для УВУС на фиг.2. Как видно из фиг.10, вследствие более быстрого восстановления уровня Vin1 по сравнению с Vin2, передний фронт Vout1 имеет значительно большую крутизну по сравнению с Vout2, передний и задний фронты Vout1 почти симметричны, тогда как Vout2 существенно асимметричен. Это обеспечивает увеличение предельной максимальной частоты работоспособности схемы.

На фиг.11 и фиг.12 приведены результаты моделирования УВУС для напряжения питания, уменьшенного относительно номинального на 20% (1,44 В) при сохранении остальных параметров. Как и ожидалось, напряжение на входе заявляемого УВУС (Vin3) растет значительно быстрее напряжения на входе УВУС на фиг.2 (Vin4), что приводит к более крутому переднему фронту напряжения на выходе (Vout3) по сравнению с «заваленным» передним фронтом Vout4 и меньшей задержке переключения. Тем не менее, УВУС на фиг.2 сохраняет свою работоспособность, хотя скважность сигнала значительно ухудшилась. Моделирование показало, что дальнейшее понижение напряжения питания до величины 70% относительно номинального (1,26 В) приводит к тому, что УВУС на фиг.2 не успевает переключиться, то есть теряет работоспособность, тогда как заявляемое УВУС свою работоспособность сохраняет при сохранении крутизны фронтов выходного сигнала, но возросшей задержке переключения.

Уровень энергопотребления заявляемого УВУС в целом сопоставим с энергопотреблением прототипа, так как выигрыш за счет увеличения крутизны сигналов компенсируется проигрышем за счет переключений дополнительных элементов схемы - 2И-НЕ 40 и ИЛЗ 50.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОЛЬЦЕВОЙ КМОП ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2011 |

|

RU2455755C1 |

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| ШИРОКОДИАПАЗОННЫЙ КОЛЬЦЕВОЙ ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2009 |

|

RU2397603C1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Формирователь импульсов на МДП-транзисторах | 1985 |

|

SU1569973A1 |

| Делитель частоты | 1984 |

|

SU1239858A1 |

| Источник питания | 1980 |

|

SU900376A1 |

| Входное устройство для электронных часов | 1990 |

|

SU1774471A1 |

Изобретение относится к интегральной электронной технике и может быть использовано в составе программируемых логических интегральных схем. Техническим результатом является уменьшение времени задержки переключения и увеличение крутизны переднего фронта сигнала, расширение диапазона питающих напряжений, увеличение предельной частоты работоспособности схемы и повышение шумового порога. Устройство содержит pull-up Р-канальные транзисторы, инвертор, логический элемент 2И-НЕ и инвертирующую линию задержки. Инвертор включает в себя Р-канальный транзистор и N-канальный транзистор. Элемент 2И-НЕ включает в себя Р-канальные транзисторы и N-канальные транзисторы. Инвертирующая линия задержки включает в себя нечетное число последовательно включенных инверторов, каждый из которых состоит из Р-канального транзистора и N-канального транзистора. 2 з.п. ф-лы, 12 ил.

1. Устройство восстановления уровня сигнала, имеющее один вход и один выход, содержащее подключенный истоком к шине питания Р-канальный транзистор, сток которого соединен с входом устройства, а затвор - с выходом устройства, и подключенный входом к входу устройства и выходом к выходу устройства инвертор, состоящий из подключенного истоком к шине питания Р-канального транзистора и подключенного истоком к шине земли N-канального транзистора, соединенные затворы которых являются входом инвертора, соединенные стоки - выходом инвертора, отличающееся тем, что устройство дополнительно содержит подключенный истоком к шине питания Р-канальный транзистор, сток которого соединен с входом устройства, логический элемент 2И-НЕ, имеющий два входа и один выход, и инвертирующую линию задержки, имеющую один вход и один выход, выход логического элемента 2И-НЕ соединен с затвором дополнительного Р-канального транзистора, первый вход логического элемента 2И-НЕ соединен с входом устройства, второй вход логического элемента 2И-НЕ соединен с выходом инвертирующей линии задержки, вход инвертирующей линии задержки соединен с входом устройства.

2. Устройство по п.1, логический элемент 2И-НЕ которого имеет два входа и один выход и содержит первый и второй Р-канальные транзисторы, истоки которых подключены к шине питания, первый N-канальный транзистор, исток которого подключен к шине земли, и второй N-канальный транзистор, исток которого соединен со стоком первого N-канального транзистора, соединенные стоки обоих Р-канальных транзисторов и второго N-канального транзистора являются выходом элемента 2И-НЕ, затворы первого Р-канального транзистора и второго N-канального транзистора соединены и образуют первый вход элемента 2И-НЕ, затворы второго Р-канального транзистора и первого N-канального транзистора соединены и образуют второй вход элемента 2И-НЕ.

3. Устройство по п.1, инвертирующая линия задержки которого имеет один вход и один выход и содержит нечетное число последовательно включенных инверторов, каждый из которых состоит из подключенного истоком к шине питания Р-канального транзистора и подключенного истоком к шине земли N-канального транзистора, соединенные затворы которых являются входом инвертора, соединенные стоки - выходом инвертора, вход первого инвертора является входом инвертирующей линии задержки, выход последнего инвертора является выходом инвертирующей линии задержки.

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 5894227 A1, 13.04.1999 | |||

| Устройство преобразования уровней логических сигналов на КМОП-транзисторах | 1986 |

|

SU1319273A1 |

| Преобразователь уровней (его варианты) | 1985 |

|

SU1256165A1 |

Авторы

Даты

2012-12-10—Публикация

2011-06-29—Подача