Настоящее изобретение относится к интегральной электронной технике и может быть использовано в составе сложно-функциональных блоков (СФ-блоков) высокочастотных синтезаторов сетки частот (ССЧ) тактовой синхронизации КМОП СБИС.

Современная методика проектирования СБИС предполагает широкое использование библиотеки ранее разработанных и верифицированных СФ-блоков. Технология изготовления кристалла СБИС подразумевает технологическую и конструктивную совместимость входящих в него СФ-блоков. При этом необходимо решать следующие проблемы:

- Минимизация площади, занимаемой СФ-блоками на кристалле СБИС.

- Минимизация энергопотребления и уровня помех по цепям питания.

- Повышение помехоустойчивости СФ-блоков.

В качестве СФ-блоков ССЧ тактовой синхронизации СБИС наибольшее распространение получили решения, основанные на использовании генератора, управляемого напряжением (ГУН), частота и фаза выходного сигнала которого стабилизируются с помощью контура импульсной фазовой автоподстройки частоты. Высокочастотный ГУН является источником помех по цепям питания для соседних СФ-блоков, а также сам подвержен влиянию помех, нарушающих его работу. Кроме того, во многих СБИС для уменьшения энергопотребления используются режимы динамической подстройки тактовой частоты под запросы исполняемого приложения. При этом диапазон перестройки ГУН СФ-блока ССЧ должен составлять не менее одной октавы.

При реализации СФ-блока ГУН должны быть выполнены следующие условия:

- Изготовление ГУН по той же технологии, что и ядро СБИС.

- ГУН должен иметь малую потребляемую мощность, а напряжение питания должно быть равным напряжению питания ядра СБИС.

- Амплитуда сигнала колебания ГУН должна быть близкой к значению напряжения питания во всем диапазоне частот. Длительности фронта и спада сигнала колебания должны быть примерно равны.

В качестве ГУН для СФ-блоков ССЧ тактовой синхронизации СБИС наибольшее распространение получили полностью интегральные кольцевые ГУН. Типовая структурная схема кольцевого КМОП ГУН представлена на фиг.1. В состав генератора входит блок 11 формирования управляющих напряжений Pent и Ncnt, задаваемых напряжением Vent, и генерирующее кольцо 12. Типовое генерирующее кольцо состоит из последовательно включенных инверторов с регулируемой напряжениями Pent и Ncnt длительностью распространения сигнала переключения. За счет общей отрицательной обратной связи в генерирующем кольце происходит вынужденное колебание, частота которого определяется количеством инверторов в кольце и общей задержкой их переключений. Выходной сигнал OUT с генерирующего кольца поступает на элементы, предназначенные для увеличения крутизны фронта и спада и нагрузочной способности выхода ГУН.

Для расширения диапазона частот типового генерирующего кольца требуется соответствующее изменение длительностей фронта и спада сигнала колебания в широких пределах. При этом более пологие фронт и спад колебания будут более чувствительны к помехам по цепям питания и по подложке кристалла СБИС. В результате чего моменты переключения элементов генерирующего кольца будут перемещаться от своего идеального местоположения во времени, тем самым увеличивая значение фазового шума в генерируемом сигнале.

Наиболее близким техническим решением к заявляемому изобретению является схема инвертора кольцевого КМОП ГУН, описанная в патенте Российской Федерации №2397603 (С1) «Широкодиапазонный кольцевой генератор, управляемый напряжением», МПК Н03В 5/08, Н03В 29/00 [1]. Эта схема выбрана в качестве прототипа заявляемого изобретения и изображена на фиг.2.

Общим признаком изобретения [1] с заявляемым изобретением является то, что в дополнении к изменению длительностей фронта и спада сигнала колебания, одновременно осуществляется изменение значений входных напряжений переключений схемы. Результатом такого комбинированного взаимодействия длительностей и уровней переключений является расширение диапазона рабочих частот генерирующего кольца, причем при меньших изменениях управляющего тока и длительностей фронта и спада сигнала колебания.

Однако, как показано в изобретении [1], для создания генерирующего кольца, имеющего диапазон частот, равный двум октавам, необходимо использовать последовательное включение трех таких схем. При этом общее количество транзисторов равно 18, что, несмотря на двухоктавный диапазон частот, является недостатком данной схемы.

Генерирующее кольцо, реализованное с использованием одной схемы изобретения [1] представлено в статье [2]: «Развитие схемотехники высокочастотного управляемого КМОП генератора для микросхемы класса «Система на кристалле»» /Зайцев А.А. // Информационные технологии в электротехнике и электроэнергетике: материалы 7-й Всерос. научн.-техн. конф. Чебоксары: Изд-во Чуваш, ун-та, 2010. - С.178-182. Генерирующее кольцо статьи [2] представлено на на фиг.3 и образовано последовательным включением схемы 21 изобретения [1] и буферного элемента 31 с регулируемой длительностью распространения сигнала переключения. При диапазоне генерируемых частот, равном одной октаве, общее количество транзисторов равно 12, что является недостатком данной схемы.

Техническим результатом заявляемого изобретения является создание микропотребляющего высокочастотного ГУН, состоящего из восьми транзисторов, изготавливаемых в стандартном цифровом КМОП техпроцессе, что определяет его компактность и конструктивную совместимость с другими блоками КМОП СБИС. Генератор обеспечивает диапазон частот, равный одной октаве, в котором поддерживает постоянную, близкую к симметричной, амплитуду сигнала, равную напряжению питания, что повышает его помехоустойчивость. При этом генератор имеет малое постоянное значение и малые пульсации потребляемого тока и сам не создает помех для других блоков СБИС.

Указанный результат достигается за счет того, что в схеме изобретения [1] с управляемыми током уровнями и длительностями фронта и спада сигнала переключения, содержащей: первый, второй, третий, четвертый и пятый выводы; первый, второй и третий Р-канальные транзисторы; первый, второй и третий N-канальные транзисторы; первый вывод первого Р-канального транзистора и первый вывод первого N-канального транзистора соединены между собой; второй вывод первого, третий вывод второго и второй вывод третьего Р-канальных транзисторов соединены между собой; второй вывод первого, третий вывод второго и второй вывод третьего N-канальных транзисторов соединены между собой; первый вывод второго Р-канального транзистора подключен к первому выводу устройства; первый вывод второго N-канального транзистора подключен к второму выводу устройства; второй вывод второго Р-канального транзистора и третий вывод третьего N-канального транзистора подключены к третьему выводу устройства; второй вывод второго N-канального транзистора и третий вывод третьего Р-канального транзистора подключены к четвертому выводу устройства; третий вывод первого и первый вывод третьего Р-канальных транзисторов, третий вывод первого и первый вывод третьего N-канальных транзисторов подключены к пятому выводу устройства, предложено ввести четвертый Р-канальный транзистор и четвертый N-канальный транзистор; первый вывод четвертого и первый вывод второго Р-канальных транзисторов соединить между собой; второй вывод четвертого и второй вывод первого Р-канальных транзисторов соединить между собой; третий вывод четвертого и первый вывод первого Р-канальных транзисторов соединить между собой; первый вывод четвертого и первый вывод второго N-канальных транзисторов соединить между собой; второй вывод четвертого и второй вывод первого N-канальных транзисторов соединить между собой; третий вывод четвертого и первый вывод первого N-канальных транзисторов соединить между собой.

В заявляемом изобретении, также как и в изобретении [1], при уменьшении управляющего напряжения на первом и втором выводах устройства и соответственном уменьшении значения тока переключения, происходит не только увеличение фронта и спада сигнала колебания, но и одновременно расхождение значений потенциалов напряжений переключений схемы, что приводит к увеличению задержки распространения сигнала колебания. И наоборот, при увеличении управляющего напряжения и соответственном увеличении значения тока переключения происходит не только обострение фронта и спада сигнала колебания, но и сближение потенциалов напряжений переключения схемы, что приводит к уменьшению задержки распространения сигнала колебания.

Новшеством в схеме КМОП ГУН заявляемого изобретения является то, что введенные четвертый Р-канальный транзистор и четвертый N-канальный транзистор создают внутреннюю нелинейную отрицательную обратную связь, зависящую от величин управляющих напряжений на первом и втором выводах устройства. Через данную связь соединенные вместе первые выводы первых Р- и N-канальных транзисторов попеременно подключаются к выходным потенциалам управляемых источников тока, образованных вторыми Р- и N-канальными транзисторами. В зависимости от состояния выхода генератора, подключение происходит или через четвертый Р- или четвертый N-канальные транзисторы, вызывая самовозбуждение ГУН. Нелинейность обратной связи обеспечивает расширение диапазона генерируемых частот до одной октавы, при этом амплитуда сигнала колебания на выходе генератора приближается к значению напряжения питания.

Заявляемое изобретение иллюстрируется следующими чертежами:

Фиг.1. Типовая структурная схема кольцевого КМОП ГУН.

Фиг.2. Схема инвертора кольцевого КМОП ГУН, представленная в изобретении [1] и выбранная в качестве прототипа заявляемого изобретения.

Фиг.3. Схема генерирующего кольца, представленного в статье [2].

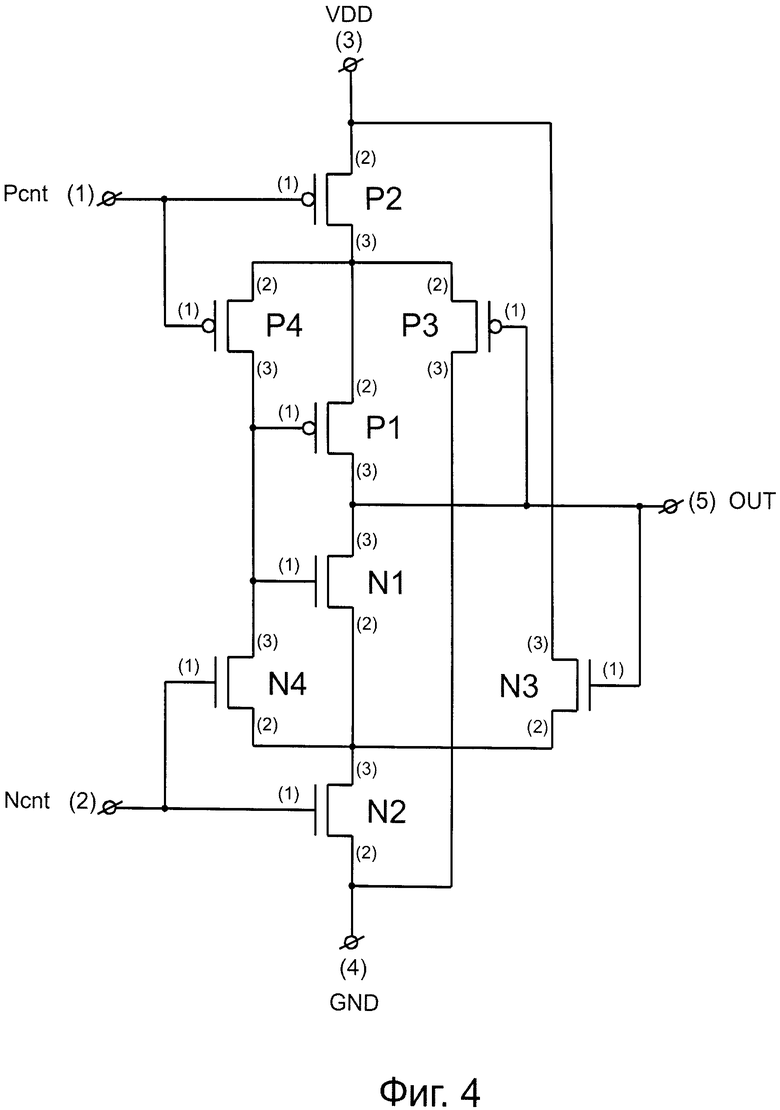

Фиг.4. Схема КМОП ГУН, заявляемая в данном изобретении.

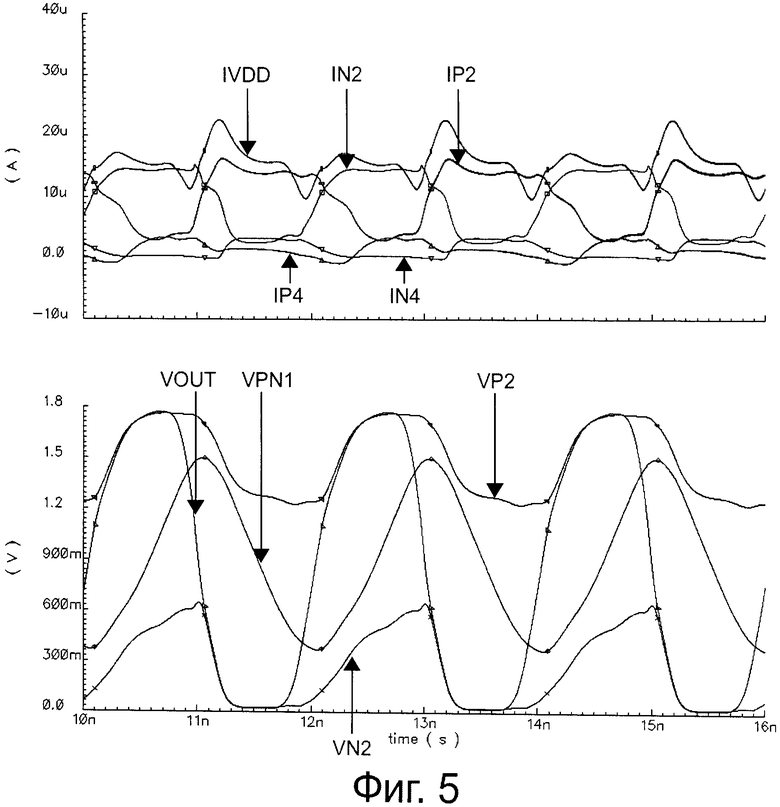

Фиг.5. Диаграммы сигналов заявляемой схемы КМОП ГУН при генерации выходного сигнала частотой 0,5 ГГц.

Фиг.6. Диаграммы сигналов заявляемой схемы КМОП ГУН при генерации выходного сигнала частотой 1,0 ГГц.

Заявляемая в данном изобретении схема КМОП ГУН представлена на фиг.4. Генератор имеет: первый (Pent) и второй (Ncnt) выводы для подключения управляющих сигналов, третий (VDD) и четвертый (GND) выводы для подключения напряжения и общего питания, пятый вывод (OUT) выходного генерируемого сигнала. В состав генератора входят: первый (Р1), второй (Р2), третий (Р3) и четвертый (Р4) Р-канальные транзисторы и первый (N1), второй (N2), третий (N3) и четвертый (N4) N-канальные транзисторы. Первый вывод транзистора Р1, третий вывод транзистора Р4, первый вывод транзистора N1 и третий вывод транзистора N4 соединены между собой. Второй вывод транзистора Р1, третий вывод транзистора Р2, второй вывод транзистора РЗ и второй вывод транзистора Р4 соединены между собой. Второй вывод транзистора N1, третий вывод транзистора N2, второй вывод транзистора N3 и второй вывод транзистора N4 соединены между собой. Первый вывод транзистора Р2 и первый вывод транзистора Р4 подключены к первому выводу Pent устройства. Первый вывод транзистора N2 и первый вывод транзистора N4 подключены к второму выводу Ncnt устройства. Второй вывод транзистора Р2 и третий вывод транзистора N3 подключены к третьему выводу VDD устройства. Второй вывод транзистора N2 и третий вывод транзистора Р3 подключены к четвертому выводу GND устройства. Третий вывод транзистора Р1, первый вывод транзистора РЗ, третий вывод транзистора N1 и первый вывод транзистора N3 подключены к пятому выводу OUT устройства.

Заявляемое изобретение работает следующим образом. Пусть на вывод VDD относительно вывода GND подано напряжение питания, на выводы Pent и Ncnt поданы соответствующие напряжения управления. Пусть потенциал напряжения на выводе OUT устройства находится в состоянии напряжения низкого уровня при котором каналы транзисторов Р1 и N3 закрыты, а каналы транзисторов Р3 и N1 открыты. Тогда, через транзисторы Р2 и РЗ от вывода VDD к выводу GND протекает ток, ограниченный напряжением управления на выводе Pent. При этом уровень напряжения на выводе 3 транзистора Р2 зависит от величины протекающего через него тока и значения сопротивления открытого канала транзистора Р3. Чем меньше значение протекающего тока, тем выше уровень падения напряжения между выводами 2 и 3 транзистора Р2 и, соответственно, ниже потенциал напряжения между выводами 1 и 2 транзистора Р4, в результате чего транзистор Р4 переходит в закрытое состояние. Одновременно, через открытый канал транзистора N2 потенциал напряжения на его выводе 3 стремится к уровню вывода GND, увеличивая потенциал напряжения между выводами 1 и 2 транзистора N4. В результате, канал транзистора N4 открывается и потенциал напряжения на первых выводах транзисторов Р1 и N1 стремится к уровню GND. Причем величина тока, перезаряжающего паразитную емкость этого узла, зависит от значения управляющего напряжения Ncnt. Когда потенциал напряжения на первых выводах транзисторов Р1 и N1 достигнет соответствующего уровня от напряжения между вторыми выводами транзисторов Р1 и N1, канал транзистора Р1 откроется, а канал транзистора N1 закроется и вывод OUT устройства переключится в состояние напряжения высокого уровня. При этом ток переключения зависит от значения управляющего напряжения Pent.

Наличие потенциала напряжения высокого уровня на выводе OUT закрывает канал транзистора РЗ и открывает канал транзистора N3. Через транзисторы N3 и N2 от вывода VDD к выводу GND протекает ток, ограниченный напряжением сигнала управления на выводе Ncnt. При этом уровень напряжения на выводе 3 транзистора N2 зависит от величины протекающего через него тока и значения сопротивления открытого канала транзистора N3. Чем меньше значение протекающего тока, тем выше уровень падения напряжения между выводами 2 и 3 транзистора N2 и, соответственно, ниже потенциал напряжения между выводами 1 и 2 транзистора N4, в результате чего транзистор N4 переходит в закрытое состояние. Одновременно, через открытый канал транзистора Р2 потенциал напряжения на его выводе 3 стремится к уровню вывода VDD, увеличивая потенциал напряжения между выводами 1 и 2 транзистора Р4. В результате канал транзистора Р4 открывается и потенциал напряжения на первых выводах транзисторов Р1 и N1 стремится к уровню VDD. Причем величина тока, перезаряжающего паразитную емкость этого узла, зависит от значения управляющего напряжения Pent. Когда потенциал напряжения на первых выводах транзисторов Р1 и N1 достигнет соответствующего уровня от напряжения между вторыми выводами транзисторов Р1 и N1, канал транзистора Р1 закроется, а канал транзистора N1 откроется и вывод OUT устройства переключится в состояние напряжения низкого уровня. При этом ток переключения зависит от значения управляющего напряжения Ncnt.

Таким образом, в заявляемой схеме КМОП ГУН возникает самовозбуждение с частотой, зависящей от величины токов переключения схемы, управляемых значениями потенциалов напряжений на выводах Pent и Ncnt. При генерации сигнала низкой частоты при уменьшении значения тока переключения происходит не только завал фронта и спада сигнала колебания, но и одновременно расхождение уровней потенциалов напряжений на первых выводах транзисторов Р1 и N1, требуемых для переключений третьих выводов транзисторов Р1 и N1 в направлении VDD и в направлении GND. Это приводит к увеличению задержки переключения сигнала, а значит, к уменьшению частоты колебания. При генерации сигнала высокой частоты при увеличении значения тока переключения одновременно происходит не только обострение фронта и спада сигнала колебания, но и сближение требуемых уровней потенциалов напряжений для переключений транзисторов Р1 и N1, что приводит к уменьшению задержки переключения сигнала, а значит, к увеличению частоты колебания. Результатом взаимодействия этих факторов является расширение диапазона генерируемых частот, в котором амплитуда генерируемого сигнала поддерживается постоянной и близкой к значению напряжения питания.

Для защиты ГУН СФ-блока ССЧ от помех по цепям питания, по подложке и посредством электромагнитных волн, в его конструкции применяются охранные кольца и электростатическое экранирование. Электростатическое экранирование осуществляется слоями металлизации, имеющими контакты с подложкой по всему периметру СФ-блока. Дополнительные экраны, располагаемые над Р-канальными транзисторами, соединяются с потенциалом VDD, а располагаемые над N-канальными транзисторами, - с потенциалом GND.

На фиг.5 и фиг.6. представлены диаграммы сигналов заявляемой схемы ГУН, реализованного по технологическому процессу КМОП 180 нм. Диаграммы на фиг.5 соответствуют частоте выходного сигнала, равной 0,5 ГГц. На фиг.6 частота выходного сигнала равна 1,0 ГГц. В верхней части чертежей представлены диаграммы токов, в нижней части чертежей - диаграммы напряжений.

Условные обозначения на диаграммах соответствуют:

IVDD - ток, потребляемый схемой по линии напряжения питания VDD;

IР2 - ток, протекающий через транзистор Р2;

IN2 - ток, протекающий через транзистор N2;

IР4 - ток, протекающий через транзистор Р4;

IN4 - ток, протекающий через транзистор N4;

VPN1 - напряжение нелинейной обратной связи на первых выводах транзисторов Р1 и N1;

VP2 - напряжение на выводе 3 транзистора Р2;

VN2 - напряжение на выводе 3 транзистора N2;

VOUT - напряжение на выводе OUT.

В обоих случаях наблюдаются практически симметричные сигналы колебаний, происходящих относительно уровня половины напряжения питания с коэффициентом заполнения, равным 0,5±5%. При этом амплитуда сигнала нелинейной обратной связи VPN1 превышает половину значения напряжения питания, а амплитуда сигнала OUT поддерживается близкой к напряжению питания схемы, равному 1,8 В. При генерации сигнала частотой 0,5 ГГц среднее значение потребляемого тока составляет 16 мкА (30 мкВт), величина пульсаций тока составляет +7/-6 мкА. При генерации сигнала частотой 1,0 ГГц среднее значение потребляемого тока составляет 27 мкА (50 мкВт), величина пульсаций +6/-7 мкА.

Диапазон генерируемых частот в заявляемой схеме КМОП ГУН может быть изменен подключением конденсатора соответствующей емкости: между выводом OUT и выводами VDD или GND; между первыми выводами транзисторов Р1 и N1 и выводами VDD или GND; между первыми выводами транзисторов Р1 и N1 и выводом OUT; комбинацией данных подключений. Требуемый конденсатор может быть образован слоями металлизации, транзисторными структурами или иным способом, удобным при интегральной реализации.

Заявляемая схема КМОП ГУН состоит из восьми транзисторов, изготавливаемых в стандартном цифровом КМОП техпроцессе, что определяет его компактность и конструктивную совместимость с другими блоками КМОП СБИС. Благодаря образованной внутренней нелинейной отрицательной обратной связи генератор вырабатывает сигнал с диапазоном частот, равным одной октаве, в котором поддерживает постоянную, близкую к симметричной амплитуду выходного сигнала колебания, равную напряжению питания, что повышает его помехоустойчивость. При этом генератор имеет малое постоянное значение и малые пульсации потребляемого тока и не создает помех для других блоков СБИС.

Совокупность этих качеств позволяет использовать заявляемую схему КМОП ГУН при разработке микропотребляющих СФ-блоков ССЧ тактовой синхронизации, предназначенных для применения в составе СБИС самого широкого назначения от АЦП до микропроцессоров.

Настоящее изобретение относится к интегральной электронной технике и может быть использовано в составе сложно-функциональных блоков высокочастотных синтезаторов сетки частот. Технический результат - поддержание постоянной, близкой к симметричной амплитуды выходного сигнала, повышение помехоустойчивости. Октавный микропотребляющий высокочастотный генератор, управляемый напряжением, содержит четыре Р-канальных транзистора, четыре N-канальных транзистора. Связи между транзисторами обеспечивают режим самовозбуждения, а нелинейность обратной связи, зависящей от управляющих напряжений, обеспечивает расширение диапазона генерируемых частот до одной октавы. 6 ил.

Октавный микропотребляющий высокочастотный генератор, управляемый напряжением, содержащий: первый, второй, третий, четвертый и пятый выводы; первый, второй и третий Р-канальные транзисторы; первый, второй и третий N-канальные транзисторы; первый вывод первого Р-канального транзистора и первый вывод первого N-канального транзистора соединены между собой; второй вывод первого, третий вывод второго и второй вывод третьего Р-канальных транзисторов соединены между собой; второй вывод первого, третий вывод второго и второй вывод третьего N-канальных транзисторов соединены между собой; первый вывод второго Р-канального транзистора подключен к первому выводу устройства; первый вывод второго N-канального транзистора подключен к второму выводу устройства; второй вывод второго Р-канального транзистора и третий вывод третьего N-канального транзистора подключены к третьему выводу устройства; второй вывод второго N-канального транзистора и третий вывод третьего Р-канального транзистора подключены к четвертому выводу устройства; третий вывод первого и первый вывод третьего Р-канальных транзисторов, третий вывод первого и первый вывод третьего N-канальных транзисторов подключены к пятому выводу устройства, отличающийся тем, что введены четвертый Р-канальный транзистор и четвертый N-канальный транзистор; первый вывод четвертого и первый вывод второго Р-канальных транзисторов соединены между собой; второй вывод четвертого и второй вывод первого Р-канальных транзисторов соединены между собой; третий вывод четвертого и первый вывод первого Р-канальных транзисторов соединены между собой; первый вывод четвертого и первый вывод второго N-канальных транзисторов соединены между собой; второй вывод четвертого и второй вывод первого N-канальных транзисторов соединены между собой; третий вывод четвертого и первый вывод первого N-канальных транзисторов соединены между собой.

| ШИРОКОДИАПАЗОННЫЙ КОЛЬЦЕВОЙ ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2009 |

|

RU2397603C1 |

| КОЛЬЦЕВОЙ КМОП ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2011 |

|

RU2455755C1 |

| ШИРОКОДИАПАЗОННЫЙ ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2007 |

|

RU2330377C1 |

| US 20080174364 A1, 24.07.2008. | |||

Авторы

Даты

2013-06-20—Публикация

2012-07-16—Подача