Область техники, к которой относится изобретение

Изобретение относится к модулю полупроводникового элемента и способу его изготовления и является подходящим для полупроводникового элемента, имеющего высокую выходную мощность, такого как, например, силовой транзистор.

Уровень техники

Силовые полупроводниковые элементы, имеющие значительную выходную мощность, но формирующие большие величины тепла, такие как биполярные транзисторы с изолированным затвором (в дальнейшем в этом документе, называемые IGBT), должны охлаждаться, чтобы обеспечивать надежность и срок службы для своих функций. В последние годы, использование таких силовых полупроводниковых элементов расширено, поскольку они применены при управлении электродвигателями электрических автомобилей и т.д. Следовательно, помимо повышения выходной мощности, требуется повышение надежности, увеличение срока службы и т.п.

Патентный документ 1. Публикация заявки на патент (Япония) номер Hei 6-188363.

Патентный документ 2. Брошюра публикации международной заявки на патент номер 98/43301.

Сущность изобретения

Проблемы, которые должны быть разрешены изобретением

Предусмотрена модульная структура силового полупроводникового элемента, например, в которой элемент монтируется прямо или косвенно на подложке, изготовленной из металла, которая имеет превосходное тепловое излучение, и проводные соединения с внешними контактными выводами формируются отдельно друг от друга посредством проводного связывания (патентный документ 1). Поскольку эта структура является открытой на стороне верхней поверхности элемента, структура имеет проблему неспособности достижения достаточной эффективности охлаждения. Помимо этого, способ формирования проводных соединений с внешними контактными выводами отдельно друг от друга посредством проводного связывания требует сложных и трудных процессов, а также большого числа процессов. Следовательно, имеется также проблема высоких производственных затрат.

Между тем, также существует модульная структура, в которой сверху и снизу силового полупроводникового элемента размещаются подложки, изготовленные из металла, который имеет превосходное тепловое излучение, допуская высвобождение тепла с верхней и нижней поверхностей элемента (патентный документ 2). В этой структуре, тем не менее, электрическое соединение устанавливается не посредством связывания, а посредством приведения металлических подложек в прижимной контакт с элементом, чтобы ослаблять нагрузки, вызываемые посредством теплообразования. Поэтому электрическое соединение металлических подложек с элементом является недостаточным, что затрудняет применение модульной структуры к элементам с высокой выходной мощностью. Кроме того, термическое соединение металлических подложек с элементом также является недостаточным (условие удельной теплопроводности между различными элементами, связанными между собой, задано в данном документе как термическое соединение). Соответственно, имеется проблема неспособности достижения ожидаемой эффективности теплового излучения.

Дополнительно, в вышеуказанных модульных структурах, предел улучшения всего модуля определяется посредством пределов припоя и проводов для межсоединений, полимера для уплотнения и т.п. с точки зрения их термостойкости, стойкости к тепловому циклическому воздействию и вибростойкости. С учетом неспособности к удовлетворению термостойкости, стойкости к тепловому циклическому воздействию и вибростойкости, требуемых для электрических автомобилей и т.п., эти модульные структуры не допускают обеспечение достаточной надежности. Например, элемент в модуле может быть исправным, но межсоединения могут быть повреждены, ухудшая функции модуля в целом и тем самым понижая надежность и срок службы модуля.

Дополнительно, имеется проблема для вышеуказанных модульных структур и т.п. в том, чтобы достигать как эффективности теплового излучения, так и надежности, касающейся связывания между подложкой(-ками) и элементом и/или между подложкой и ребром для теплового излучения. Например, использование связующего вещества для связывания может приводить к проблеме в определенной степени низкой удельной теплопроводности и увеличения числа процессов. Использование диффузного связывания или анодного связывания для связывания может приводить к таким проблемам, что типы материалов ограничены для целей связывания и что, поскольку нагрев участвует в связывании, определенное время требуется для охлаждения, а также на модуль оказывает влияние тепло (формирует термическое напряжение).

Настоящее изобретение осуществлено в свете вышеуказанных проблем и имеет цель, чтобы предоставлять модуль полупроводникового элемента, имеющий высокую надежность, отличное электрическое соединение и термическое соединение и допускающий обеспечение достаточной эффективности охлаждения, а также предоставлять способ для изготовления модуля.

Средство разрешения проблем

Модуль полупроводникового элемента согласно первому изобретению для разрешения проблем - это модуль полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется, при этом полупроводниковый элемент включает в себя множество поверхностей электродов, сформированных на части поверхности полупроводникового элемента на одной стороне, первая изолирующая подложка включает в себя множество первых поверхностей межсоединений, сформированных на поверхности первой изолирующей подложки на одной стороне таким образом, чтобы соответствовать каждой из поверхностей электродов полупроводникового элемента, и полупроводниковый элемент монтируется на первой изолирующей подложке и второй изолирующей подложке посредством связывания поверхности полупроводникового элемента на одной стороне с первой изолирующей подложкой при помощи связывания при комнатной температуре таким образом, что поверхности электродов полупроводникового элемента устанавливаются так, чтобы располагаться напротив первых поверхностей межсоединений, и связывания поверхности полупроводникового элемента на другой стороне со второй изолирующей подложкой посредством связывания при комнатной температуре.

Модуль полупроводникового элемента согласно второму изобретению для разрешения проблем - это модуль полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется, при этом полупроводниковый элемент включает в себя множество поверхностей электродов, сформированных на части поверхностей полупроводникового элемента на обеих сторонах, первая изолирующая подложка включает в себя первую поверхность межсоединений, сформированную на поверхности первой изолирующей подложки на одной стороне таким образом, чтобы соответствовать поверхностям электродов полупроводникового элемента на одной стороне, вторая изолирующая подложка включает в себя вторую поверхность межсоединений, сформированную на поверхности второй изолирующей подложки на одной стороне таким образом, чтобы соответствовать поверхностям электродов полупроводникового элемента на другой стороне, и полупроводниковый элемент монтируется на первой изолирующей подложке и второй изолирующей подложке посредством связывания поверхности полупроводникового элемента на одной стороне с первой изолирующей подложкой при помощи связывания при комнатной температуре таким образом, что поверхности электродов полупроводникового элемента на одной стороне устанавливаются так, чтобы располагаться напротив первой поверхности межсоединений, и связывания поверхности полупроводникового элемента на другой стороне со второй изолирующей подложкой посредством связывания при комнатной температуре таким образом, что поверхности электродов полупроводникового элемента на другой стороне устанавливаются так, чтобы располагаться напротив второй поверхности межсоединений.

Модуль полупроводникового элемента согласно третьему изобретению для разрешения проблем - это модуль полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется, при этом полупроводниковый элемент включает в себя множество поверхностей электродов, сформированных по всей поверхности полупроводникового элемента на одной стороне, первая изолирующая подложка включает в себя множество первых поверхностей межсоединений, сформированных на поверхности первой изолирующей подложки на одной стороне таким образом, чтобы соответствовать каждой из поверхностей электродов полупроводникового элемента, и полупроводниковый элемент монтируется на первой изолирующей подложке и второй изолирующей подложке посредством связывания поверхностей электродов полупроводникового элемента с первыми поверхностями межсоединений при помощи связывания при комнатной температуре и связывания поверхности полупроводникового элемента на другой стороне со второй изолирующей подложкой при помощи связывания при комнатной температуре.

Модуль полупроводникового элемента согласно четвертому изобретению для разрешения проблем - это модуль полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется, при этом полупроводниковый элемент включает в себя множество поверхностей электродов, сформированных по всем поверхностям полупроводникового элемента на обеих сторонах, первая изолирующая подложка включает в себя первую поверхность межсоединений, сформированную на поверхности первой изолирующей подложки на одной стороне таким образом, чтобы соответствовать поверхностям электродов полупроводникового элемента на одной стороне, вторая изолирующая подложка включает в себя вторую поверхность межсоединений, сформированную на поверхности второй изолирующей подложки на одной стороне таким образом, чтобы соответствовать поверхностям электродов полупроводникового элемента на другой стороне, и полупроводниковый элемент монтируется на первой изолирующей подложке и второй изолирующей подложке посредством связывания поверхностей электродов полупроводникового элемента на одной стороне с первой поверхностью межсоединений при помощи связывания при комнатной температуре и связывания поверхностей электродов полупроводникового элемента на другой стороне со второй поверхностью межсоединений посредством связывания при комнатной температуре.

Модуль полупроводникового элемента согласно пятому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с первого по четвертое, в котором, по меньшей мере, одна из первой изолирующей подложки и второй изолирующей подложки включает в себя проводные межсоединения, которые соединяются с соответствующей одной из первой поверхности межсоединений и второй поверхности межсоединений и которые являются соединяемыми с внешней средой, и проводные межсоединения формируются так, чтобы проникать, по меньшей мере, через одну из первой изолирующей подложки и второй изолирующей подложки в направлении ее толщины.

Модуль полупроводникового элемента согласно шестому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с первого по четвертое, в котором, по меньшей мере, одна из первой изолирующей подложки и второй изолирующей подложки включает в себя проводные межсоединения, которые соединяются с соответствующей одной из первой поверхности межсоединений и второй поверхности межсоединений и которые являются соединяемыми с внешней средой, и проводные межсоединения являются любыми из следующего: проводные соединения, которые формируются таким образом, чтобы отходить от поверхности любой из первой изолирующей подложки и второй изолирующей подложки в боковом направлении, а также проникать через внешнюю периферийную часть между первой изолирующей подложкой и второй изолирующей подложкой в боковом направлении; и проводные соединения, которые формируются в канавке, сформированной таким образом, чтобы отходить от поверхности любой из первой изолирующей подложки и второй изолирующей подложки в боковом направлении, а также проникать, по меньшей мере, через одну из первой изолирующей подложки и второй изолирующей подложки в боковом направлении.

Модуль полупроводникового элемента согласно седьмому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с первого с шестое, в котором, по меньшей мере, одна из поверхностей электродов, первой поверхности межсоединений и второй поверхности межсоединений формируется так, чтобы иметь плоскую поверхность.

Модуль полупроводникового элемента согласно восьмому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с первого по седьмое, в котором, по меньшей мере, одна из поверхностей электродов, первой поверхности межсоединений и второй поверхности межсоединений изготовлена из металла.

Модуль полупроводникового элемента согласно девятому изобретению для разрешения проблем - это модуль полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется с помощью герметизирующего элемента, при этом полупроводниковый элемент включает в себя металлические и плоские поверхности электродов, сформированные на всех или практически на всех поверхностях полупроводникового элемента на обеих сторонах, первая изолирующая подложка включает в себя металлическую и плоскую первую поверхность межсоединений, сформированную на поверхности первой изолирующей подложки на одной стороне таким образом, чтобы соответствовать поверхностям электродов полупроводникового элемента на одной стороне, герметизирующий элемент включает в себя металлические первые сквозные межсоединения, соединенные с первой поверхностью межсоединений и предусмотренные так, чтобы проникать через герметизирующий элемент, вторая изолирующая подложка включает в себя металлическую и плоскую вторую поверхность межсоединений, сформированную на поверхности второй изолирующей подложки на одной стороне таким образом, чтобы соответствовать поверхностям электродов полупроводникового элемента на другой стороне, металлические вторые сквозные межсоединения, соединенные со второй поверхностью межсоединений и предусмотренные так, чтобы проникать через вторую изолирующую подложку, и металлические третьи сквозные межсоединения, соединенные с первыми сквозными межсоединениями и предусмотренные так, чтобы проникать через вторую изолирующую подложку, и полупроводниковый элемент монтируется на первой изолирующей подложке и второй изолирующей подложке посредством связывания первой изолирующей подложки с помощью герметизирующего элемента при помощи связывания при комнатной температуре, чтобы тем самым связывать первую поверхность межсоединений с первыми сквозными межсоединениями, и связывания поверхностей электродов полупроводникового элемента с первой поверхностью межсоединений и второй поверхностью межсоединений при помощи связывания при комнатной температуре.

Модуль полупроводникового элемента согласно десятому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с третьего по девятое, в котором множество деформируемых и тонких столбчатых электродов предусмотрено на поверхностях из либо первой и второй поверхностей межсоединений, либо поверхностей электродов полупроводникового элемента, либо и тех, и других, и, по меньшей мере, одна из первой поверхности межсоединений и второй поверхности межсоединений связывается с поверхностями электродов полупроводникового элемента с множеством столбчатых электродов между ними при помощи связывания при комнатной температуре.

Модуль полупроводникового элемента согласно одиннадцатому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно десятому изобретению, в котором буртики на краях частей связывания столбчатых электродов округлены, причем буртики находятся либо на сторонах ближе к первой и второй поверхностям межсоединений, либо на сторонах ближе к поверхностям электродов полупроводникового элемента, либо на обеих сторонах.

Модуль полупроводникового элемента согласно двенадцатому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с пятого по одиннадцатое, в котором средство охлаждения для охлаждения модуля полупроводникового элемента предусмотрено для внешней поверхности, по меньшей мере, одной из первой изолирующей подложки и второй изолирующей подложки при помощи связывания при комнатной температуре, в случае если как первая изолирующая подложка, так и вторая изолирующая подложка либо или первая изолирующая подложка, или вторая изолирующая подложка не имеют межсоединений, проникающих через них в направлении толщины.

Способ для изготовления модуля полупроводникового элемента согласно тринадцатому изобретению для разрешения проблем - это способ для изготовления модуля полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется, при этом способ содержит: формирование множества поверхностей электродов на части поверхности полупроводникового элемента на одной стороне, формирование множества первых поверхностей межсоединений на поверхности первой изолирующей подложки на одной стороне таким образом, что первые поверхности межсоединений соответствуют каждой из поверхностей электродов полупроводникового элемента, и монтаж полупроводникового элемента на первой изолирующей подложке и второй изолирующей подложке посредством связывания поверхности полупроводникового элемента на одной стороне с первой изолирующей подложкой при помощи связывания при комнатной температуре таким образом, что поверхности электродов полупроводникового элемента задаются так, чтобы располагаться напротив первых поверхностей межсоединений, и связывания поверхности полупроводникового элемента на другой стороне со второй изолирующей подложкой посредством связывания при комнатной температуре.

Способ для изготовления модуля полупроводникового элемента согласно четырнадцатому изобретению для разрешения проблем - это способ для изготовления модуля полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется, при этом способ содержит: формирование множества поверхностей электродов на части поверхностей полупроводникового элемента на обеих сторонах; формирование первой поверхности межсоединений на поверхности первой изолирующей подложки на одной стороне таким образом, что первая поверхность межсоединений соответствует поверхностям электродов полупроводникового элемента на одной стороне; формирование второй поверхности межсоединений на поверхности второй изолирующей подложки на одной стороне таким образом, что вторая поверхность межсоединений соответствует поверхностям электродов полупроводникового элемента на другой стороне; и полупроводниковый элемент монтируется на первой изолирующей подложке и второй изолирующей подложке посредством связывания поверхности полупроводникового элемента на одной стороне с первой изолирующей подложкой при помощи связывания при комнатной температуре таким образом, что поверхности электродов полупроводникового элемента на одной стороне задаются так, чтобы располагаться напротив первой поверхности межсоединений, и связывания поверхности полупроводникового элемента на другой стороне со второй изолирующей подложкой посредством связывания при комнатной температуре таким образом, что поверхности электродов полупроводникового элемента на другой стороне задаются так, чтобы располагаться напротив второй поверхности межсоединений.

Способ для изготовления модуля полупроводникового элемента согласно пятнадцатому изобретению для разрешения проблем - это способ для изготовления модуля полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется, при этом способ содержит: формирование множества поверхностей электродов по всей поверхности полупроводникового элемента на одной стороне; формирование множества первых поверхностей межсоединений на поверхности первой изолирующей подложки на одной стороне таким образом, что первые поверхности межсоединений соответствуют каждой из поверхностей электродов полупроводникового элемента на одной стороне; и монтаж полупроводникового элемента на первой изолирующей подложке и второй изолирующей подложке посредством связывания поверхностей электродов полупроводникового элемента с первыми поверхностями межсоединений при помощи связывания при комнатной температуре и связывания поверхности полупроводникового элемента на другой стороне со второй изолирующей подложкой при помощи связывания при комнатной температуре.

Способ для изготовления модуля полупроводникового элемента согласно шестнадцатому изобретению для разрешения проблем - это способ для изготовления модуля полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется, при этом способ содержит: формирование множества поверхностей электродов по всем поверхностям полупроводникового элемента на обеих сторонах; формирование первой поверхности межсоединений на поверхности первой изолирующей подложки на одной стороне таким образом, что первая поверхность межсоединений соответствует поверхностям электродов полупроводникового элемента на одной стороне; формирование второй поверхности межсоединений на поверхности второй изолирующей подложки на одной стороне таким образом, что вторая поверхность межсоединений соответствует поверхностям электродов полупроводникового элемента на другой стороне; и монтаж полупроводникового элемента на первой изолирующей подложке и второй изолирующей подложке посредством связывания поверхностей электродов полупроводникового элемента на одной стороне с первой поверхностью межсоединений при помощи связывания при комнатной температуре и связывания поверхностей электродов полупроводникового элемента на другой стороне со второй поверхностью межсоединений посредством связывания при комнатной температуре.

Способ для изготовления модуля полупроводникового элемента согласно семнадцатому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с тринадцатого по шестнадцатое, в котором проводные межсоединения формируются, по меньшей мере, в одной из первой изолирующей подложки и второй изолирующей подложки таким образом, чтобы соединяться с соответствующей одной из первой поверхности межсоединений и второй поверхности межсоединений и проникать, по меньшей мере, через одну из первой изолирующей подложки и второй изолирующей подложки в направлении ее толщины так, что проводные межсоединения являются соединяемыми с внешней средой.

Способ для изготовления модуля полупроводникового элемента согласно восемнадцатому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с тринадцатого по шестнадцатое, в котором проводные межсоединения, которые соединяются с любой из первой поверхности межсоединений и второй поверхности межсоединений и которые являются соединяемыми с внешней средой, формируются посредством следующего: формирование межсоединений таким образом, что межсоединения выдаются из поверхности любой из первой изолирующей подложки и второй изолирующей подложки в боковом направлении и проникают через внешнюю периферийную часть между первой изолирующей подложкой и второй изолирующей подложкой в боковом направлении; или формирование канавки и межсоединений в канавке таким образом, что канавка и межсоединения выдаются из поверхности любой из первой изолирующей подложки и второй изолирующей подложки в боковом направлении и проникают, по меньшей мере, через одну из первой изолирующей подложки и второй изолирующей подложки в боковом направлении.

Способ для изготовления модуля полупроводникового элемента согласно девятнадцатому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с тринадцатого по восемнадцатое, в котором, по меньшей мере, одна из поверхностей электродов, первой поверхности межсоединений и второй поверхности межсоединений формируется так, чтобы иметь плоскую поверхность.

Способ для изготовления модуля полупроводникового элемента согласно двадцатому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с тринадцатого по девятнадцатое, в котором, по меньшей мере, одна из поверхностей электродов, первой поверхности межсоединений и второй поверхности межсоединений изготовлена из металла.

Способ для изготовления модуля полупроводникового элемента согласно двадцать первому изобретению для разрешения проблем - это способ для изготовления модуля полупроводникового элемента, в котором, по меньшей мере, один полупроводниковый элемент размещается между первой изолирующей подложкой, имеющей высокую удельную теплопроводность, и второй изолирующей подложкой, имеющей высокую удельную теплопроводность, и внешняя периферийная часть между первой изолирующей подложкой и второй изолирующей подложкой герметизируется с помощью герметизирующего элемента, при этом способ содержит: формирование металлических и плоских поверхностей электродов на всех или практически на всех поверхностях полупроводникового элемента на обеих сторонах; формирование металлической и плоской первой поверхности межсоединений на поверхности первой изолирующей подложки на одной стороне таким образом, что первая поверхность межсоединений соответствует поверхностям электродов полупроводникового элемента на одной стороне; формирование металлических первых сквозных межсоединений, проникающих через герметизирующий элемент и соединенных с первой поверхностью межсоединений; формирование металлической и плоской второй поверхности межсоединений на поверхности второй изолирующей подложки на одной стороне таким образом, что вторая поверхность межсоединений соответствует поверхностям электродов полупроводникового элемента на другой стороне; формирование металлических вторых сквозных межсоединений, проникающих через вторую изолирующую подложку и соединенных со второй поверхностью межсоединений; формирование металлических третьих сквозных межсоединений, проникающих через вторую изолирующую подложку и соединенных с первыми сквозными межсоединениями; и монтаж полупроводникового элемента на первой изолирующей подложке и второй изолирующей подложке посредством связывания первой изолирующей подложки с помощью герметизирующего элемента при помощи связывания при комнатной температуре, чтобы тем самым связывать первую поверхность межсоединений с первыми сквозными межсоединениями, и связывания поверхностей электродов полупроводникового элемента с первой поверхностью межсоединений и второй поверхностью межсоединений при помощи связывания при комнатной температуре.

Способ для изготовления модуля полупроводникового элемента согласно двадцать второму изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с пятнадцатого по двадцать первое, в котором множество деформируемых и тонких столбчатых электродов формируется на поверхностях из либо первой и второй поверхностей межсоединений, либо поверхностей электродов полупроводникового элемента, либо и тех, и других, и, по меньшей мере, одна из первой поверхности межсоединений и второй поверхности межсоединений связывается с поверхностями электродов полупроводникового элемента с множеством столбчатых электродов между ними при помощи связывания при комнатной температуре.

Способ для изготовления модуля полупроводникового элемента согласно двадцать третьему изобретению для разрешения проблем - это модуль полупроводникового элемента согласно двадцать второму изобретению, в котором буртики на краях частей связывания столбчатых электродов округлены, причем буртики находятся либо на сторонах ближе к первой и второй поверхностям межсоединений, либо на сторонах ближе к поверхностям электродов полупроводникового элемента, либо на обеих сторонах.

Способ для изготовления модуля полупроводникового элемента согласно двадцать четвертому изобретению для разрешения проблем - это модуль полупроводникового элемента согласно любому из изобретений с семнадцатого по двадцать третье, в котором средство охлаждения для охлаждения модуля полупроводникового элемента связывается с внешней поверхностью, по меньшей мере, одной из первой изолирующей подложки и второй изолирующей подложки при помощи связывания при комнатной температуре, в случае если как первая изолирующая подложка, так и вторая изолирующая подложка либо или первая изолирующая подложка, или вторая изолирующая подложка не имеют межсоединений, проникающих через них в направлении толщины.

Преимущество изобретения

Согласно настоящему изобретению, поверхности электродов формируются на поверхности(ях) полупроводникового элемента, и также поверхности межсоединений формируются на керамических подложках, имеющих высокую удельную теплопроводность. Затем, полупроводниковый элемент связывается с подложками при помощи связывания при комнатной температуре. Это позволяет получать модуль полупроводникового элемента, имеющий структуру, в которой обеспечивается электрическое соединение и эффективность теплового излучения является высокой. Помимо этого, поскольку связывание выполняется посредством связывания при комнатной температуре, прочность связи между связывающими элементами становится эквивалентной прочности связи сухих материалов, так что достигается высокая жесткость. Кроме того, связывание при комнатной температуре не требует нагрева на этапах изготовления, так что термическое напряжение не формируется. Следовательно, стойкость к тепловому циклическому воздействию и вибростойкость повышаются, что позволяет повышать износостойкость и надежность модуля полупроводникового элемента. Дополнительно, при такой структуре, процесс формирования межсоединений, а также процесс монтажа упрощаются, сокращая число требуемых компонентов. Это дает возможность значительного уменьшения производственных затрат для процессов изготовления.

Краткое описание чертежей

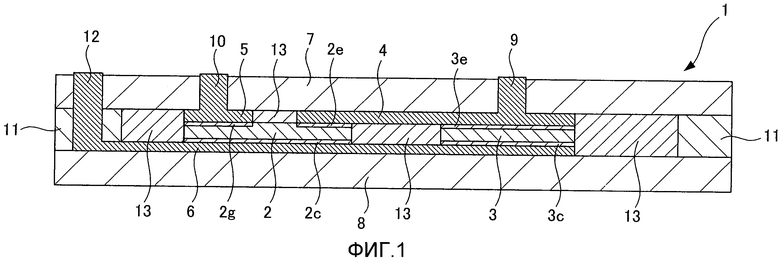

Фиг. 1 показывает схему в поперечном разрезе, иллюстрирующую примерный вариант осуществления (вариант осуществления 1) модуля полупроводникового элемента согласно настоящему изобретению.

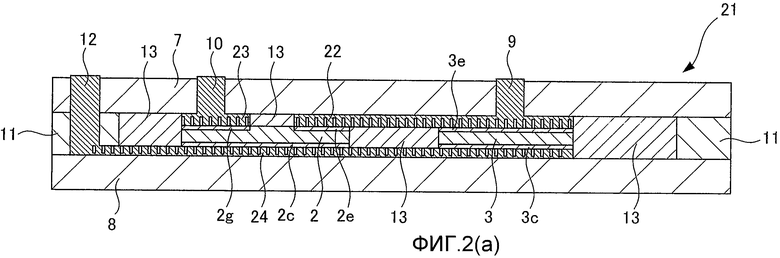

Фиг. 2 показывает схемы в поперечном разрезе, иллюстрирующие другой примерный вариант осуществления (вариант осуществления 2) модуля полупроводникового элемента согласно настоящему изобретению.

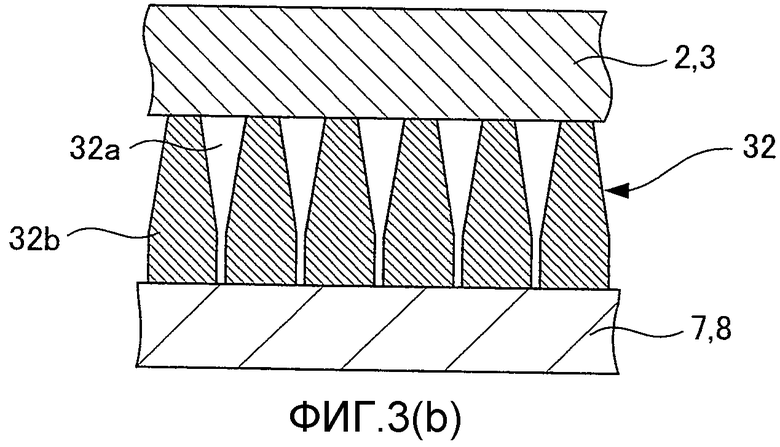

Фиг. 3 показывает схемы в поперечном разрезе, иллюстрирующие модификации модуля полупроводникового элемента, проиллюстрированного в варианте осуществления 2.

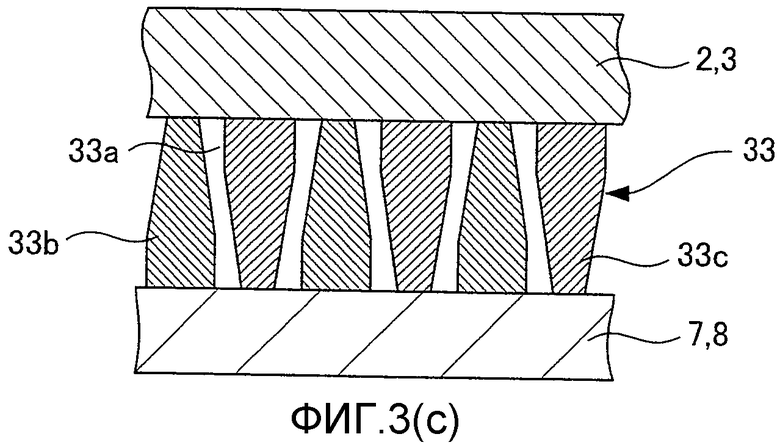

Фиг. 4 показывает схему конфигурации, иллюстрирующую еще один примерный вариант осуществления (вариант осуществления 3) модуля полупроводникового элемента согласно настоящему изобретению.

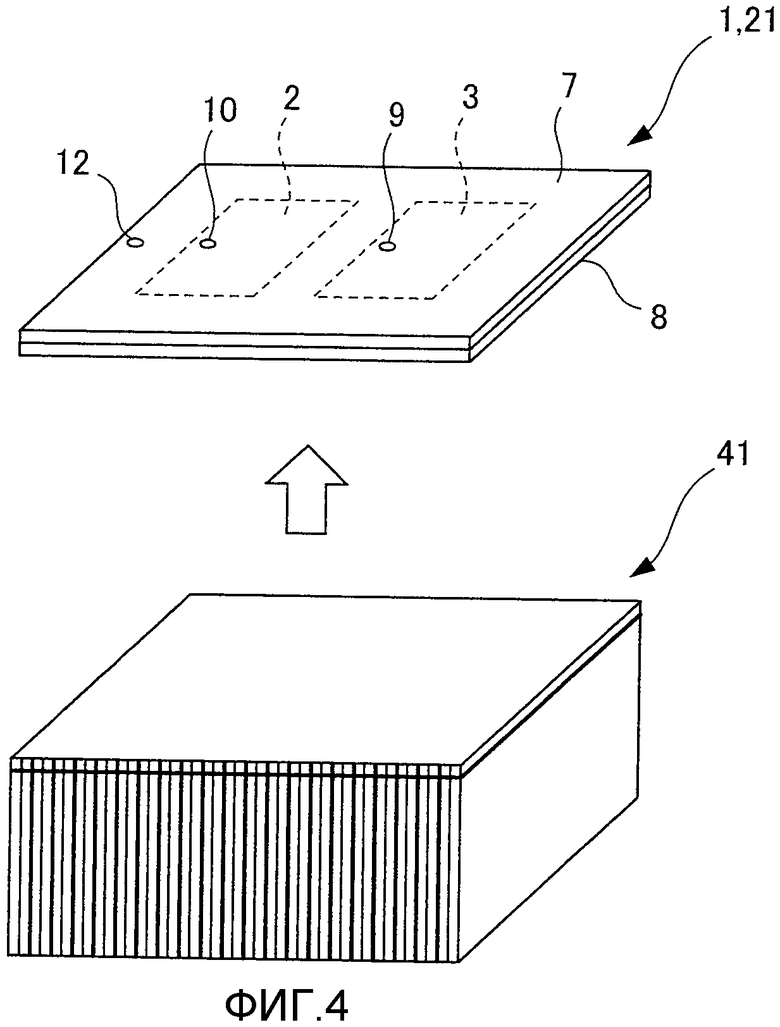

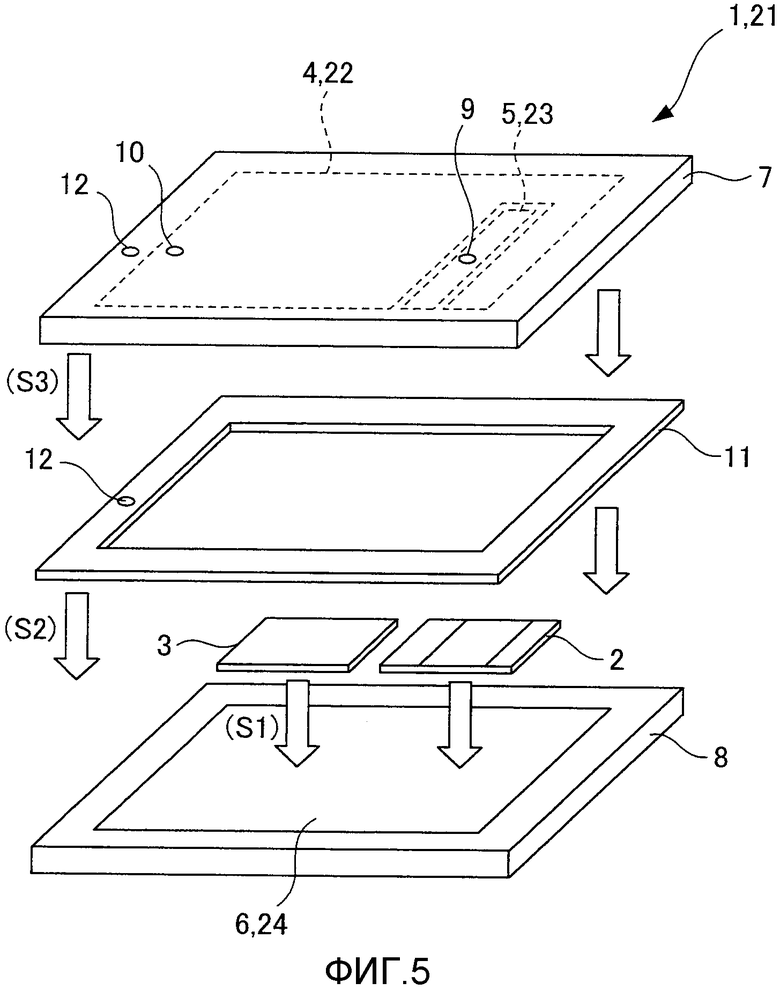

Фиг. 5 показывает схему для пояснения структуры способа для изготовления модулей полупроводниковых элементов, показанного в вариантах осуществления 1 и 2.

Фиг. 6 показывает схемы для пояснения подробностей способа для изготовления модулей полупроводниковых элементов, показанного в вариантах осуществления 1 и 2.

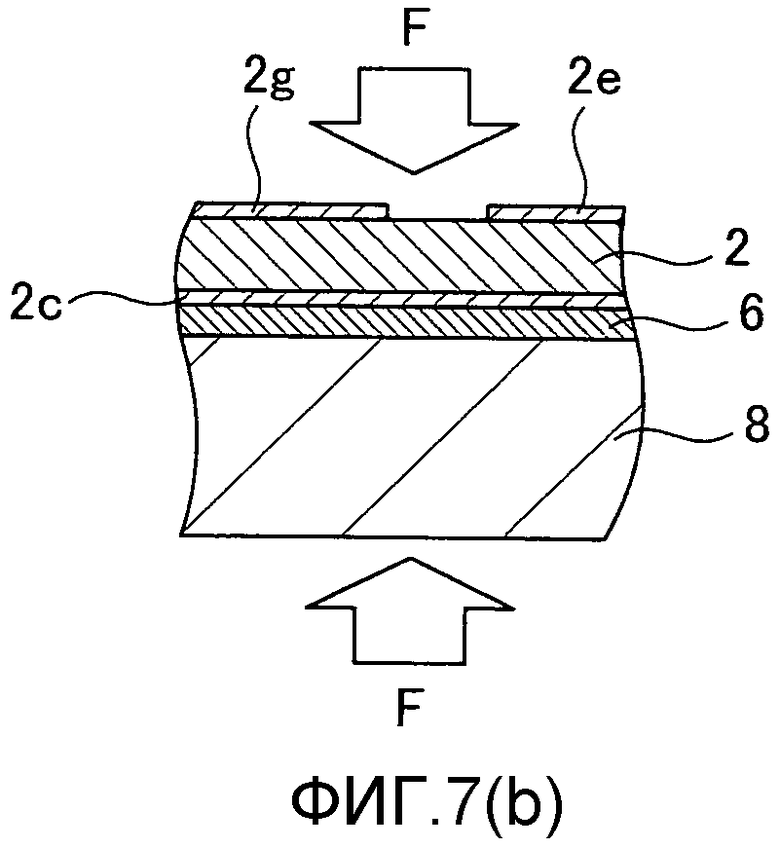

Фиг. 7 показывает схемы для пояснения подробностей способа для изготовления модулей полупроводниковых элементов, показанного в вариантах осуществления 1 и 2.

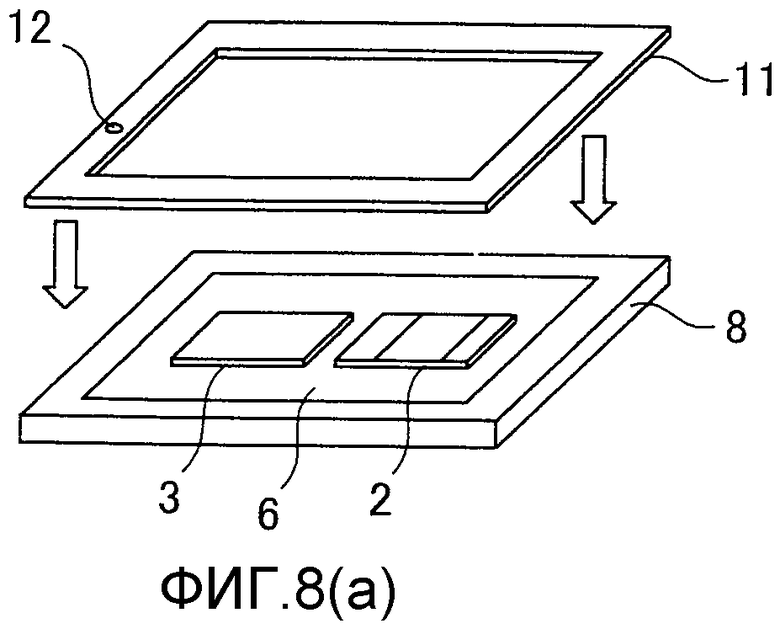

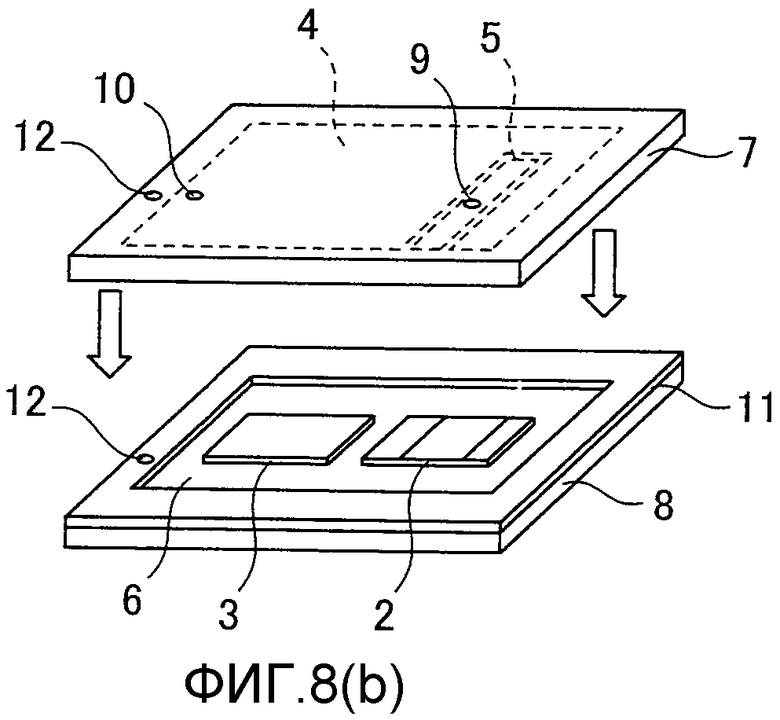

Фиг. 8 показывает схемы для пояснения подробностей способа для изготовления модулей полупроводниковых элементов, показанного в вариантах осуществления 1 и 2.

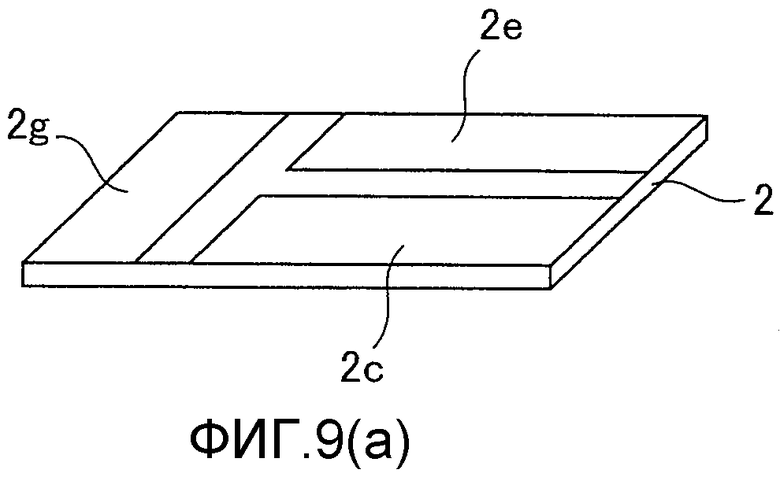

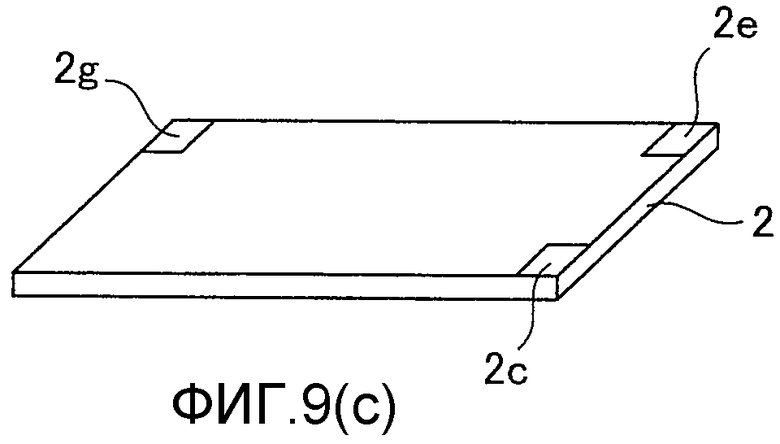

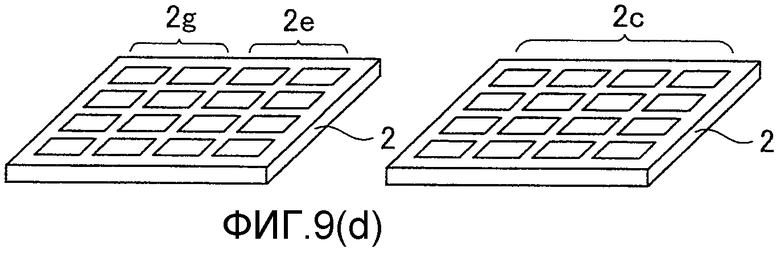

Фиг. 9 показывает схемы, иллюстрирующие некоторые примеры компоновки поверхностей электродов каждого полупроводникового элемента, используемого в модуле полупроводникового элемента согласно настоящему изобретению.

Пояснение ссылок с номерами

1, 21 - модуль полупроводникового элемента

2 - IGBT (полупроводниковый элемент)

2c, 2e, 2g - поверхность электрода

3 - диод (полупроводниковый элемент)

3c, 3e - поверхность электрода

4, 5, 6 - слой схемы межсоединений

7, 8 - керамическая подложка

9, 10, 12 - сквозные межсоединения

11 - герметизирующий элемент

13 - полимер

22, 23, 24, 31 - слой схемы межсоединений

41 - ребро для теплового излучения

Оптимальный режим осуществления изобретения

Ниже описывается модуль полупроводникового элемента согласно настоящему изобретению и способ для его изготовления со ссылкой на фиг. 1-8.

Первый вариант осуществления

Фиг. 1 показывает структурную схему, иллюстрирующую примерный вариант осуществления модуля полупроводникового элемента согласно настоящему изобретению.

Следует отметить, что модуль 1 полупроводникового элемента этого варианта осуществления выполнен с возможностью включать в себя IGBT 2 и диод 3 в качестве полупроводниковых элементов, но может быть выполнен с возможностью включать в себя, по меньшей мере, один полупроводниковый элемент. Полупроводник 1 является, в частности, подходящим для полупроводникового элемента, который имеет большую величину теплообразования.

Как показано на фиг. 1, модуль 1 полупроводникового элемента этого варианта осуществления включает в себя IGBT 2, диод 3, плоскую керамическую подложку 7 пластинчатой формы (вторую изолирующую подложку), плоскую керамическую подложку 8 пластинчатой формы (первую изолирующую подложку) и герметизирующий элемент 11. IGBT 2 и диод 3 имеют плоские поверхности электродов, сформированные на обеих их поверхностях. Керамическая подложка 7 имеет высокую удельную теплопроводность и имеет плоские слои 4 и 5 схемы межсоединений (вторая поверхность межсоединений), сформированные на ее поверхности на одной стороне. Слои 4 и 5 схемы межсоединений должны связываться с поверхностями электродов IGBT 2 и диода 3 на одной стороне. Керамическая подложка 8 имеет высокую удельную теплопроводность и имеет плоский слой 6 схемы межсоединений (первую поверхность межсоединений), сформированный на ее поверхности на одной стороне. Слой 6 схемы межсоединений связывается с поверхностями электродов IGBT 2 и диода 3 на другой стороне. Герметизирующий элемент 11 размещается между внешними краевыми частями керамических подложек 7 и 8, чтобы тем самым герметизировать внутреннюю часть. Модуль 1 полупроводникового элемента формируется посредством непосредственного связывания поверхностей раздела этих элементов через связывание при комнатной температуре.

Следует отметить, что связывание при комнатной температуре (также называемое поверхностно-активированным связыванием при комнатной температуре) является способом связывания с помощью явления, при котором прочное химическое связывание достигается даже при комнатной температуре посредством следующего: выполнения излучения ионных лучей и т.п. в вакууме так, что неактивные поверхностные слои, имеющие слабую реакционную активность, такие как оксиды и примеси на поверхностях материала, могут удаляться, т.е. обеспечения видимости атомных плоскостей, которые являются чистыми и имеют существенную реакционную активность, с поверхностей материала; и затем посредством сварки давлением атомных плоскостей поверхностей материала между собой. Посредством этого связывания при комнатной температуре можно достигать прочности связи, эквивалентной прочности связи сухих материалов, без необходимости использовать какое-либо связующее вещество. Выполнение связывания при комнатной температуре также приводит к такому преимуществу, что термическое напряжение не остается в материалах, связанных между собой. Следует отметить, что в случае технологии прямого связывания, такой как анодное связывание или диффузное связывание, трудно достигать надежной прочности связи, поскольку связывание с изоляционным материалом или между металлами является трудным.

Далее каждый компонент описывается более подробно.

IGBT 2 является элементом, полученным посредством формирования заранее, по меньшей мере, одной транзисторной структуры на полупроводниковой подложке. IGBT 2 формируется дополнительно посредством формирования поверхности 2c электрода коллектора, который должен выступать в качестве электрода транзистора, на всей поверхности IGBT 2 на одной стороне, а также формирования поверхности 2e электрода эмиттера и поверхности 2g электрода затвора, которые должны выступать в качестве электродов транзистора, на поверхности IGBT 2 на другой стороне таким образом, что его полная площадь поверхности достигает предпочтительно практически полной площади поверхности для всей поверхности на другой стороне. Аналогично, диод 3 является элементом, полученным посредством формирования заранее, по меньшей мере, одной диодной структуры на полупроводниковой подложке. Диод 3 формируется дополнительно посредством формирования поверхности 3c электрода, который должен выступать в качестве электрода диода, на всей поверхности диода 3 на одной стороне, а также формирования поверхности 3e электрода, который должен выступать в качестве электрода диода, на всей поверхности на другой стороне.

Поверхности из поверхности 2c электрода коллектора, поверхности 2e электрода эмиттера и поверхности 2g электрода затвора, расположенные на поверхностях IGBT 2, а также поверхности из поверхности 3c электрода и поверхности 3e электрода, расположенные на поверхностях диода 3, полируются и выравниваются для связывания с керамическими подложками 7 и 8 с помощью связывания при комнатной температуре.

На внутренней поверхности керамической подложки 7 формируются слои 4 и 5 схемы межсоединений, имеющие рисунки, соответствующие поверхности 2e электрода эмиттера и поверхности 2g электрода затвора IGBT 2 и поверхности 3e электрода диода 3 в местоположениях, соответствующих поверхности 2e электрода эмиттера, поверхности 2g электрода затвора и поверхности 3e электрода. Слои 4 и 5 схемы межсоединений соединяются, соответственно, со сквозными межсоединениями 9 и 10 (вторыми сквозными межсоединениями), предусмотренными так, чтобы проникать через керамическую подложку 7 в направлении ее толщины. Эти сквозные межсоединения 9 и 10 выступают в качестве электродных контактных выводов для внешних межсоединений. Между тем, на внутренней поверхности керамической подложки 8, формируется слой 6 схемы межсоединений, имеющий рисунок, соответствующий поверхности 2c электрода коллектора IGBT 2 и поверхности 3c электрода диода 3 в местоположении, соответствующем поверхности 2c электрода коллектора и поверхности 3c электрода. Слой 6 схемы межсоединений соединяется со сквозными межсоединениями 12 (первым и третьим сквозными электродами), предусмотренными так, чтобы проникать через герметизирующий элемент 11 и керамическую подложку 7 в направлении их толщины. Эти сквозные межсоединения 12 выступают в качестве электродного контактного вывода для внешних межсоединений.

Поверхности слоев 4, 5 и 6 схемы межсоединений, расположенных на внутренних поверхностях керамических подложек 7 и 8, также полируются и выравниваются для связывания с IGBT 2 и диодом 3 с помощью связывания при комнатной температуре. Между тем, каждый из слоев 4, 5 и 6 схемы межсоединений формируется так, чтобы иметь толщину 10-100 мкм, и имеет электрическую функцию в качестве межсоединений, а также функцию теплового излучения в качестве элемента теплопередачи. В частности, тепло, сформированное посредством IGBT 2 и диода 3, переносится на керамические подложки 7 и 8, имеющие высокую удельную теплопроводность, через слои 4, 5 и 6 схемы межсоединений, изготовленные из металла, которые имеют превосходную удельную теплопроводность, и затем высвобождается наружу.

Таким образом, хотя поликремний и т.п. может использоваться для слоев 4, 5 и 6 схемы межсоединений и сквозных электродов 9, 10 и 12, по вышеуказанной причине, желательным является металл, в частности медь и т.п., имеющий низкое электрическое сопротивление и превосходную удельную теплопроводность. Кроме того, для керамических подложек 7 и 8 подходящим является изоляционный материал, который имеет высокую удельную теплопроводность и имеет аналогичный коэффициент теплового расширения с таким полупроводниковым материалом, как кремний (Si), используемый для подложек полупроводниковых элементов. Например, нитрид алюминия (AlN) и т.п. является предпочтительным. Например, коэффициент теплового расширения AlN (приблизительно 5×10-6/K) является аналогичным коэффициенту теплового расширения Si (3,5×10-6/K), и, следовательно, проблема термического напряжения может смягчаться даже в случае работы при высокой температуре модуля полупроводникового элемента.

Между тем, сквозные электроды 9, 10 и 12 предусмотрены так, чтобы проникать через керамические подложки 7 и 8 и герметизирующий элемент 11 и соединяться с соответствующими слоями 4, 5 и 6 схемы межсоединений. Следовательно, расстояние межсоединений может сокращаться. Это позволяет уменьшать индуктивность в модуле и тем самым сокращать число конденсаторов схемы управления полупроводниковых элементов.

Поверхность 2c электрода коллектора, поверхность 2e электрода эмиттера и поверхность 2g электрода затвора IGBT 2 и поверхность 3c электрода и поверхность 3e электрода, расположенные на поверхностях диода 3, непосредственно связываются со слоями 4, 5 и 6 схемы межсоединений, соответствующими этим поверхностям электродов, посредством использования связывания при комнатной температуре. Следовательно, IGBT 2 и диод 3 монтируются и механически, электрически и термически соединяются с керамическими подложками 7 и 8.

Между тем, сквозные межсоединения 9, 10 и 12 предусмотрены на керамической подложке 7 в качестве наружных электродных контактных выводов, как показано на фиг. 1, что означает то, что все наружные электродные контактные выводы расположены на поверхности на одной стороне. Таким образом, соединение с внешними межсоединениями может упрощаться.

В этом случае, средство охлаждения, такое как охлаждающее ребро, может связываться с керамической подложкой 8, в которой сквозные межсоединения 9, 10 и 12 отсутствуют, как описано в нижеописанном варианте осуществления 3. Это упрощает применение к структуре для повышения эффективности охлаждения всего модуля. В этой связи, если это не обязательно должно учитываться, сквозные межсоединения 12 могут быть предусмотрены так, чтобы проникать через керамическую подложку 8 и соединяться со слоем 6 схемы межсоединений.

Помимо этого, герметизирующий элемент 11 связывается с внешними краевыми частями керамических подложек 7 и 8 и имеет функцию герметизации внутренней части модуля. Герметизирующий элемент 11 связывается с керамическими подложками 7 и 8 посредством связывания при комнатной температуре. Когда связывание выполняется таким образом, что IGBT 2 и диод 3 размещаются между керамическими подложками 7 и 8, пустоты (части, указываемые посредством ссылок с номерами 13), созданные между IGBT 2 и диодом 3 и между каждым из IGBT 2 и диода 3 и герметизирующим элементом 11, становятся разреженными или герметизируются с помощью инертного газа, такого как аргон (Ar). Иначе, пустоты заполняются заполнителем 13 из полимера, таким как силиконовая смазка и т.п., чтобы удерживать IGBT 2 и диод 3. Заполнение заполнителя 13 является желательным с точки зрения эффективности охлаждения (эффективности теплового излучения).

Как описано выше, модуль 1 полупроводникового элемента этого варианта осуществления получается посредством связывания, посредством связывания при комнатной температуре, поверхностей электродов, сформированных практически на всех поверхностях IGBT 2 и диода 3, с керамическими подложками 7 и 8, имеющими высокую удельную теплопроводность, при этом слои 4, 5 и 6 схемы межсоединений, имеющие высокую удельную теплопроводность, размещаются между ними. Тем самым, IGBT 2 и диод 3 монтируются таким плоским способом, чтобы размещаться между керамическими подложками 7 и 8.

Соответственно, дополнительные промежуточные слои не должны предусматриваться между поверхностями связывания. Кроме того, поскольку ковалентная связь делает связывание прочным, связываемые поверхности раздела могут иметь низкую термостойкость. Тем самым, удельная теплопроводность между элементами повышается, что позволяет достигать высокого теплового излучения. Большие части поверхностей IGBT 2 и диода 3 находятся в плотном контакте с проводящими керамическими подложками 7 и 8, имеющими высокую удельную теплопроводность, при этом проводящие слои 4, 5 и 6 схемы межсоединений, имеющие высокую удельную теплопроводность, размещаются между ними. Следовательно, получается двухсторонняя структура модуля охлаждения, в которой большие части обеих поверхностей IGBT 2 и диода 3 используются в качестве поверхностей, через которые переносится тепло. Это позволяет достигать дополнительно более высокого теплового излучения.

Кроме того, поверхности электродов IGBT 2 и диода 3 непосредственно связываются со слоями 4, 5 и 6 схемы межсоединений керамических подложек 7 и 8 посредством связывания при комнатной температуре без использования припоя или проводов. Следовательно, прочность связи между ними может быть задана такой высокой, как прочность связи сухих материалов, что позволяет значительно повышать вибростойкость частей, в которых монтируются IGBT 2 и диод 3 (частей межсоединений). Кроме того, межсоединения могут противостоять высокой температуре и термостойкость следовательно, может повышаться. Кроме того, число процессов может сокращаться и уменьшение производственных затрат, следовательно, может достигаться.

Как результат, может достигаться более высокая рабочая температура полупроводникового элемента, а также однородная температура в плоскости. В частности, можно повышать износостойкость и надежность частей межсоединений против циклического высокотемпературного воздействия. Помимо этого, поскольку нагрев не требуется при связывании, температурная деформация не вызывается и тем самым термическое напряжение не формируется. Соответственно, надежность самого модуля полупроводникового элемента также может повышаться.

Следует отметить, что керамические подложки 7 и 8 имеют небольшие толщины и IGBT 2 и диод 3 монтируются между керамическими подложками 7 и 8 плоским способом. Следовательно, когда модуль формируется, его толщина может значительно уменьшаться, что делает сам модуль компактным. Например, при условии, что толщина каждой керамической подложки составляет 2 мм, а толщина каждого полупроводникового элемента составляет 1 мм, толщина всего модуля составляет приблизительно 5 мм (=2×2 мм +1 мм), указывая то, что толщина может снижаться приблизительно до одной десятой толщины традиционных модулей.

Следует отметить, что хотя конфигурация в этом варианте осуществления является такой, что каждый полупроводниковый элемент имеет поверхности электродов на обеих своих поверхностях, элементы, каждый из которых имеет поверхности электродов только на своей поверхности на одной стороне, могут использоваться вместо этого. В этом случае, поверхности межсоединений, соответствующие поверхностям электродов полупроводниковых элементов, а также сквозные межсоединения в качестве электродных контактных выводов наружу могут формироваться на одной из керамических подложек. Другая керамическая подложка и полупроводниковые элементы могут связываться между собой посредством связывания при комнатной температуре без формирования слоя межсоединений в этой керамической подложке.

Кроме того, хотя связывание выполняется после того, как поверхности электродов полируются и выравниваются в этом варианте осуществления, они не должны быть плоскими. Например, можно использовать способ, в котором, когда выровненная керамическая подложка должна связываться с полупроводниковым элементом посредством связывания при комнатной температуре, часть электрода, немного выступающая из поверхности связывания, сдавливается так, что может обеспечиваться проводимость.

Кроме того, конфигурация в этом варианте осуществления является такой, что поверхности электродов формируются на всех или практически на всех поверхностях полупроводниковых элементов. Тем не менее, вместо использования всех поверхностей для электродов, конфигурация может быть такой, что часть поверхности используется для электродов или несколько электродов формируются на части или всей поверхности (см. фиг. 9(b) и 9(c), которые должны быть описаны ниже). Примером этого является пример, в котором несколько электродов затвора и электроды эмиттера формируются на поверхности на одной стороне и несколько электродов коллектора формируются на поверхности на другой стороне либо поверхность электрода в качестве общего электрода коллектора формируется на всей или практически на всей поверхности на другой стороне. Даже в этом случае полупроводниковые элементы непосредственно связываются с керамическими подложками посредством связывания при комнатной температуре в частях, отличных от тех, где находятся электроды. Следовательно, могут достигаться прочное связывание и высокое тепловое излучение. Кроме того, в вышеописанном случае конфигурация может быть такой, что поверхности межсоединений, соответствующие рисункам электродов полупроводниковых элементов, формируются на керамических подложках или что только сквозные электроды формируются в позициях, соответствующих электродам. Кроме того, можно использовать способ, в котором проводимость устанавливается посредством сдавливания, посредством сварки давлением, поверхностей электродов и поверхностей межсоединений, сформированных из более мягких материалов, чем полупроводниковые элементы и их изолирующие подложки.

Кроме того, конфигурация в этом варианте осуществления является такой, что сквозные межсоединения 9, 10 и 12 в качестве наружных электродных контактных выводов предусмотрены проникающим способом в направлении толщины керамических подложек 7 и 8. Тем не менее, следующие межсоединения могут формироваться вместо этих сквозных межсоединений. В частности, в качестве проводных межсоединений, которые соединяются со слоями 4, 5 и 6 схемы межсоединений и выступают в качестве наружных электродных контактных выводов, межсоединения могут формироваться таким образом, чтобы отходить от поверхности, по меньшей мере, одной из керамических подложек 7 и 8 в боковом направлении и проникать через герметизирующий элемент 11 в боковом направлении, которое должно выступать в качестве внешней периферийной части между керамическими подложками 7 и 8. Альтернативно, канавки могут формироваться таким образом, чтобы отходить от поверхности, по меньшей мере, одной из керамических подложек 7 и 8 в боковом направлении, и межсоединения могут формироваться в канавках таким образом, чтобы проникать, по меньшей мере, через одну из керамических подложек 7 и 8 в боковом направлении.

Второй вариант осуществления

Фиг. 2 показывает структурные схемы, иллюстрирующие другой примерный вариант осуществления модуля полупроводникового элемента согласно настоящему изобретению. Следует отметить, что идентичные ссылки с номерами присваиваются компонентам, идентичным компонентам в модуле полупроводникового элемента, проиллюстрированном в варианте осуществления 1 (фиг. 1), и дублированное описание опускается.

Как показано на фиг. 2(a), модуль 21 полупроводникового элемента этого варианта осуществления имеет конфигурацию, практически идентичную конфигурации модуля в варианте осуществления 1, но отличается в слоях 22, 23 и 24 схемы межсоединений керамических подложек 7 и 8, сформированных, соответственно, для поверхности 2c электрода коллектора, поверхности 2e электрода эмиттера и поверхности 2g электрода затвора, расположенных на поверхностях IGBT 2, и поверхности 3c электрода и поверхности 3e электрода, расположенных на поверхностях диода 3.

Аналогично слоям 4 и 5 схемы межсоединений в варианте осуществления 1, на внутренней поверхности керамической подложки 7 формируются слои 22 и 23 схемы межсоединений (вторая поверхность межсоединений), имеющие рисунки, соответствующие поверхности 2e электрода эмиттера и поверхности 2g электрода затвора IGBT 2 и поверхности 3e электрода диода 3 в местоположениях, соответствующих поверхности 2e электрода эмиттера, поверхности 2g электрода затвора и поверхности 3e электрода. Дополнительно, слои 22 и 23 схемы межсоединений соединяются, соответственно, со сквозными межсоединениями 9 и 10, предусмотренными так, чтобы проникать через керамическую подложку 7. Аналогично слою 6 схемы межсоединений в варианте осуществления 1, на внутренней поверхности керамической подложки 8 формируется слой 24 схемы межсоединений (первая поверхность межсоединений), имеющий рисунок, соответствующий поверхности 2c электрода коллектора IGBT 2 и поверхности 3c электрода диода 3 в местоположении, соответствующем поверхности 2c электрода коллектора и поверхности 3c электрода. Дополнительно, слой 24 схемы межсоединений соединяется с герметизирующим элементом 11 и сквозными межсоединениями 12, предусмотренными так, чтобы проникать через керамическую подложку 7.

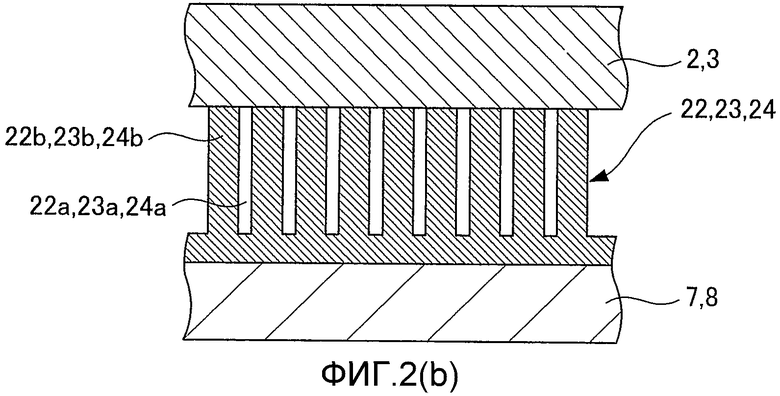

Конфигурация в этом варианте осуществления, тем не менее, является такой, что несколько частей 22a (23a, 24a) канавок с высоким соотношением сторон формируются вертикально в каждом плоском слое схемы межсоединений, как показано на фиг. 2(b), чтобы ослаблять нагрузки на связываемые поверхности раздела, присущие в связи с разностями между коэффициентами расширения IGBT 2 и диода 3 и коэффициентами расширения керамических подложек 7 и 8. Таким образом, несколько тонких столбчатых электродов 22b (23b, 24b), которые являются прямоугольными, многоугольными или круговыми, формируются на стороне поверхности слоя 22 (23, 24) схемы межсоединений. Поверхности связывания столбчатых электродов 22b (23b, 24b) имеют форму прямоугольных, многоугольных или круговых точек и связываются с поверхностями электродов IGBT 2 и диода 3 (иллюстрация поверхностей электродов IGBT 2 и диода 3 опускается). Передний конец каждого столбчатого электрода 22b (23b, 24b) является плоским и имеет заранее определенную площадь поперечного сечения, при этом его длина задается равной заранее определенной длине. Таким образом, предусмотрена структура, которая предоставляет возможность столбчатым электродам 22b (23b, 24b) обеспечивать электрическое соединение и термическое соединение в их продольном направлении, а также упруго деформироваться в ортогональном направлении (горизонтальном направлении на фиг. 2(b)) для продольного направления. Структура тем самым приводит к тому, что столбчатые электроды 22b (23b, 24b) выступают в качестве межсоединений для IGBT 2 и диода 3, а также в качестве элемента теплопередачи для теплового излучения. Дополнительно, структура приводит к тому, что выпуклые части 22b (23b, 24b) упруго деформируются при возникновении смещения IGBT 2 и диода 3 вследствие теплового расширения, посредством чего нагрузка, сформированная таким способом, ослабляется без ухудшения электрического соединения и термического соединения.

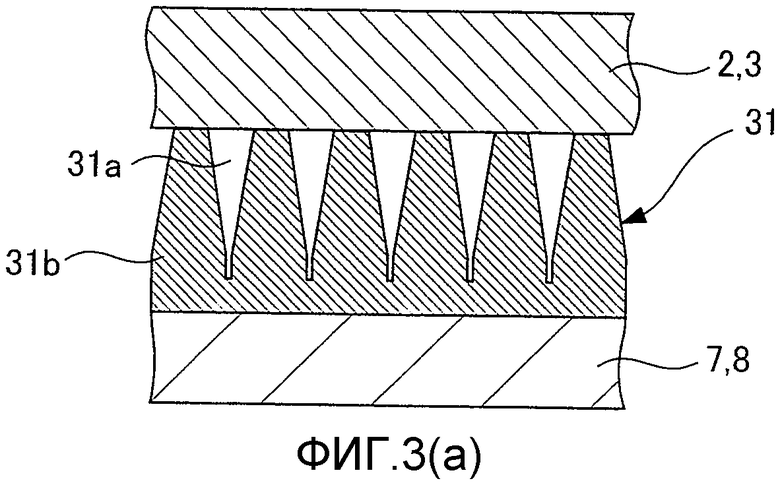

В этой связи, структурой слоя 22 (23, 24) схемы межсоединений может быть структура квадратной усеченной пирамиды, многоугольной усеченной пирамиды или усеченного конуса (повернутой трапеции), аналогично слою 31 схемы межсоединений, показанному на фиг. 3(a). В частности, конфигурация является такой, что несколько клиновидных частей 31a канавок с высоким соотношением сторон формируются в плоском слое схемы межсоединений, так что несколько столбчатых электродов 31b, каждый из которых имеет форму квадратной усеченной пирамиды, многоугольной усеченной пирамиды или усеченного конуса, формируются на поверхности слоя 31 схемы межсоединений. Поверхности связывания столбчатых электродов 31b имеют квадратную, многоугольную или круговую форму и связываются с поверхностями электродов IGBT 2 и диода 3 (иллюстрация поверхностей электродов IGBT 2 и диода 3 опускается). Передний конец каждого столбчатого электрода 31b также является плоским и имеет заранее определенную площадь поперечного сечения, при этом его длина задается равной заранее определенной длине. Таким образом, предусмотрена структура, которая предоставляет возможность столбчатым электродам 31b обеспечивать электрическое соединение и термическое соединение в своем продольном направлении, а также упруго деформироваться в ортогональном направлении (горизонтальном направлении на фиг. 3(a)) для продольного направления. Структура тем самым приводит к тому, что столбчатые электроды 31b выступают в качестве межсоединений для IGBT 2 и диода 3, а также в качестве элемента теплопередачи для теплового излучения. Дополнительно, структура приводит к тому, что выпуклые части 31b упруго деформируются при возникновении смещения IGBT 2 и диода 3 вследствие теплового расширения, посредством чего нагрузка, сформированная таким способом, ослабляется без ухудшения электрического соединения и термического соединения.

Далее описывается упруго деформированное состояние слоя 31 схемы межсоединений, имеющей вышеуказанную структуру.

IGBT 2 и диод 3 формируют тепло при использовании. Посредством этого теплообразования подложки термически расширяются и смещаются. Смещение, вследствие теплового расширения, является большим, в частности, когда дело касается IGBT 2 и диода 3, выходные мощности которых являются большими. В традиционных модульных структурах смещение не может быть разрешено, так что электрическое соединение и термическое соединение ухудшаются. Это серьезно влияет на надежность и срок службы модуля. Например, максимальная величина смещения может вычисляться при допущении, что: размер каждого полупроводникового элемента составляет 10 мм2; возрастание температуры вследствие теплообразования составляет 500°C; коэффициент теплового расширения Si, формирующего подложку полупроводникового элемента, составляет приблизительно 3,5×10-6/K; коэффициент теплового расширения Cu, формирующей поверхности электродов и слои схемы межсоединений, составляет 17×10-6/K и коэффициент теплового расширения AlN, формирующего керамические подложки, составляет 5×10-6/K. Затем, ожидается, что смещение составляет приблизительно 7,5 мкм на поверхности раздела Si-AlN и приблизительно 65 мкм на поверхности раздела Si-Cu, при этом предполагается, что большое смещение должно возникать на поверхности раздела Si-Cu.

Напротив, в этом варианте осуществления, даже когда подложки IGBT 2 и диода 3 термически расширяются и тепловое расширение вызывает их смещение, столбчатые электроды 22b, 23b и 24b или столбчатые электроды 31b упруго деформируются при помощи слоев 22, 23 и 24 схемы межсоединений или слоев 31 схемы межсоединений, имеющих вышеописанную структуру. Смещение, следовательно, может быть разрешено. Как результат, надежность и срок службы могут обеспечиваться без ухудшения электрического соединения и термического соединения.

Следует отметить, что слои схемы межсоединений не ограничены слоем 31 схемы межсоединений, показанным на фиг. 3(a). Можно использовать слой 32 схемы межсоединений, который формируется из нескольких столбчатых электродов 32b в форме пирамиды/конуса, отделенных друг от друга посредством частей 32a канавок, как показано на фиг. 3(b). Также можно использовать слой 33 схемы межсоединений, который формируется из нескольких столбчатых электродов 33b и 33c в форме пирамиды/конуса, отделенных друг от друга посредством частей 33a канавок, и в котором верхние стороны каждой пары смежных столбчатых электродов 33b и 33c смотрят во взаимно различных направлениях, как показано на фиг. 3(c). Помимо этого, столбчатые электроды 32b в форме пирамиды/конуса слоя 32 схемы межсоединений, показанной на фиг. 3(b), могут быть расположены с инвертированными вершинами. Дополнительно, структура столбчатых электродов может быть такой, что столбчатые электроды 22b, 23b и 24b слоев 22, 23 и 24 схемы межсоединений, показанных на фиг. 2(b), отделяются друг от друга посредством частей 22a, 23a и 24a канавок.

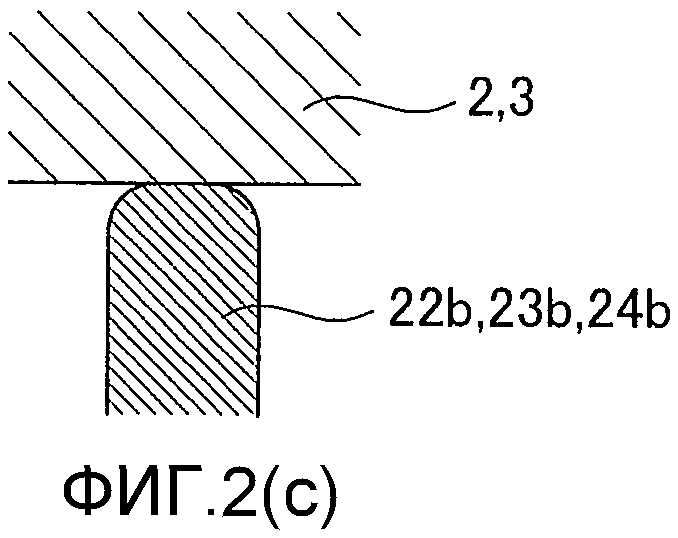

В структурах столбчатых электродов, показанных на фиг. 2(b) и 3(a)-3(c), буртик на краю части связывания каждого из столбчатых электродов находится под прямым углом или заранее определенным углом наклона с поверхностью цели связывания. Например, на фиг. 2(b), буртик на краю части связывания каждого столбчатого электрода 22b (23b, 24b) на стороне ближе к IGBT 2 или диоду 3 находится практически под прямым углом с поверхностью электрода IGBT 2 или диода 3, на которой осуществляется связывание. Релаксация напряжений является достаточной даже при этой конфигурации. Тем не менее, дополнительная релаксация напряжений должна быть возможной, если буртик на краю части связывания каждого столбчатого электрода 22b (23b, 24b) сформирован в круглой форме с заранее определенной кривизной (т.е. форме, заданной как R), как показано на фиг. 2(c). В этом случае, R может быть задана для буртика на краю части связывания столбчатого электрода 22b (23b, 24b) на стороне ближе к поверхности электрода IGBT 2 или диода 3 или для буртика на краю части связывания столбчатого электрода 22b (23b, 24b) на стороне ближе к поверхности межсоединений соответствующей одной из керамических подложек 7 и 8.

Как пояснено в нижеописанном варианте осуществления 4, столбчатые электроды формируются с использованием технологии микрообработки, такой как травление с помощью лазера или электронных лучей или впечатывание через прессование в формах. При формировании R в буртике на краю части связывания столбчатого электрода, R может формироваться в буртике на краю части связывания столбчатого электрода посредством использования тепла лазера или электронных лучей в ходе или после формирования столбчатого электрода. Альтернативно, R может формироваться в буртике на краю части связывания столбчатого электрода посредством впечатывания с помощью пресс-формы, на которой R формируется, в ходе формирования столбчатого электрода.

Помимо этого, в этом варианте осуществления, аналогично частям, указываемым посредством ссылок с номерами 13 в варианте осуществления 1, части 22a, 23a и 24a канавок или части 31a канавок могут становиться разреженными, или герметизироваться с помощью инертного газа, или, альтернативно, заполняться заполнителем из полимера, таким как силиконовая смазка и т.п., с учетом повышения удельной теплопроводности.

Третий вариант осуществления

Фиг. 4 показывает структурную схему, иллюстрирующую другой примерный вариант осуществления модуля полупроводникового элемента согласно настоящему изобретению. Следует отметить, что идентичные ссылки с номерами присваиваются компонентам, идентичным компонентам в модулях полупроводниковых элементов, проиллюстрированных в вариантах осуществления 1 и 2 (фиг. 1 и 2), и дублированное описание опускается.

Модуль полупроводникового элемента этого варианта осуществления получается посредством непосредственного связывания, посредством связывания при комнатной температуре, ребра 41 для теплового излучения (средства охлаждения), изготовленного из металла, которое имеет превосходное тепловое излучение, с керамической подложкой 8 модуля 1 или 21 полупроводникового элемента, показанного в варианте осуществления 1 или 2 (фиг. 1 или 2).

В частности, поверхность связывания керамической подложки 8 модуля 1 или 21 полупроводникового элемента и поверхность ребра 41 для теплового излучения активируются посредством физического напыления через излучение ионных лучей и т.п. и затем посредством сварки друг к другом под давлением при комнатной температуре, посредством чего поверхности связывания непосредственно связываются друг с другом. В этой связи, средство охлаждения может быть ребром для теплового излучения, например, и при этом может быть, например, модулем охлаждения, содержащим проход, через который хладагент, такой как вода, принудительно протекает, или аналогичным средством либо, альтернативно, структурой, в которой такой модуль охлаждения заранее интегрирован в саму подложку посредством формирования прохода и т.п. в самой подложке.

Как описано в вариантах осуществления 1 и 2, в настоящем изобретении межсоединения для IGBT 2 и диода 3, расположенные внутри, могут формироваться из сквозных межсоединений 9, 10 и 12, предусмотренных для одной из керамических подложек, т.е. керамической подложки 7. Средство охлаждения, такое как ребро 41 для теплового излучения, следовательно, может связываться с другой керамической подложкой 8. Кроме того, связывание при комнатной температуре дает возможность прямого связывания между керамической подложкой 8 и ребром 41 для теплового излучения без необходимости использовать промежуточный элемент. Это приводит к более высокой прочности физической связи, что, в свою очередь, приводит к более прочному термическому соединению. Тем самым, высокая удельная теплопроводность может достигаться между керамической подложкой 8 и ребром 41 для теплового излучения.

Помимо этого, процесс связывания посредством связывания при комнатной температуре выполняется при комнатной температуре, как упомянуто ранее. Таким образом, влияние, связанное с нагревом, не вызывается в модуле, так что термическое напряжение не формируется. Прочное связывание также может достигаться даже при связывании различных материалов. Между тем, промежуточный элемент, чтобы поддерживать связывание, может быть необходим в некоторых случаях, в зависимости от типа материала. Тем не менее, в этом случае прочность физической связи также является высокой, и, следовательно, термическое соединение является прочным. Следовательно, высокая удельная теплопроводность может достигаться между керамической подложкой 8 и ребром 41 для теплового излучения.

Следует отметить, что конфигурация в этом варианте осуществления является такой, что ребро 41 для теплового излучения предусмотрено для внешней поверхности керамической подложки 8, не имеющей сквозных межсоединений, проникающих через нее в направлении толщины; вместо этого, если сквозные межсоединения расположены только на стороне керамической подложки 8, ребро 41 для теплового излучения может быть предусмотрено для внешней поверхности керамической подложки 7, не имеющей сквозных межсоединений, проникающих через нее в направлении толщины. Между тем, если проводные межсоединения, выступающие в боковом направлении керамических подложек 7 и 8, предусмотрены вместо сквозных межсоединений, сквозные межсоединения отсутствуют на керамических подложках 7 и 8 и тем самым ребро 41 для теплового излучения может быть присоединено к внешней поверхности каждой из керамических подложек 7 и 8.

Четвертый вариант осуществления

Далее описывается способ для изготовления модулей 1 и 21 полупроводниковых элементов, проиллюстрированных в вариантах осуществления 1 и 2 (фиг. 1, 2 и т.д.), с помощью фиг. 5-8. Здесь, фиг. 5 показывает схему, иллюстрирующую элементы в несобранном состоянии, составляющем модуль 1 или 21 полупроводникового элемента, проиллюстрированный в варианте осуществления 1 или 2, и используется для пояснения структуры способа для изготовления модуля. Фиг. 6-8 показывают схемы для пояснения подробностей этапов изготовления в способе изготовления. Таким образом, каждый этап изготовления описывается со ссылкой на фиг. 5. Следует отметить, что идентичные ссылки с номерами присваиваются компонентам, идентичным компонентам в модулях 1 и 21 полупроводниковых элементов, проиллюстрированных в вариантах осуществления 1 и 2.

(1) Подготовка элементов

IGBT 2, диод 3, керамическая подложка 7, керамическая подложка 8 и герметизирующий элемент 11 подготавливаются заранее.

Относительно IGBT 2 и диода 3, по меньшей мере, одна транзисторная структура и диодная структура формируются на полупроводниковых подложках посредством использования общих полупроводниковых процессов. На обеих поверхностях полупроводниковых подложек предусмотрены сформированные поверхности электродов (поверхность 2c электрода коллектора, поверхность 2e электрода эмиттера, поверхность 2g электрода затвора, поверхность 3c электрода и поверхность 3e электрода), которые должны соединяться с транзисторной структурой и диодной структурой. Эти поверхности электродов формируются так, чтобы иметь максимально большую площадь. Например, поверхность 2c электрода коллектора и поверхность 3c электрода формируются на всей поверхности соответствующего одного из IGBT 2 и диода 3 на одной стороне. Поверхность 3e электрода формируется на всей поверхности диода 3 на другой стороне. Поверхность 2e электрода эмиттера и поверхность 2g электрода затвора формируются на поверхности IGBT 2 на другой стороне таким образом, чтобы иметь максимально большие площади при обеспечении изоляции друг от друга. Эти поверхности электродов используются не только для того, чтобы обеспечивать электрическое соединение, но также и для того, чтобы обеспечивать термическое соединение, следовательно, имеют функцию переноса тепла, сформированного посредством IGBT 2 и диода 3.

В этой связи, конфигурация может быть такой, что часть поверхности используется для электродов или множество электродов формируются на всей или части поверхности (см. фиг. 9(b) и 9(c), которые должны быть описаны ниже). Затем, на керамической подложке могут быть сформированы поверхности межсоединений, соответствующие рисункам электродов полупроводникового элемента или только сквозных электродов в позициях, соответствующих электродам. Даже в этом случае полупроводниковый элемент непосредственно связывается с керамической подложкой посредством связывания при комнатной температуре в частях, отличных от тех, где находятся электроды. Следовательно, могут достигаться прочное связывание и высокое тепловое излучение.

Керамические подложки 7 и 8 формируются в плоских пластинчатых формах посредством использования общего процесса изготовления керамики. Затем, на поверхности каждой из керамических подложек 7 и 8 на одной стороне (поверхности, находящейся на внутренней стороне после того, как модуль сформирован) формируются слои 4, 5 и 6 схемы межсоединений (или слои 22, 23 и 24 схемы межсоединений) в местоположениях, соответствующих поверхностям электродов IGBT 2 и диода 3. Дополнительно, сквозные межсоединения 9, 10 и 12, которые должны соединяться, соответственно, со слоями 4, 5 и 6 схемы межсоединений (или слоями 22, 23 и 24 схемы межсоединений), формируются проникающими через керамическую подложку 7. Другими словами, слои 4, 5 и 6 схемы межсоединений (или слои 22, 23 и 24 схемы межсоединений) формируют рисунок таким образом, что проводимость устанавливается между поверхностями электродов IGBT 2 и диода 3 и соответствующими сквозными межсоединениями 9, 10 и 12. Герметизирующий элемент 11, чтобы герметизировать внутреннюю часть модуля, формируется в полой плоской пластинчатой форме посредством использования общего процесса изготовления керамики. Сквозные межсоединения 12, которые должны соединяться со слоем 6 (24) схемы межсоединений, также формируются в герметизирующем элементе 11 таким образом, чтобы проникать через сам герметизирующий элемент 11.

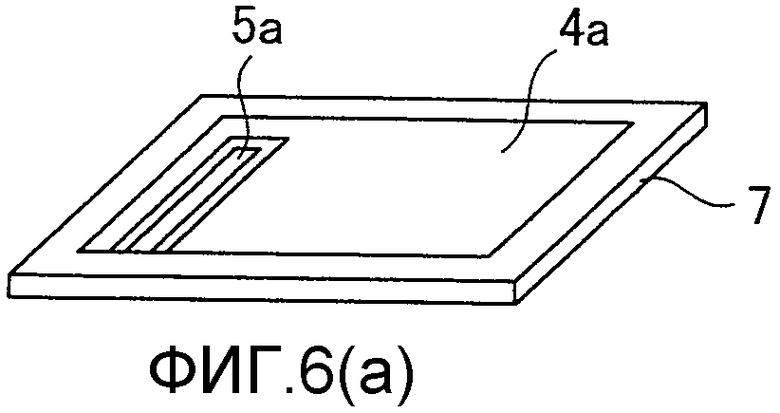

Относительно слоев 4 и 5 схемы межсоединений, слои 4a и 5a схемы межсоединений формируются непосредственно на керамической подложке 7 через процесс пленкообразования, как показано, например, на фиг. 6(a). В качестве процесса пленкообразования, используется общий процесс пленкообразования, например, такой как CVD (химическое осаждение из паровой фазы), металлизация, напыление и т.п. Более конкретно, слои 4a и 5a схемы межсоединений, соответствующие поверхностям электродов IGBT 2 и диода 3, могут формироваться посредством образования пленки на всей поверхности керамической подложки 7 и удаления ее части и тем самым формирования рисунка на пленке посредством вытравливания и т.п. Альтернативно, слои 4a и 5a схемы межсоединений, соответствующие поверхностям электродов IGBT 2 и диода 3, могут формировать рисунок посредством их формирования избирательно посредством маскирования.

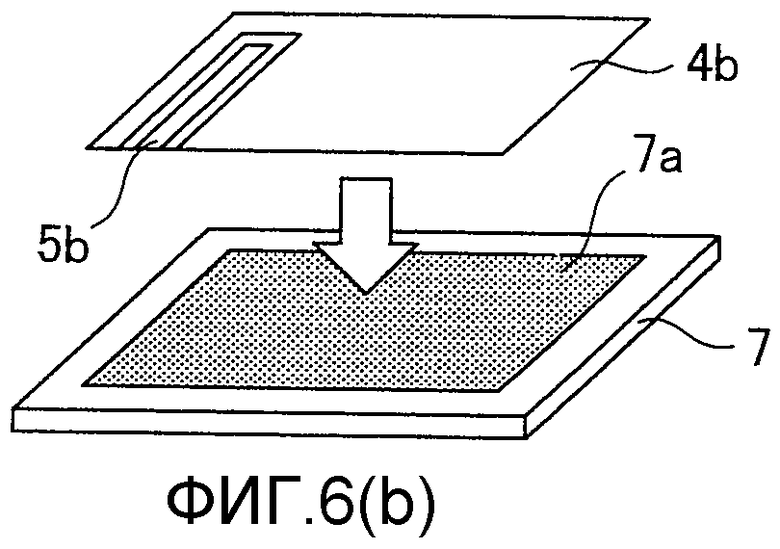

В качестве другой альтернативы для слоев 4 и 5 схемы межсоединений, как показано на фиг. 6(b), слои 4b и 5b схемы межсоединений, соответствующие поверхностям электродов IGBT 2 и диода 3, могут формироваться посредством формирования рисунка на металлической фольге в отдельном процессе, и затем слои 4b и 5b схемы межсоединений из металлической фольги могут связываться с поверхностью керамической подложки 7 посредством связывания при комнатной температуре. Слои 4b и 5b схемы межсоединений, соответствующие поверхностям электродов IGBT 2 и диода 3, могут формироваться также посредством связывания металлической фольги со всей поверхностью керамической подложки 7 посредством связывания при комнатной температуре и затем удаления ее части и тем самым формирования рисунка на металлической фольге посредством вытравливания и т.п. Когда металлическая фольга должна связываться с керамической подложкой 7, промежуточный слой 7a может формироваться между металлической фольгой и керамической подложкой 7, если прочность связи между ними должна повышаться. Примеры материала промежуточного слоя включают в себя металлы, к примеру золото (Au), платина (Pt), титан (Ti) и алюминий (Al).

Слой 6 схемы межсоединений керамической подложки 8 может подготавливаться аналогично слоям 4 и 5 схемы межсоединений. Тем не менее, слой 6 схемы межсоединений не должен формировать рисунок, соответственно, для поверхностей электродов IGBT 2 и диода 3, как в случае слоев 4 и 5 схемы межсоединений. Следовательно, слой 6 схемы межсоединений может формироваться практически на всей поверхности керамической подложки 8 посредством процесса пленкообразования. Слой 6 схемы межсоединений также может формироваться посредством отдельной подготовки металлической фольги как слоя 6 схемы межсоединений и затем связывания металлической фольги на всей поверхности керамической подложки 8 посредством связывания при комнатной температуре.

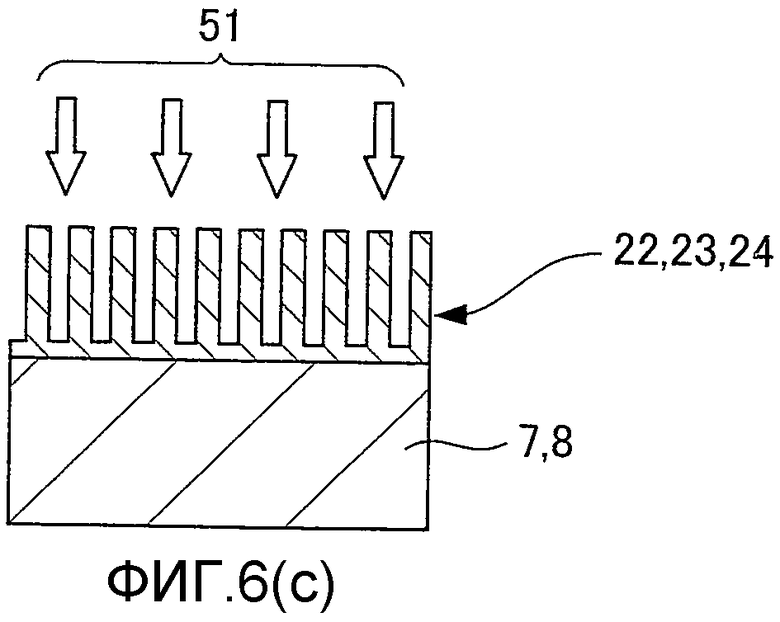

Следует отметить, что согласно информации по слоям 22, 23 и 24 схемы межсоединений или слоям 31 схемы межсоединений, проиллюстрированным в варианте осуществления 2, несколько вертикальных канавок, каждая из которых имеет высокое соотношение сторон в направлении толщины, могут формироваться в плоских слоях схемы межсоединений, сформированных на керамических подложках 7 и 8. Таким образом, формируются слои 22, 23 и 24 схемы межсоединений или слои 31 схемы межсоединений, имеющие структуру с несколькими тонкими столбчатыми электродами. Например, в обработке слоев 4a, 5a и 9a схемы межсоединений несколько тонких вертикальных канавок с высоким соотношением сторон могут формироваться в плоских слоях схемы межсоединений, имеющих толщины 10-100 мкм, посредством использования технологии микрообработки, такой как травление с помощью лазера или электронных лучей 51, как показано на фиг. 6(c), или впечатывание через прессование в формах. Таким образом, формируются слои 4a, 5a и 9a схемы межсоединений, имеющие структуру с несколькими тонкими столбчатыми электродами.

Между тем, когда используется металлическая фольга, как в случаях слоев 4b, 5b и 9b схемы межсоединений, несколько тонких вертикальных канавок с высоким соотношением сторон могут формироваться в металлической фольге заранее и металлическая фольга затем может связываться с керамическими подложками 7 и 8 посредством связывания при комнатной температуре. Таким образом, формируются слои 4b, 5b и 9b схемы межсоединений, имеющие структуру с несколькими тонкими столбчатыми электродами. Дополнительно, структура с несколькими тонкими столбчатыми электродами может формироваться через прессование выдавливанием или выращивание металлической пленки в конкретных областях. Помимо этого, структура с несколькими тонкими столбчатыми электродами может формироваться через многослойную конструкцию посредством связывания при комнатной температуре.

Следует отметить, что слои 22, 23 и 24 схемы межсоединений или слои 31 схемы межсоединений, имеющие структуру столбчатого электрода, формируются предпочтительно в деформируемой, а более предпочтительно, в упругой деформируемой форме и с размером, подходящим на основе среды эксплуатации (например, рабочей температуры, электродного материала и т.п.). Помимо этого, соотношение сторон структуры столбчатого электрода предпочтительно составляет 5:1 и выше, а более предпочтительно, 10:1 и выше.

Использование слоев 22, 23 и 24 схемы межсоединений или слоев 31 схемы межсоединений, имеющих структуру столбчатого электрода, позволяет ослаблять нагрузки вследствие теплообразования, а также надежно обеспечивать электрическое соединение и термическое соединение слоев 22, 23 и 24 схемы межсоединений или слоев 31 схемы межсоединений.

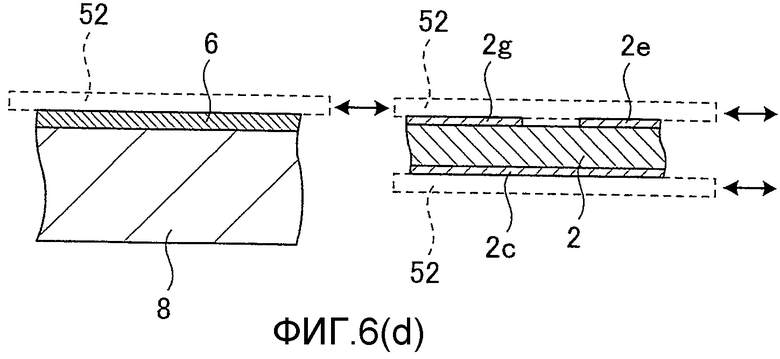

При связывании, посредством связывания при комнатной температуре, таким образом подготовленных IGBT 2, диода 3, керамической подложки 7, керамической подложки 8 и герметизирующего элемента 11 их поверхности связывания полируются и выравниваются для более надежного и более прочного связывания, чем в иных случаях. В частности, устройство 52 CMP (химико-механического полирования), например, используется для того, чтобы полировать и выравнивать: поверхности элементов, включающие в себя поверхность 2c электрода коллектора, поверхность 2e электрода эмиттера и поверхность 2g электрода затвора для IGBT 2; поверхности элементов, включающие в себя поверхность 3c электрода и поверхность 3e электрода для диода 3; поверхности слоев 4 и 5 схемы межсоединений для керамической подложки 7; поверхности слоя 6 схемы межсоединений для керамической подложки 8 и т.п. (см. фиг. 6 (d)). Полировка и выравнивание поверхности выполняются посредством химико-механического процесса, такого как CMP, или процесса механического шлифования с помощью обратного шлифовального станка и т.п. Следует отметить, что на прочность связи посредством связывания при комнатной температуре оказывает влияние шероховатость поверхности для поверхностей связывания. Таким образом, желательно выравнивать поверхности до максимальной гладкости предпочтительно посредством CMP и т.п. Таким образом, не допускается наличие пустот на связываемых поверхностях раздела, что, в свою очередь, позволяет достигать более высокой прочности связи, чем в иных случаях.