Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано в высокоскоростных арифметико-логических устройствах или в качестве самостоятельного вычислительного элемента в гибридных вычислительных системах в качестве ускорителя арифметических вычислений.

Известен «Реконфигурируемый асинхронный сумматор-умножитель» (см. патент РФ №2159464, опубликован 20.11.2000), содержащий блок асинхронного суммирования, состоящий из 2m блоков параллельной обработки разрядных срезов, 2m-1 формирователей импульсов и запускающего формирователя импульсов. Первые выходы формирователей импульсов и запускающего формирователя импульсов соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого является выходом готовности суммы блока асинхронного суммирования, а вторые выходы блоков параллельной обработки разрядных срезов являются выходами результата блока асинхронного суммирования. В устройство введены 2m шинных мультиплексоров слагаемых, каждый из которых содержит m мультиплексоров n в 1, блок управления устройством, шинный мультиплексор множителя, состоящий из m мультиплексоров n в 1, m-1 блоков асинхронного суммирования. В каждый блок асинхронного суммирования введены коммутатор-сдвигатель первого слагаемого, блок мультиплексоров первого слагаемого, состоящий из 2m мультиплексоров 3 в 1, блок мультиплексоров второго слагаемого, состоящий из 2m мультиплексоров 2 в 1, мультиплексор готовности суммы, инвертор. Информационные входы шинных мультиплексоров слагаемых соединены с n 2m-разрядными входами данных сумматора-умножителя, информационные входы шинного мультиплексора множителя соединены с n m-разрядными входами данных, являющимися младшими разрядами входов данных сумматора-умножителя. Выход шинного мультиплексора множителя и вход команд сумматора-умножителя подключены к блоку управления, управляющие выходы которого соединены с соответствующими шинными мультиплексорами слагаемых, шинным мультиплексором множителя. Выходы шинных мультиплексоров слагаемых соединены с соответствующими входами слагаемых блоков асинхронного суммирования. Выход результата и выход готовности суммы каждого блока асинхронного суммирования являются выходами сумматора-умножителя и одновременно служат входами результата и готовности суммы для соответствующего следующего блока асинхронного суммирования. В каждом блоке асинхронного суммирования вход первого слагаемого соединен со вторым входом блока мультиплексоров первого слагаемого и коммутатором-сдвигателем первого слагаемого, выход которого соединен с первым входом блока мультиплексоров первого слагаемого. Третий вход блока мультиплексоров первого слагаемого соединен с логическим нулем, вход второго слагаемого и выход результата предыдущего блока асинхронного суммирования - соответственно со вторым и первым входами блока мультиплексоров второго слагаемого. Выходы блока мультиплексоров первого слагаемого и блока мультиплексоров второго слагаемого - с соответствующими первыми и вторыми входами блоков параллельной обработки разрядных срезов. Вход готовности суммы блока асинхронного суммирования через инвертор соединен с первым входом мультиплексора готовности суммы, выход которого соединен с соответствующими входами блоков параллельной обработки разрядных срезов и запускающим формирователем импульсов. Блок управления предназначен для подачи на блоки мультиплексоров первого и второго слагаемых, на мультиплексор готовности суммы каждого блока асинхронного суммирования соответствующих управляющих сигналов.

Вышеуказанное устройство является наиболее близким к заявляемому устройству и поэтому выбрано в качестве прототипа.

Недостатком реконфигурируемого асинхронного сумматора-умножителя являются ограниченные функциональные возможности, не позволяющие выполнять более сложные арифметические алгоритмы.

Решаемой задачей является создание реконфигурируемого вычислительного конвейера с расширенными функциональными возможностями.

Достигаемым техническим результатом является увеличение реконфигурируемости заявляемого устройства и возможность адаптации вычислительной системы под структуру решаемой задачи.

Для достижения технического результата в реконфигурируемом вычислительном конвейере, содержащем счетное поле, состоящее из вычислительных ячеек, содержащих блок арифметического оператора и образующих матрицу из m-строк и k-столбцов, при этом каждая вычислительная ячейка соединена, по крайней мере, с одной соседней и включает в себя первый и второй мультиплексоры n в 1, первая группа входов которых является входами вычислительной ячейки, новым является то, что в каждую вычислительную ячейку дополнительно введены блок конфигурационной памяти, первый, второй, третий блоки программируемой задержки, группы выходов первого и второго из которых соединены соответственно с группами входов блока арифметического оператора, группа выходов которого соединена с первой группой входов блока управления знаком результата, группа выходов которого соединена с первой группой входов третьего блока программируемой задержки, группа выходов которого является выходами вычислительной ячейки, первая и вторая группы выходов блока конфигурационной памяти соединены со вторыми группами входов первого и второго мультиплексоров соответственно, группы выходов которых соединены с первыми группами входов первого и второго блоков программируемой задержки, вторые группы входов которых соединены с третьей и четвертой группами выходов блока конфигурационной памяти, пятая, шестая и седьмая группы выходов которого соединены соответственно со вторыми группами входов блока арифметического оператора, блока управления знаком результата и третьим блоком программируемой задержки, группа входов блока конфигурационной памяти является второй группой входов вычислительной ячейки, при этом первые группы входов вычислительных ячеек первого столбца и группы выходов вычислительных ячеек k-столбца являются соответственно группами входов и выходов счетного поля, группы входов которого являются входами устройства, вторые группы входов вычислительных ячеек объединены между собой и являются второй группой входов счетного поля и второй группой входов устройства.

Новая совокупность существенных признаков позволяет расширить функциональные возможности устройства за счет образования новой конфигурации вычислительных ячеек.

Сущность изобретения поясняется чертежами.

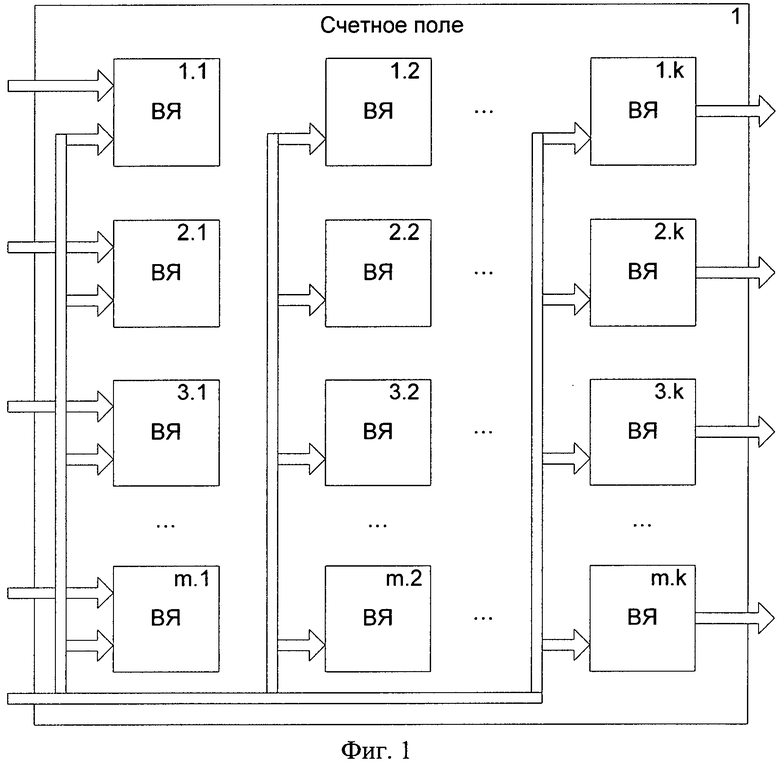

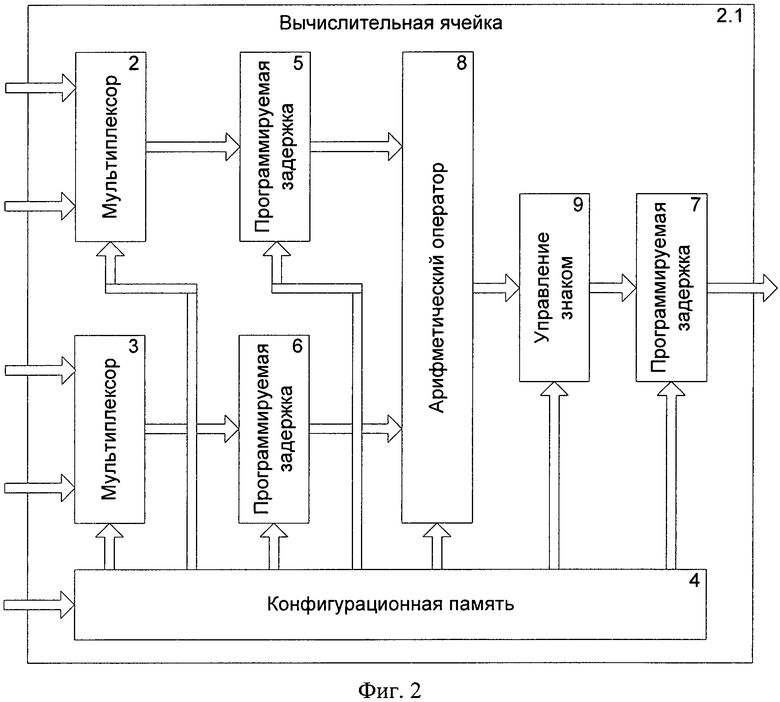

На фиг.1 изображена структурная схема реконфигурируемого вычислительного конвейера.

На фиг.2 изображена структурная схема вычислительной ячейки (ВЯ).

Реконфигурируемый вычислительный конвейер содержит счетное поле 1, которое состоит из вычислительных ячеек (ВЯ 1.1…ВЯ m.k), содержащих блок арифметического оператора 8 и образующих матрицу из m-строк и k-столбцов. Каждая вычислительная ячейка соединена, по крайней мере, с одной соседней и включает в себя первый 2 и второй 3 мультиплексоры n в 1, первые группы входов которых являются входами вычислительных ячеек ВЯ 1.1…ВЯ m.k. В каждую вычислительную ячейку дополнительно введены блок конфигурационной памяти 4, первый 5, второй 6, третий 7 блоки программируемой задержки, группы выходов первого 5 и второго 6 из которых соединены соответственно с группами входов блока арифметического оператора 8, группа выходов которого соединена с первой группой входов блока управления знаком результата 9, группа выходов которого соединена с первой группой входов третьего блока программируемой задержки 7, группа выходов которого является группой выходов вычислительных ячеек (ВЯ 1.1…ВЯ m.k.), первая и вторая группы выходов блока конфигурационной памяти 4 соединены со вторыми группами входов первого 2 и второго 3 мультиплексоров соответственно, группы выходов которых соединены с первыми группами входов первого 5 и второго 6 блоков программируемой задержки, вторые группы входов которых соединены с третьей и четвертой группами выходов блока конфигурационной памяти 4, пятая, шестая и седьмая группы выходов которого соединены соответственно со вторыми группами входов блока арифметического оператора 8, блока управления знаком результата 9 и третьим блоком программируемой задержки 7, группа входов блока конфигурационной памяти 4 является второй группой входов вычислительных ячеек (ВЯ 1.1…ВЯ m.k.), при этом первые группы входов всех вычислительных ячеек первого столбца ВЯ 1.1…ВЯ m.1 и группы выходов всех вычислительных ячеек k-столбца ВЯ 1.k…ВЯ m.k являются соответственно группами входов и выходов счетного поля 1, группы входов которого являются входами устройства, вторые группы входов всех вычислительных ячеек (ВЯ 1.1…ВЯ m.k.) объединены между собой и являются второй группой входов счетного поля 1 и второй группой входов устройства.

Устройство работает следующим образом.

Реконфигурируемое счетное поле 1 представляет собой массив вычислительных ячеек (ВЯ 1.1…ВЯ m.k.). Каждая вычислительная ячейка может выполнять базовую арифметическую операцию: сложение, вычитание, умножение, деление или выполнять транзитную передачу входных данных на выход ячейки. Операция, выполняемая ячейкой в данный момент, задается значением, хранящимся в конфигурационной памяти.

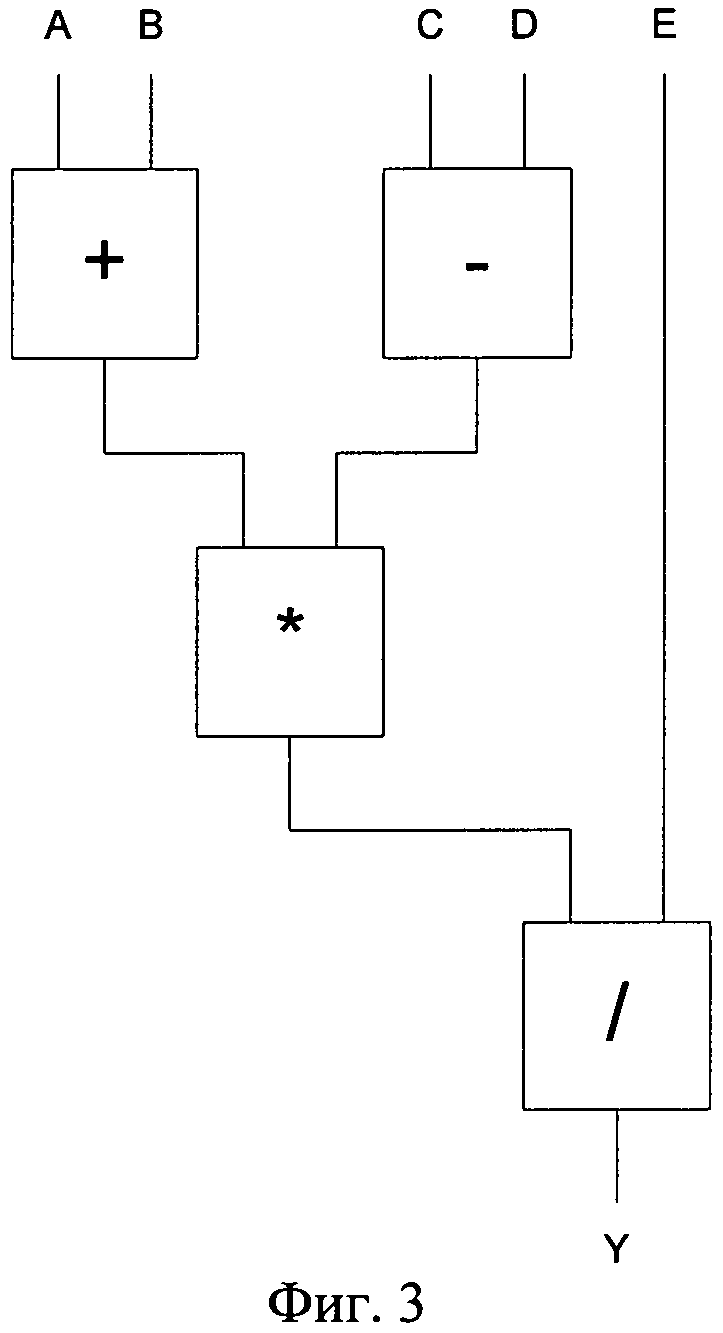

Для расчета заданного арифметического выражения необходимо на счетном поле 1 построить вычислительное дерево, которое будет вычислять заданное выражение. Так, например, для расчета арифметического выражения:

на счетном поле 1 необходимо сформировать вычислительное дерево, представленное на фиг.3.

Вычислительное дерево на счетном поле 1 формируется за счет задания связей между ячейками, которое осуществляется с помощью мультиплексоров 2 и 3 путем выбора одного из входов мультиплексора, данные с которого будут поступать через блоки программируемой задержки 5 и 6 на вход арифметического оператора 8. Таким образом, управляя мультиплексорами 2 и 3 с помощью информации, записанной в конфигурационной памяти 4, фактически задается связь между выходом одной вычислительной ячейки и входом другой.

Так как разные арифметические операции выполняются за различное число тактов, то для обеспечения одновременного прихода операндов на следующую вычислительную ячейку необходимо осуществлять выравнивание потока данных, используя блоки программируемой задержки 5, 6 и 7. Программируемая задержка может быть индивидуально задана для каждого операнда с помощью блоков 5 и 6 или блока 7 для выхода арифметического оператора 8. Количество тактов, на которые задерживается поток данных, задается информацией, хранящейся в конфигурационной памяти 4.

Результат арифметического оператора 8 поступает на входы блока управления знаком 9, который манипулируя битом, отвечающим за знак числа, управляет знаком результата арифметического оператора 8. Инверсия этого бита приводит к смене знака числа на противоположный. Установка бита делает число отрицательным, и наконец, сброс бита делает число положительным. Функция блока управления знаком результата задается информацией из конфигурационной памяти 4.

Для подтверждения работоспособности реконфигурируемого вычислительного конвейера в программируемой логической интегральной схеме было реализовано счетное поле размерности 6 строк на 8 столбцов. Испытания подтвердили работоспособность заявляемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ M N-РАЗРЯДНЫХ ЧИСЕЛ | 2012 |

|

RU2486576C1 |

| МНОГОПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2012 |

|

RU2502126C1 |

| РЕКОНФИГУРИРУЕМЫЙ АСИНХРОННЫЙ СУММАТОР-УМНОЖИТЕЛЬ | 1999 |

|

RU2159464C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| Устройство для определения среднего арифметического значения | 1989 |

|

SU1658169A1 |

| РЕКОНФИГУРИРУЕМОЕ УСТРОЙСТВО АППАРАТНОЙ РЕАЛИЗАЦИИ ГЕНЕТИЧЕСКОГО АЛГОРИТМА | 2014 |

|

RU2572379C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ АРИФМЕТИЧЕСКИХ ВЫЧИСЛЕНИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2011 |

|

RU2477513C1 |

| Устройство для обработки многотоновых изображений | 1987 |

|

SU1416975A1 |

| Матричное вычислительное устройство тригонометрических функций | 1984 |

|

SU1238060A1 |

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано в высокоскоростных арифметико-логических устройствах или в качестве самостоятельного вычислительного элемента в гибридных вычислительных системах в качестве ускорителя арифметических вычислений. Техническим результатом является увеличение реконфигурируемости вычислительного конвейера и возможность адаптации вычислительной системы под структуру решаемой задачи. Конвейер содержит счетное поле, состоящее из вычислительных ячеек, образующих матрицу из m-строк и k-столбцов, при этом вычислительная ячейка содержит 2 мультиплексора, 3 блока программируемых задержек, блок арифметического оператора, блок управления знаком и блок конфигурационной памяти. 3 ил.

Реконфигурируемый вычислительный конвейер, содержащий счетное поле, состоящее из вычислительных ячеек, образующих матрицу из m-строк и k-столбцов, при этом каждая вычислительная ячейка соединена, по крайней мере, с одной соседней и включает в себя два мультиплексора n в 1, первая группа входов которых является входами вычислительной ячейки, отличающийся тем, что в каждую вычислительную ячейку дополнительно введены блок конфигурационной памяти, первый, второй, третий блоки программируемой задержки, группы выходов первого и второго из которых соединены соответственно с группами входов блока арифметического оператора, группа выходов которого соединена с первой группой входов блока управления знаком результата, группа выходов которого соединена с первой группой входов третьего блока программируемой задержки, группа выходов которого является выходами вычислительной ячейки, первая и вторая группы выходов блока конфигурационной памяти соединены со вторыми группами входов первого и второго мультиплексоров соответственно, группы выходов которых соединены с первыми группами входов первого и второго блоков программируемой задержки, вторые группы входов которых соединены с третьей и четвертой группами выходов блока конфигурационной памяти, пятая, шестая и седьмая группы выходов которого соединены соответственно со вторыми группами входов блока арифметического оператора, блока управления знаком результата и третьим блоком программируемой задержки, группа входов блока конфигурационной памяти является второй группой входов вычислительной ячейки, при этом первые группы входов вычислительных ячеек первого столбца и группы выходов вычислительных ячеек k-столбца являются соответственно группами входов и выходов счетного поля, группы входов которого являются входами устройства, вторые группы входов вычислительных ячеек объединены между собой и являются второй группой входов счетного поля и второй группой входов устройства.

| РЕКОНФИГУРИРУЕМЫЙ АСИНХРОННЫЙ СУММАТОР-УМНОЖИТЕЛЬ | 1999 |

|

RU2159464C1 |

| СПОСОБ, УСТРОЙСТВО И КОМАНДА ДЛЯ ВЫПОЛНЕНИЯ ЗНАКОВОЙ ОПЕРАЦИИ УМНОЖЕНИЯ | 2003 |

|

RU2275677C2 |

| Арифметическое устройство | 1984 |

|

SU1229754A1 |

| US 20100045351 A1, 25.02.2010 | |||

| US 7759974 B1, 20.07.2010. | |||

Авторы

Даты

2012-09-20—Публикация

2011-06-23—Подача