1

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих процессорах в специализированных вычислительных устройствах.

Цель изобретения - упрощение устройства.

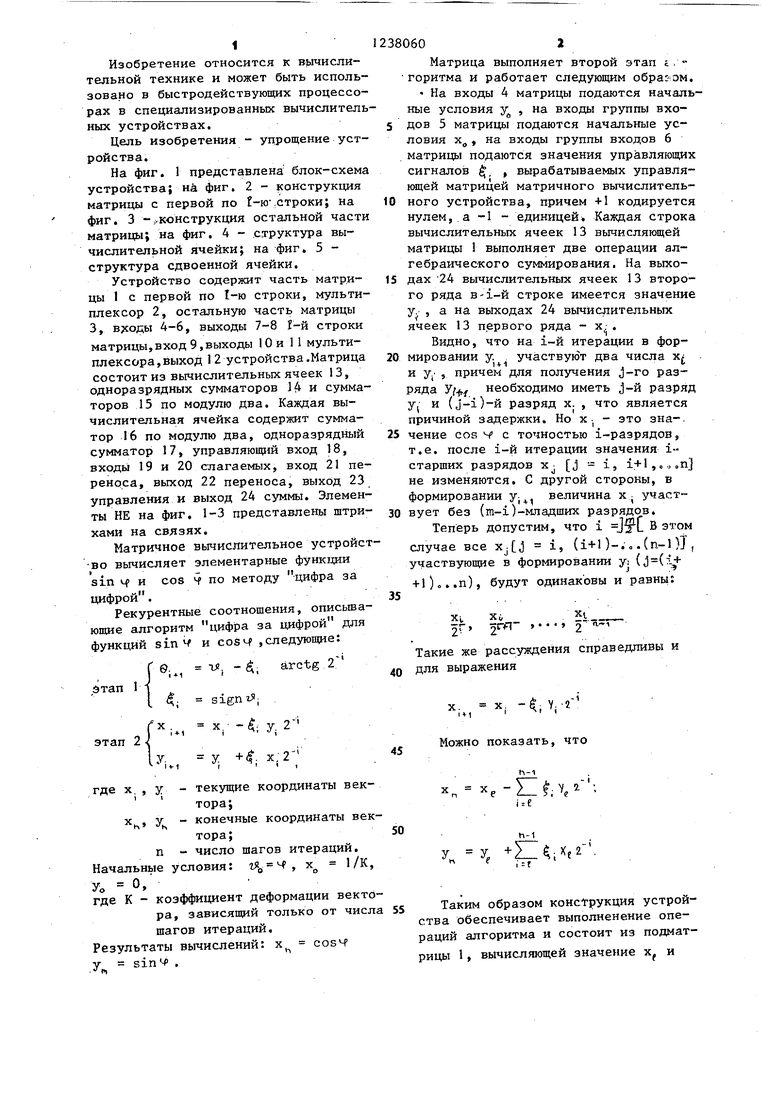

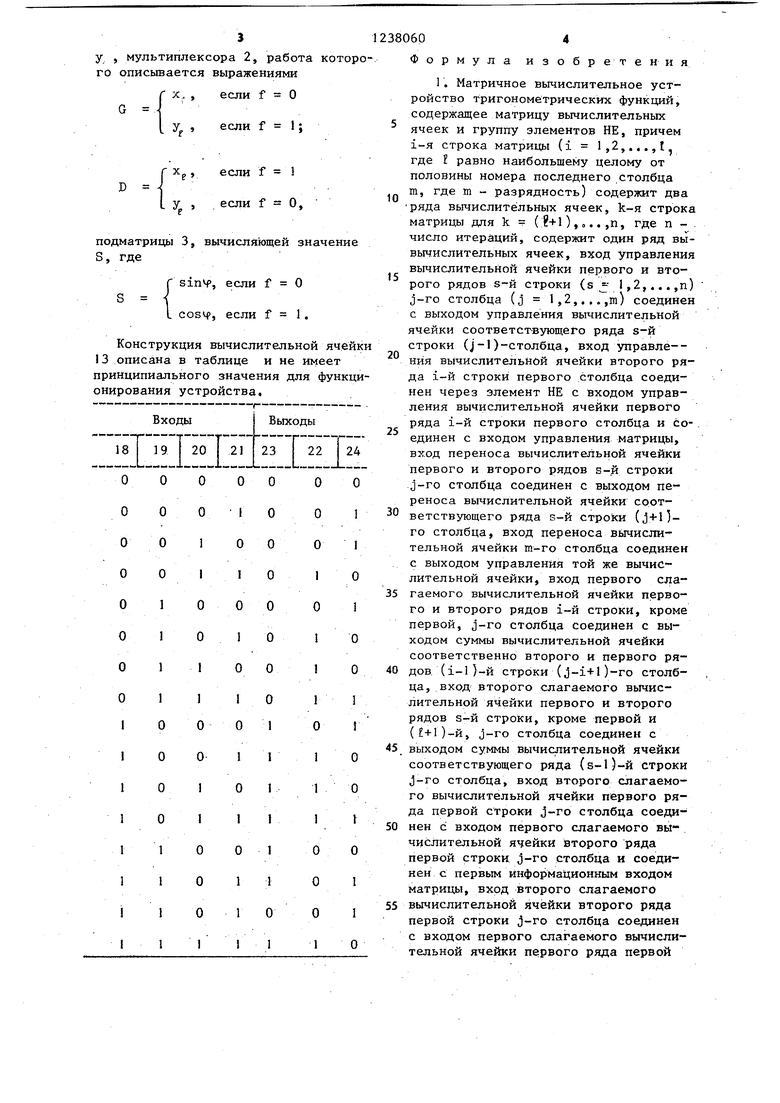

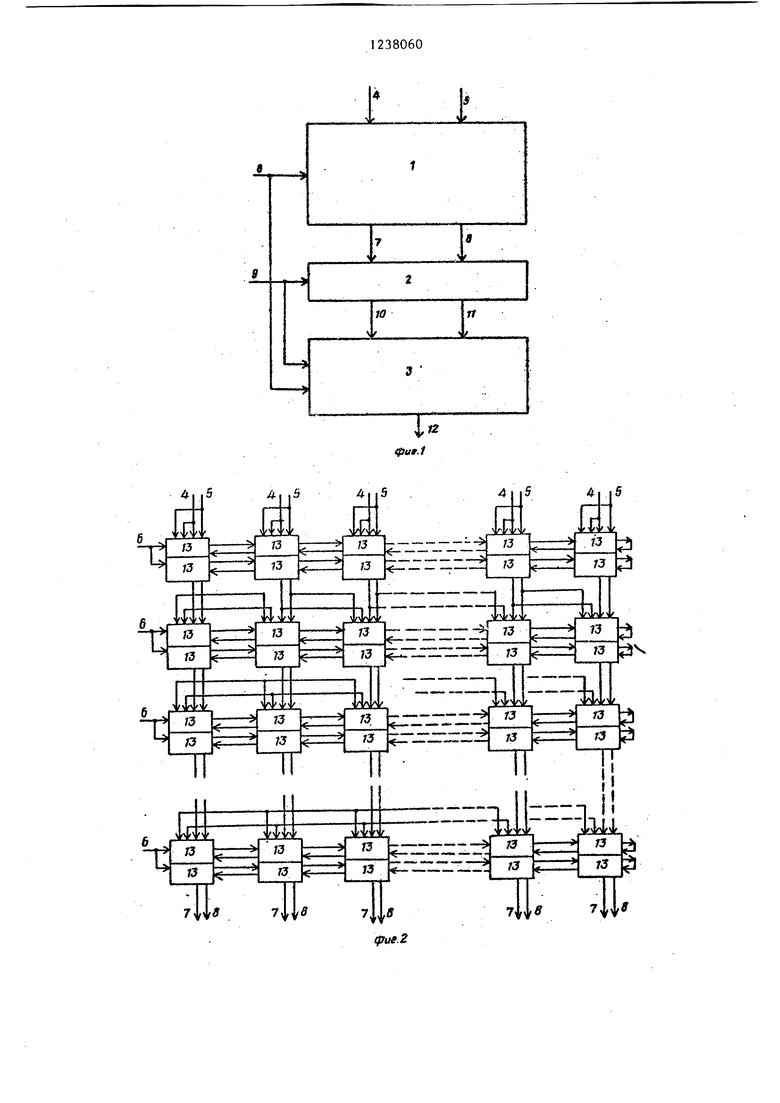

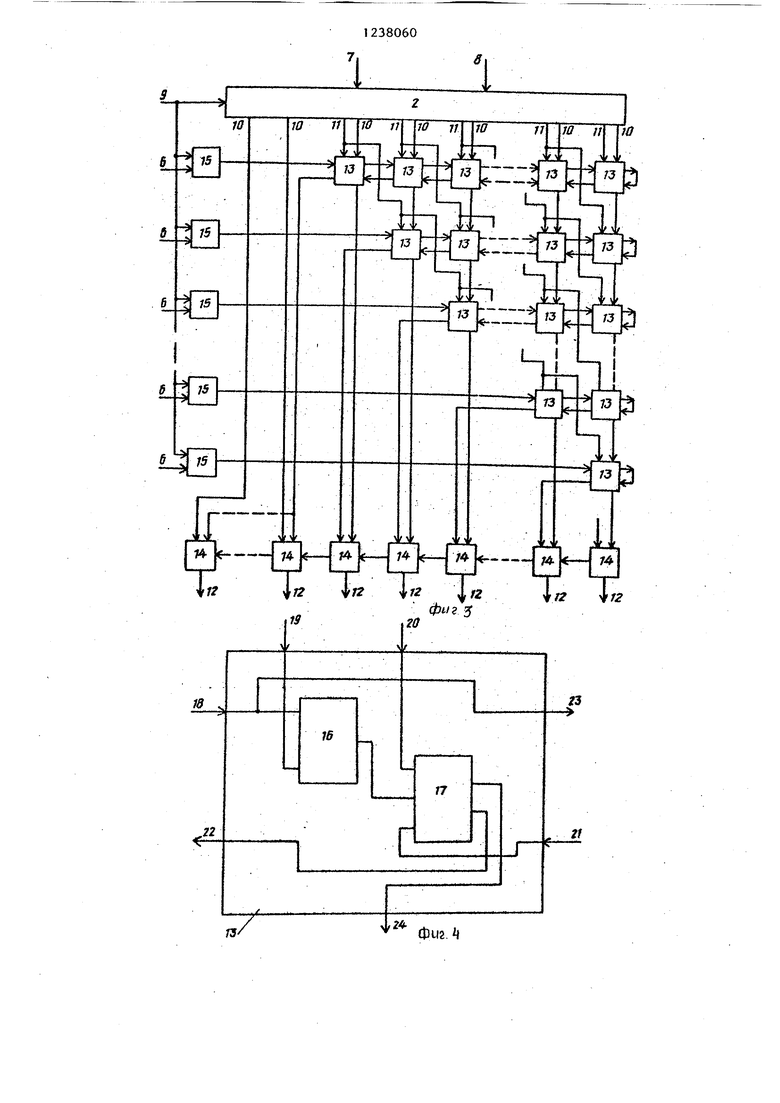

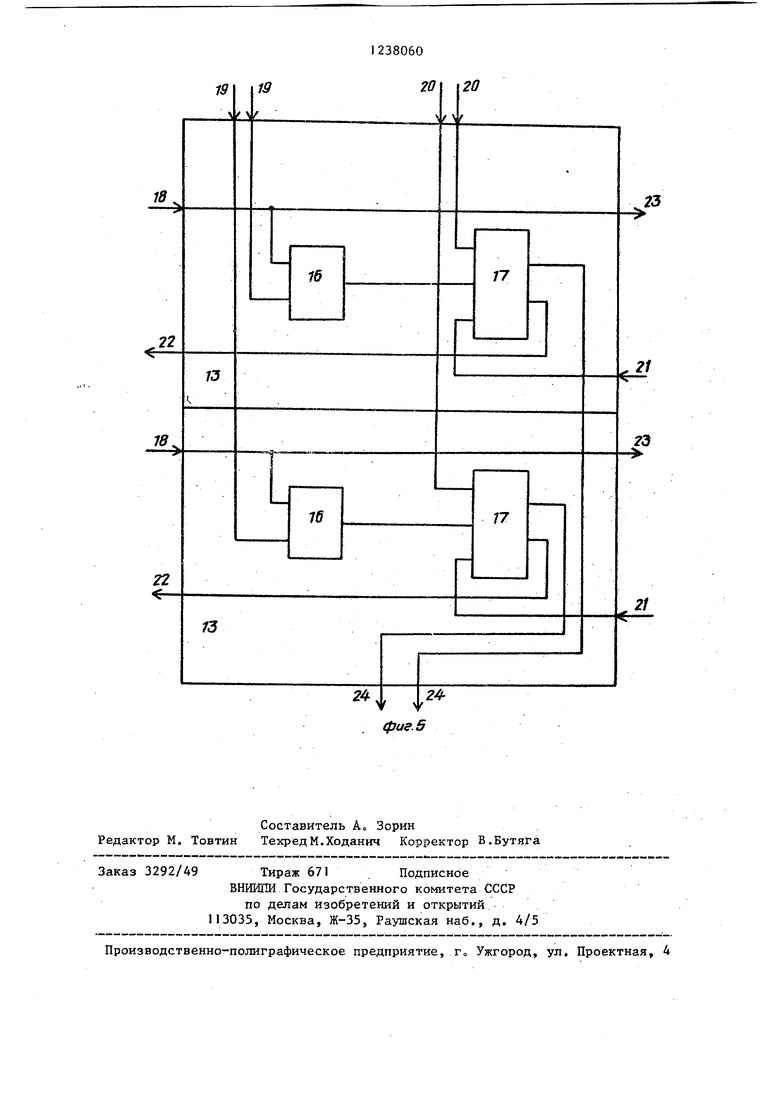

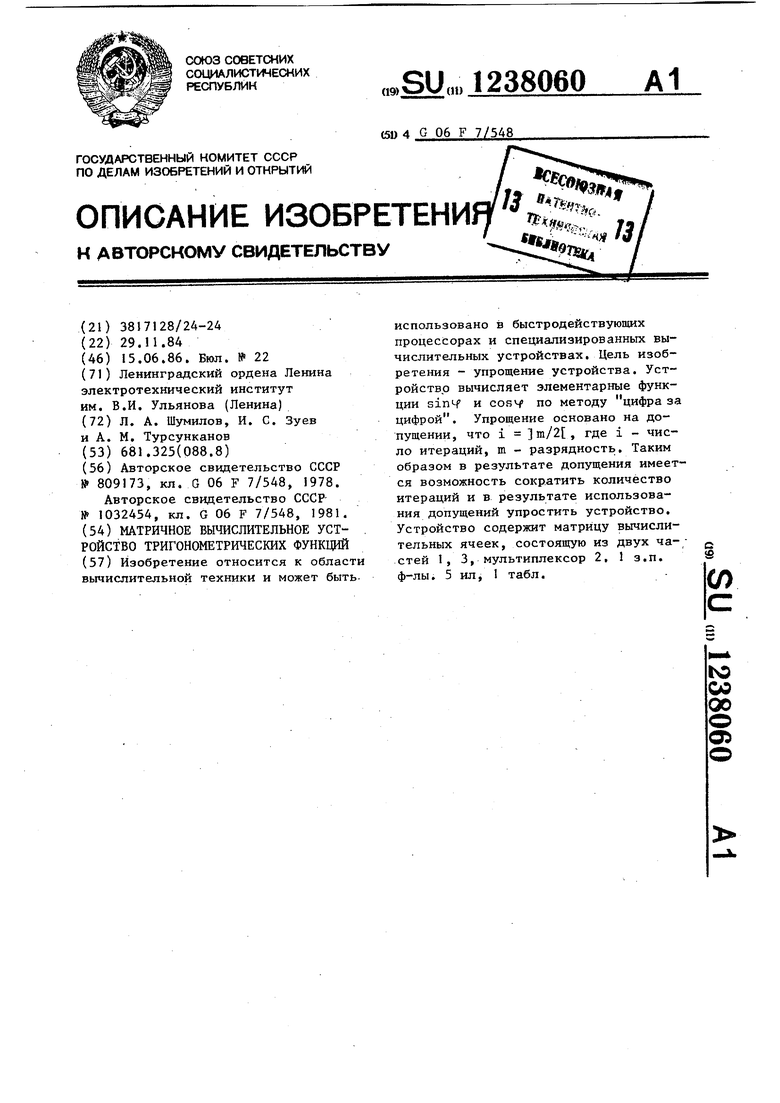

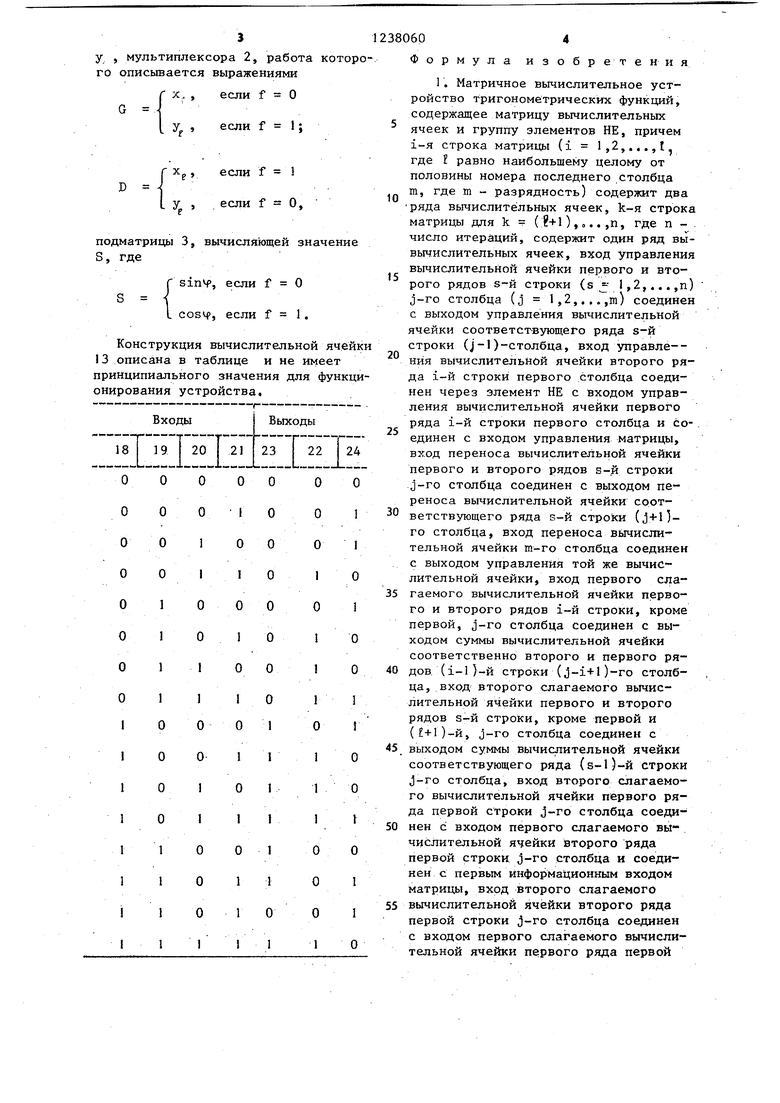

На фиг. 1 представлена блок-схема устройства} ни фиг. 2 - конструкция матрицы с первой по f-ю .строки; на фиг. 3 -;.конструкция остальной части матрицы; на фиг. 4 - структура вычислительной ячейки; на фиг. 5 - структура сдвоенной ячейки.

Устройство содержит часть матрицы 1 с первой по t-ю строки, мультиплексор 2, остальную часть матрицы 3, входы 4-6, выходы 7-8 Г-й строки матрицы,вход 9,выходы 10 и 11 мультиплексора ,выход 12 устройства .Матрица состоит из вычислительных ячеек 13, одноразрядных сумматоров А и сумматоров 15 по модулю два. Каждая вы- числительна.я ячейка содержит сумматор 16 по модулю два, одноразрядный сумматор 17, управляющий вход 18, входы 19 и 20 слагаемых, вход 21 переноса, выход 22 переноса, выход 23 управления и выход 24 суммы. Элементы НЕ на фиг, 1-3 представлены штрихами на связях.

Матричное вычислительное устройст во вычисляет элементарные функ1л 1И sin ч и cos ч по методу цифра за

цифрой.

Рекурентные соотношения, описьта- ющие алгоритм за цифрой для функций sin Ч и cos ,следующие:

&.. L - d; arctg 2

зтап i

этап 2

.

- -.

signi ij

- ; У. 2X.

У:

у. +t. х,2

где X., у - текущие координаты вектора;

Xf, У конечные координаты вектора;

п - число шагов итераций. Начальные условия: гйд Ч , х 1/К, У. 0,

где К - коэффициент деформации вектора, зависящий только от числа шагов итераций. Результаты вычислений: х cosч

у sin .

- р

602

Матрица выполняет второй этап с , горитма и работает следующим обрагэм. На входы 4 матрицы подаются начальные условия у , на входы группы входов 5 матрицы подаются начальные условия Хд, на входы группы входов 6 матрицы подаются значения управляющих сигналов , , вырабатываемых управля- кяцей матрицей матричного вычислительного устройства, причем +1 кодируется нулем,.а -1 - единицей. Каждая строка вычислительных ячеек 13 вычисляющей матрицы 1 выполняет две операции алгебраического суммирования. На выходах 24 вычислительных ячеек 13 второго ряда В 1-й строке имеется значение у. , а на выходах 24 вычислительных ячеек 13 первого ряда - х,. .

Видно, что на 1-й итерации в формировании у. участвуют два числа х и у/ , причем для получения j-ro разяда необходимо иметь J-й разряд у и (J-i)-й разряд X. , что является причиной задержки. Но х - это зна-.

чение cos ч с точностью i-разрядов, т.е. после i-й итерации значения 1- старших разрядов Xj j - i, i+l,,, n не изменяются. С другой стороны, в формировании у, величина х- участвует без (m-i)-младших разрядов.

Теперь допустим, что 1 L В этом случае все i, (i+1)-;..(n-1) , участвующие в формировании у: (j(i+ +l)...n), будут одинаковы и равны:

2ЛТ

Xl

Такие же рассуждения справедливы и для выражения

,„

Можно показать, что

х, .a-:

i e

50

n-1

У. Уе

Таким образом конструкция устройства обеспечивает выполненение операций алгоритма и состоит из подматрицы 1, вычисляющей значение х, и

31238060

у , мультиплексора 2, работа котороФ

го описывается выражениями

если f О

G

у , если f 1;

D

Хр , если f 5

у , если f О,

подматрицы 3, вычисляющей значение S, где

S

sinvp, если f О созц), если f 1.

Конструкция вычислительной ячейки 13 описана в таблице и не имеет принципиального значения для функционирования устройства.

5

0

5

0

5

0

5

0

5

Формула изобретения

1. Матричное вычислительное устройство тригонометрических функций, содержащее матрицу вычислительных ячеек и группу элементов НЕ, причем i-H строка матрицы (1 1,2,...,1, где равно наибольшему целому от половины номера последнего столбца т, где m - разрядность) содержит два ряда вычислительных ячеек, k-я строка матрицы для k (+l),o..,n, где п - . число итераций, содержит один ряд вы- вьмислительных ячеек, вход управления вычислительной ячейки первого и второго рядов s-й строки (s - 1,2,...,п) j-ro столбца (j l,2,...,in) соединен с выходом управления вычислительной ячейки соответствующего ряда s-й строки (J-1)-столбца, вход управле-- ния вычислительной ячейки второго ряда i-й строки первого столбца соединен через элемент НЕ с входом управления вычислительной ячейки первого ряда i-й строки первого столбца и со-. единен с входом управления матрицы, вход переноса вычислительной ячейки первого и второго рядов s-й строки j-ro столбца соединен с выходом переноса вычислительной ячейки соответствующего ряда s-й строки (j+l)- го столбца, вход переноса вычислительной ячейки т-го столбца соединен с выходом управления той же вычислительной ячейки, вход первого слагаемого вычислительной ячейки первого и второго рядов i-й строки, кроме первой, j-ro столбца соединен с выходом суммы вычислительной ячейки соответственно второго и первого рядов (i-l)-й строки (j-i+1)-го столбца, вход второго слагаемого вычислительной ячейки первого и второго рядов s-й строки, кроме первой и (+1)-й, j-ro столбца соединен с выходом суммы вычислительной ячейки соответствующего ряда (з-О-й строки j-ro столбца, вход второго слагаемого вычислительной ячейки первого ряда первой строки j-ro столбца соединен с входом первого слагаемого вычислительной ячейки jBToporo ряда первой строки j-ro столбца и соединен с первым информационным входом матрицы, вход второго слагаемого вычислительной ячейки второго ряда первой строки j-ro столбца соединен с входом первого слагаемого вычислительной ячейки первого ряда первой

строки j-го столбца и соединен с вторым информационным входом матрицы, вьгхрд суммы вычислительной ячейки первого и второго рядов i-й стро- ки, кроме t-й, первого столбца соединен с входом первого слагаемого вычислительной ячейки соответственно второго и.первого рядов (1+1)-й стро ки .последовательно с второго по (1+1)-й столбец, о т л и ч а ю -i . щ е е с я тем, что, с целью упроще ния устройства, оно содержит мультиплексор , группу одноразрядных сумматоров и группу сумматоров по модулю два, причем (E+q)-я строка матрицы (q l,2,..c,n-l) содержит вычисли- тельные ячейки только с номерами ,(l+q), (5+q+l) , о.. ,m, выхода суммы вьгчисли телькых ячеек первого рядэ: 1-й строки каждого столбца соединены , с первым информационным входом мультиплексора, второй информационный вход которого соединен с выходами суммы вычислительньж ячеек второго .ряда Г-й строки каждого столбца, уп- равляющий вход мультиплексора соединен с входом задания кода функции устройства, вход управления вьгчисли- тельной ячейки (1+д)-й строки (2+q)- го столбца соединен с выходом q-ro сумматора по модулю Д6а, входами которого являются (E+q)-й разряд управляющего входа матрицы и вход кода функции устройства, выход первого разряда первого выхода мультиплексора соединен через злемент НЕ с входами первого слагаемого вычислительных ячеек (l+q)-и строки (E+q)-ro столбца, выход р-го разряда первого выхода мультиплексора (р 2,3,...,Е соединен с входом первого слагаемого вычислительной ячейки (I+q)-й строки (l+q+p-l)-ro столбца, вход, второго слагаемого вычислительной ячейки (1+1) и строки j-ro столбца соединен с выходом j-ro разряда второго выхода мультиплексора, выход суммы вычислительной ячейки (.t+q)-й строки (E+q)-ro столбца соединен с входом первого слагаемого (t+q)-ro одноразрядного сумматора, выход переноса вычислительной ячейки ( )-й строки (.+q)-ro столбца, кроме q 1, соединен с входом второго слагаемого (1+ +q-1)-го одноразрядного сумматора, выход переноса вычислительной ячейки (+1)-й строки Ц1+1)-го столбца соединен через элемент НЕ с входами второго слагаемого с первого по f-й одноразрядных сумматоров, вход первого слагаемого ,1-го одноразрядного сумматора для J 6 I соединен с выходо j-ro разряда второго выхода мультиплексора, вход переноса J-ro одноразрядного сумматора соединен с выходом переноса (j+l)-ro одноразрядного сумматора, выход суммы каждого одноразрядного сумматора является выходо соответствующего разряда значения функции устройства, вход второго слагаемого т-го одноразрядного сумматора соединен с входом логической I устройства

2. Устройство по По 1, отличающееся тем, что каждая вычислительная ячейка содержит сумматор по модулю два и одноразрядный сумматор, вход первого слагаемого которого соединен с входом второго слагаемого вычислительной ячейки, вход первого слагаемого которой соединен с первым входом сумматора по модулю два, второй вход которого соединен с входом и выходом управления вычислительной ячейки, вход пе реноса которой соединен с входом переноса одноразрядного сумматора, вход второго слагаемого которого соединен с выходом сумматора по модулю два, выход суммы и переноса одноразрядного сумматора соединен с одноименными выходами вычислительной ячейки.

А

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1984 |

|

SU1247892A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1092497A1 |

| Вычислительное устройство | 1983 |

|

SU1164701A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Вычислительное устройство | 1981 |

|

SU1032454A1 |

| Устройство для умножения | 1989 |

|

SU1697078A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Вычислительное устройство | 1989 |

|

SU1697077A2 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

Изобретение относится к области вычислительной техники и может быть. использовано в быстродействующих процессорах и специализированных вычислительных устройствах. Цель изобретения - упрощение устройства. Устройство вычисляет элементарные функции sin4 и COSV по методу цифра за цифрой. Упрощение основано на допущении, что i m/2, где i - число итераций, m - разрядность. Таким образом в результате допущения имеется возможность сократить количество итераций и в результате использования допущений упростить устройство. Устройство содержит матрицу вычислительных ячеек, состоящую из двух ча-; стей 1, 3, мультиплексор 2, 1 з.п. ф-лы. 5 ил, 1 табл. i (Л to 00 00

4rf

|й if2

фиг.

Составитель А Зорин Редактор М. Товтин ТехредМ.Ходанич Корректор В.Бутяга

3292/49

Тираж 671 Подписное ВНИИГШ Государственного комитета СССР

по делам Изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1981 |

|

SU1032454A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-11-29—Подача