-г

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для построения гистограммы | 1988 |

|

SU1688261A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1652982A1 |

Изобретение относится к вычислите л ь- ной технике и может быть использовано в системах обработки результатов измерений. Цель изобретения - повышение быстродействия. Устройство содержит блок 1 ассоциативной памяти, комбинационный сумматор 2, три сумматор 3,5 м If. сумма- тор-вычитатель 6. два мультиплексора 7 и 9. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, злемент НЕ 13, элемент И-НЕ 14, элемент И 15. два регистра 4 и 17, регистр 20 сдвига, сметчик 21, элемент 22 задержки, генератор 23 тактовых импульсов. За счет анализа разрядных срезов в блоке ассоциативной памяти среднее значение определяется без вычисления суммы чисел за время, не зависящее от их количества. 1 ил., 1 табл.

а ел

00

I

Изобретение относится к вычислительной технике и может быть использовано в системах обработки результатов измерений.

1ель изобретения - повышение быстродействия.

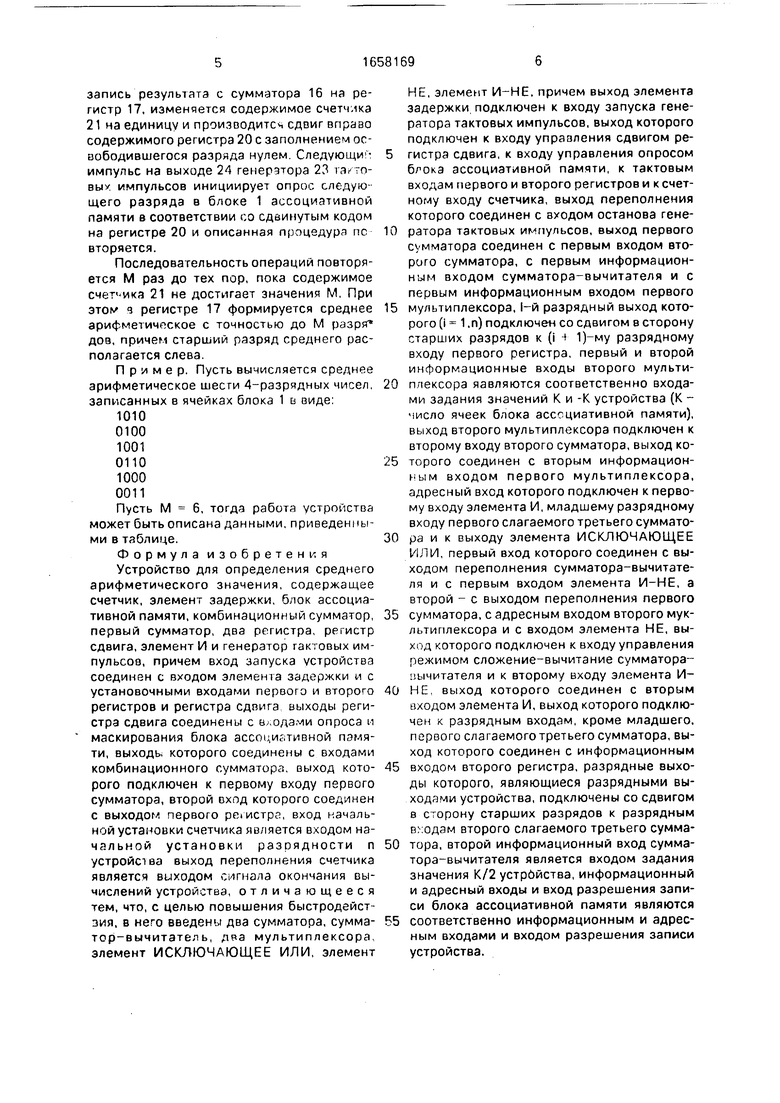

На чертеже изображена струнчурная схема устройства.

Устройство для определения среднего арифметического значения содержит блок 1 ассоциативной памяти, комбинационный сумматор 2, первый 3 сумматор, первый регистр 4, второй сумматор 5, сумматор-вычи- 6, первый мультиплексор 7, вход 8 задания значения К/2 устройства (К число ячеек блока ассоциативной памяти), вюрой мультиплексор 3, входы 10 и 11 задания значений соответственно К и -К устройства, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, элемент НЕ 13, элемент И-НЕ 14, элемент 15 И. третий сумматор 16, второй регистр 1 Л информационный выход 18 устройства, вход 19 запуска устройства, регистр 20 сдвига, счетчик 21, элемент 22 задержки, генератор 23 тактовых импульсов и его выход 24, вход 25 начальной установки разрядности устройства, выход 26 сигнала окончания работы устройства, информационный 27 и адресный 28 входы устройства, вход 29 раз- зап ICH устройства.

Устройство работает следующим обра зом.

Перед началом работы по входу 25 в счетчик 1 заносится код М фебуемой раз- ряднос и результа га (попученного среднего арифметического).

Сигнал запуска, подаваемый по входу 19, устанавливает регистр 20 в исходное состояние (все разряды, кроме старшего, обнулены), устанавливает в нуль регистры 4 и 17, через элемент 22 задержки запускает генератор 23 тактовых импульсоо, который начинает формировать на своем выходе 24 последовательность импульсов По переднему фронту импульса с чыхсдч 1 инициируется опрос блока 1 ассоциативной памяти, на выходах опроса которого формируются сигналы совпадения всех С юв, старший разряд которых равен единице

Информация с выходов блока 1 подается на вхсды комбинационного сумматор: 2 на выхсде которого формируется двоичный код Ci суммы единиц, стоящих в текущем (в первом такте- старшем) разряде чисел, хра- няшихся в блоке 1. Дач ее код Ci поступает на первые входы сумматора 3, и так -ак на его вторые входы поступает код с регистра 4, в первом такте состоящий из нуле1, по на выходе формируетя код Si Ci Если -К/2 Si К/2 где К - коли Р ;ТВО чисел

хранящихся в блоке 1, то к текущему значению результата, хранящемуся в регистре 17, прибавляется нуль, если Si К/2 - к результату прибавляется един ица, а из суммы Si

вычитается число К. Если S1 K/I из результата вычитается единица, а к сумме Si прибавляется число К.

Описанная операция осуществляется в следующей последовательности. Для срав0 нения Si с числом К/2 сумма Si поступает на первую группу входов сумматора-вычи- тателя 6, на управляющий вход которого поступает сигнал с выхода переполнения (ВП) сумматора 3, причем при ВП 1 произ5 водится суммирование Si с числом К/2, которое поступает извне на вторую группу входов сумматора-вычитателя 6, в противном случае производится вычитание К/2 из Si. Сигнал переноса формируемый при

0 этом, поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ И ПИ 12, на второй вход которого поступает значение бита ВП. Если значения на обоих входах элемента 12 равны, это значит, что Si принадлежит интерва5 лу -К/2, К/2 и, соответственно, сигнал с эп мента 12, который поступает на младший разряд первой группы входов сумматора 16, равен нулю. Старшие разряды первой группы входов блока 16 формируются с вы0 хода элемента И 15, на входы которого поступает сигнал с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 и сигнал с элемента И-НЕ 14, на входы которого поступают соответственно сигнал переноса с

с сумматора-вычитателя 6 и значение бита ВП, инвертированное на элементе НЕ 13. На вторую группу входов сумматора 16 поступает содержимое регистра 17, сдвигаемое при передаче за счет соответствующей

0 комму ации входов сумматора 16 и выходов регистра 17 результата. Сигнал с элемента 12, управляющий мультиплексором 7, при равенстве сигналов на входах, коммутирует на выход результат с сумматора 3, в против5 нем случае - результат с сумматора 5, где производится операция сложения суммы Si с числом К или вычитание на Si числа К. Под воздействием бита ВП, равного единице, на вторую группу входов сумматора 5 коммути0 руется через мультиплексор 9 код числа К, чем обеспечивается суммирование. В прогнано случае на вторую группу входов коммутируется число (-К) в дополнительном коде, чем достигается реализация операции

5 вычигэчия

По заднему фронту импульса с выхода 24 произаодится прием ча регист р 4 сдвинутого в сюрону старших разрядов значения ни выходе мультиплексора 7, по заднему фронту сигнала с выхода 24 производится

запись результата с сумматора 16 на регистр 17, изменяется содержимое счетчика 21 на единицу и производите сдвиг вправо содержимого регистра 20 с заполнением освободившегося разряда нулем. Следующи импульс на выходе 24 генератора 23 газовых импульсов инициирует опрос следующего разряда в блоке 1 ассоциативной памяти в соответствии со сдвинутым кодом на регистре 20 и описанная процедура пс вторяется.

Последовательность операций повторяется М раз до тех пор, пока содержимое счетчика 21 не достигает значения М, При этом в регистре 17 формируется среднее арифметическое с точностью до М разря доз, причем старший разряд среднего располагается слева.

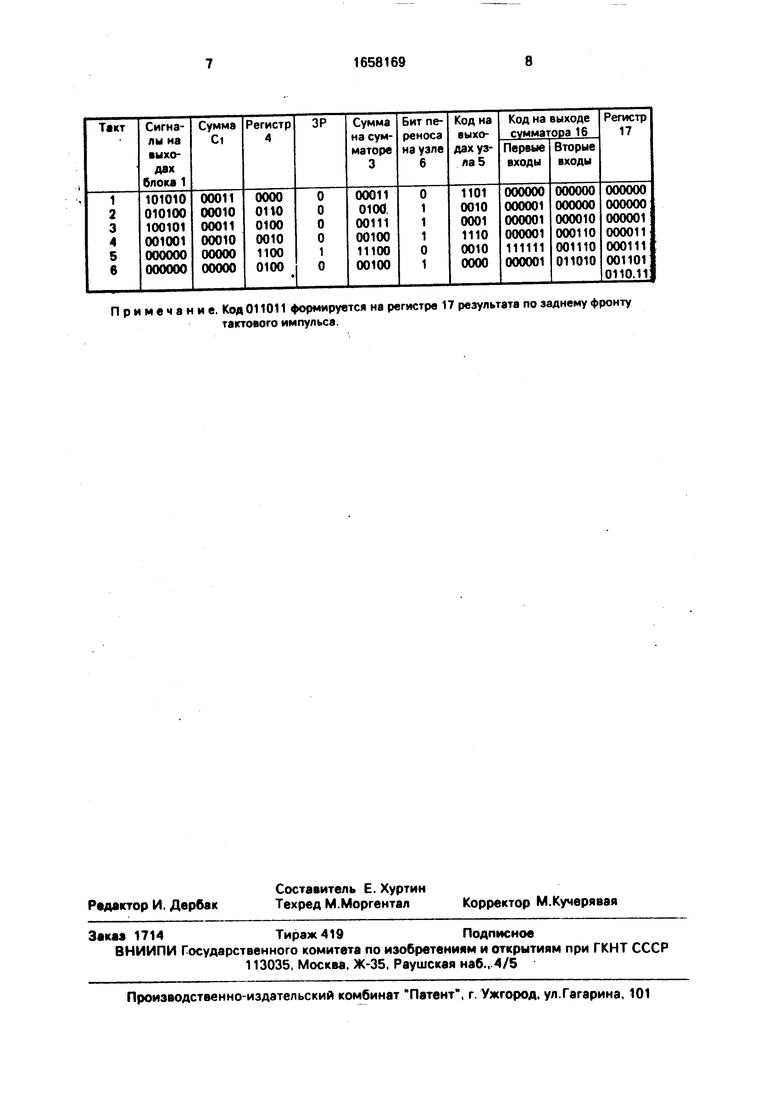

Пример. Пусть вычисляется среднее арифметическое шести 4-разрядных чисел, записанных в ячейках блока 1 в виде:

1010

0100

1001

0110

1000

0011

Пусть М 6, тогда работя устройства может быть описана данными, приведенными в таблице.

Формула изобретения

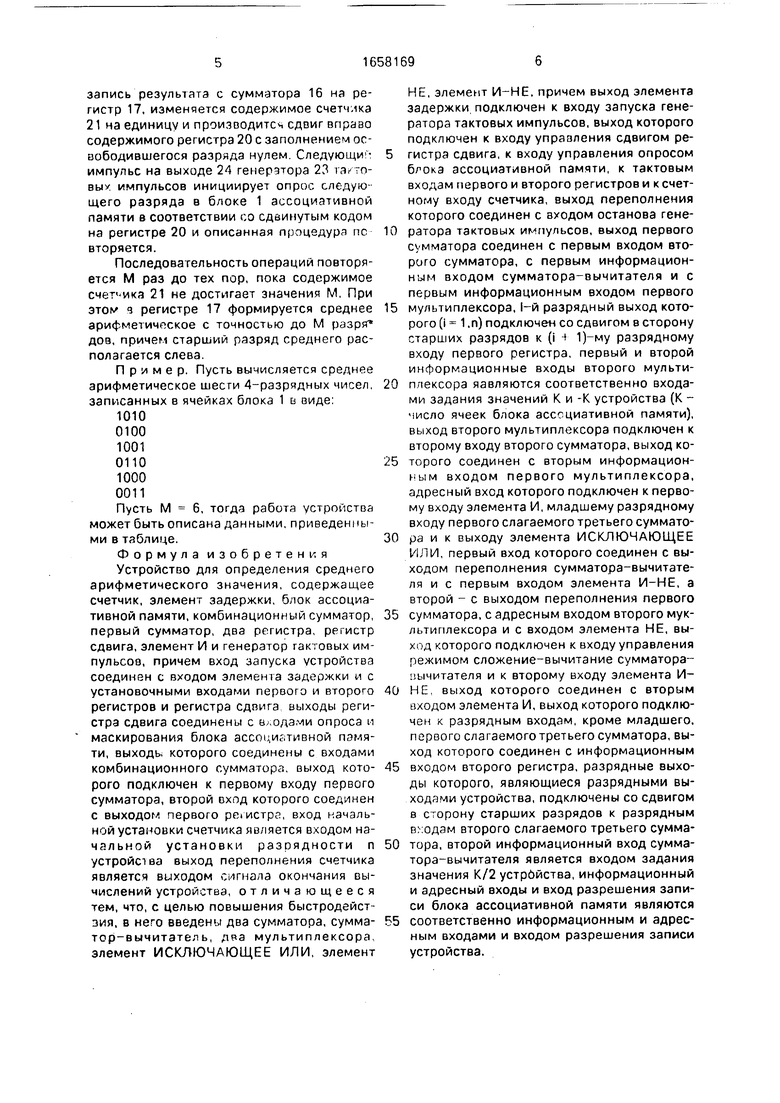

Устройство для определения среднего арифметического значения, содержащее счетчик, элемент задержки, блок ассоциативной памяти, комбинационный сумматор, первый сумматор, два регистра, регистр сдвига, элемент И и генератор тактовых им- пульсоа, причем вход запуска устройства соединен с входом элемента задержки и с установочными входами первого и второго регистров и регистра сдвига выходы регистра сдвига соединены с влодами опроса и маскирования блока ассоциативной памяти, выходы которого соединены с входами комбинационного сумматора, выход которого подключен к первому входу первого сумматора, второй вход которого соединен с выходом первого реестра, вход начальной установки счетчика является входом на- чальной установки разрядности п устройства выход переполнения счетчика является выходом сигнала окончания вычислений устройства, отличающееся тем, что, с целью повышения быстродейст- зия, в него введены два сумматора, сумма- тор-вычитатель, два мультиплексора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент

НЕ, элемент И-НЕ, причем выход элемента задержки подключен к входу запуска генератора тактовых импульсов, выход которого подключен к входу управления сдвигом регистра сдвига, к входу управления опросом блока ассоциативной памяти, к тактовым входам первого и второго регистров и к счетному входу счетчика, выход переполнения которого соединен с входом останова генератора тактовых импульсов, выход первого сумматора соединен с первым входом второго сумматора, с первым информационным входом сумматора-вычитателя и с первым информационным входом первого

мультиплексора, 1-й разрядный выход которого (I 1 ,п) подключен со сдвигом в сторону старших разрядов к (М 1)-му разрядному входу первого регистра, первый и второй информационные входы второго мультиплексора яавляются соответственно входами задания значений К и -К устройства (К - число ячеек блока ассоциативной памяти), выход второго мультиплексора подключен к второму входу второго сумматора, выход которого соединен с вторым информационным входом первого мультиплексора, адресный вход которого подключен к первому входу элемента И, младшему разрядному входу первого слагаемого третьего сумматора и к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом переполнения сумматора-вычитателя и с первым входом элемента И-НЕ, а второй - с выходом переполнения первого

сумматора, с адресным входом второго мук- льтиплексора и с входом элемента НЕ, выход которого подключен к входу управления режимом сложение-вычитание сумматора- иычитателя и к второму входу элемента И-

НЕ, выход которого соединен с вторым входом элемента И, выход которого подключен к разрядным входам, кроме младшего. первого слагаемого третьего сумматора, выход которого соединен с информационным

входом второго регистра, разрядные выходы которого, являющиеся разрядными выходами устройства, подключены со сдвигом в сторону старших разрядов к разрядным входам второго слагаемого третьего сумматора, второй информационный вход сумматора-вычитателя является входом задания значения К/2 устройства, информационный и адресный входы и вход разрешения записи блока ассоциативной памяти являются

соответственно информационным и адресным входами и входом разрешения записи устройства.

П р и м в ч а н и е. Код 011011 формируется на регистре 17 результата по заднему фронту тактового импульса.

| Устройство для определения среднего арифметического значения | 1981 |

|

SU1008751A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-23—Публикация

1989-02-07—Подача