Область техники

Настоящее изобретение относится к контроллеру для электрического транспортного средства, работающего от переменного тока (AC), а более конкретно к контроллеру для электрического транспортного средства, работающего на переменном токе, который выполнен с возможностью проведения управляющих арифметических операций блока преобразователя в FPGA (программируемой пользователем вентильной матрице).

Предшествующий уровень техники

Патентный документ 1, японская выложенная патентная заявка № 62-77867, ниже раскрывает на фиг.2, например, типовую конфигурацию устройства управления преобразователем в традиционном контроллере для электрического транспортного средства, работающего на переменном токе. В традиционных устройствах управления преобразователем, включающих в себя устройство управления преобразователем, раскрытое в патентном документе 1, арифметическая обработка посредством программного обеспечения с помощью DSP (цифрового сигнального процессора) обычно выполняется, потому что управляющая арифметика, выполняемая посредством функции управления преобразователем, зачастую является набором арифметических операций, главным образом, подразумевающих сложение, вычитание, умножение и деление аналоговых значений, и может быть легко сконфигурирована посредством арифметических операций с числами с плавающей запятой.

Как описано выше, арифметическая обработка посредством программного обеспечения с помощью DSP главным образом сконфигурирована в устройстве управления преобразователем традиционного контроллера для электрического транспортного средства, работающего на переменном токе.

Однако в случае программной арифметической обработки с помощью DSP скорость обработки обычно не может быть увеличена по сравнению с аппаратной арифметикой, что затрудняет дополнительное повышение точности управления.

Когда главным образом выполняется программная арифметика с помощью DSP, непредусмотренные задержки или расхождения во времени возникают во время обмена данными между модулем управления (аппаратным) с относительно более высокой скоростью обработки и модулем управления (программным) с более низкой скоростью обработки. Следовательно, асинхронные составляющие частоты питания, которые в идеале не должны возникать, накладываются на гармоники обратного тока, создаваемого посредством работы преобразователя, и могут мешать работе других сигнальных блоков.

Конфигурация может быть изменена на выполнение арифметической обработки, главным образом, посредством FPGA вместо арифметической обработки посредством программного обеспечения с помощью DSP. Однако устройство управления преобразователем выполняет арифметические операции, главным образом, подразумевающие сложение, вычитание, умножение и деление аналоговых значений, и соответственно FPGA, которая выполняет арифметические операции с числами с плавающей запятой, требует большего числа битов, чтобы успешно выполнять арифметические операции с высокой точностью. Следовательно, арифметические операции с высокими скоростями обработки, которые присущи характеристикам FPGA, становятся затруднительными.

Краткое изложение существа изобретения

Задачей настоящего изобретения является предоставление контроллера для электрического транспортного средства, работающего на переменном токе, который может не допускать снижения скорости обработки, чтобы гарантировать требуемую точность управления и уменьшить воздействия на обратные гармоники, когда управляющая арифметика в устройстве управления преобразователем осуществляется посредством FPGA.

Чтобы решить задачу, упомянутую выше, в электрическом транспортном средстве, работающем на переменном токе, используется контроллер для электрического транспортного средства, работающего на переменном токе, имеющий преобразователь широтно-импульсной модуляции (ШИМ), который преобразует напряжение переменного тока, подаваемое из воздушной линии через трансформатор, в напряжение постоянного тока (DC) и который содержит устройство управления преобразователем, управляющее работой ШИМ-преобразователя, при этом арифметическая обработка, выполняемая в устройстве управления преобразователем, делится на множество блоков арифметической обработки, и разделенные блоки арифметической обработки конфигурируются посредством программируемой пользователем вентильной матрицы (FPGA), а некоторые из разделенных блоков арифметической обработки конфигурируются, чтобы обеспечить одновременную параллельную обработку.

В контроллере для электрического транспортного средства, работающего на переменном токе, согласно настоящему изобретению арифметическая обработка, выполняемая в устройстве управления преобразователем, выполняется в множестве блоков арифметической обработки. Разделенные блоки арифметической обработки конфигурируются посредством FGPA, а некоторые из разделенных блоков арифметической обработки конфигурируются, чтобы обеспечивать одновременную параллельную обработку. Следовательно, снижение скорости обработки может быть исключено, чтобы обеспечивать требуемую точность управления, а воздействия на обратные гармоники могут быть уменьшены.

Краткое описание чертежей

В дальнейшем изобретение поясняется описанием предпочтительных вариантов воплощения со ссылками на сопроводительные чертежи, на которых:

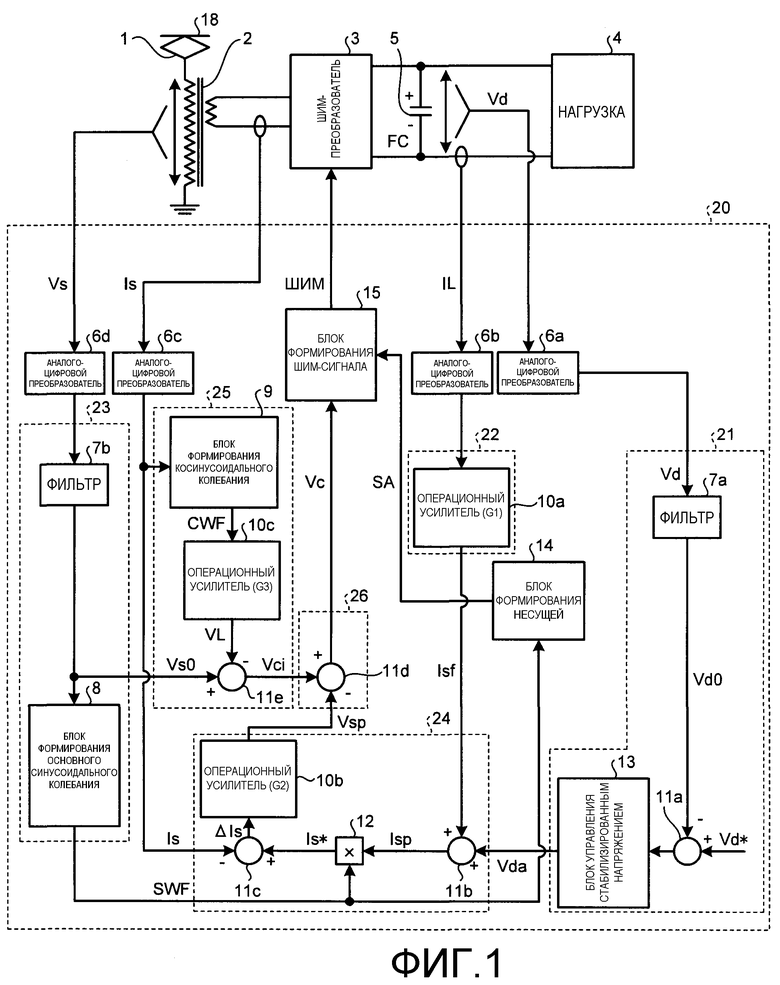

фиг.1 изображает функциональную схему устройства управления преобразователем согласно варианту осуществления настоящего изобретения;

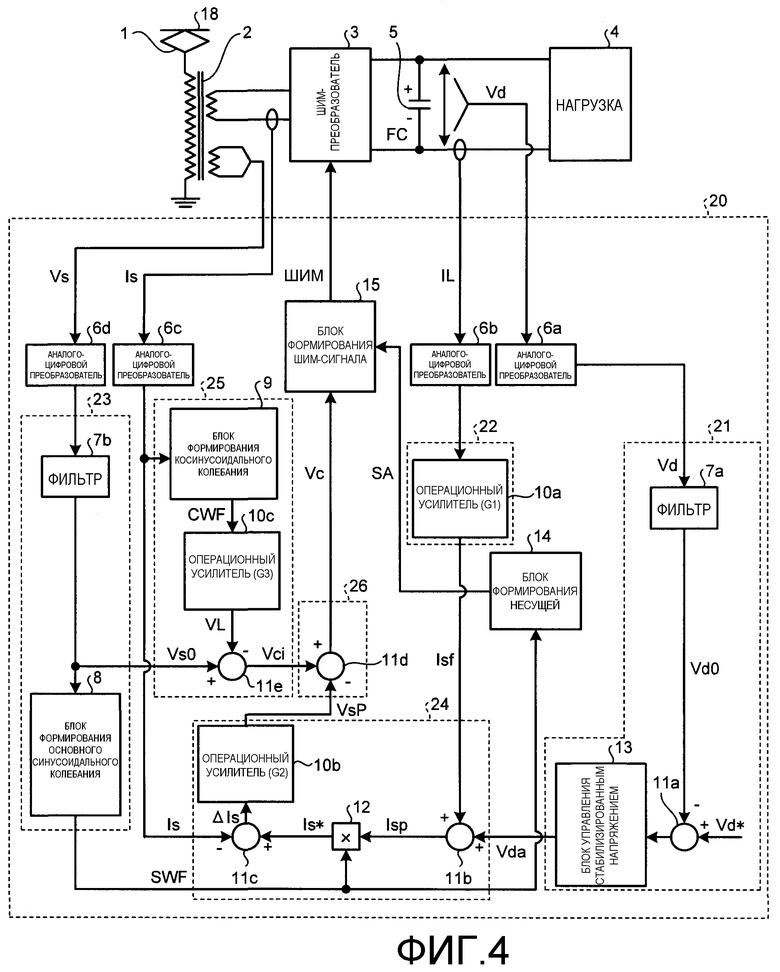

фиг.2 изображает блок-схему последовательности операций, выполняемых устройством 20 управления преобразователем, показанным на фиг.1;

фиг.3 изображает блок-схему последовательности операций, выполняемых блоком обработки входного сигнала и обработки аналого-цифрового преобразования, показанным на фиг.2;

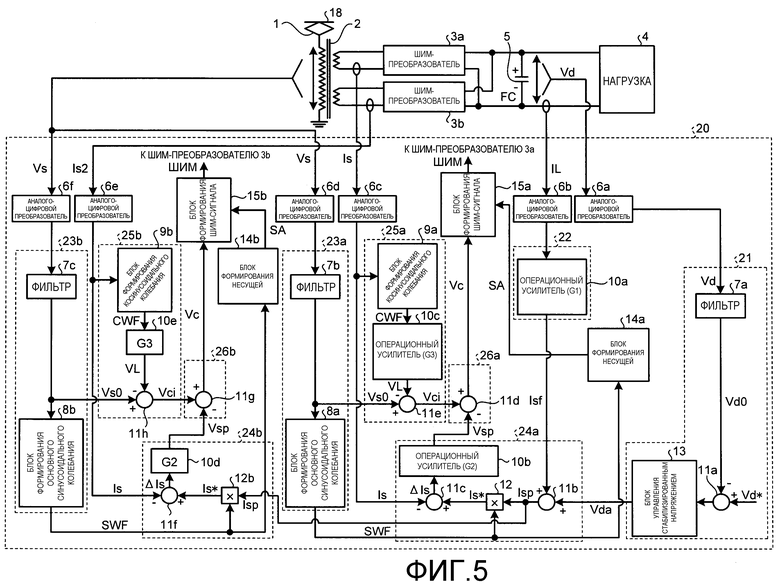

фиг.4 изображает схему контроллера, применяемого в электрическом транспортном средстве, работающем на переменном токе, имеющего конфигурацию, отличную от показанной на фиг.1;

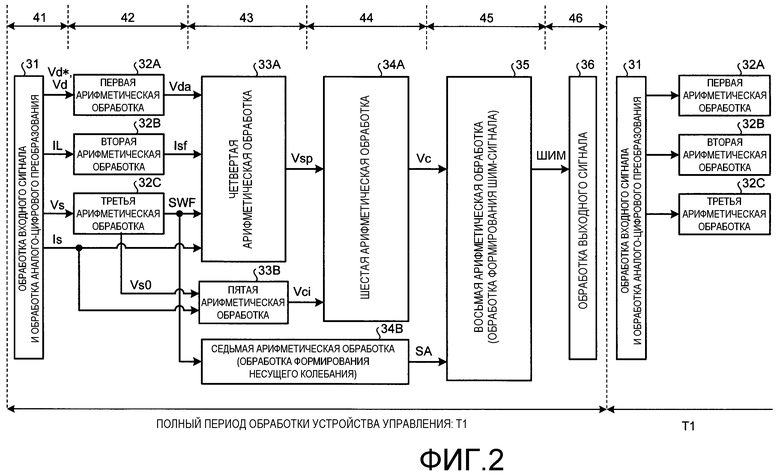

фиг.5 изображает схему контроллера, применяемого в электрическом транспортном средстве, работающем на переменном токе, имеющего конфигурацию, отличную от показанных на фиг.1 и 4.

Описание предпочтительных вариантов осуществления изобретения

Примерные варианты осуществления контроллера электрического транспортного средства, работающего на переменном токе согласно настоящему изобретению, будут пояснены ниже подробнее со ссылкой на сопровождающие чертежи. Настоящее изобретение не ограничено вариантами осуществления.

Фиг.1 является функционально схемой, изображающей, главным образом, конфигурацию устройства управления преобразователем согласно варианту осуществления настоящего изобретения. Система возбуждения электрического транспортного средства, работающего на переменном токе, показана в верхней части, а устройство 20 управления преобразователем, которое составляет систему управления электрического транспортного средства, работающего на переменном токе, показано в нижней части.

На фиг.1 система возбуждения электрического транспортного средства, работающего на переменном токе, включает в себя пантограф 1 (токоприемник), на который подается энергия переменного тока из воздушной линии 18 переменного тока, силовой трансформатор 2, на который энергия переменного тока подается с пантографа 1 в качестве входного сигнала, преобразователь 3 широтно-импульсной модуляции (ШИМ), на который подается напряжение переменного тока силового трансформатора 2 и который преобразует поданное напряжение переменного тока в напряжение постоянного тока, конденсатор 5 фильтра (далее в данном документе FC), который сглаживает напряжение постоянного тока ШИМ-преобразователя 3, и нагрузку 4, которая приводится в действие посредством напряжения постоянного тока, сглаженного посредством FC 5. Нагрузка 4 включает в себя инвертор, который преобразует напряжение постоянного тока, выводимое из ШИМ-преобразователя 3, в напряжение переменного тока, электродвигатель переменного тока, на который подается напряжение переменного тока инвертора, железнодорожный подвижной состав, приводимый в движение посредством электродвигателя переменного тока, и т.п.

С другой стороны, устройство 20 управления преобразователем, которое составляет систему управления электрического транспортного средства, работающего на переменном токе, включает в себя с первого по шестой блоки 21-26 арифметической обработки, блок 14 формирования несущей, блок 15 формирования ШИМ-сигнала и аналого-цифровые (AD) преобразователи 6 (6a-6d).

Первый блок 21 арифметической обработки включает в себя фильтр 7a, сумматор/вычитатель 11a и блок 13 управления стабилизированным напряжением и вычисляет величину Vda корректировки напряжения постоянного тока на основе предварительно определенного опорного напряжения Vd* постоянного тока, внутренне сформированного, и фактического напряжения Vd постоянного тока преобразователя. Детектированное значение, которое является детектированным напряжением между обоими концами FC 5, может использоваться в качестве напряжения Vd постоянного тока преобразователя, например, как показано на фиг.1.

Второй блок 22 арифметической обработки включает в себя операционный усилитель ("G1" на фиг.1 обозначает значение коэффициента усиления. Далее в данном документе значения коэффициентов усиления обозначаются аналогичным образом.) 10a и вычисляет величину прямой связи (далее в данном документе "величину прямой связи вторичного тока") Isf входного тока преобразователя на основе выходного тока IL преобразователя. Детектированное значение, которое получается посредством детектирования тока, протекающего через шину постоянного тока, которая соединяет ШИМ-преобразователь 3 и нагрузку 4, может быть использовано в качестве выходного тока IL преобразователя, например, как показано на фиг.1.

Третий блок 23 арифметической обработки включает в себя фильтр 7b и блок 8 формирования основного синусоидального колебания и вычисляет основное синусоидальное колебание SWF на основе выведенного из фильтра напряжения Vs воздушной линии. Третий блок 23 арифметической обработки также выводит напряжение Vs0 воздушной линии через фильтр 7b в дополнение к основному синусоидальному колебанию SWF.

Четвертый блок 24 арифметической обработки включает в себя сумматоры/вычитатели 11b и 11c, умножитель 12 и операционный усилитель 10b и вычисляет первую величину Vsp корректировки, требуемую для формирования опорного напряжения Vc преобразователя, которое будет пояснено позже, на основе величины Vda корректировки напряжения постоянного тока, величины Isf прямой связи вторичного тока, основного синусоидального колебания SWF и входного тока Is преобразователя.

Пятый блок 25 арифметической обработки включает в себя блок 9 формирования косинусоидального колебания, операционный усилитель 10c и сумматор/вычитатель 11e и вычисляет вторую величину Vci корректировки, требуемую для формирования опорного напряжения Vc преобразователя, на основе выходного сигнала Vs0 фильтра напряжения воздушной линии и входного тока Is преобразователя.

Шестой блок 26 арифметической обработки включает в себя сумматор/вычитатель 11d и вычисляет опорное напряжение Vc преобразователя на основе первой величины Vsp корректировки и второй величины Vci корректировки.

Блок 14 формирования несущей вычисляет несущую SA, требуемую для формирования ШИМ-сигнала, на основе основного синусоидального колебания SWF.

Блок 15 формирования ШИМ-сигнала формирует ШИМ-сигнал для возбуждения переключающего элемента (не показан), включенного в ШИМ-преобразователь 3, на основе опорного напряжения Vc преобразователя и несущей SA и выводит ШИМ-сигнал.

В то время как фиг.1 изображает конфигурацию, включающую в себя второй блок 22 арифметической обработки, который вычисляет величину Isf прямой связи вторичного тока, устройство управления преобразователем может быть реализовано без второго блока 22 арифметической обработки. Однако второй блок 22 арифметической обработки может выполнять одновременные арифметические действия и является одним из блоков обработки, которые являются ключевыми для пояснения работы, согласно настоящему варианту осуществления. Следовательно, последующие пояснения даны исходя из предположения, что второй блок 22 арифметической обработки включен в конструкцию.

Подробная работа устройства 20 управления преобразователем поясняется далее со ссылкой на фиг.1 и 2. Фиг.2 изображает блок-схему последовательности операций процессов, выполняемых устройством 20 управления преобразователем, показанным на фиг.1.

В устройстве 20 управления преобразователем согласно настоящему варианту осуществления арифметическая обработка и т.п. соответствующих составных элементов, выполняемая в устройстве 20 управления преобразователем, делится на шесть периодов обработки с первого периода 41 обработки по шестой период 46 обработки в полном периоде T1 обработки устройства управления преобразователем, как показано на фиг.2. В частности, обработка посредством блока 31 аналого-цифрового преобразования входного сигнала выполняется в первом периоде 41 обработки, а обработка посредством первого блока 32A арифметической обработки, второго блока 32B арифметической обработки и третьего блока 32C арифметической обработки выполняется во втором периоде 42 обработки. Обработка посредством четвертого блока 33A арифметической обработки и пятого блока 33B арифметической обработки выполняется в третьем периоде 43 обработки, а обработка посредством шестого блока 34A арифметической обработки и седьмого блока 34B арифметической обработки (обработка формирования несущего колебания) выполняется в четвертом периоде 44 обработки. Обработка посредством восьмого блока 35 арифметической обработки (обработка формирования ШИМ-сигнала) выполняется в пятом периоде 45 обработки, а обработка посредством блока 36 обработки выходного сигнала выполняется в шестом периоде 46 обработки.

В то время как фиг.2 изображает случай, когда время начала соответствующих обработок посредством пятого блока 33B арифметической обработки и седьмого блока 34B арифметической обработки совпадают с временем начала обработки посредством четвертого блока 33A арифметической обработки, настоящий вариант осуществления не ограничивается этим случаем. Например, пятый блок 33B арифметической обработки может начинать обработку до четвертого блока 33A арифметической обработки или может устанавливать момент начала обработки в произвольный момент времени в течение третьего периода 43 обработки, так что полное время обработки почти совпадает с полным временем обработки посредством четвертого блока 33A арифметической обработки. Седьмой блок 34B арифметической обработки может устанавливать момент начала обработки в произвольный момент времени в течение периодов обработки - третьего периода 43 обработки и четвертого периода 44 обработки, так что полное время обработки почти совпадает с полным временем обработки посредством шестого блока 34A арифметической обработки.

Соответствующие блоки обработки поясняются далее.

Блок 31 обработки входного сигнала аналого-цифрового преобразования включает в себя аналого-цифровое преобразование, выполняемое в аналого-цифровых преобразователях 6a-6d, обработку установки коэффициентов усиления, выполняемую в операционных усилителях 10a-10c, обработку ввода постоянных фильтра, выполняемую в фильтрах 7a и 7b, и т.п.

Первый блок 32A арифметической обработки соответствует обработке, выполняемой первым блоком 21 арифметической обработки. Аналогичным образом второй блок 32B арифметической обработки соответствует обработке, выполняемой вторым блоком 22 арифметической обработки, третий блок 32C арифметической обработки соответствует обработке, выполняемой третьим блоком 23 арифметической обработки, четвертый блок 33A арифметической обработки соответствует обработке, выполняемой четвертым блоком 24 арифметической обработки, пятый блок 33B арифметической обработки соответствует обработке, выполняемой пятым блоком 25 арифметической обработки, а шестой блок 34A арифметической обработки соответствует обработке, выполняемой шестым блоком 26 арифметической обработки. Седьмой блок 34B арифметической обработки (обработка формирования несущего колебания) соответствует обработке, выполняемой блоком 14 формирования несущей, а восьмой блок 35 арифметической обработки (обработка формирования ШИМ-сигнала) соответствует обработке, выполняемой блоком 15 формирования ШИМ-сигнала. Блок 36 обработки выходного сигнала соответствует интерфейсной обработке, выполняемой, когда ШИМ-сигнал выводится в ШИМ-преобразователь 3, и т.п.

Работа устройства 20 управления преобразователем согласно настоящему варианту осуществления поясняется далее относительно составных элементов, показанных на фиг.1, и блоков обработки, показанных на фиг.2.

Работа первого блока 21 арифметической обработки

Выходное напряжение Vd преобразователя, подаваемое в устройство 20 управления преобразователем, преобразуется посредством аналого-цифрового преобразователя 6a в цифровой сигнал (блок 31 обработки входного сигнала и обработки аналого-цифрового преобразования). Полученный цифровой сигнал подается на фильтр 7a первого блока 21 арифметической обработки. Сумматор/вычитатель 11a затем вычисляет разницу между опорным напряжением Vd* постоянного тока и выходным сигналом Vd0 фильтра 7a, а блок 13 управления постоянным напряжением вычисляет величину Vda корректировки напряжения постоянного тока (первый блок 32A арифметической обработки).

Работа второго блока 22 арифметической обработки

Выходной ток IL преобразователя, подаваемый в устройство 20 управления преобразователем, преобразуется посредством аналого-цифрового преобразователя 6b в цифровой сигнал (блок 31 обработки входного сигнала и обработки аналого-цифрового преобразования). Полученный цифровой сигнал умножается на коэффициент G1 усиления в операционном усилителе 10a второго блока 22 арифметической обработки, чтобы вычислять величину Isf вторичного тока прямой связи (второй блок 32B арифметической обработки).

Работа третьего блока 23 арифметической обработки

Напряжение Vs воздушной линии, поданное на устройство 20 управления преобразователем, преобразуется посредством аналого-цифрового преобразователя 6d в цифровой сигнал (блок 31 обработки входного сигнала и обработки аналого-цифрового преобразования). Полученный цифровой сигнал подается в фильтр 7b третьего блока 23 арифметической обработки, чтобы формировать выходной сигнал Vs0 фильтра напряжения воздушной линии, и выходной сигнал Vs0 фильтра напряжения воздушной линии подается в блок 8 формирования основного синусоидального колебания, чтобы вычислять основное синусоидальное колебание SWF (третий блок 32C арифметической обработки).

Операции с первого блока 21 арифметической обработки по третий блок 23 арифметической обработки могут выполняться одновременно параллельно и, следовательно, могут быть исполнены как арифметические обработки, использующие различные схемы в FPGA.

Работа четвертого блока 24 арифметической обработки

Выходной ток Is преобразователя, подаваемый в устройство 20 управления преобразователем, преобразуется посредством аналого-цифрового преобразователя 6c в цифровой сигнал (блок 31 обработки входного сигнала и обработки аналого-цифрового преобразования). Величина Vda корректировки напряжения постоянного тока, величина Isf вторичного тока прямой связи и основное синусоидальное колебание SWF, которые являются выходными сигналами с первого блока 21 арифметической обработки по третий блок 23 арифметической обработки, вводятся в четвертый блок 24 арифметической обработки. Величина Vda корректировки напряжения постоянного тока и величина Isf вторичного тока прямой связи вводятся в сумматор/вычитатель 11b четвертого блока 24 арифметической обработки. Выходной сигнал Isp сложения из него умножается на основное синусоидальное колебание SWF в умножителе 12, чтобы вычислять опорное значение Is* входного тока преобразователя. Отклонение ∆Is между опорным значением Is* входного тока преобразователя и входным током Is преобразователя, преобразованное в цифровой сигнал посредством аналого-цифрового преобразователя 6c, вычисляется посредством сумматора/вычитателя 11c. Операционный усилитель 10b вычисляет первую величину Vsp корректировки посредством умножения отклонения ∆Is на коэффициент G2 усиления (это соответствует четвертому блоку 33A арифметической обработки).

Работа пятого блока 25 арифметической обработки

Входной ток Is преобразователя, преобразованный в цифровой сигнал посредством аналого-цифрового преобразователя 6c, также подается в блок 9 формирования косинусоидального колебания пятого блока 25 арифметической обработки (блок 31 обработки входного сигнала и обработки аналого-цифрового преобразования). В пятом блоке 25 арифметической обработки блок 9 формирования косинусоидального колебания формирует косинусоидальное колебание CWF на основе входного тока Is преобразователя, и операционный усилитель 10c вычисляет величину VL корректировки посредством умножения косинусоидального колебания CWF на коэффициент G3 усиления. Вычисленная величина VL корректировки и выходной сигнал Vs0 фильтра напряжения воздушной линии, введенные из третьего блока 23 арифметической обработки, вводятся в сумматор/вычитатель 11e. Результат их вычитания вычисляется как вторая величина Vci корректировки (это соответствует пятому блоку 33B арифметической обработки).

Операции четвертого блока 24 арифметической обработки и пятого блока 25 арифметической обработки также могут выполняться одновременно параллельно и, следовательно, могут быть выполнены как арифметические обработки, использующие различные схемы в FPGA.

Работа шестого блока 26 арифметической обработки

Первая величина Vsp корректировки и вторая величина Vci корректировки, которые являются выходными величинами из четвертого и пятого блоков 24 и 25 арифметической обработки соответственно, вводятся в сумматор/вычитатель 11d шестого блока 26 арифметической обработки. Результат их вычитания вычисляется как опорное напряжение Vc преобразователя (шестой блок 34A арифметической обработки).

Работа блока 14 формирования несущей

Блок 14 формирования несущей вычисляет несущую SA, требуемую для формирования ШИМ-сигнала, на основе основного синусоидального колебания SWF, введенного из третьего блока 23 арифметической обработки (седьмой блок 34B арифметической обработки). Арифметическая обработка блока 14 формирования несущей может выполняться параллельно с арифметической обработкой четвертого блока 24 арифметической обработки и пятого блока 25 арифметической обработки или параллельно с арифметической обработкой шестого блока 26 арифметической обработки.

Работа блока 15 формирования ШИМ-сигнала

Блок 15 формирования ШИМ-сигнала формирует управляющий ШИМ-сигнал для возбуждения ШИМ-преобразователя 3 на основе опорного напряжения Vc преобразователя, вычисленного шестым блоком 26 арифметической обработки, и несущей SA, вычисленной блоком 14 формирования несущей (восьмой блок 35 арифметической обработки). Сформированный управляющий ШИМ-сигнал выводится в ШИМ-преобразователь 3 (блок 36 обработки выходного сигнала).

Как описано выше, устройство управления преобразователем согласно настоящему варианту осуществления выполняет соответствующую арифметическую обработку в течение всего периода T1 обработки устройства управления преобразователем и выполняет соответствующую арифметическую обработку посредством FPGA так, что арифметическая обработка завершается в течение периода T1 обработки.

Фиг.3 изображает последовательность операций обработки, выполняемую блоком обработки входного сигнала и обработки аналого-цифрового преобразования, показанным на фиг.2. Как показано на фиг.3, блок 31 обработки входного сигнала и обработки аналого-цифрового преобразования выполняет обработку, такую как обработка 51 аналого-цифрового преобразования для напряжения Vd постоянного тока преобразователя, обработка 52 аналого-цифрового преобразования для выходного тока IL преобразователя, обработка 53 аналого-цифрового преобразования для напряжения Vs воздушной линии, обработка 54 аналого-цифрового преобразования для входного тока Is преобразователя, обработка 55 входного сигнала для опорного напряжения Vd* постоянного тока, обработка 56 ввода коэффициентов G1, G2 и G3 усиления и обработка 57 ввода постоянных фильтра.

Когда арифметическая обработка устройства управления преобразователем реализована посредством FPGA, постоянные, которые должны использоваться в соответствующий арифметической обработке, могут быть объединены в FPGA. Однако изменение FPGA-логики требует специального блока по сравнению с изменением программной логики и усложняет операции. Соответственно, например, когда постоянные устройства управления должны быть изменены, например, на этапе регулировки, операция изменения не может быть выполнена легко и для регулировки требуется длительное время.

Между тем, устройство управления преобразователем согласно настоящему варианту осуществления имеет конфигурацию, в которой установка или изменение коэффициентов G1-G3 усиления и постоянных фильтра, которые должны использоваться для управляющей арифметической обработки в блоке 31 обработки входного сигнала и обработки аналого-цифрового преобразования, выполняются посредством считывания программного обеспечения, как показано на фиг.3, и, следовательно, для регулировки не требуется длительное время. Т.е. в устройстве управления преобразователем согласно настоящему варианту осуществления изменение коэффициентов усиления и постоянных фильтра реализуется посредством изменения программного обеспечения. Следовательно, каких-либо специальных устройств или процедур, как при изменении встроенных в FPGA постоянных, не требуется, что облегчает регулировку и обеспечивает сокращение времени.

В то время как считывание коэффициентов усиления и постоянных фильтра выполняется в начале каждого периода обработки в процессе, показанном на фиг.2 и 3, настоящий вариант осуществления не ограничивается этим. Например, процесс считывания может выполняться в предварительно определенный момент, непосредственно после включения электропитания. Также в таком случае могут быть получены результаты, аналогичные результатам настоящего варианта осуществления.

Как описано выше, согласно контроллеру для электрического транспортного средства, работающего на переменном токе настоящего варианта осуществления, когда арифметика устройства управления преобразователем реализована посредством FPGA, некоторые части арифметической обработки, которые могут выполняться одновременно среди многих частей арифметической обработки, требуемой для управления преобразователем, объединяются и выполняются параллельно. Следовательно, во время выполнения арифметических операций с числами с плавающей запятой с большим числом битов может быть достигнута высокоскоростная обработка.

Согласно контроллеру электрического транспортного средства, работающего на переменном токе настоящего варианта осуществления, некоторые части арифметической обработки, требуемой для управления преобразователем, могут выполняться при обработке посредством FPGA. Следовательно, возможно исключить непреднамеренные задержки в обработке или разницы во времени между модулями управления, имеющими различные скорости обработки. В результате обратные гармоники, создаваемые работой преобразователя, могут быть уменьшены и влияние на операции других сигнальных блоков могут быть уменьшены.

Согласно контроллеру для электрического транспортного средства, работающего на переменном токе настоящего варианта осуществления, изменение коэффициентов усиления и констант фильтра, используемых в управляющей арифметике, может быть выполнено посредством изменения программного обеспечения. Следовательно, каких-либо специальных устройств или процедур, как при изменении встроенных в FPGA постоянных, не требуется, что облегчает регулировку и уменьшает время регулировки.

Фиг.4 изображает конфигурацию контроллера, применяемого в электрическом транспортном средстве, работающем на переменном токе, имеющего конфигурацию, отличную от показанной на фиг.1. В контроллере, показанном на фиг.1, напряжение на первичной обмотке силового трансформатора 2 отслеживается как напряжение Vs воздушной линии. Между тем, в контроллере, показанном на фиг.4, отслеживается напряжение на третьей обмотке силового трансформатора 2. Даже с конфигурацией, которая отслеживает напряжение на третьей обмотке силового трансформатора 2, когда устройство 20 управления преобразователем имеет ту же или эквивалентную конфигурацию, что и показанная на фиг.1, могут быть получены преимущества, аналогичные преимуществам контроллера, описанного выше.

Фиг.5 изображает конфигурацию контроллера, применяемого в электрическом транспортном средстве, работающем на переменном токе, имеющего конфигурацию, отличную от показанных на фиг.1 и 4. В то время как электрическое транспортное средство, работающее на переменном токе, показанное на фиг.1, имеет конфигурацию, включающую в себя ШИМ-преобразователь, электрическое транспортное средство, работающее на переменном токе, показанное на фиг.5, имеет конфигурацию, включающую в себя два ШИМ-преобразователя, подключенных параллельно к нагрузке. В электрическом транспортном средстве, работающем на переменном токе с такой конфигурацией, первый блок 21 арифметической обработки и второй блок 22 арифметической обработки используются совместно, а с третьего блока 23 арифметической обработки по шестой блок 26 арифметической обработки, блок 14 формирования несущей и блок 15 формирования ШИМ-сигнала предусмотрены соответственно, как показано на фиг.5. Таким образом, может быть реализована обработка, разделенная на блоки арифметической обработки, как на фиг.2. Следовательно, даже с конфигурацией контроллера, показанного на фиг.5, могут быть получены преимущества, аналогичные преимуществам контроллера, который описан выше.

Дополнительно в контроллере согласно настоящему варианту осуществления блоки арифметической обработки, отличные от блока 31 обработки входного сигнала и обработки аналого-цифрового преобразования и блока 36 обработки выходного сигнала, разделены на блоки арифметической обработки с первого по восьмой. Следовательно, даже когда характеристики и конфигурация электрического транспортного средства, работающего на переменном токе, или характеристики и конфигурация контроллера изменяются, как показано на фиг.1, 4 и 5, требуется изменение только ассоциированных арифметических блоков, соответствующих изменению в характеристиках или т.п. Соответственно, изменение или корректировка моделей может быть упрощена, и может быть достигнуто сокращение времени. Дополнительно также в случае отказа, такого как авария, неисправная часть легко может быть отделена и, следовательно, могут быть улучшены простота восстановления и надежность контроллера.

Когда арифметическая обработка контроллера делится на блоки арифметической обработки с первого по восьмой аналогично настоящему варианту осуществления, соответствующие средства уменьшаются в размерах, а гибкость в размещении на FPGA увеличивается. Соответственно, возможно конфигурировать множество относительно меньших FPGA, при этом сохраняя высокоскоростную арифметическую обработку, что уменьшает общий размер контроллера.

Промышленная применимость

Как описано выше, контроллер для электрического транспортного средства, работающего на переменном токе согласно настоящему изобретению, полезен, поскольку может обрабатывать управляющую арифметику устройства преобразователя в FPGA.

Пояснения к буквенным или числовым ссылкам

1 пантограф

2 силовой трансформатор

3 ШИМ-преобразователь

4 нагрузка

6a-6d аналого-цифровой преобразователь

7a, 7b фильтр

8 блок формирования основного синусоидального колебания

9 блок формирования косинусоидального колебания

10a-10c операционный усилитель

11a-11e сумматор/вычитатель

12 умножитель

13 блок управления стабилизированным напряжением

14 блок формирования несущей

15 блок формирования ШИМ-сигнала

18 воздушная линия

20 блок управления преобразователем

21 первый блок арифметической обработки

22 второй блок арифметической обработки

23 третий блок арифметической обработки

24 четвертый блок арифметической обработки

25 пятый блок арифметической обработки

26 шестой блок арифметической обработки

31 блок обработки входного сигнала и обработки аналого-цифрового преобразования

32A первый блок арифметической обработки

32B второй блок арифметической обработки

32C третий блок арифметической обработки

33A четвертый блок арифметической обработки

33B пятый блок арифметической обработки

34A шестой блок арифметической обработки

34B седьмой блок арифметической обработки (обработка формирования несущей волны)

35 восьмой блок арифметической обработки (обработка формирования ШИМ-сигнала)

36 блок обработки выходного сигнала

41 первый период обработки

42 второй период обработки

43 третий период обработки

44 четвертый период обработки

45 пятый период обработки

46 шестой период обработки

51 обработка аналого-цифрового преобразования для напряжения Vd постоянного тока преобразователя

52 обработка аналого-цифрового преобразования для выходного тока IL преобразователя

53 обработка аналого-цифрового преобразования для напряжения Vs воздушной линии

54 обработка аналого-цифрового преобразования для входного тока Is преобразователя

55 обработка входного сигнала для опорного напряжения постоянного тока Vd*

56 обработка ввода коэффициентов усиления G1, G2 и G3

57 обработка ввода для постоянных фильтра

| название | год | авторы | номер документа |

|---|---|---|---|

| Контроллер магнитного поля | 2023 |

|

RU2799103C1 |

| УСТРОЙСТВО ОБРАБОТКИ | 2006 |

|

RU2431232C2 |

| СПОСОБ И СИСТЕМА КАЛИБРОВКИ | 2020 |

|

RU2814611C2 |

| СПОСОБ УПРАВЛЕНИЯ ЧЕТЫРЕХКВАДРАНТНЫМ ПРЕОБРАЗОВАТЕЛЕМ С ВЫЧИСЛЕНИЕМ ФАЗ КОММУТАЦИИ И МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2006 |

|

RU2327276C1 |

| ЧАСТОТНО-РЕГУЛИРУЕМЫЙ ЭЛЕКТРОПРИВОД ПЕРЕМЕННОГО ТОКА | 1998 |

|

RU2136103C1 |

| СВАРОЧНЫЙ ИСТОЧНИК ПИТАНИЯ С ЦИФРОВЫМ УПРАВЛЕНИЕМ РАБОЧИМ ЦИКЛОМ | 2010 |

|

RU2540952C2 |

| СИСТЕМЫ И СПОСОБЫ ДЛЯ ОПРЕДЕЛЕНИЯ ИНДУКТИВНОСТИ СВАРОЧНОГО КАБЕЛЯ | 2010 |

|

RU2561542C2 |

| ТРЕХФАЗНЫЙ ИСТОЧНИК БЕСПЕРЕБОЙНОГО ПИТАНИЯ БОЛЬШОЙ МОЩНОСТИ | 2010 |

|

RU2529017C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ УВЕЛИЧЕНИЯ ДИАПАЗОНА РЕГУЛИРОВАНИЯ ОСВЕЩЕННОСТИ ТВЕРДОТЕЛЬНЫХ ОСВЕТИТЕЛЬНЫХ ПРИБОРОВ | 2011 |

|

RU2556019C2 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ МОЩНОСТИ | 2013 |

|

RU2594359C2 |

Использование: в области электротехники. Технический результат заключается в повышении быстродействия. Контроллер включает в себя устройство (20) управления преобразователем, управляющее работой ШИМ-преобразователя (3), который преобразует напряжение переменного тока, поданное из воздушной линии переменного тока через трансформатор, в напряжение постоянного тока, арифметическая обработка, выполняемая в устройстве (20) управления преобразователем, разделена, по меньшей мере, на блоки арифметической обработки с первого по шестой, причем блоки арифметической обработки с первого по шестой сконфигурированы посредством FPGA и блоки арифметической обработки с первого по третий и четвертый и пятый блоки арифметической обработки сконфигурированы, чтобы обеспечивать одновременную параллельную обработку соответственно. 3 н.п. и 8 з.п. ф-лы, 5 ил.

1. Контроллер (20) для электрического транспортного средства, работающего на переменном токе, который применяется в электрическом транспортном средстве, работающем на переменном токе, имеющий преобразователь (3) широтно-импульсной модуляции (ШИМ), который преобразует напряжение переменного тока, подаваемое из воздушной линии (18) через трансформатор (2), в напряжение постоянного тока, и который содержит устройство управления преобразователем, управляющее работой ШИМ-преобразователя (3), при этом устройство управления преобразователем разделено на множество блоков арифметической обработки, сконфигурированных посредством программируемой вентильной матрицы (FPGA), и блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя: первый блок (32А) арифметической обработки, который вычисляет величину корректировки напряжения постоянного тока на основе предварительно определенного опорного напряжения постоянного тока и напряжения постоянного тока ШИМ-преобразователя, чтобы выводить величину корректировки напряжения постоянного тока; третий блок (32С) арифметической обработки, который выполняет обработку параллельно с первым блоком арифметической обработки и вычисляет основное синусоидальное колебание на основе напряжения воздушной линии через фильтр, чтобы выводить основное синусоидальное колебание; четвертый блок (33А) арифметической обработки, который вычисляет первую величину корректировки, ассоциированную с формированием опорного напряжения преобразователя, на основе величины корректировки напряжения постоянного тока, основного синусоидального колебания и входного тока ШИМ-преобразователя для того, чтобы выводить первую величину корректировки; пятый блок (33 В) арифметической обработки, который выполняет обработку параллельно с четвертым блоком арифметической обработки и вычисляет вторую величину корректировки, ассоциированную с формированием опорного напряжения преобразователя, на основе вывода фильтра напряжения воздушной линии и входного тока ШИМ-преобразователя для того, чтобы выводить вторую величину корректировки; и шестой блок (34А) обработки, который вычисляет опорное напряжение преобразователя на основе первой и второй величин корректировки, чтобы выводить опорное напряжение преобразователя.

2. Контроллер (20) для электрического транспортного средства, работающего на переменном токе, который применяется в электрическом транспортном средстве, работающем на переменном токе, имеющий множество ШИМ-преобразователей (3а, 3b), которые преобразуют напряжение переменного тока, подаваемое из воздушной линии через трансформатор, в напряжение постоянного тока, и который содержит устройство управления преобразователем, управляющее работой ШИМ-преобразователей (3а, 3b), подключеных параллельно к нагрузке, при этом устройство управления преобразователем разделено на множество блоков арифметической обработки, сконфигурированных посредством FPGA, и блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя: первый блок (32А) арифметической обработки, который вычисляет величину корректировки напряжения постоянного тока на основе предварительно определенного опорного напряжения постоянного тока и напряжения постоянного тока ШИМ-преобразователя, чтобы выводить величину корректировки напряжения постоянного тока; третий блок (32С) арифметической обработки, который выполняет обработку параллельно с первым блоком арифметической обработки и вычисляет основное синусоидальное колебание на основе напряжения воздушной линии через фильтр, чтобы выводить основное синусоидальное колебание; четвертый блок (33А) арифметической обработки, который вычисляет первую величину корректировки, ассоциированную с формированием опорного напряжения преобразователя, на основе величины корректировки напряжения постоянного тока, основного синусоидального колебания и входного тока ШИМ-преобразователей для того, чтобы выводить первую величину корректировки; пятый блок (33 В) арифметической обработки, который выполняет обработку параллельно с четвертым блоком арифметической обработки и вычисляет вторую величину корректировки, ассоциированную с формированием опорного напряжения преобразователя, на основе вывода фильтра напряжения воздушной линии и входного тока ШИМ-преобразователей для того, чтобы выводить вторую величину корректировки; и шестой блок (34А) обработки, который вычисляет опорное напряжение преобразователя на основе первой и второй величин корректировки, чтобы выводить опорное напряжение преобразователя.

3. Контроллер (20) по п.1 или 2, в котором блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя: второй блок (32 В) арифметической обработки, который выполняет обработку параллельно с первым и третьим блоками (32А, 32С) арифметической обработки и вычисляет величину прямой связи для входного тока ШИМ-преобразователя на основе выходного тока ШИМ-преобразователей для того, чтобы выводить величину прямой связи.

4. Контроллер (20) по п.1 или 2, в котором блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя: седьмой блок (34 В) арифметической обработки, который выполняет обработку параллельно с шестым блоком (34А) арифметической обработки и вычисляет несущую, ассоциированную с формированием ШИМ-сигнала для возбуждения ШИМ-преобразователей, на основе основного синусоидального колебания для того, чтобы выводить несущую; и восьмой блок (35) арифметической обработки, который вычисляет ШИМ-сигнал на основе опорного напряжения преобразователя и несущей, чтобы выводить ШИМ-сигнал.

5. Контроллер (20) по п.2, в котором первый блок арифметической обработки разделен посредством ШИМ-преобразователей, и блоки (32С, 33А, 33В, 34А) арифметической обработки с третьего по шестой предусмотрены для каждого из ШИМ-преобразователей.

6. Контроллер (20) по п.1 или 2, в котором блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя блок (31) обработки входного сигнала и аналого-цифрового преобразования, который считывает постоянные, которые должны использоваться в арифметических операциях посредством блоков арифметической обработки, сконфигурированных посредством FPGA, в предварительно определенные моменты в пределах каждого периода арифметической обработки.

7. Контроллер (20) по п.3, в котором блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя блок (31) обработки входного сигнала и аналого-цифрового преобразования, который считывает постоянные, которые должны использоваться в арифметических операциях посредством блоков арифметической обработки, сконфигурированных посредством FPGA, в предварительно определенные моменты в пределах каждого периода арифметической обработки.

8. Контроллер (20) по п.4, в котором блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя блок (31) обработки входного сигнала и аналого-цифрового преобразования, который считывает постоянные, которые должны использоваться в арифметических операциях посредством блоков арифметической обработки, сконфигурированных посредством FPGA, в предварительно определенные моменты в пределах каждого периода арифметической обработки.

9. Контроллер (20) по п.5, в котором блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя блок (31) обработки входного сигнала и аналого-цифрового преобразования, который считывает постоянные, которые должны использоваться в арифметических операциях посредством блоков арифметической обработки, сконфигурированных посредством FPGA, в предварительно определенные моменты в пределах каждого периода арифметической обработки.

10. Контроллер (20) по п.6, в котором блок (31) обработки входного сигнала и аналого-цифрового преобразования выполняет установку или изменение постоянных, которые должны использоваться в арифметических операциях посредством блоков арифметической обработки, посредством считывания из программного обеспечения.

11. Контроллер (20) для электрического транспортного средства, работающего на переменном токе, который применяется в электрическом транспортном средстве, работающем на переменном токе, имеющий ШИМ-преобразователь (3), который преобразует напряжение переменного тока, подаваемое из воздушной линии (18) через трансформатор (2), в напряжение постоянного тока, и который содержит устройство управления преобразователем, управляющее работой ШИМ-преобразователя (3), при этом арифметическая обработка, выполняемая в устройстве управления преобразователем, разделена на множество блоков арифметической обработки, сконфигурированных посредством FPGA, причем блоки арифметической обработки, сконфигурированные посредством FPGA, включают в себя: первый блок (32А) арифметической обработки, который вычисляет величину корректировки напряжения постоянного тока на основе предварительно определенного опорного напряжения постоянного тока и напряжения постоянного тока ШИМ-преобразователя, чтобы выводить величину корректировки напряжения постоянного тока; второй блок (32В) арифметической обработки, который вычисляет величину прямой связи для входного тока ШИМ-преобразователя на основе выходного тока ШИМ-преобразователя для того, чтобы выводить величину прямой связи; третий блок (32С) арифметической обработки, который вычисляет основное синусоидальное колебание на основе напряжения воздушной линии, прошедшего через фильтр для того, чтобы выводить основное синусоидальное колебание; четвертый блок (33А) арифметической обработки, который вычисляет первую величину корректировки, ассоциированную с формированием опорного напряжения преобразователя, на основе величины корректировки напряжения постоянного тока, основного синусоидального колебания и входного тока ШИМ-контроллера для того, чтобы выводить первую величину корректировки; пятый блок (33В) арифметической обработки, который вычисляет вторую величину корректировки, ассоциированную с формированием опорного напряжения преобразователя, на основе вывода фильтра напряжения воздушной линии и входного тока ШИМ-преобразователя для того, чтобы выводить вторую величину корректировки; шестой блок (34А) арифметической обработки, который вычисляет опорное напряжение преобразователя на основе первой и второй величин корректировки, чтобы выводить опорное напряжение преобразователя; седьмой блок (34В) арифметической обработки, который вычисляет несущую, ассоциированную с формированием ШИМ-сигнала для возбуждения ШИМ-преобразователя, на основе основного синусоидального колебания, чтобы выводить несущую; и восьмой блок (35) арифметической обработки, который вычисляет ШИМ-сигнал на основе опорного напряжения преобразователя и несущей, чтобы выводить ШИМ-сигнал, при этом первый, второй и третий блоки (32А, 32 В, 32С) арифметической обработки предназначены для выполнения арифметической обработки в ходе первого периода обработки, четвертый и пятый блоки (33А, 33В) арифметической обработки предназначены для выполнения арифметической обработки в ходе второго периода обработки, следующего после первого периода обработки, шестой блок (34А) арифметической обработки предназначен для выполнения арифметической обработки в ходе третьего периода обработки, следующего после второго периода обработки, седьмой блок (34В) арифметической обработки предназначен для выполнения арифметической обработки в ходе второго и третьего периодов обработки, и восьмой блок (35) арифметической обработки предназначен для выполнения арифметической обработки в ходе четвертого периода обработки, следующего после третьего периода обработки.

| JP 2007336632 А, 27.12.2007 | |||

| JP 2008131833 А, 05.06.2008 | |||

| СПОСОБ ШИРОТНО-ИМПУЛЬСНОГО РЕГУЛИРОВАНИЯ НАПРЯЖЕНИЯ НА ВЫХОДЕ СЕТЕВОГО ПРЕОБРАЗОВАТЕЛЯ | 1996 |

|

RU2110136C1 |

| JP 11164565 А, 18.06.1999. | |||

Авторы

Даты

2012-11-20—Публикация

2008-07-31—Подача