Изобретение относится к наноэлектронике и может быть использовано при создании энергонезависимого статического оперативного запоминающего устройства с произвольной выборкой информации (ЭН.С. ОЗУ ПВ) с повышенной интеграцией, технологичностью и отсутствием энергопотребления в режиме хранения информации.

Известна электрическая схема ячейки памяти динамического оперативного запоминающего устройства с произвольной выборкой информации (ДОЗУ ПВ) [US 3387286, опублик. 04.06.1968], содержащая n-МОП (Металл-Оксид-Полупроводник) транзистор, общую шину, шину питания, адресную шину и две разрядные шины. Конструкция ячейки представляет собой n-МОП и конденсатор расположенные на лицевой поверхности кремниевой пластины.

Недостатком Ячейки ДОЗУ являются невысокое быстродействие и уменьшение надежности работы при уменьшении ее топологических размеров.

Известна электрическая схема 6-ти транзисторной ячейки памяти для К-МОП С.ОЗУ ПВ [Патент РФ №2216795 от 20.11.2003], содержащая два переключающих n-МОП и два нагрузочных р-МОП транзистора образующих триггер и два n-МОП управляющих транзистора обеспечивающих режимы записи - считывания и хранении информации, а также общую шину, шину питания, адресную шину и две разрядные шины.

Конструкция ячейки представляет собой четыре n-МОП и два р-МОП транзистора расположенные на лицевой поверхности кремниевой пластины.

Недостатком являются сложная технология изготовления и относительно большие размеры, что не позволяет достичь максимальной интеграции ОЗУ ПВ.

Наиболее близкой по технической сущности является ячейка памяти n-МОП ОЗУ ПВ [US 4901284 опублик. 13.02.1990], содержащая два переключающих n-МОП транзистора и два нагрузочных резистора, образующих триггер при этом их истоки подсоединены к общей шине, стоки через нагрузочные резисторы к шине питания и соответственно к затворам друг друга, два n-МОП управляющих транзистора, затворы которых подсоединены к адресной шине, истоки к соответствующим стокам переключающих, а стоки к соответствующим разрядным шинам.

Конструкция ячейки, представляющая собой четыре n-МОП транзистора, расположенных на лицевой поверхности кремниевой пластины, на поверхности транзисторов расположен диэлектрик, на котором расположены нагрузочные резисторы [US 4901284 опублик. 13.02.1990].

Недостатком являются значительное потребление энергии в режиме хранения, считывания и записи информации относительно большая площадь, занимаемая высокоомными поликремниевыми резисторами, плохая воспроизводимость резисторов при уменьшении их топологических размеров, что также ограничивает возможность повышения интеграции ОЗУ СБИС.

Общим недостатком перечисленных ячеек является потеря информации при отключении питания.

Целью изобретения является создание энергонезависимого ОЗУ ПВ с повышенной интеграцией и технологичностью.

Технический результат, достигаемый в изобретении заключается в уменьшении энергопотребления и повышении степени интеграции.

Указанный технический результат достигается следующим образом. В электрической схеме стоки переключающих n(р)-МОП транзисторов подсоединены к анодам соответствующих (катодам) нагрузочных фотодиодов, катоды (аноды) которых подсоединены к шине питания, при этом фотодиоды являются источниками фото-э.д.с., положительные потенциалы которых находятся на анодах, а отрицательные на катодах фотодиодов. Катоды (аноды) фотодиодов подсоединены к общей шине.

А также цель достигается тем что, в конструкции ячейки на диэлектрике расположены (поликремниевые / аморфные) фотодиоды, на поверхности которых расположен сцинтиллятор, на поверхности сцинтиллятора - источник радиоактивного излучения.

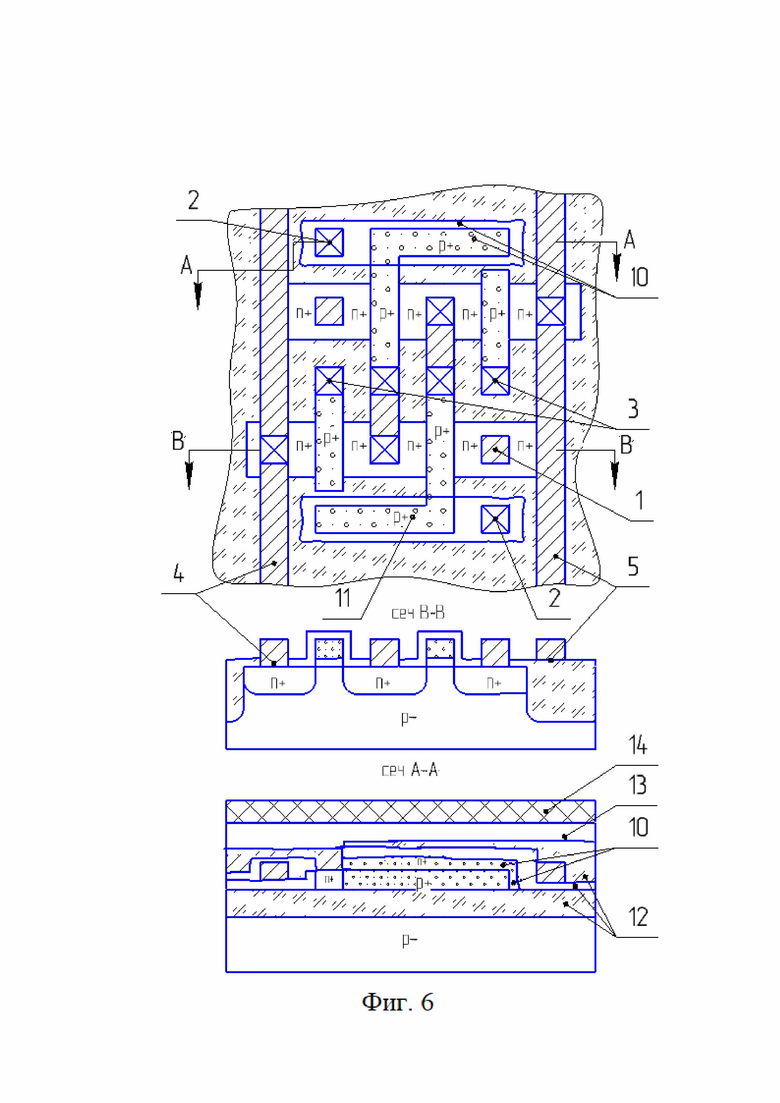

Изобретение поясняется чертежом, где на фиг. 1. показана электрическая схема ячейки памяти прототипа, на фиг. 2. - электрическая схема ячейки памяти изобретения по П1, на фиг. 3. - электрическая схема ячейки памяти изобретения по П2, на фиг. 4. - электрическая схема ячейки памяти изобретения по П3, на фиг. 5. - конструкция ячейки памяти n-МОП ОЗУ ПВ с поликремниевыми нагрузочными транзисторами, на фиг. 6. - конструкция ячейки памяти статического оперативного запоминающего устройства с радиоактивным источником питания.

На Фиг. 1 показана электрическая схема ячейки памяти прототипа, которая содержит общую шину 1 , шину питания 2 , адресную шину 3, первую 4 и вторую 5 разрядные шины, первый 6 и второй 7 управляющие n(р)-МОП транзисторы, первый 8 и второй 9 переключающие n(р)-МОП транзисторы, истоки которых подсоединены к общей шине 1 ,сток первого переключающего МОП транзистора 8 подсоединен к затвору второго переключающего МОП транзистора 9, а сток второго переключающего МОП транзистора 9 к затвору первого переключающего МОП транзистора 8, затворы управляющих МОП транзисторов 6,7 подсоединены к адресной шине 3, истоки первого и второго управляющих транзисторов 6,7 подсоединены соответственно к стокам первого 8 и второго 9 переключающих МОП транзисторов, а их стоки к соответственно к первой 4 и второй 5 разрядным шинам, сток первого переключающего МОП транзистора 8 подсоединен через первый нагрузочный резистор 10 к шине питания 2, а сток второго переключающего МОП транзистора 9 подсоединен через второй нагрузочный резистор 11 к шине питания 2.

На Фиг. 2 показана электрическая схема ячейки памяти изобретения по П1, которая содержит общую шину 1 , шину питания 2 , адресную шину 3 ,первую 4 и вторую 5 разрядные шины, первый 6 и второй 7 управляющие n(р)-МОП транзисторы, первый 8 и второй 9 переключающие n(р)-МОП транзисторы, истоки которых подсоединены к общей шине 1, сток первого переключающего МОП транзистора 8 подсоединен к затвору второго переключающего МОП транзистора 9, а сток второго переключающего МОП транзистора 9 к затвору первого переключающего МОП транзистора 8, затворы управляющих МОП транзисторов 6, 7 подсоединены к адресной шине 3, истоки первого и второго управляющих транзисторов 6,7 подсоединены соответственно к стокам первого 8 и второго 9 переключающих МОП транзисторов, а их стоки к соответственно к первой 4 и второй 5 разрядным шинам, сток первого переключающего МОП транзистора 8 подсоединен к аноду (катоду) первого нагрузочного фотодиода 10, а сток второго переключающего МОП транзистора 9 подсоединен к аноду (катоду) второго нагрузочного фотодиода 11, катод первого фотодиода 10 соединен с отрицательным полюсом первого источника э.д.с. 12, а его анод соединен с положительным полюсом первого источника э.д.с. 12, катод второго фотодиода 11 соединен с отрицательным полюсом второго источника э.д.с. 13 , а его анод соединен с положительным полюсом второго источника э.д.с. 13.

На Фиг. 3, показана электрическая схема ячейки памяти изобретения по П2, содержащая общую шину 1, шину питания 2, адресную шину 3, первую и вторую разрядные шины 4,5, первый и второй управляющие n(р)-МОП транзисторы 6,7, первый и второй переключающие n(р)-МОП транзисторы 8,9, истоки которых подсоединены к общей шине, сток первого переключающего транзистора подсоединен к затвору второго переключающего МОП транзистора, а сток второго переключающего МОП транзистора к затвору первого переключающего МОП транзистора 8, затворы управляющих МОП транзисторов подсоединены к адресной шине 3, истоки первого и второго управляющих транзисторов подсоединены соответственно к стокам первого и второго переключающих МОП транзисторов 8,9, а их стоки к соответственно к первой и второй разрядным шинам 4,5, первый и второй нагрузочные фотодиоды, при этом стоки первого и второго переключающих n(р)-МОП транзисторов 8,9 подсоединены соответственно к анодам (катодам) первого и второго нагрузочных фотодиодов 10,11, при этом фотодиоды являются источниками фото э.д.с., положительные потенциалы которых находится на анодах, а отрицательный на катодах фотодиодов. Катоды (аноды) фотодиодов подсоединены к общей шине 1.

На Фиг.4 показана электрическая схема ячейки памяти изобретения по П3, содержащая общую шину 1, шину питания 2, адресную шину 3, первую и вторую разрядные шины 4,5, первый и второй управляющие n(р)-МОП транзисторы 6,7, первый и второй переключающие n(р)-МОП транзисторы 8,9, истоки которых подсоединены к общей шине, сток первого переключающего транзистора подсоединен к затвору второго переключающего МОП транзистора, а сток второго переключающего МОП транзистора к затвору первого переключающего МОП транзистора 8, затворы управляющих МОП транзисторов подсоединены к, адресной шине 3, истоки первого и второго управляющих транзисторов подсоединены соответственно к стокам первого и второго переключающих МОП транзисторов 8,9, а их стоки к соответственно к первой и второй разрядным шинам 4, 5, первый и второй нагрузочные фотодиоды, при этом стоки первого и второго переключающих n(р)-МОП транзисторов 8,9, подсоединены соответственно к анодам (катодам) первого и второго нагрузочных фотодиодов 10,11, при этом фотодиоды являются источниками фото э.д.с., положительные потенциалы которых находится на анодах, а отрицательный на катодах фотодиодов. Катоды (аноды) фотодиодов подсоединены к адресной шине 3.

На Фиг. 5 показана конструкция (топология сечения) известной ячейки памяти n-МОП ОЗУ ПВ с поликремниевыми нагрузочными транзисторами, взятая за прототип. Конструкция содержит переключающие и управляющие n(р)-МОП транзисторы 6,7,8,9, расположенные на лицевой поверхности кремниевой пластины, на поверхности которой расположен диэлектрик 12 (оксид кремния).

На Фиг. 6 показана конструкция ячейки памяти. Конструкция содержит переключающие и управляющие n(р)-МОП транзисторы 6,7,8,9, расположенные на лицевой поверхности кремниевой пластины, на поверхности которой расположен диэлектрик 12 (оксид кремния), на диэлектрике расположены поликремниевые (аморфные) фотодиоды 10,11, на поверхности которых расположен сцинтиллятор 13, на поверхности сцинтиллятора источник радиоактивного излучения 14 (никель-63, тритий)

Ячейка памяти ЭН. С. ОЗУ ПВ работает следующим образом:

В режиме "хранения информации" в ячейку памяти на адресную шину 3 и соответственно затворы управляющих n-МОП транзисторов 6,7 подается нулевой потенциал общей шины 1, отключающий тригерную ячейку от разрядных шин 4,5.

В режиме "записи информации" в ячейку памяти на шину питания 2 на адресную шину 3 и соответственно затворы управляющих n-МОП транзисторов 6,7 подается положительный потенциал относительно общей шины, а на разрядные шины 4,5 подаются высокий и низкий потенциалы, соответствующие логическому нулю и единице (либо наоборот).

В режиме "считывания информации" с ячейки памяти на адресную шину 3 и соответственно затворы управляющих n-МОП транзисторов 6, 7, подается положительный потенциал относительно общей шины 1, а к разрядным шинам 4,5 подключаются усилители считывания информации логического нуля.

В этом варианте электрическая схема и конструкция ячейки более проста, чем у прототипа, из-за отсутствия шины питания (см. Фиг. 3)

Электрическая схема и конструкция может еще более упрощена путем подсоединения катодов (анодов) диодов с адресной шиной 3 (см. Фиг. 4)

Фотодиоды могут быть выполнены в монокремнии. Использование поликремниевых диодов в качестве нагрузочных резисторов не представляется возможным из-за невоспроизводимости величин их темновых токов.

Примеры:

Первый - "комбинированный" состоящий в подаче на шину питания 2 напряжения питания схемы от внешнего источника э.д.с. – Vdd (например, +5 в) с одновременным облучением фотодиодов потоками ионизирующего излучения, например, фотонами оптического диапазона или радиационного излучения - электронов, рентгеновских квантов, а-частиц. Индуцированный излучением фототок одного из диодов создает на стоке закрытого транзистора триггерной пары высокий потенциал, практически равный напряжению питания – Vdd. Фототок второго диода коммутируется \ закорачивается \ другим транзистором на общую шину. В этом случае имеет место потребление электрической энергии от источника э.д.с. - Vdd.

Второй - "энергонезависимый", в этом варианте источник э.д.с. - Vdd отсутствует и облучаемые диоды находятся в "фотовольтаическом режиме" и сами генерируют фото э.д.с по величине близкую к контактной разности потенциалов р-n перехода фотодиода (Vк - 0,7 в). В этом случае высокий потенциал на стоке закрытого транзистора практически равен -Vк - 0,7 в.

В этом случае отсутствует потребление электрической энергии от источника э.д.с. - Vdd, а энергопитание ячейки памяти осуществляется источником оптического или радиоактивного ионизирующего излучения.

При этом фото э.д.с. диодов может быть создана либо прямым взаимодействием радиационного излучения с материалом фотодиодов (например, изотопа никеля-63, трития) либо косвенно - через сцинтиллятор, преобразующий радиационное излучение в поток оптических фотонов.

При размещении "долгоживущего" источника радиационного излучения (например, от никеля-63) в корпусе микросхемы над элементами памяти кристалла ОЗУ ПВ становится для пользователя "энергонезависимой".

Из фиг. 6 видно, что ячейки памяти "энергонезависимой" СОЗУ ПВ реализуются по стандартной технологии n-МОП СОЗУ ПВ - технологии изготовления прототипа (см. фиг. 5).

При этом фотодиоды могут быть изготовлены из поликремния, аморфного кремния или других материалов. В качестве источника излучения могут быть применены относительно безопасные для здоровья человека изотоп никеля-63 или изотоп водорода - тритий и тд. В качестве сцинтиллятора - цезий-йод, фосфор и тд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти | 1990 |

|

SU1786508A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| Ячейка памяти на основе комплементарных МОП-транзисторов | 1989 |

|

SU1640738A1 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| Ячейка памяти | 1987 |

|

SU1444888A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| ДИНАМИЧЕСКОЕ ПОСЛЕДОВАТЕЛЬНОЕ ФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО | 2005 |

|

RU2392672C2 |

Изобретение относится к наноэлектронике и служит для создания энергонезависимого статического оперативного запоминающего устройства с произвольной выборкой информации. Техническим результатом является уменьшение энергопотребления и повышение степени интеграции. Технический результат достигается тем, что электрическая схема 4-транзисторной ячейки памяти статического оперативного запоминающего устройства с радиоактивным источником питания содержит общую шину, шину питания, адресную шину, первую и вторую разрядные шины, первый и второй управляющие n(р)-МОП транзисторы, первый и второй переключающие n(р)-МОП транзисторы и использует встроенный в матрицу ОЗУ ПВ радиоактивный источник излучения в качестве генератора фототоков в нагрузочных диодах триггерной ячейки. 2 з.п. ф-лы, 6 ил.

1. Электрическая схема 4-транзисторной ячейки памяти статического оперативного запоминающего устройства с радиоактивным источником питания, содержащая общую шину, шину питания, адресную шину, первую и вторую разрядные шины, первый и второй управляющие n(р)-МОП транзисторы, первый и второй переключающие n(р)-МОП транзисторы, истоки которых подсоединены к общей шине, сток первого переключающего транзистора подсоединен к затвору второго переключающего МОП транзистора, а сток второго переключающего МОП транзистора - к затвору первого переключающего МОП транзистора, затворы управляющих МОП транзисторов подсоединены к адресной шине, истоки первого и второго управляющих транзисторов подсоединены соответственно к стокам первого и второго переключающих МОП транзисторов, а их стоки соответственно к первой и второй разрядным шинам, отличающаяся тем, что содержит первый и второй нагрузочные фотодиоды, при этом стоки первого и второго переключающих n(р)-МОП транзисторов подсоединены соответственно к анодам и катодам первого и второго нагрузочных фотодиодов, катоды и аноды которых подсоединены к шине питания, или к общей шине, или к адресной шине, при этом фотодиоды являются источниками фотоЭДС, положительные потенциалы которых находятся на анодах, а отрицательные на катодах фотодиодов.

2. Электрическая схема 4-транзисторной ячейки памяти по п.1, отличающаяся тем, что катоды и аноды фотодиодов подсоединены к общей шине.

3. Электрическая схема 4-транзисторной ячейки памяти по п.1, отличающаяся тем, что катоды и аноды фотодиодов подсоединены к адресной шине.

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| US 4901284 A1, 13.02.1990 | |||

| US 3387286 A1, 04.06.1968 | |||

| US 4794571 A1, 27.12.1988. | |||

Авторы

Даты

2022-08-08—Публикация

2021-07-15—Подача