(54) УСТРОЙСТВО ДЛЯ ВЫБОРКИ АДРЕСОВ ИЗ БЛОКОВ ПАМЯТИ

I

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Известно устройство для выборки адресов из блоков памяти, состоящее из адресных формирователей прямого и дополнительного кода адреса по одному на каждую входную адресную шину, динамических вентилей ИЛИ-НЕ, входы которых соединены со всеми комбинациями выхбдных шин адресных формировате.(1ей для выбора одного из выходов устройства и выходн ях. формирователей по одному на каждый выход. Адресные формирователи состоят из двадцати трех МОП-транзисторов и четырех конденсаторов, образующих первые и вторые динамические инверторные каскады и выходные каскады 1.

Недостатком такого устройства является большое число МОП-транзисторов и кондерсаторов в составе устройства.

Наиболее близким к предлагаемому техническим решением является устройство для. выборки адресов из блоков памяти, включающее в себя адресные формирователи, в которых истоки первого и второго адресных МОП-транзисторов подключены к шине иулевого потенциа,па, затвор второго адресного МОП-транзистЬра соединен со стоком первого и истоком третьего адресных МОПтранзисторов, затворы третьего и четвертого адресных МОП-транзисторов соединены с первой TiaKTOBoA шиной, исток четвертого адресного МОП-транзистора соединен со стокбм второго адресного МОП-транзистора, стоки третьего и четвертого адресных МОП-транзисторов соединены соответственно с истоками пятого и uiecToro адресных МОП-транзисторов, затворы которых соеди10нены со второй тактовой шиной, стоки пятого н шестого адресных МОП-транзисторов подключены к шине стокового питания. Исто ки пятого и шестого адресных МОП-транзисторов через первый и второй конденса15торы соединены с шиной первого тактового сигнала, а также с затворами соответственно седьмого и восьмого адресных МОП-транзисторов, истоки которых соединены с шиной нулевого потенциала. Стоки седьмого 2Q и восьмого адресных МОП-транзисторов соединены соответственно с истоками девятого и десятого адресных МОП-транлнсторов, затворы которых подключены соответственно к истокам шестого и пятого адресных МОП траШнскУров a их стоки соединены с истоком одиннадцатого адресного МОП-транзистора, затвор которого подключен к первой тактоиой тине, а сток - к шине питания. Истоки девятого и десятого адресных МОП-транзисторов соединены соответственно со стоками двенадцатого итрй надцатого адресных МОП-транзисторов, их за-творы подключены к шине второго тактового сигнала, и истоки - к шиие нулевогопотенциала. Истоки девятого и десятого адресных МОП-транзисторов также подключены к затворам логических МОП-транзисторов лищмимеских вентилей ИЛИ-НЕ по схеме параллельного декодера, истоки логических МОП-транзисторов подключены к шине нулевого потенциала, а стоки - к истокам зарядных МОП-транзисторов н к выходным шинам. Затворы зарядных MOTfl-транзисторов подключены ко второй тактовой шине, а стоки - к шине питания 2.

Цель изобретения

упрощение устройства.

Поставленная цель достигается тем, что устройстве для выборки адресов из блоков памяти, содержашем адресные формиователи, каждый из которых состоит из шести адресных МОП-транзисторов, причем истоки первого и второго адресных МОПранзисторов подключены к шине нулевого потенциала, затвор второго адресного МОПранзистора соединен со стоком первого и стоком третьего адресных МОП-транзисоров, затворы третьего и четвертого адресных МОП-транзисторов соединены с первой тактовой шиной, исток четвертого адресного МОП-транзистора соединен со стоком второго ад:ресного МОП-транзистора, ,стоки третьего и четвертого адресных МОП-транзисторов соединены соответственно с истокамиПятого и Шестого адресных МОП-транзисторов, затворы которых соединены со втброй тактовой шиной, стоки пятого и шестого адресных МОП-транзисторов подключены к Ц1ине питания, элементы ИЛИ-НЕ, подключенные к выходным шинам выходных формирователей, состоящих из зарядных МОПтранаисторов и логических МОП-транзистрров, причем истоки зарядных МОП-тр анэ;Исторов соединены с выходными шинами элементов ИЛИ-НЕ и стоками логических МОПтранзйсторов, стоки зарядных МОП-транзис торов соединены с шиной питания, истоки пягого и ujecTorp адресных МОП-транзисторов соединены с затворами логических МОП траИЛисторов, истоки логических МОП-тр анзисторов и затворы зарядных МОП-транзисторов подключены к первой тактовой щине

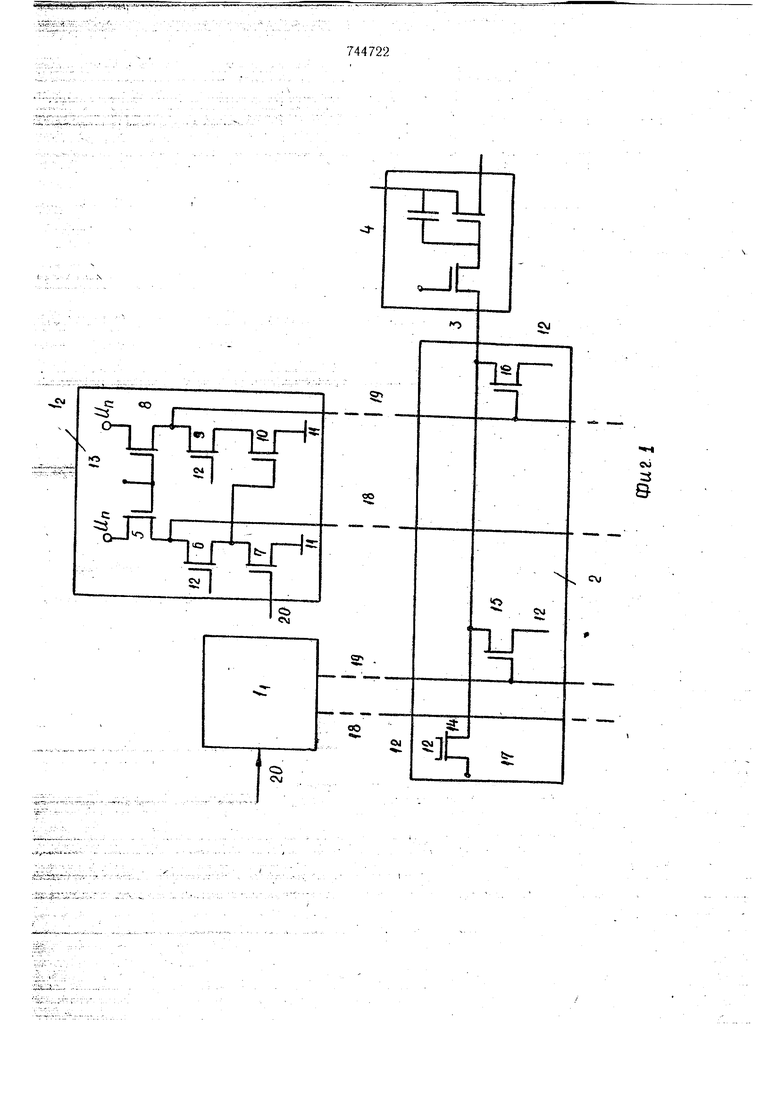

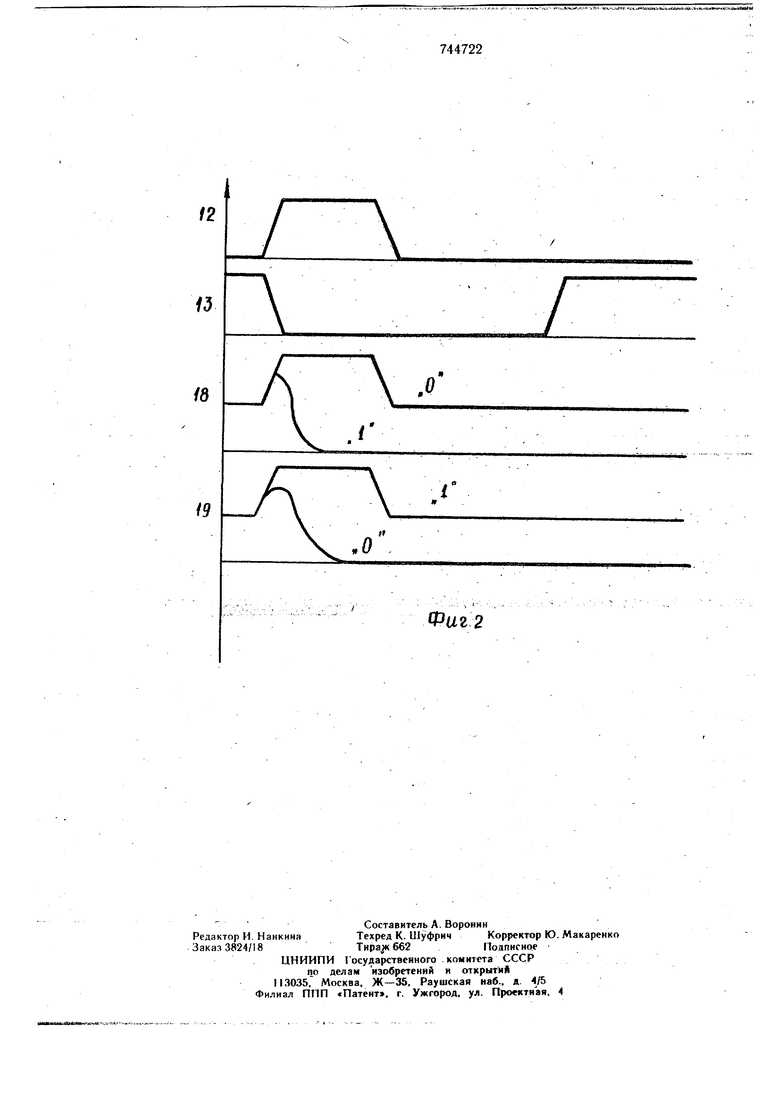

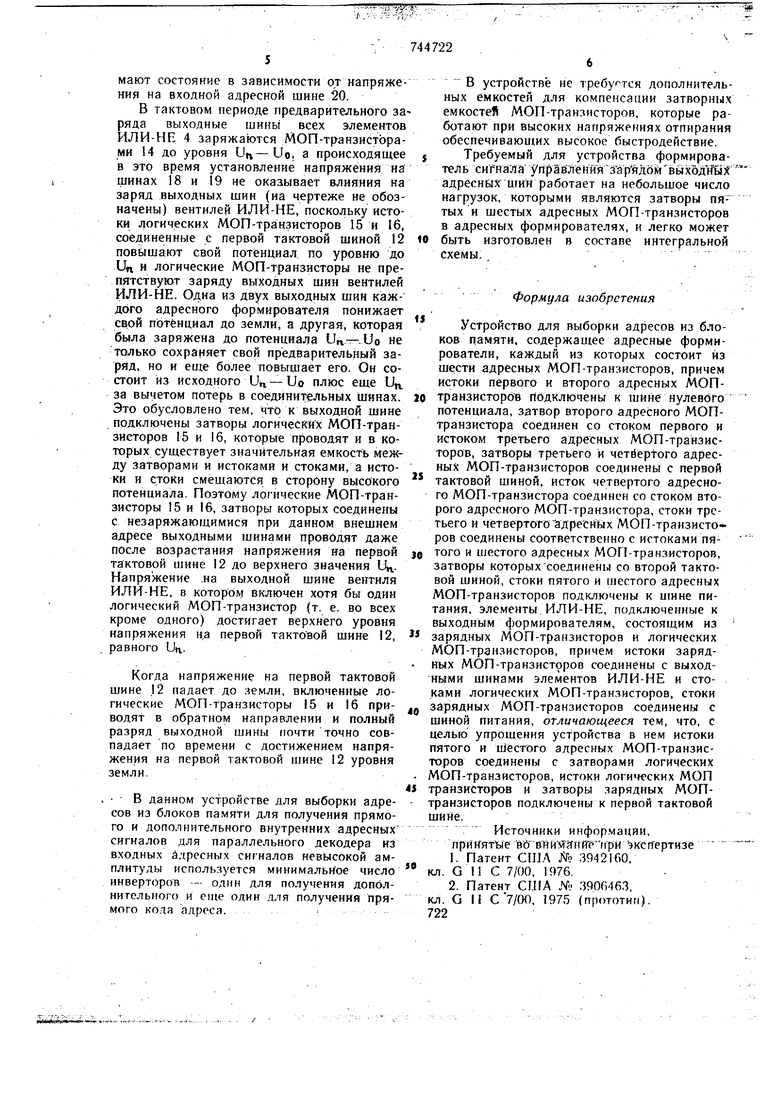

На фиг. I представлена сокращенная схема устройства; на фиг. 2 -- временная диаграмма напряжения на тактовых шинах нуялах устройства.

744722

Устройство содержит адресные формирователи 11, 12, выходной формирователь 2, входная шина 3 которого соединена с элементом ИЛИ-НЕ 4, каждый адресный формирователь I содержит шесть адресных

МОП-транзисторов 5, 6, 7, 8, 9 и 10, истоки первого 7 и второго 10 адресных МОПтранзисторов подключены к шине 11 нулевого потенциала, затворы третьего б и четвертого 9 адресных МОП-транзисторов соединены с первой тактовой шиной 12, затворы пятого 5 и шестого 8 адресных МОП-тран зисторов соединены со второй тактовой шиной 13, выходной формирователь 2 содержит зарядный МОП-транзистор 14 и логические МОП-транзисторы 15 и 16, сток зарядного МОП-транзистора 14 соединен с шиной 17 питания.

Устройство работает следущим образом. Обе выходные адресные шины 18 и 19 каждого адресного формирователя i за пределами цикла памяти заряжены до уровня

Uit.- Uo МОП-транзисторами 5 и 8, где УП - напряжете питания стока, Uo - пороговое напряжение МОП-транзисторов обо- гашенного типа, Первым сигналом временной диаграммы (фиг. 2) является сигнал предварительного заряда по первой такто вой шине 12, имеющей форму импульса с амплитудой UH- На входных адресных шинах 20 в начале предварительного заряда и в течение всего времени предварительного заряда должен быть установившийся адрес. По

0 сигналу 12 по первой тактовой шине уровень сигнала 13 пЬ второй тактовой шине понижается до уровня земли «О и выходные адресные шины J8 и 19 отключаются от шнны питания Un, а МЬП-транзисторы 6 и 9 вводятся в проводяи1ее состояние н начи;

нается разряд одной из выходных шин 18 и 19. При логическом нуле на входной шине 20 адресный МОП-транзистор 5 оказывается выключенным, и несмотря на включение адресного МОП-транзистора 7, разц ряд выходной адресной шины {8 на землю отсутствует. Прбтекаюший через адресный МОП-транзистор 7 ток заряжает затвор адресного МОП-транзистора 6 и при включении его разряжается выходная адресная шина 19. .

Если же на входной адресной шине 20 установлена логическая единица, то адресный МОП-транзистор 7 проводит и при включении адресного МОП-транзистора 6 вь1х0дная шина 18 разряжается. Соотношение меж

в ду проводимостям адресных МОП-транзисторов б и 7 должно ,b таким, чтобы высокий потенциал на выходной шине 18 не воздействовал на затвор адресного МОПтранзистора 10 и не произошел ложный разJ ряд выходной, (адресной) шины 19, которая должйа оставаться заряженной.

После возрастания напряжения на пер вой тактовой.шине 12 ло верхнего значения выходные адресные шины 18 и 19 прииимают состояние в зависимости от напряжения на входной адресной шине 20.

В тактовом периоде предварительного заряда выходные шины всех элементов ИЛИ-НЕ 4 заряжаются МОП-транзисторами 14 до уровня Utv- Uo, а происходящее в это время установление напряжения на шинах 18 и 19 не оказывает влияния на заряд выходных шин (на чертеже не обозначены) вентилей ИЛИ-НЕ, поскольку истоки логических МОП-транзисторов 15 и 16, соединенные с первой тактовой шиной 12 повышают свой потенциал по уровню до Un и логические МОП-транзисторы не препятствуют заряду выходных шин вентилей ИЛИ-НЕ. Одна из двух выходных шин каждого адресного формирователя понижает свой потенциал до земли, а другая, которая была заряжена до потенциала Un-.Uo не только сохраняет свой предварительный заряд, но и еще более повышает его. Он состоит из исходного UH-UO плюс еще Un. за вычетом потерь в соединительных шинах. Это обусловлено тем, что к выходной шине подключены затворы логических МОП-транзисторов 15 и 16, которые проводят и в которых существует значительная емкость между затворами и истоками и стоками, а истоки н стоки смещаются в сторону высокого потенциала. Поэтому логические МОП-транзисторы 15 и 16, затворы которых соединены с незаряжающимися при данном внешнем адресе выходными шинами Проводят даже после возрастания напряжения на первой тактовой шине 12 до верхнего значения Un.Напряжение ,на выходной шнне вентиля ИЛИ-НЕ, в котором включен хотя бы один огический МОП-транзистор (т. е. во всех кроме одного) достигает верхнего уровня напряжения н,а первой тактовой шине 12, авного Uti.

Когда напряжение на первой тактовой шине 12 падает до земли, включенные логические МОП-транзисторы 15 и 16 приводят в обратном направлении и полный разряд выходной шины почти точно совпадает по времени с достижением напряжения на первой тактовой шине 12 уровня емли.

В данном устройстве для выборки адресов из блоков памяти для получения прямого и дополнительного внутренних адресных сигналов для параллельного декодера из входных Адресных сир-налов невысокой амплитуды используется минимальное число инверторов -- один для получения дополнительного и еще один для Получения прямого кода адреса.

В устройстве не требу тся дополнительных емкостей для компенсации затворных емкостей МОП-транзисторов, которые работают при высоких нaпpяжeF ияx отпирания обеспечивающих высокое быстродействие.

Требуемый для устройства формирователь сигнаЛа управЛенйязарядбмвыхддда адресных шин работает на небольшое число нагрузок, которыми являются затворы пятых и шестых адресных МОП-транзисторов в адресных формирователях, и легко может

быть изготовлен в составе интегральной схемы.

Формула изобретения

Устройство для выборки адресов из блоков памяти, содержащее адресные формирователи, каждый из которых состоит из шести адресных МОП-транзисторов, причем истоки первого и второго адресных МОПтранзисторов Г1одключень1 к шине нулевбГо потенциала, затвор второго адресного МОПтранзистора соединен со стоком первого и истоком TpieTbero адресных МОП-транзисторов, затворы третьего и четйерТого адресных МОП-транзисторов соединены с первой

тактовой шиной, исток четвертого адресного МОП-транзистора соединен со стоком второго адресного МОП-транзистора, стоки третьего и четвертогоадресных МОП-транзисторов соединены соответственно с истоками пятого и шестого адресных МОП-транзисторов, затворы которыхсоединены со второй тактовой шиной, стоки пятого и шестого адресных МОП-транзисторов подключены к шине питания, элементы ИЛИ-НЕ, подключенные к выходным формирователям, состоящим из

зарядных МОП-транзисторов и логических МОП-транзисторов, причем истоки зарядных МОП-транзисторов соединены с выходными шинами элементов ИЛИ-FiE и стоками логических МОП-транзисторов, стоки

зарядных МОП-транзисторов соединены с шиной питания, отличающееся тем, что, с целью упрощения устройства в нем истоки пятого и Шестого адресных МОП-транзисторов соединены с затворами логических

МОП-транзисторов, истоки логических МОП транзисторов и затворы зарядных МОПтранзисторов подключены к первой тактовой шине.

Источники информации, принятые вбВТ)HNSaffiTrfipH экспертизе

1.Патент СШ.Л ff« 3942160, кл. G 11 С 7/00, 1976.

2.Патент США № ,5906463, кл. G И С7/0(), 1975 (прототип). 722

см

3 S

/

12

fJ

/8

/9

r

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Блок выборки информации из матричного накопителя | 1980 |

|

SU928413A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Формирователь импульсов на МОП-транзисторах | 1984 |

|

SU1236604A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

Фаг 2

Авторы

Даты

1980-06-30—Публикация

1976-07-27—Подача