Текст описания приведен в факсимильном виде.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФОРМИРОВАНИЯ НЕРЕГУЛЯРНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ С ЭЛЕМЕНТАМИ, СОСТАВЛЕННЫМИ ИЗ ДВОИЧНЫХ СИГНАЛОВ | 2011 |

|

RU2467378C1 |

| ПРОГРАММНО-УПРАВЛЯЕМАЯ ЛОГИЧЕСКАЯ СХЕМА, ИСПОЛЬЗУЮЩАЯ МАГНИТОРЕЗИСТИВНЫЕ УСТРОЙСТВА С ПЕРЕДАЧЕЙ СПИНОВОГО ВРАЩЕНИЯ | 2008 |

|

RU2420865C1 |

| СПОСОБ И СИСТЕМА ИДЕНТИФИКАЦИИ ИЗМЕРЕНИЙ В МНОГОДИАПАЗОННЫХ РЛС | 2014 |

|

RU2574075C1 |

| СЪЕМНЫЙ НОСИТЕЛЬ ИНФОРМАЦИИ С ПОВЫШЕННОЙ СКОРОСТЬЮ ДОСТУПА | 2011 |

|

RU2473142C1 |

| Ячейка однородной структуры | 1988 |

|

SU1501035A2 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ КРАЕВ ДЛЯ СИСТЕМЫ ОБРАБОТКИ ИЗОБРАЖЕНИЯ | 1991 |

|

RU2020582C1 |

| СИСТОЛИЧЕСКИЙ ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1992 |

|

RU2029437C1 |

| СИСТЕМА И СПОСОБ ОПРЕДЕЛЕНИЯ КООРДИНАТ ОПОРНОГО МЕСТОПОЛОЖЕНИЯ | 2009 |

|

RU2498347C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ, СПОСОБ ОБРАБОТКИ ДАННЫХ И ПРОГРАММА | 2012 |

|

RU2603550C2 |

| Устройство для измерения спектрального распределения радиоактивного излучения | 1987 |

|

SU1424512A1 |

Изобретение относится к цифровой технике и может быть использовано для генерации случайных чисел и преобразования данных, обработки шумоподобных сигналов, идентификации, аутентификации и авторизации, в стохастических системах и устройствах, системах представления и отображения информации, информационно-коммуникационных и сенсорных устройствах и системах. Техническим результатом является формирование регулярных двоичных последовательностей, являющихся исходными для осуществления преобразований и получения последовательностей (бесповторных или равноповторных) с периодом не менее заданного, с предопределенными, характерными для реальных процессов гармоничными и хаотичными свойствами. Реализуемые на его основе многоразрядные устройства характеризуются устойчивым, функционально непредсказуемым поведением, исчерпывающе полным параллелизмом и простотой в реализации, малыми аппаратными и энергетическими затратами, высоким уровнем производительности. Устройство, реализующее способ, содержит генератор тактовых импульсов, блок нелинейных управляемых элементов, состоящих из логических элементов с перестраиваемой конфигурацией, D-триггеры. 2 з.п. ф-лы, 30 ил., 2 табл.

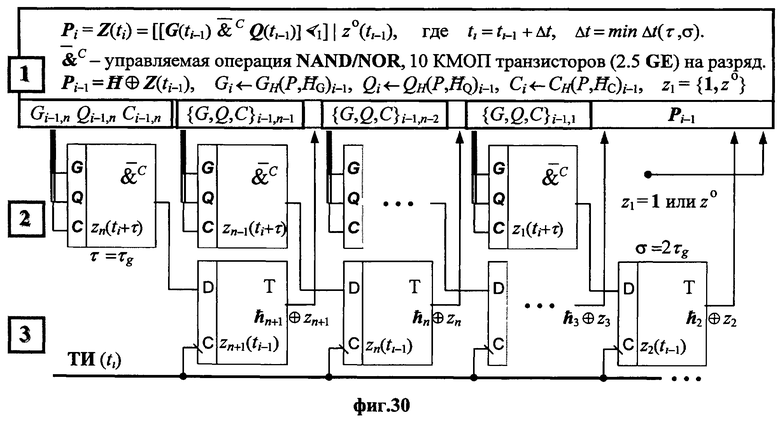

1. Способ формирования регулярных последовательностей с элементами, составленными из двоичных сигналов, включающий в себя

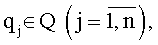

- итерационный процесс осуществления действий в дискретном времени  , начиная с некоторого начального момента времени t0, над двоичными, идентифицируемыми как 0 или 1, сигналами материальной природы, входящими в состав функционально связанных между собой двоичных блоков, которые формируют из двоичных разрядов, нумеруемых согласно принятым правилам по степени 2j-1, а сами разряды в упомянутых блоках размещают в порядке, предписываемом техническим результатом; а

, начиная с некоторого начального момента времени t0, над двоичными, идентифицируемыми как 0 или 1, сигналами материальной природы, входящими в состав функционально связанных между собой двоичных блоков, которые формируют из двоичных разрядов, нумеруемых согласно принятым правилам по степени 2j-1, а сами разряды в упомянутых блоках размещают в порядке, предписываемом техническим результатом; а

- упомянутые действия задают на множестве действий, с подмножеством действий, представляемых нелинейными двоичными операциями Δ и ∇ над сигналами, осуществляемых посредством соответствующих им логических элементов ▲∈{NAND, AND} и ▼∈{NOR, OR}, из множества логических элементов {NAND, AND, NOR, OR} и подмножеством действий, представляемых цифровыми устройствами - нелинейными управляемыми логическими элементами ▲/▼∈{NAND/NOR, AND/OR} и ▼/▲∈{NOR/ NAND, OR/AND}, из множества управляемых логических элементов {NAND/NOR, AND/OR, NOR/NAND, OR/AND};

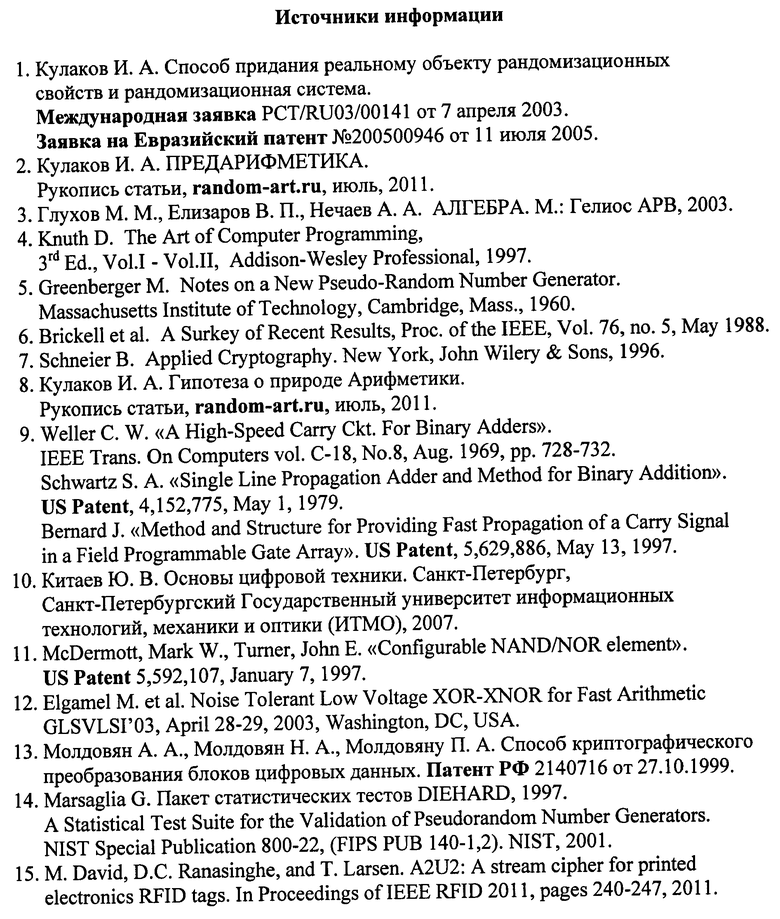

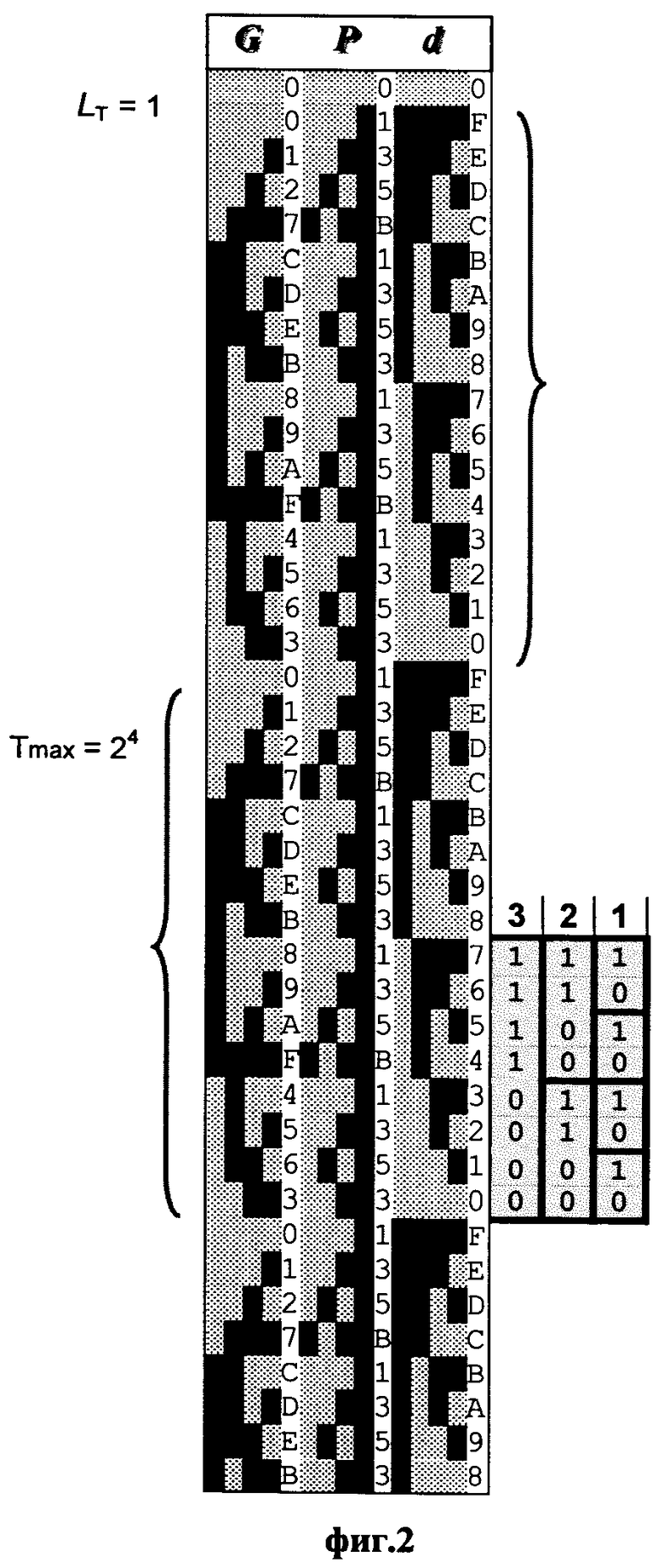

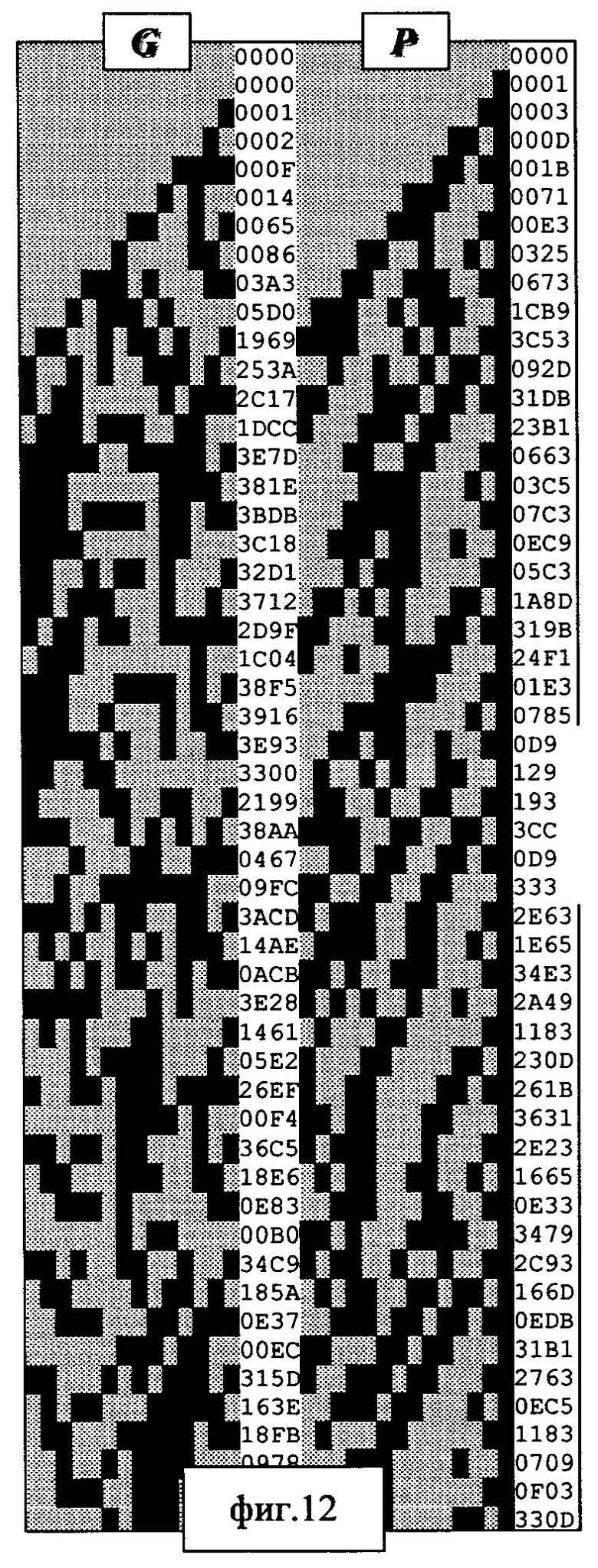

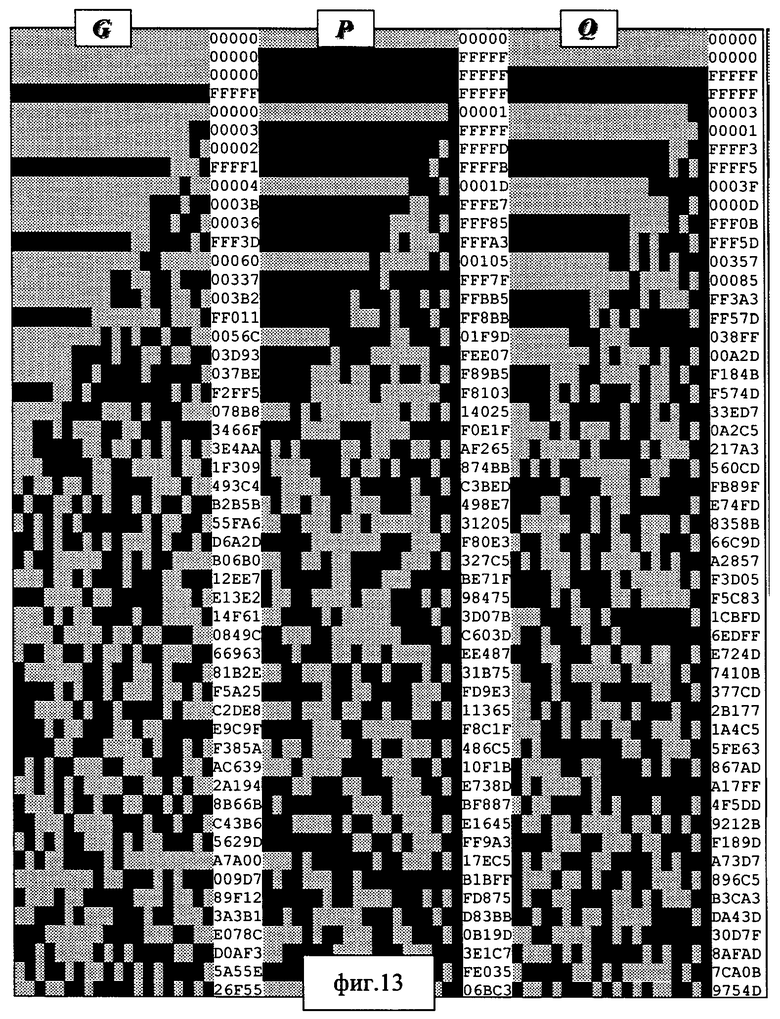

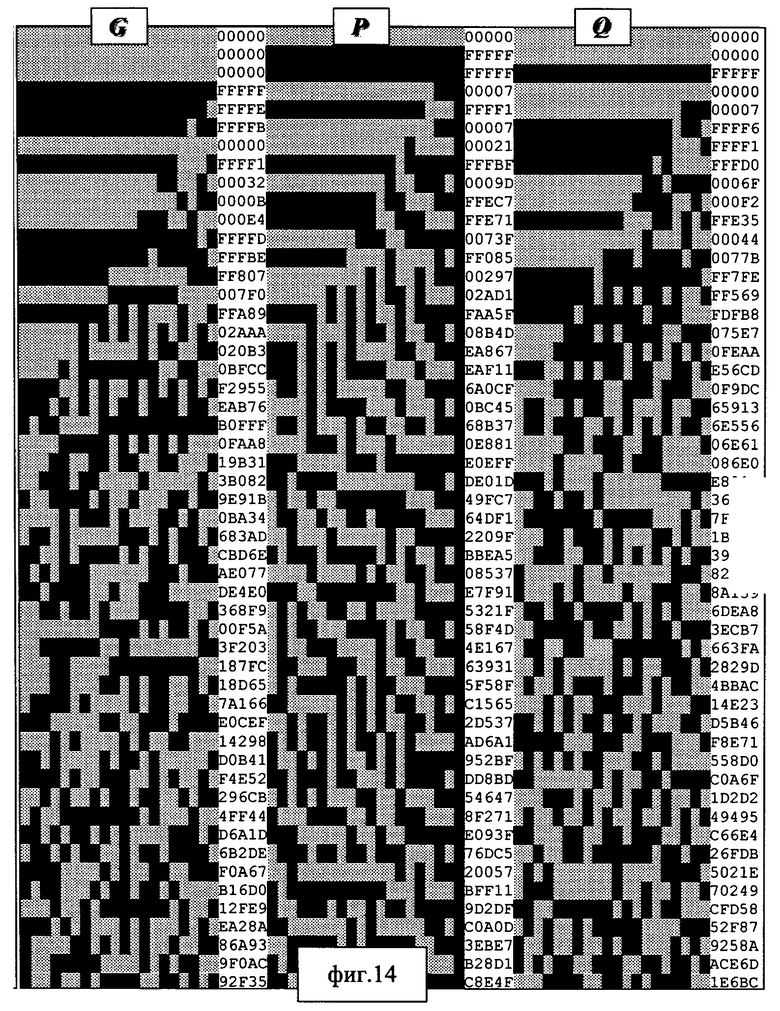

- а каждому очередному np-разрядному элементу pi∈PΩ, представляемой способом, не менее чем одной, двоичной последовательности PΩ, ставят в соответствие сигналы  поступающие с разрядов j (n+ε)-разрядного двоичного образующего блока Z, а указанное приращение ε разрядности блока задают равным 0 или 1;

поступающие с разрядов j (n+ε)-разрядного двоичного образующего блока Z, а указанное приращение ε разрядности блока задают равным 0 или 1;

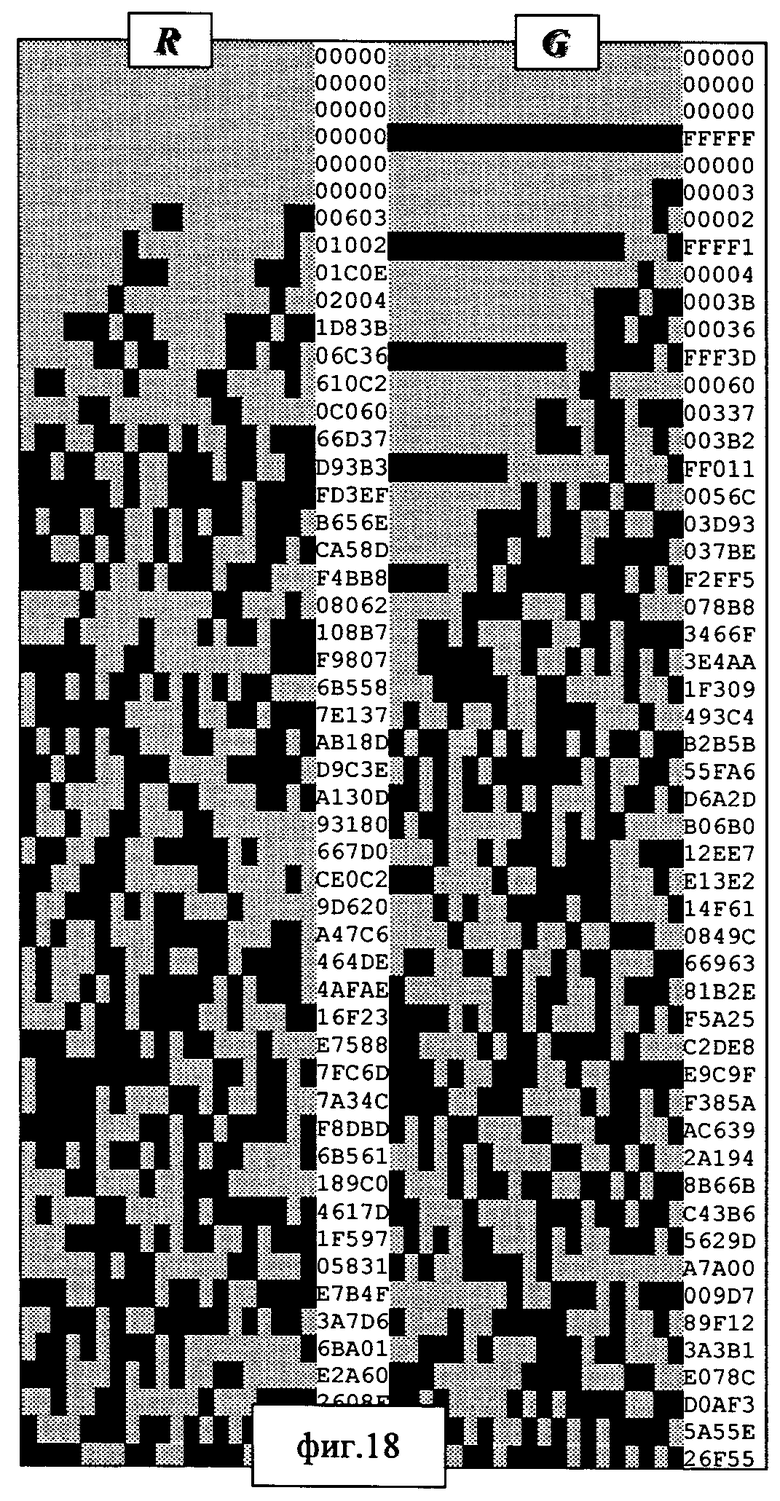

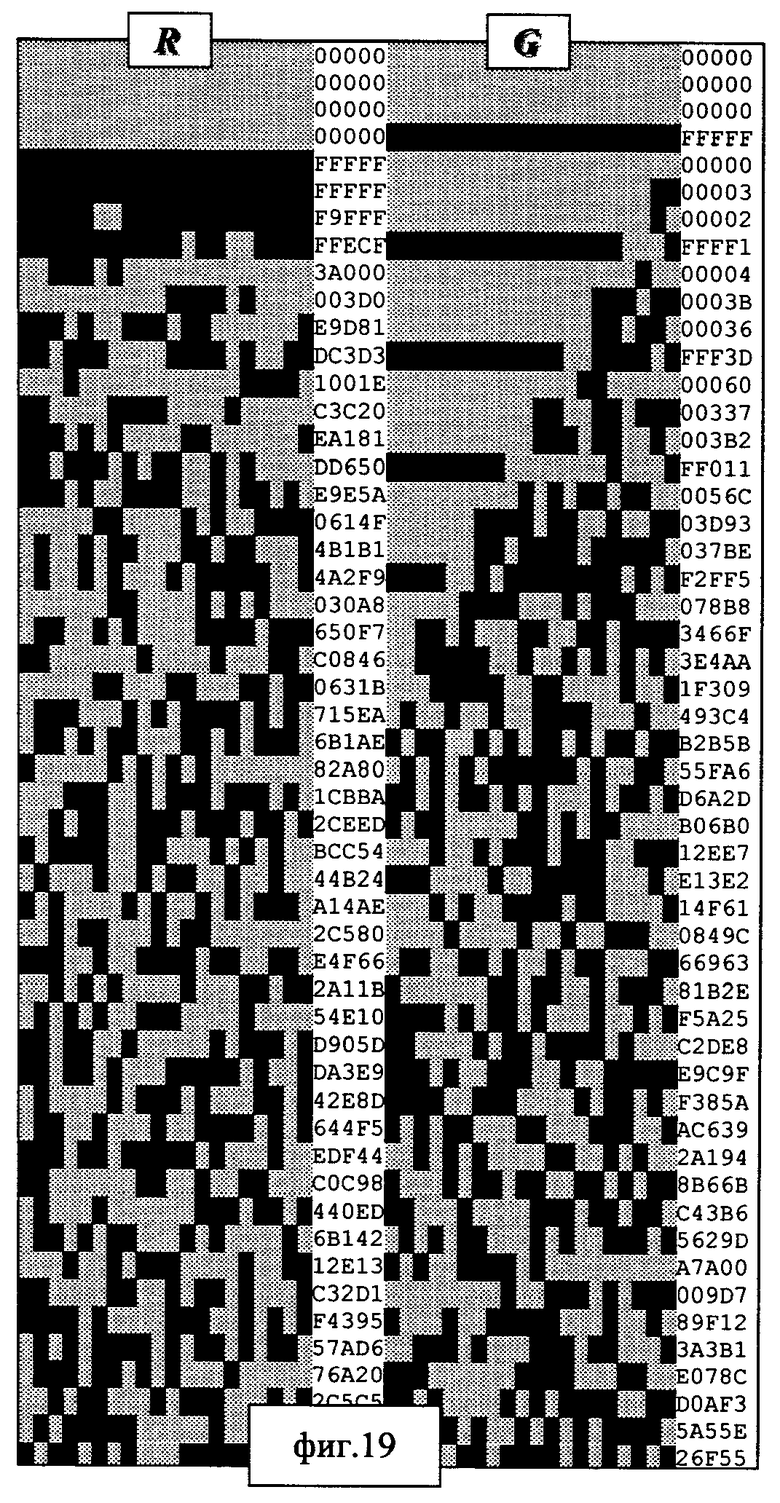

- и при этом состояние образующего блока Z изменяют согласно с упомянутым временем ti хода итерационного процесса в зависимости от его предшествующих состояний, исходя из предписываемой техническим результатом зависимости очередных элементов pi∈PΩ последовательности PΩ, от изменений ее предшествующих элементов;

- при этом по ходу упомянутого процесса состояние двоичных разрядов  образующего блока Z изменяют исходя из формальных условий, что при замене константой или изоляции внешних по отношению к упомянутому процессу переменных сигналов изменения сигналов zk в каждом из младших разрядов

образующего блока Z изменяют исходя из формальных условий, что при замене константой или изоляции внешних по отношению к упомянутому процессу переменных сигналов изменения сигналов zk в каждом из младших разрядов  блока Z не зависят от изменений сигналов zl в каждом из его старших разрядов

блока Z не зависят от изменений сигналов zl в каждом из его старших разрядов  что фактически означает отсутствие обратных связей между составляющими блок Z разрядами j; при этом

что фактически означает отсутствие обратных связей между составляющими блок Z разрядами j; при этом

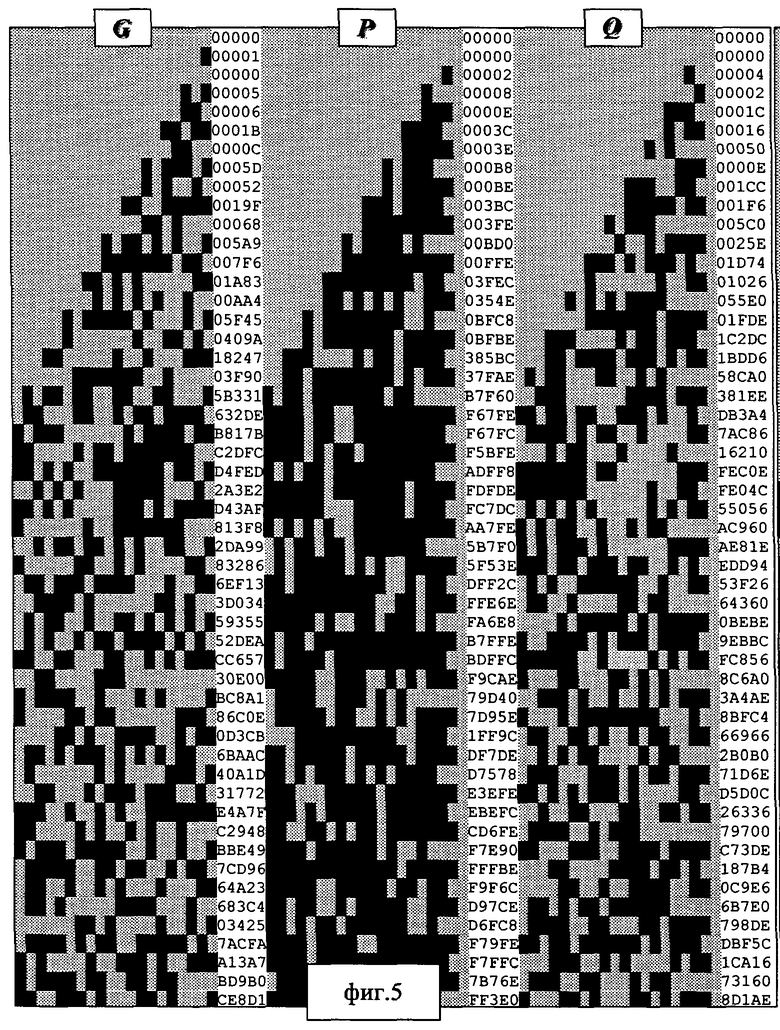

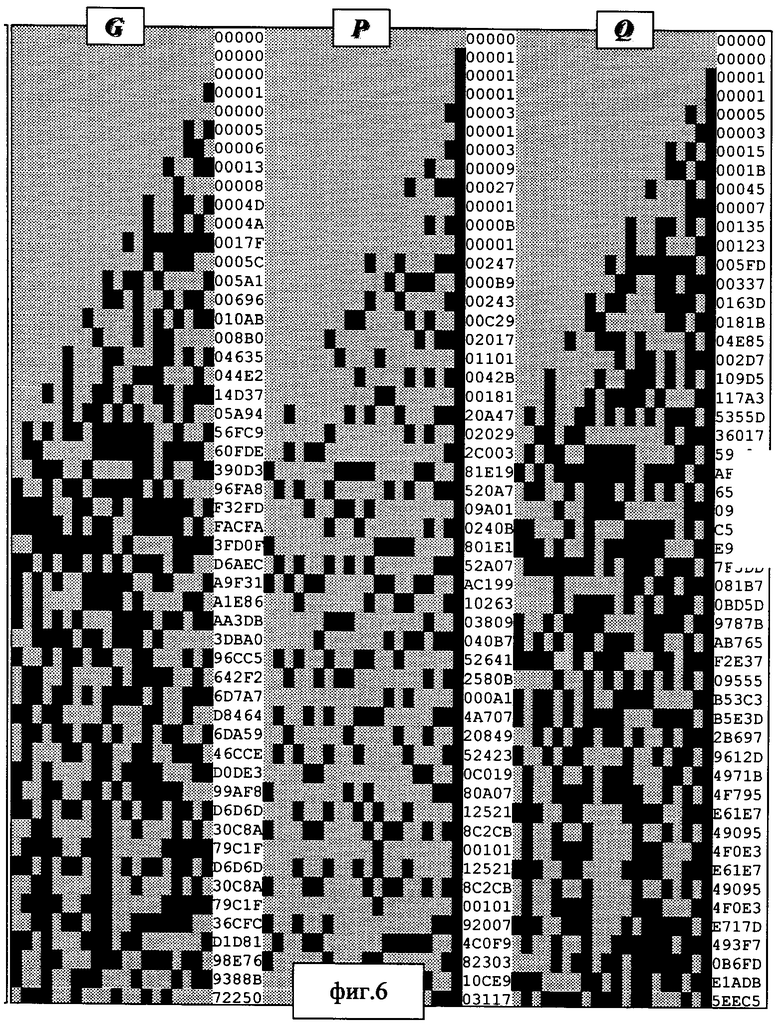

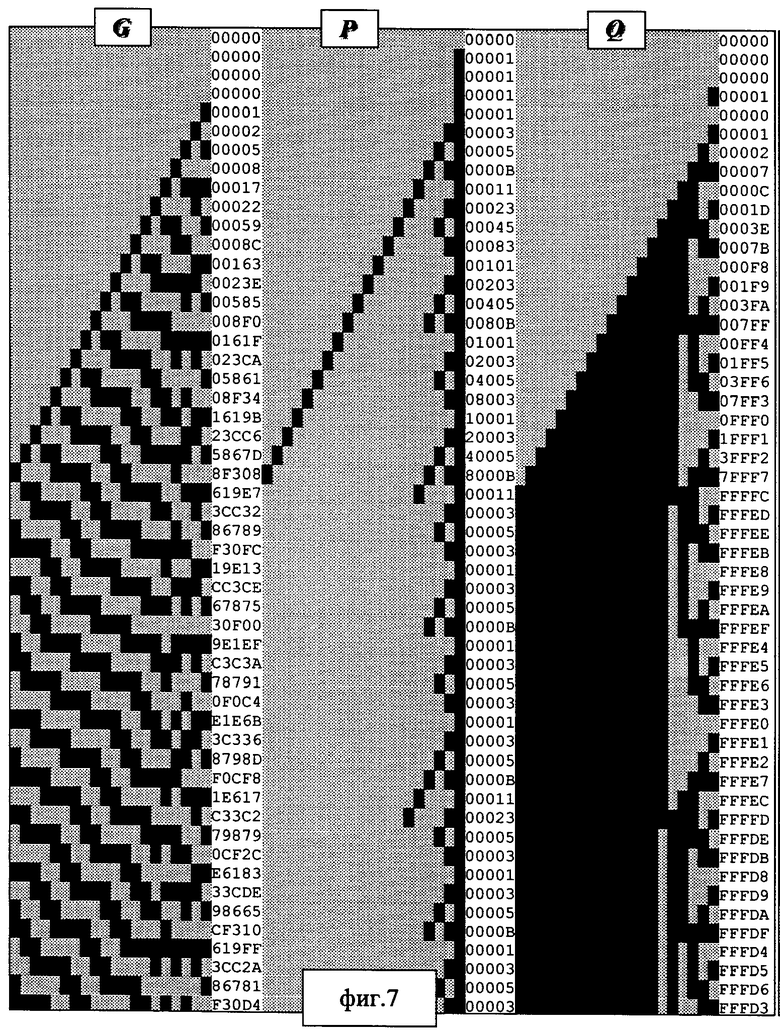

- упомянутый итерационный процесс включает в себя n-разрядные двоичные блоки:

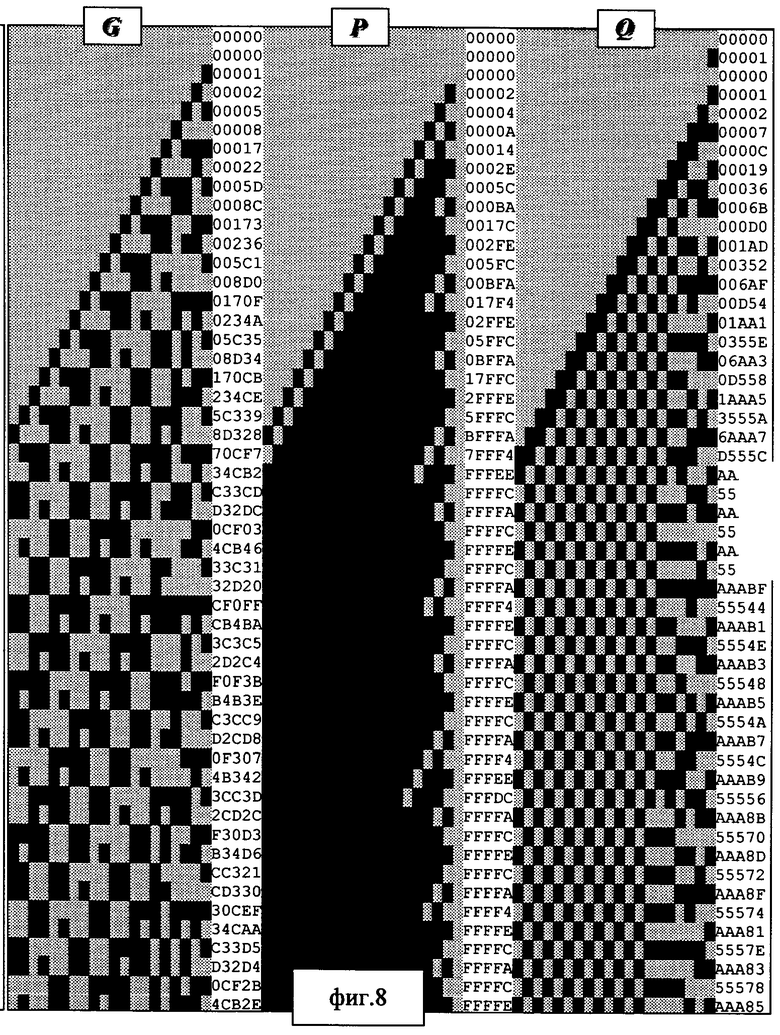

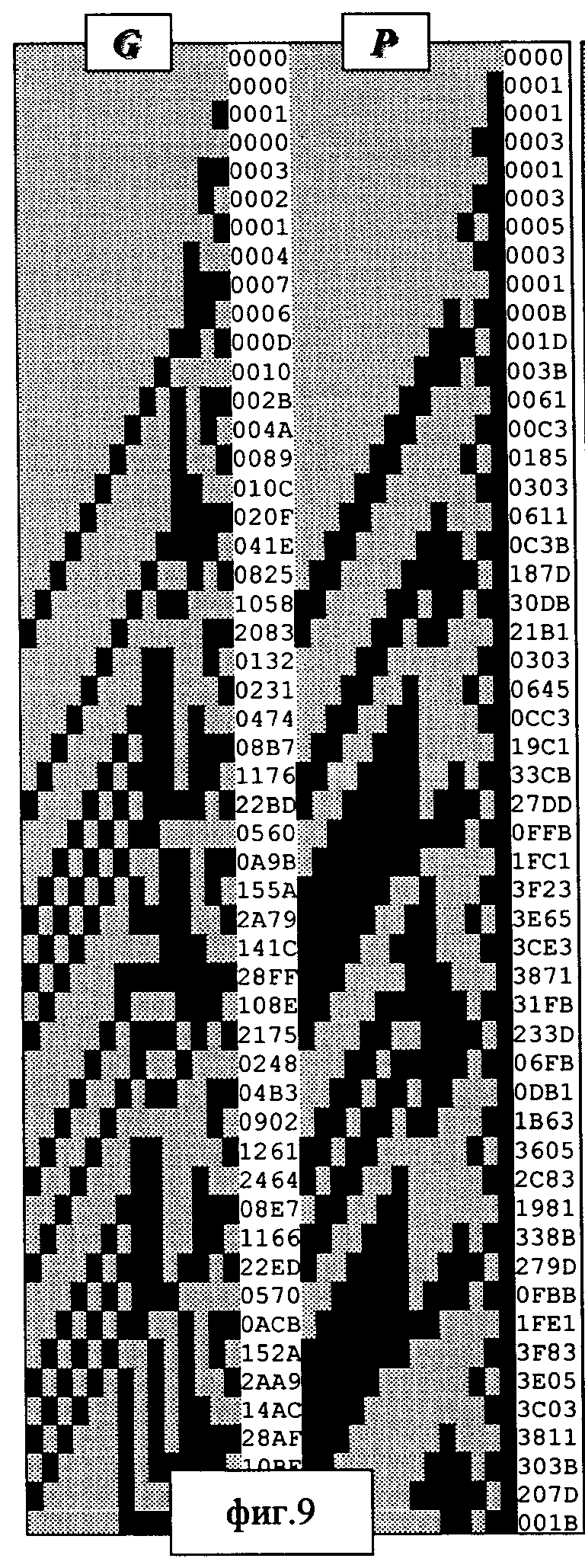

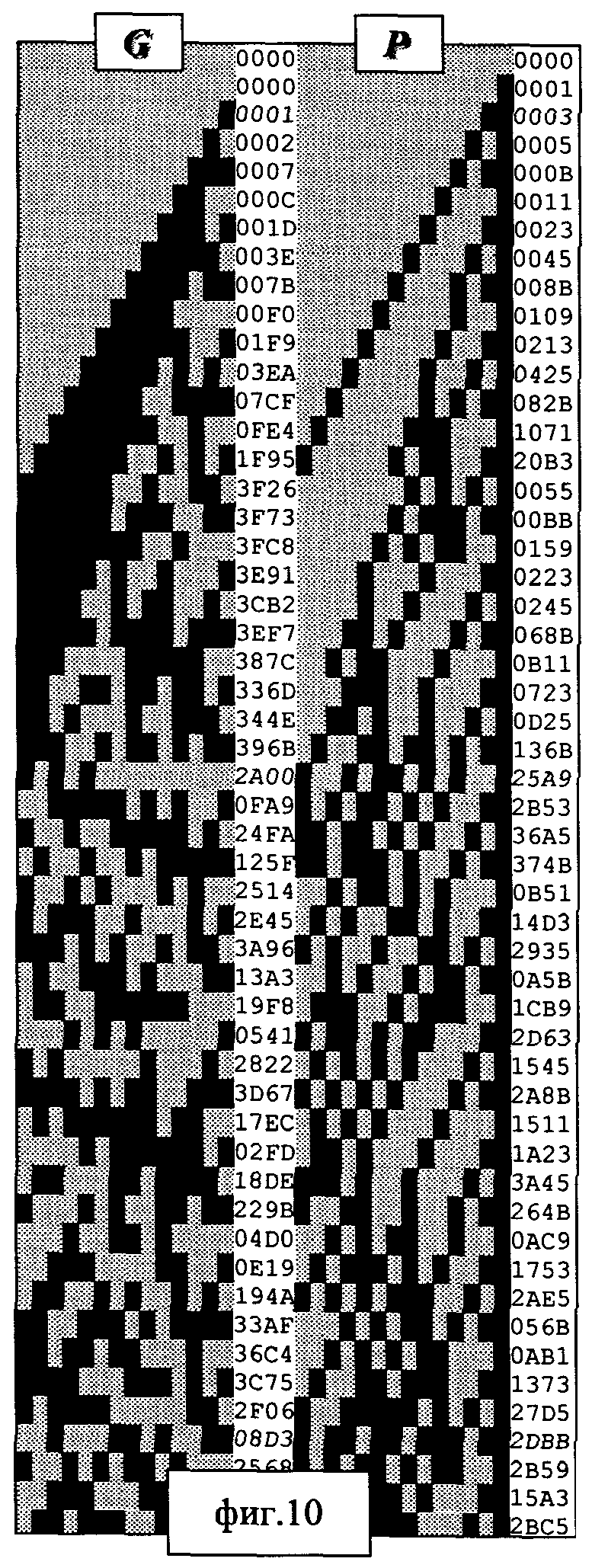

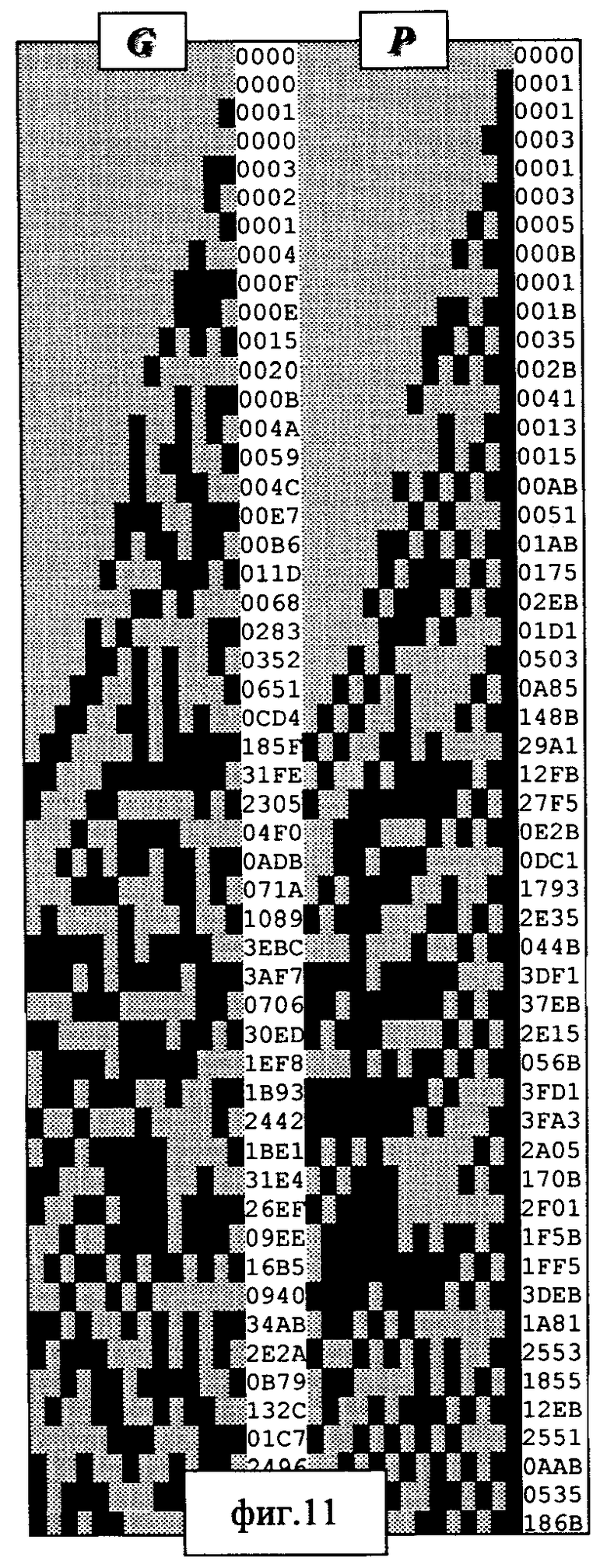

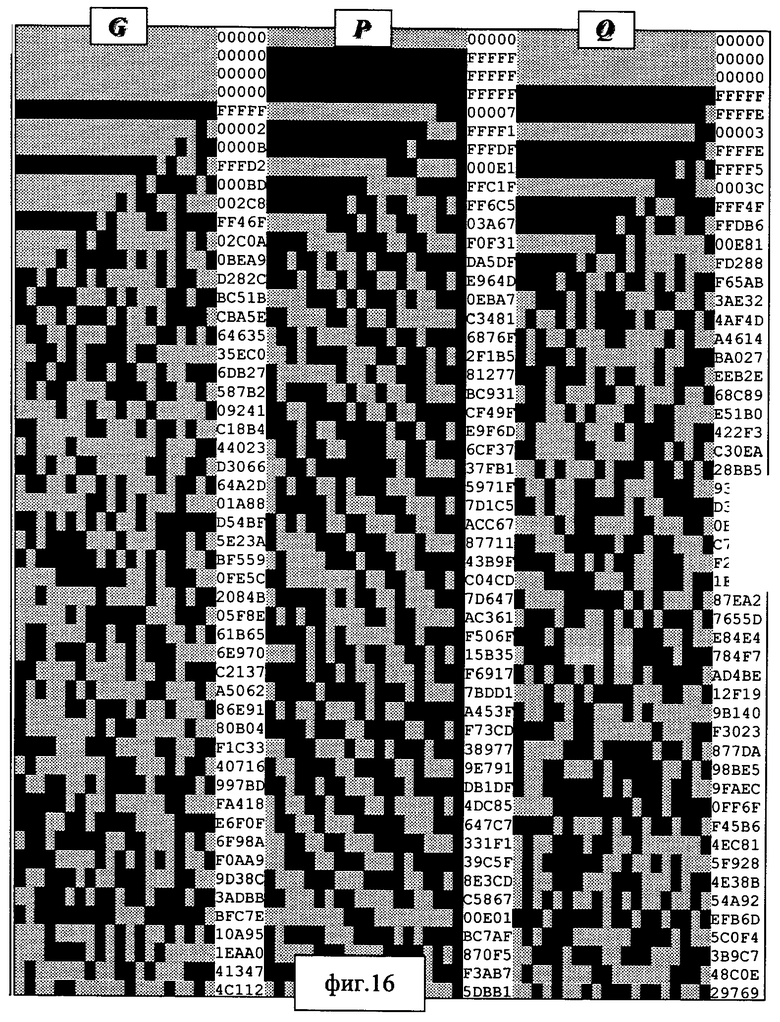

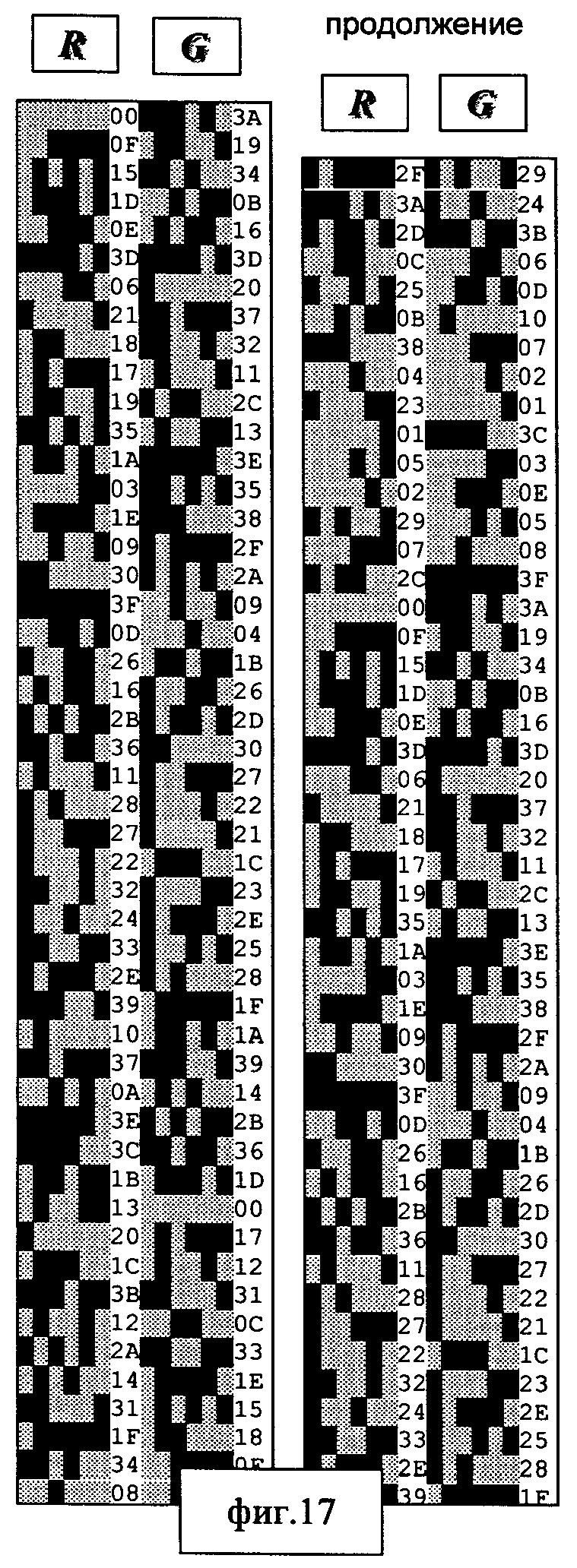

- базовый блок G сигналов gj∈G и нелинейный блок Q сигналов  которые формируют в зависимости от предшествующих состояний блока Z;

которые формируют в зависимости от предшествующих состояний блока Z;

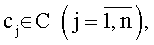

- управляющий блок C сигналов  которые задают в зависимости или независимо от предшествующих состояний блока Z, при этом блок C, у которого все поступающие из разрядов сигналы неидентифицируемы, считают пустым;

которые задают в зависимости или независимо от предшествующих состояний блока Z, при этом блок C, у которого все поступающие из разрядов сигналы неидентифицируемы, считают пустым;

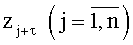

- а сигналы  образующего блока Z формируют прямо, без смещения (τ=0) или со смещением τ=1 на один разряд, в зависимости от состояния cj разряда j управляющего блока C и двоичных сигналов {Δzj, ∇zj};

образующего блока Z формируют прямо, без смещения (τ=0) или со смещением τ=1 на один разряд, в зависимости от состояния cj разряда j управляющего блока C и двоичных сигналов {Δzj, ∇zj};

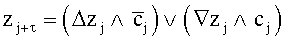

- при идентифицируемом сигнале cj сигнал zj+τ формируют в соответствии с логическим выражением  путем выбора одного из двух двоичных сигналов {Δzj, ∇zj}, формируемых исходя из индексируемых {Δj, ∇j} по номеру разряда j блока C упомянутых операций Δ и ∇, осуществляемых посредством соответствующего нелинейного управляемого логического элемента ▲/▼ или ▼/▲ с перестраиваемой конфигурацией по сигналу cj; так, что

путем выбора одного из двух двоичных сигналов {Δzj, ∇zj}, формируемых исходя из индексируемых {Δj, ∇j} по номеру разряда j блока C упомянутых операций Δ и ∇, осуществляемых посредством соответствующего нелинейного управляемого логического элемента ▲/▼ или ▼/▲ с перестраиваемой конфигурацией по сигналу cj; так, что

- при сигнале cj, идентифицируемом как 0, сигнал zj+τ отождествляют zj+τ=Δzj с сигналом Δzj; а

- при сигнале cj, идентифицируемом как 1, сигнал zj+τ отождествляют zj+τ=∇zj с сигналом ∇zj;

- а в случае, когда упомянутый сигнал cj не идентифицируется, как предписывают изначально, сигнал zj+τ отождествляют с сигналом Δzj или с сигналом ∇zj, или задают постоянным или исходя из  сторонних одноразрядных сигналов

сторонних одноразрядных сигналов  ;

;

- при этом упомянутые сигналы {Δzj, ∇zj} формируют {Δzj=gjΔjqj, ∇zj=gj∇jqj} исходя из поставленных в соответствие указанному разряду j упомянутых операций {Δj, ∇j} и сигналов gj и qj базового G и нелинейного блока Q;

- при этом сигнал z1 в первом разряде образующего блока Z, который формируют с упомянутым смещением τ=1 на единицу, задают постоянным или исходя из z1=zо стороннего постоянного или переменного одноразрядного сигнала zо.

2. Способ по п.1, характеризующийся тем, что в составе разрядов образующего блока Z используют одинаковые упомянутые нелинейные управляемые логические элементы ▲/▼ или ▼/▲ и одинаковые нелинейные логические элементы ▲ или ▼.

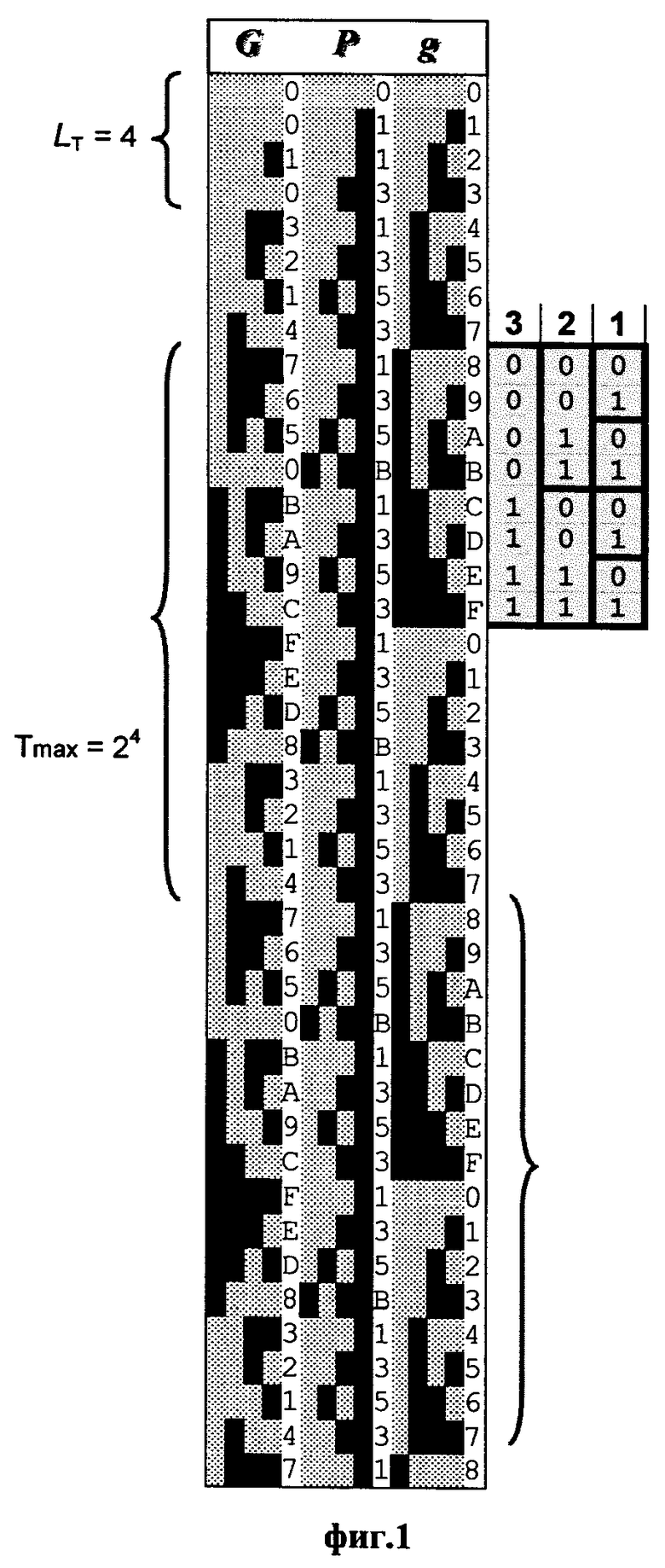

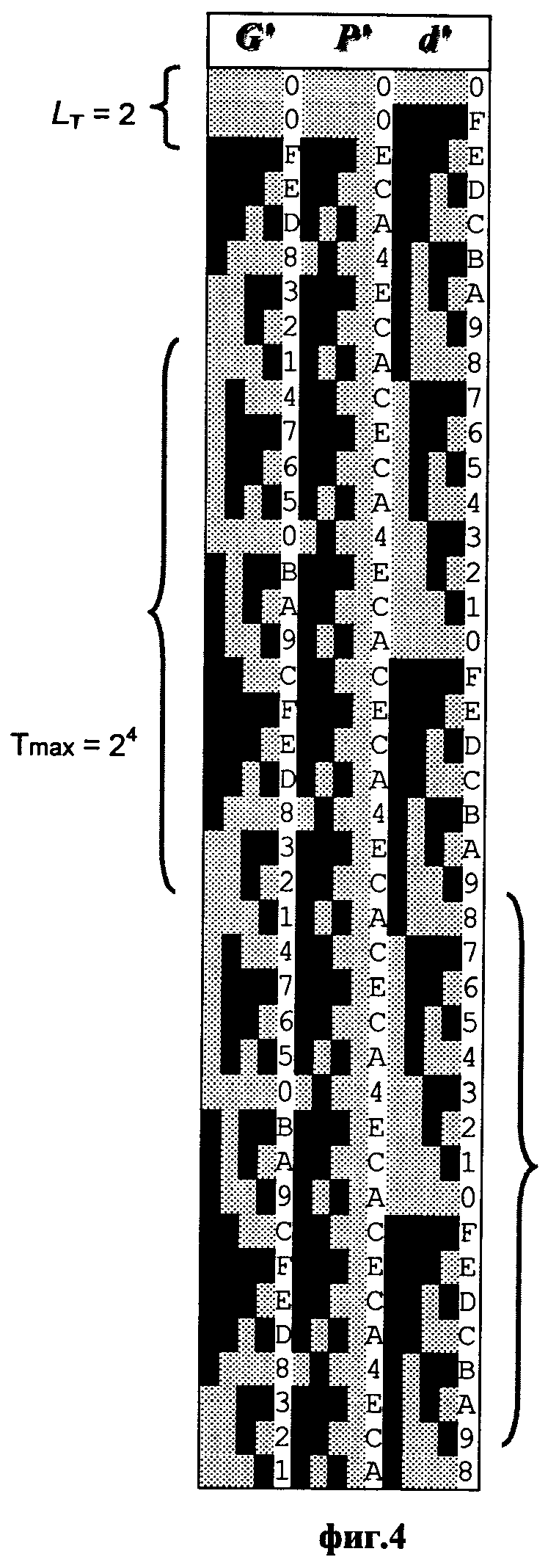

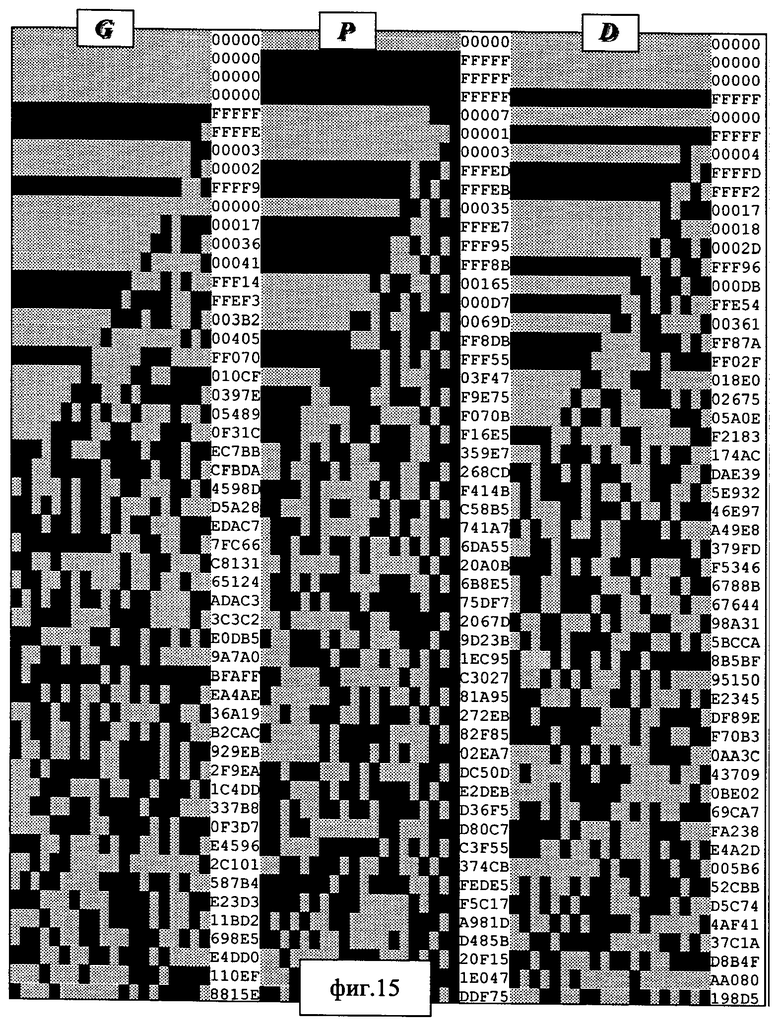

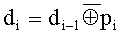

3. Способ по п.1, характеризующийся тем, что упомянутый сигнал z1 в первом разряде образующего блока Z задают постоянным, и при этом поставленная в соответствие упомянутому процессу последовательность D={di}, состоящая из (n+ε)-разрядных элементов di образуемых di=di-1⊕pi, при сигнале z1, идентифицируемом как 1, посредством поразрядной операции ⊕ сложения по модулю 2, представляемой логическими элементами XOR, или при сигнале z1, идентифицируемом как 0, инверсных по отношению к ним элементов  посредством поразрядной операции

посредством поразрядной операции  , представляемой логическими элементами XNOR, соответственно, значения предшествующего элемента di-1∈D последовательности D, со значением, следующим из очередного (n+ε)-разрядного элемента pi∈PΩ упомянутой последовательности PΩ, имеет максимальный период повторения Tmax=2n+ε и в пределах периода не имеет одинаковых элементов.

, представляемой логическими элементами XNOR, соответственно, значения предшествующего элемента di-1∈D последовательности D, со значением, следующим из очередного (n+ε)-разрядного элемента pi∈PΩ упомянутой последовательности PΩ, имеет максимальный период повторения Tmax=2n+ε и в пределах периода не имеет одинаковых элементов.

| EP 0467239 A2, 22.01.1992 | |||

| US 7206797 B2, 17.04.2007 | |||

| US 7003109 B2, 21.02.2006 | |||

| US 5592107 A, 07.01.1997. |

Авторы

Даты

2012-12-10—Публикация

2011-08-19—Подача